ECPE Roadmap 2025 Workshop

# **Vision – Power Electronics 2025**

#### Johann W. Kolar

Swiss Federal Institute of Technology (ETH) Zurich Power Electronic Systems Laboratory www.pes.ee.ethz.ch

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

#### ECPE Roadmap 2025 Workshop

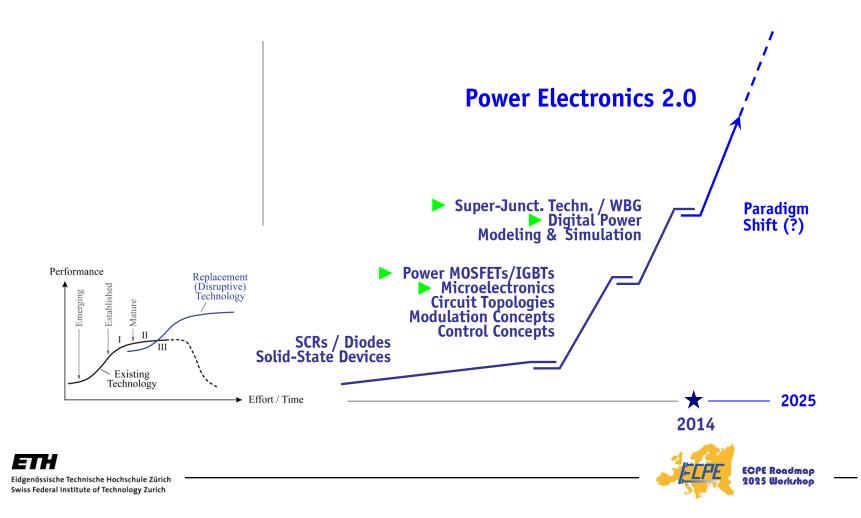

# **Power Electronics 2.0**

#### Johann W. Kolar

Swiss Federal Institute of Technology (ETH) Zurich Power Electronic Systems Laboratory www.pes.ee.ethz.ch

# **Outline**

- **Evolution of Power Electronics**

- Performance Trends / Enablers & Barriers / New Paradigms

Characteristics of Power Electronics 2.0

- **Conclusions**

# Evolution of Power Electronics

≻

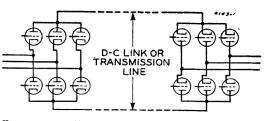

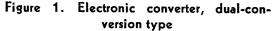

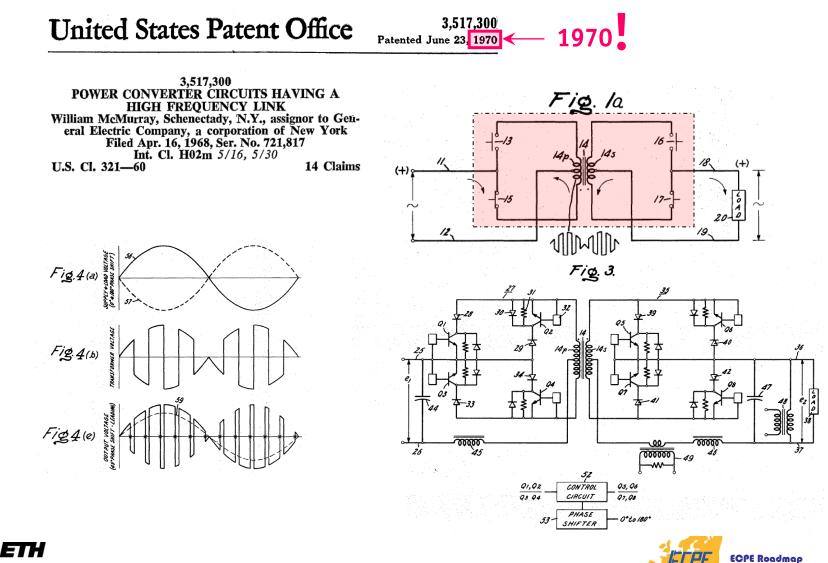

### History and Development of the Electronic Power Converter

E. F. W. ALEXANDERSON E. L. PHILLIPI FELLOW AIEE NONMEMBER AIEE

THE TERM "electronic power converter" needs some definition. The object may be to convert power from direct current to alternating current for d-c power transmission, or to convert power from one frequency into another, or to serve as a commutator for operating an a-c motor at variable speed, or for transforming high-voltage direct current into low-voltage direct current. Other objectives may be mentioned. It is thus evidently not the objective but the means which characterizes the electronic power converter. Other names have been used tentatively but have not been accepted. The emphasis is on electronic means and the term is limited to conversion of power as distinguished from electric energy for purposes of communication. Thus the name is a definition.

Paper 44-143, recommended by the AIEE committee on electronics for presentation at the AIEE summer technical meeting, St. Louis, Mo., June 26. 30, 1944. Manuscript submitted April 25, 1944 made available for printing May 18, 1944. E. F. W. ALEXANDERSON and E. L. PHILLIPI are with the General Electric Company. Schemestrady

with the General Electric Company, Schenectady, N. Y.

D-c transformer

Alexanderson, Phillipi-Electronic Converter

ELECTRICAL ENGINEERING

ECPE Roadmap 2025 Workshop

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

2025 Workshop

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich Power Electronic Systems Laboratory

United States Patent [19]

[11]

4,143,414

Brewster et al.

[45]

Mar. 6, 1979

1979

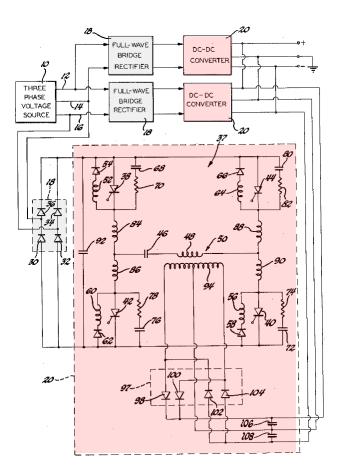

#### [54] THREE PHASE AC TO DC VOLTAGE CONVERTER WITH POWER LINE HARMONIC CURRENT REDUCTION

- [75] Inventors: Roger F. Brewster; Alfred H. Barrett, both of Santa Barbara, Calif.

- [73] Assignee: General Motors Corporation, Detroit, Mich.

- [21] Appl. No.: 894,739

- [22] Filed: Apr. 10, 1978

#### [57] ABSTRACT

A three phase AC to DC voltage converter includes separate single phase AC to DC converters for each phase of a three phase source with the DC voltage output of the three converters paralleled and controlled to provide necessary regulation. Each of the single phase AC to DC converters includes a full-wave bridge rectifier feeding a substantially resistive load including an inverter and a second single phase full-wave bridge rectifier. To the extent that each inverter and second single phase full-wave bridge rectifier approximate a resistive load, the source current harmonics are reduced. Additionally, the triplen harmonics produced in the three phase source lines by each of the three AC to DC converters are cancelled by the triplen harmonics produced in the three phase source lines by the remaining two AC to DC converters.

2 Claims, 1 Drawing Figure

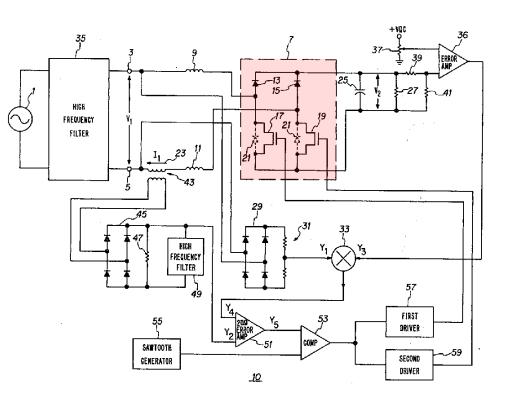

#### [54] AC-DC CONVERTER HAVING AN IMPROVED POWER FACTOR

- [75] Inventor: Daniel M. Mitchell, Cedar Rapids, Iowa

- [73] Assignee: Rockwell International Corporation, El Segundo, Calif.

- [21] Appl. No.: 414,757

- [22] Filed: Sep. 3, 1982

#### [57] ABSTRACT

An AC to DC converter utilizes a first power converter for converting an AC signal to a DC signal under the control of a control signal. The control signal is generated by a control circuit that includes a first analog generator that provides a first signal that is analogous to the voltage of the AC signal that is to be converted. A second analog generator generates a second signal that is analogous to the current of the AC signal that is to be converted and a third analog generator generates a third signal that is analogous to the voltage of the DC output signal. The third signal and the first signal are multiplied together to obtain a fourth signal. The control signal is generated from the fourth signal and the second signal and is used to control the power converter such that the waveform of the current of the AC signal is limited to a sinusoidal waveform of the same frequency and phase as the AC signal.

8 Claims, 2 Drawing Figures

1983

4,412,277

Oct. 25, 1983

[11]

[45]

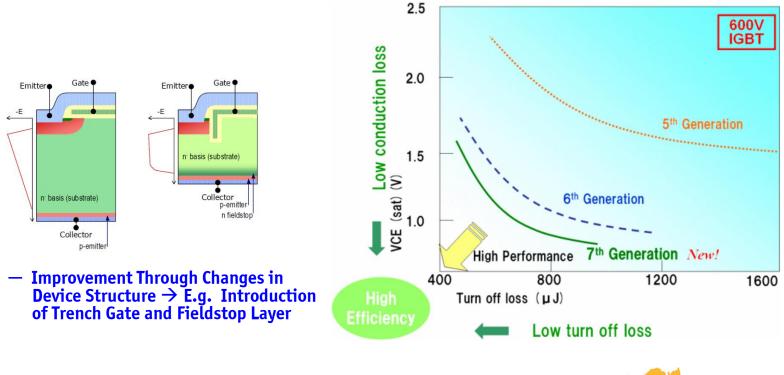

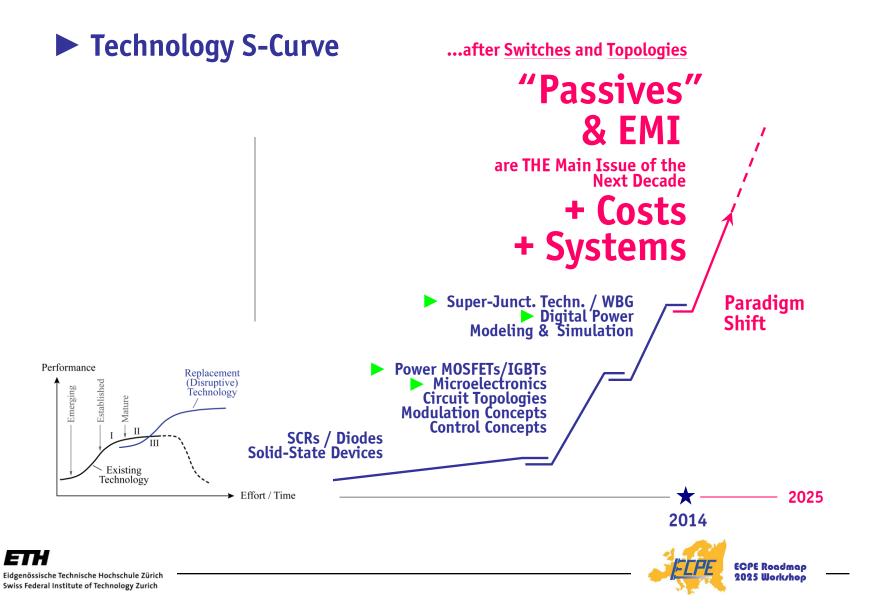

### Technology S-Curve

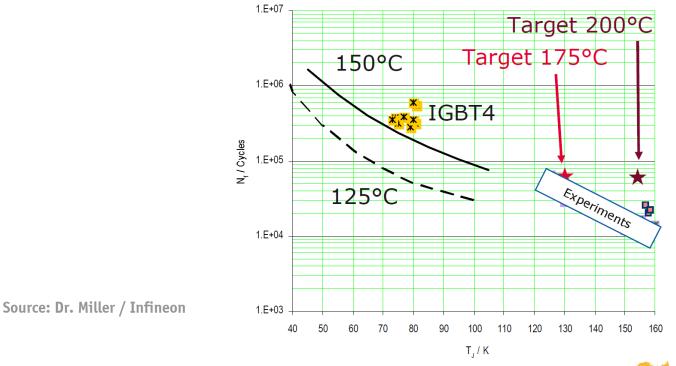

Source: Dr. Miller / Infineon

# Technology S-Curve

- Sub-S-Curves

- Overall Development Defined by Improvement of Core Technologies

4 2nd Gen 3rd Gen 4th Gen 5th Gen 3.5 VCEsat(125°C) [V] @ 75A 3 1st Gen  $A/A_0 = 1$  $A/A_0 = 0.65$ 2.5 1200 V / 75 A IGBT rated switching power: 100kW rated short circuit power: 500 kW 2 - $A/A_0 = 0.44$ 1.5 1 1988 1992 1996 2000 2004 2008 2012 20 conventional HVMOS RDS(on)\*A,max [Ohm\*mm<sup>2</sup>] 16 12 8 Future CoolMOST MOSFET-Gen. 2nd Gen. 3rd Gen. 4 0 1992 1996 2000 2004 2008 2012

> ECPE Roadmap 2025 Workshop

Importance

- Power Semiconductors (incl. Package)

Microelectronics / Signal Processing

Topologies

- 4. Analysis / Modeling & Simulation

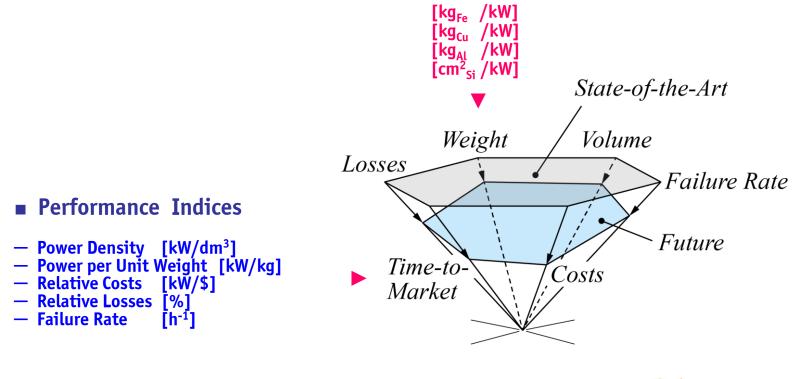

#### Performance Indices \_ → Coupling & Limits

$\rightarrow$

#### 12/102

### Power Electronics Converters Performance Trends

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

2025 Workshop

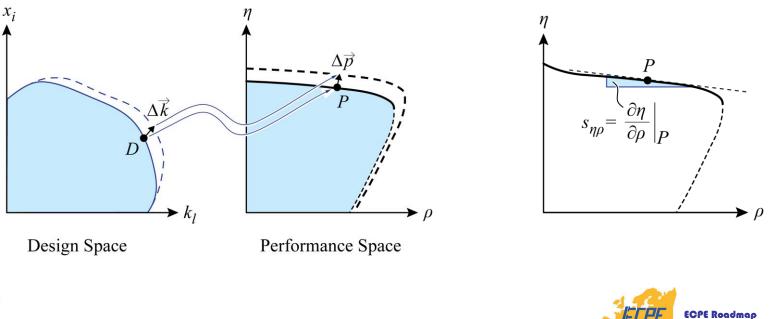

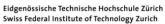

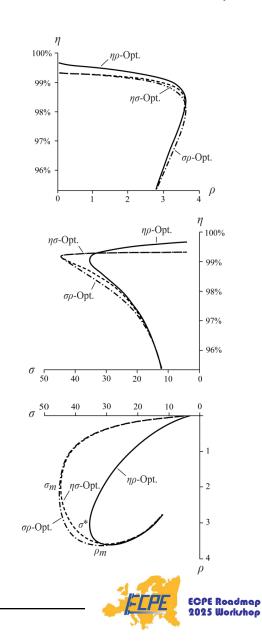

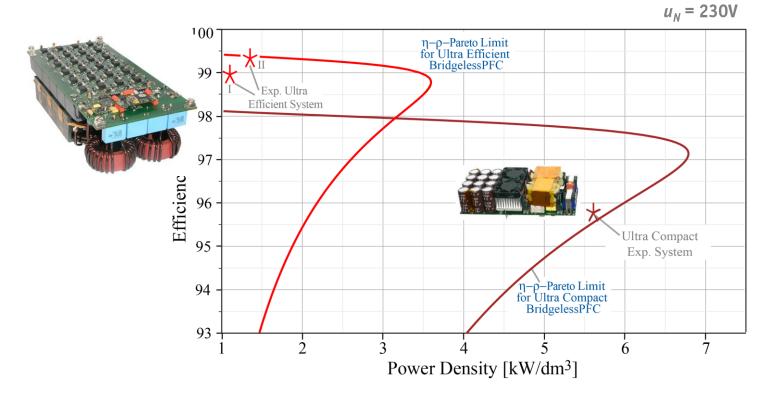

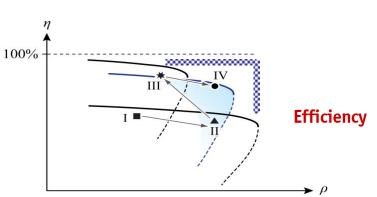

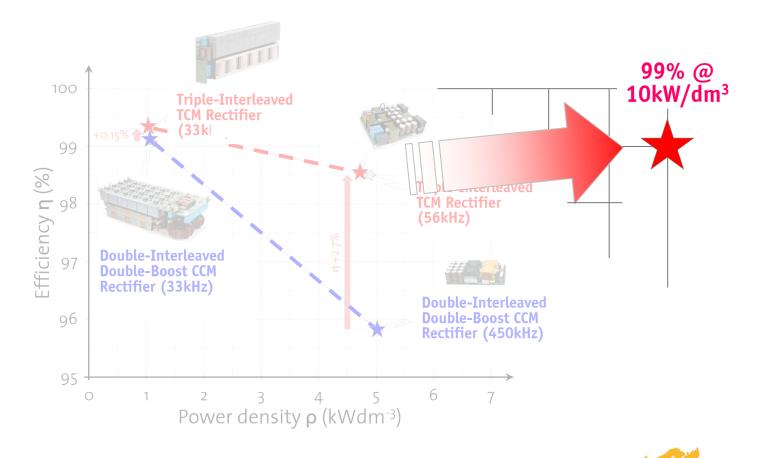

### ► Analysis of Performance Limits $\rightarrow$ Pareto Front

- **Sensitivity** to Technology Advancements (Example: η-ρ-Pareto Front)

- **Trade-off** Analysis

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

ET

#### Experimental Verification of Performance Limits

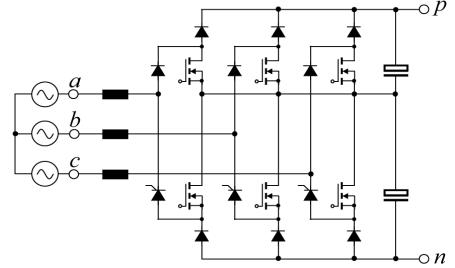

$\rightarrow$  3-ph. VIENNA Rectifier  $\rightarrow$  1-ph. PFC Rectifiers

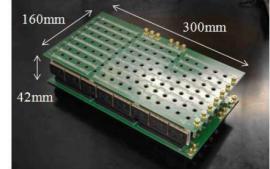

**Demonstrator #1**  $\rightarrow$  3-ph. VIENNA Rectifier

#### Specifications

$U_{LL} = 3 \times 400 V$   $f_N = 50 Hz \dots 60 Hz \text{ or } 360 Hz \dots 800 Hz$   $P_0 = 10 kW$   $U_0 = 2 \times 400 V$  $f_s = 250 \text{ kHz}$

Characteristics

η = 96.8 % THD<sub>i</sub> = 1.6 % @ 800 Hz 10 kW/dm3 3.3 kg (≈3 kW/kg)

**Dimensions:** 195 x 120 x 42.7 mm<sup>3</sup>

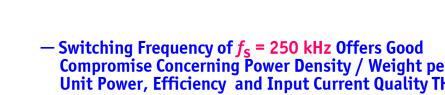

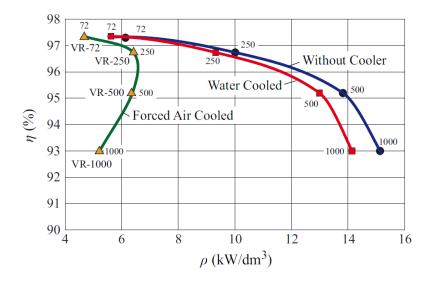

### **Demonstrator #1** $\rightarrow$ 3-ph. VIENNA Rectifier

Experimental Evaluation of Generation 1 – 4 of VIENNA Rectifier Systems

| of                        | $f_{\rm S}$ = 50 kHz<br>ho = 3 kW/dm <sup>3</sup>                                                    |  |

|---------------------------|------------------------------------------------------------------------------------------------------|--|

| per<br>/ THD <sub>i</sub> | $f_{\rm S}$ = 72 kHz<br>ho = 4.6 kW/dm <sup>3</sup>                                                  |  |

|                           | f <sub>s</sub> = 250 kHz<br>ρ = 10 kW/dm <sup>3</sup><br>(164 W/in <sup>3</sup> )<br>Weight = 3.4 kg |  |

|                           | $f_{\rm S}$ = 1 MHz<br>ho = 14.1 kW/dm <sup>3</sup><br>Weight = 1.1 kg                               |  |

#### **Demonstrator #2** $\rightarrow$ 1-ph. Bridgeless PFC Rectifiers

**Power Density is Based on Net Volumes** → **Scaling by 0.6-0.8 Necessary**

ECPE Roadmap 2025 Workshop

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

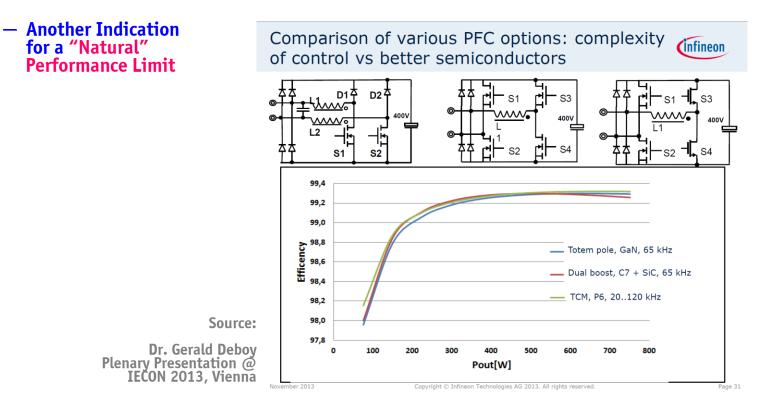

### Pareto Front of Power Semiconductors

#### Trade-Off Between Conduction and Switching Losses

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

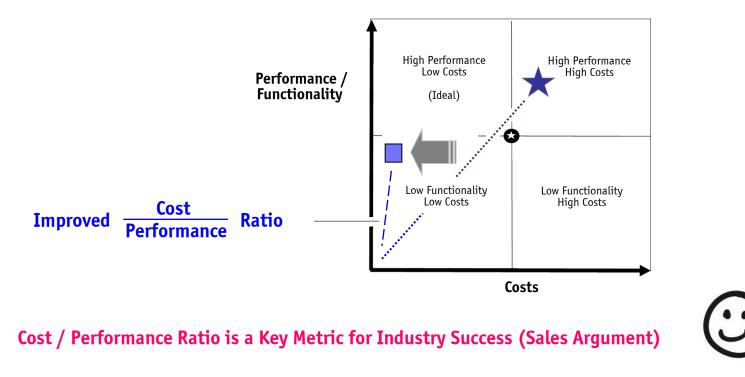

### Observation

"Standard" / Relatively High Performance Solutions for Nearly All Key Applications Existing Today !

#### • Very Limited Room for Further Perform. Improvement $\rightarrow$ only COST Reduction (!)

### General Remark

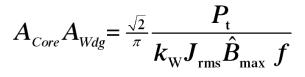

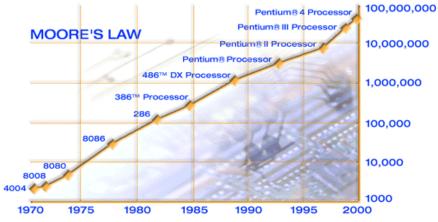

- → There is No "Moore's Law" in Power Electronics !

- **Example:** Scaling Law of Transformers

transistors

ECPE Roadmap 2025 Workshop

■ No Fundamentally New Concepts of Passives → We are Left with Progress in Material Science (Takes Decades)

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

Source: EPCOS

### ► General Remark (2)

#### **Expected (Slow) Technology Progress of Passives**

#### - Foil Capacitors

OPP = Oriented Polypropylene PHD = Advanced OPP COC = Cycloolefine Copolymers

|                  | 2000   | 2005   | 2010   | 2015   |

|------------------|--------|--------|--------|--------|

| Energy Density   | 100%   | 100%   | 110%   | 120%   |

| Film Material    | OPP    | PHD    | COC    | ?      |

| Max. Temperature | 105 °C | 115 °C | 150 °C | 160 °C |

| Self Inductance  | 60 nH  | 30 nH  | 15 nH  | 10 nH  |

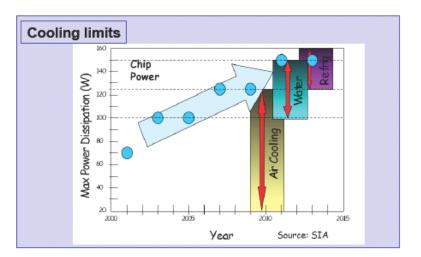

#### - Cooling

Air Cooling Water Cooling Refrigeration Technologies

#### ... similar for Magnetics

# Next Evolutional Step

"... Prediction is Very Difficult, Especially if it's About the Future ..."

(N. Bohr)

# — "Optimistic" View \_\_\_\_\_

# ▶ Optimistic View $\rightarrow$ Break Through (Shift) the Barriers

Degrees of Freedom

- Topologies

- Modulation Schemes

- Control Schemes

- etc.

... only if not Fundamental Physical Properties

**Remark:** Designer's Point of View (Given Semiconductors & Base Materials)

ECPE Roadmap 2025 Workshop

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

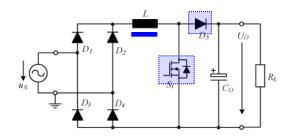

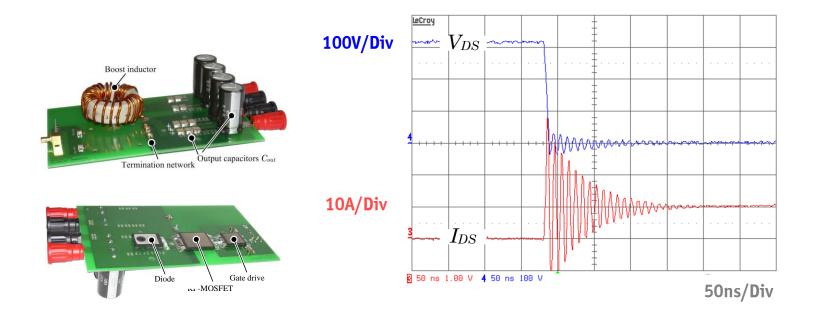

► "Snubbers" (1)

Example: 1-ph. Telekom Boost-Type PFC Rectifier

- Complexity Increases Exp. if "Natural" Limit of a Technology is Approached

- Next Step in Semiconductor Technologies Makes Snubbers Obsolete → SiC Diodes

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

2025 Workshop

**Power Electronic Systems** Laboratory

▶ "Snubbers" (2)

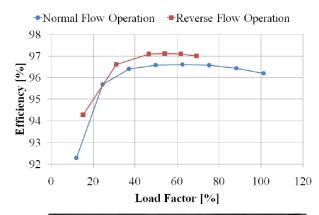

**Example: Non-Isolated Buck+Boost** \_\_\_\_ **DC-DC Converter for Automotive Applications**

Instead of Adding Aux. Circuits Change Operation of BASIC (!) Structure – "Natural" Performance Limit

29kW/dm<sup>3</sup>

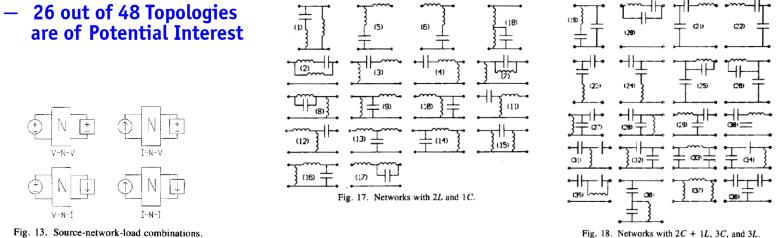

### New Converter Topologies

Minimum Performance Difference for Best Matching of Topology/Semicond./Modulation Only Use BASIC Topologies - Costs are THE Deciding Criteria (!)

### New Converter Topologies

Very Large Number of Options !

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 7, NO. 1, JANUARY 1992

**Topologies for Three-Element Resonant Converters** Example

#### **Tools for Comprehensive Comparative Evaluation Urgently needed !**

#### Rudolf P. Severns

Fig. 18. Networks with 2C + 1L, 3C, and 3L.

**Examples:**

### **Integration of Functions**

\* Single-Stage Approaches / Matrix Converters

\* Multi-Functional Utilization (Machine as Inductor of DC/DC Conv.)

\* etc.

- **Integration Restricts Controllability / Overall Functionality** Frequently Lower Performance of Integrated Solution Basic Physical Properties remain Unchanged (e.g. Filtering Effort)

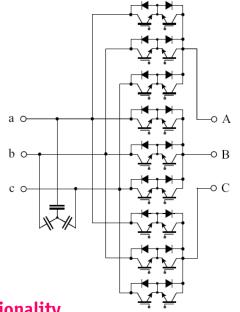

# **Extreme Restriction of Functionality**

- Highly Optimized Specific Functionality  $\rightarrow$  High Performance for Specific Task

- Restriction of Functionality  $\rightarrow$  Lower Costs

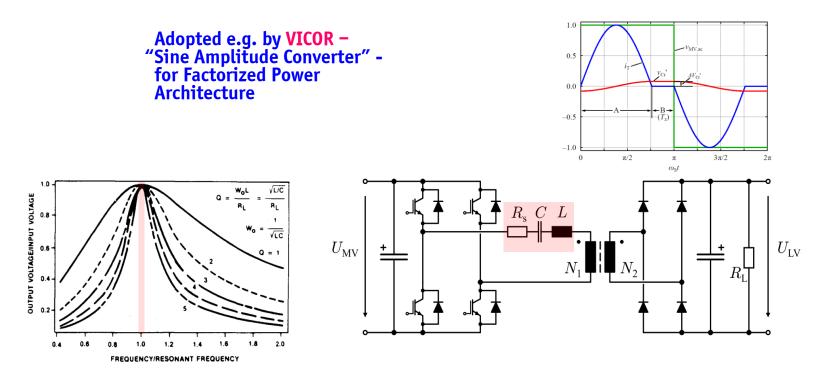

# Extreme Restriction of Functionality

- Example: DC-Transformer  $\rightarrow$  Isolation @ Constant (Load Ind.) Voltage Transfer Ratio

■ Resonant Frequ. ~ Switching Frequ. ~ Input/Output Voltage Ratio =  $N_1/N_2$  (Steigerwald, 1988)

34/102

ECPE Roadmap 2025 Workshop

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

ETH

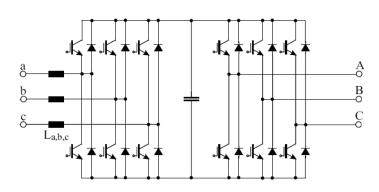

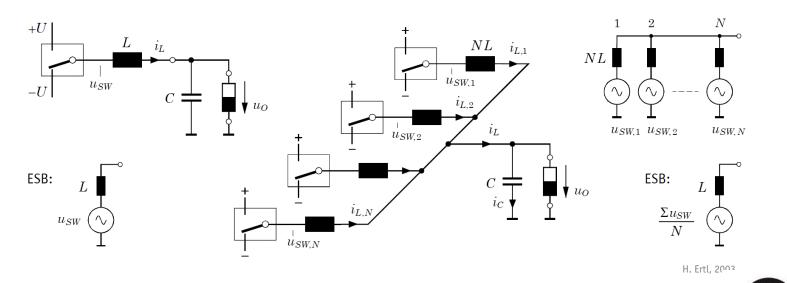

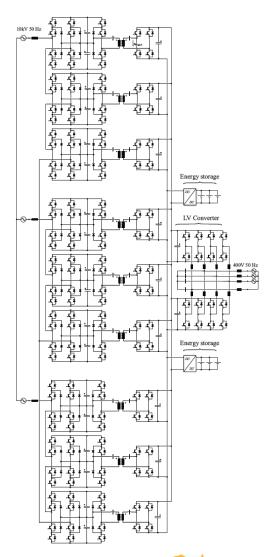

### Multi-Cell Converters (Homogeneous Power)

**Example of Parallel Interleaving**

- Breaks the Frequency Barrier

- Breaks the Impedance Barrier

- Breaks Cost Barrier Standardization

- High Part Load Efficiency

Fully Benefits from Digital IC Technology (Improving in Future)

Redundancy → Allows Large Number of Units without Impairing Reliability

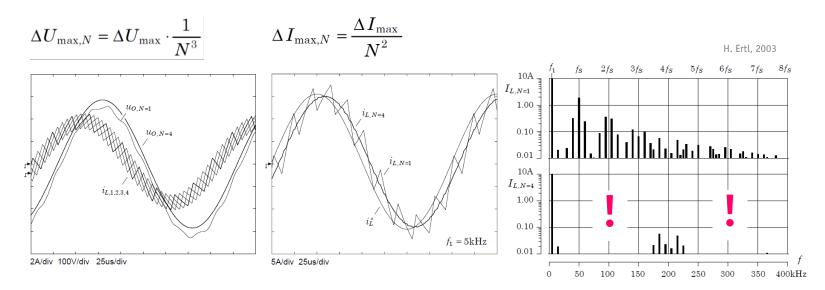

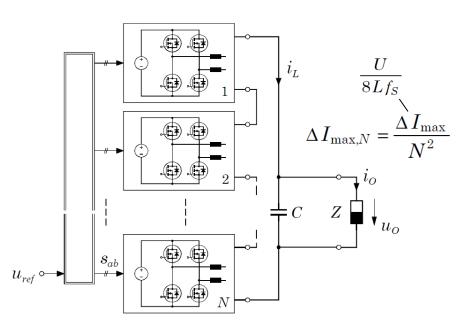

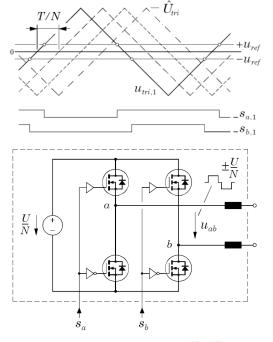

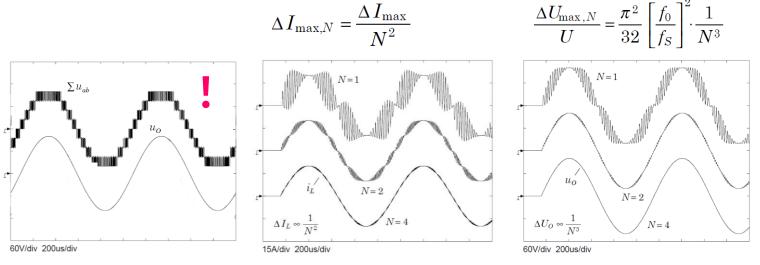

### Multi-Cell Converters

Basic Concept @ Example of Parallel Interleaving

- Multiplies Frequ. / Red. Ripple @ Same Switching Losses & Increases Control Dynamics

■ Fully Benefits from Digital IC Technology (Improving in Future)

■ Redundancy → Allows Large Number of Units without Impairing Reliability

**Example of Series Interleaving**

$$\frac{\Delta U_{\max,N}}{U} = \frac{\pi^2}{32} \left[ \frac{f_0}{f_S} \right]^2 \cdot \frac{1}{N^3}$$

- Breaks the Frequency Barrier

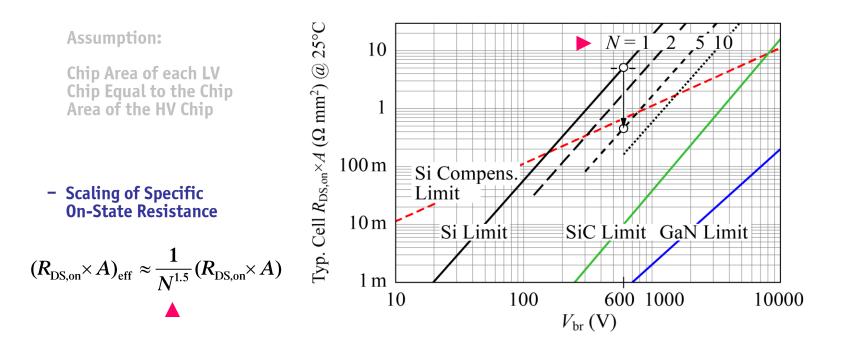

Breaks the Silicon Limit 1+1=2 NOT 4 (!)

Breaks Cost Barrier Standardization

- Extends LV Technology to HV

ECPE Roadmap 2025 Workshop

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

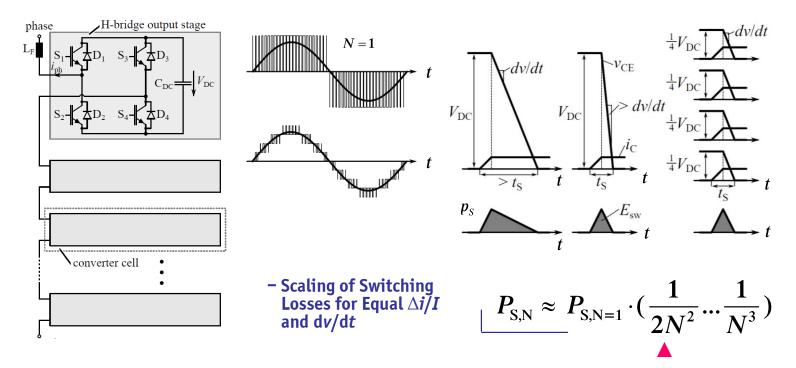

- **Example of Series Interleaving**

- Multiplies Frequ. / Red. Ripple @ Same Switching Losses & Increases Control Dynamics

H. Ertl, 2003

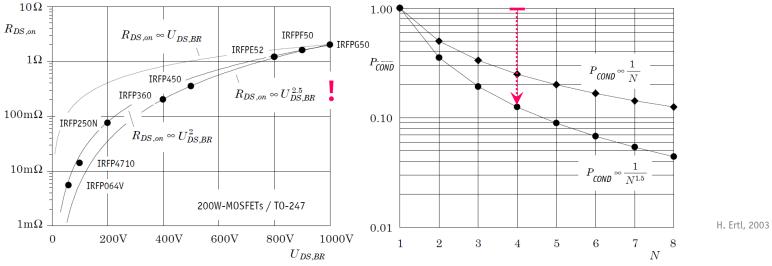

Especially Advantageous for Ohmic On-State Behavior of Power Switches (!)

Redundancy

Allows Large Number of Units without Impairing Reliability

- **Example of Series Interleaving**

- Scaling of  $R_{DS,on}$  of MOSFETs with Blocking Voltage  $\rightarrow$  Loss Red. by Factor of 8 for N=4

Especially Advantageous for Ohmic On-State Behavior of Power Switches (!) Redundancy  $\rightarrow$  Allows Large Number of Units without Impairing Reliability

Series Connection of LV MOSFETs (LV Cells) Effectively SHIFTS the Si-Limit (!)

Excellent Opportunity for Extreme Efficiency Ultra-Compact Converters

#### Interleaved Series Connection Dramatically Reduces Switching Losses (or Harmonics)

Converter Cells Could Operate at VERY Low Switching Frequency (e.g. 5kHz)

Minimization of Passives (Filter Components)

ECPE Roadmap 2025 Workshop

### Multi-Cell Converters – Summary

#### Advantages

- Switching Frequency Multiplication @ No Loss Increase

- Ripple Reduction @ Input and Output

- Distribution of Losses (Parallel Connect. of Therm. Resistances)

- Larger Surface / Volume Ratio of Indiv. Unit (Easier Cooling)

- Redundancy Possible (High Reliability)

- Deactivation of Units at Part Load (High Part Load Efficiency)

- Solves the Impedance Matching Problem @ High I or U

- Multiplies U, I Capabilities of Single Devices (Very High U, I possible)

- Reduction of Eff. RDS(on) (Shifting Si-Limit for Series Connection)

- Eff. Increase of Switching Speed @ Given du/dt, di/dt

- Supports Standardization (Potential Cost Reduction)

- Minimizes Time-to-Market (Allows Platform Solutions)

- Supports PCB Realization even for High Current (Current Partitioning)

- Challenges

- Handling of Control Complexity (Digital Control)

- Overall Complexity Increasing Costs (Economy of Scale?)

- Symmetrization of the Loading of the Individual Units

- Idea for Supporting Technology

PCBs with Embedded Optical Fibers / Link

... a Highly Powerful Concept with Large Potential (!)

ECPE Roadmap 2025 Workshop

#### Examples of Multi-Cell Converters

$\begin{array}{l} \rightarrow \text{VRM} \\ \rightarrow \text{ Ultra-Efficient 1ph. PFC} \\ \rightarrow \text{ Telecom Power Supplies} \end{array}$

44/102

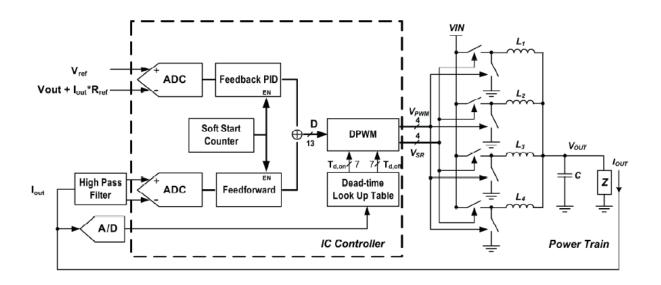

#### Voltage Regulator Module

Multi-Channel / Parallel Interleaving of up to 12 Channels

Coupling Inductors (Interphase Inductors) allows Further Reduction of Ind. Comp. Volume

For On-Chip Integration Challenged by Switched Capacitor Converters

#### 45/102

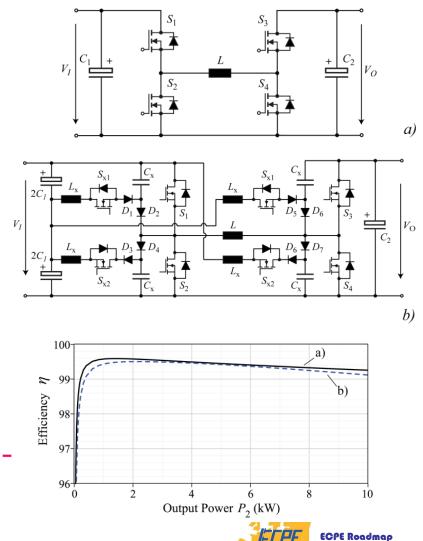

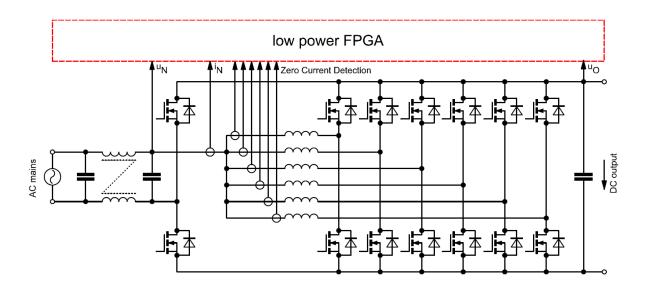

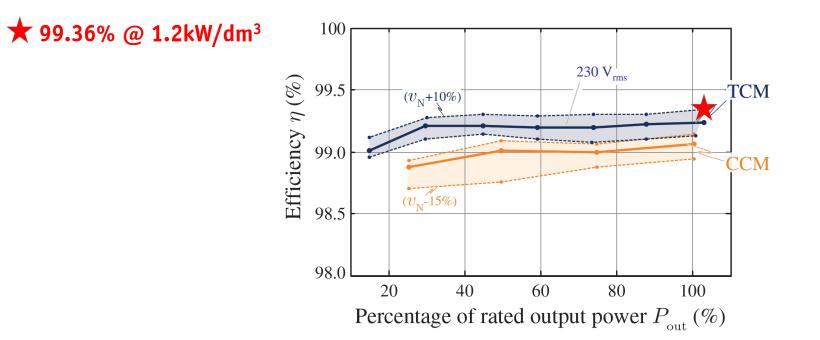

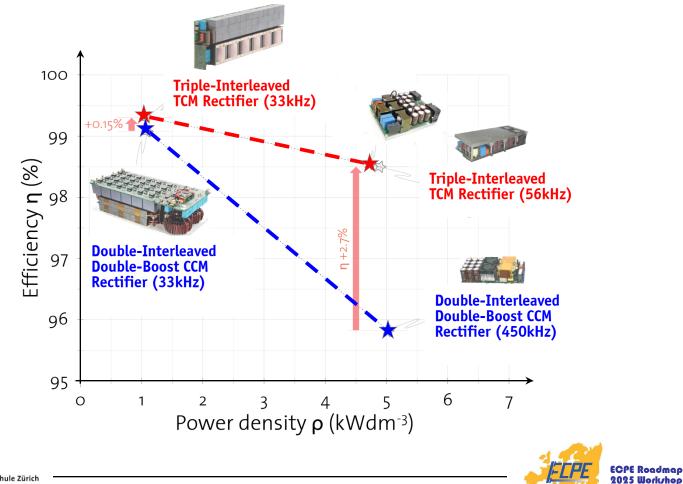

#### Bidirectional Ultra-Efficient 1-Ф PFC Mains Interface

### ★ 99.36% @ 1.2kW/dm<sup>3</sup>

**Employs NO Sic Power Semiconductors -- Si SJ MOSFETs only**

ECPE Roadmap 2025 Workshop

#### ► Bidirectional Ultra-Efficient 1-Φ PFC Mains Interface

#### ■ AC-DC Rectifier - Single Boost Cell - Measurements

Eidgenössische Technische Hochschule Zürich

Swiss Federal Institute of Technology Zurich

#### ► Bidirectional Ultra-Efficient 1-Φ PFC Mains Interface

Hardware Testing to be finalized in September 2011

#### **Employs NO SiC Power Semiconductors** -- **Si SJ MOSFETs only**

ECPE Roadmap 2025 Workshop

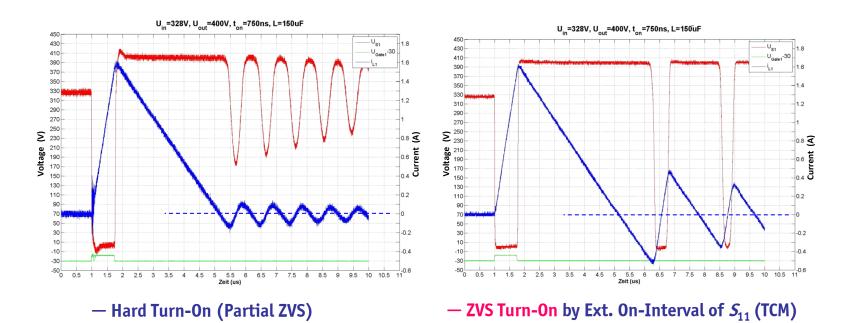

#### Bidirectional Ultra-Efficient 1-Ф PFC Mains Interface

#### **Employs NO SiC Power Semiconductors** -- **Si SJ MOSFETs only**

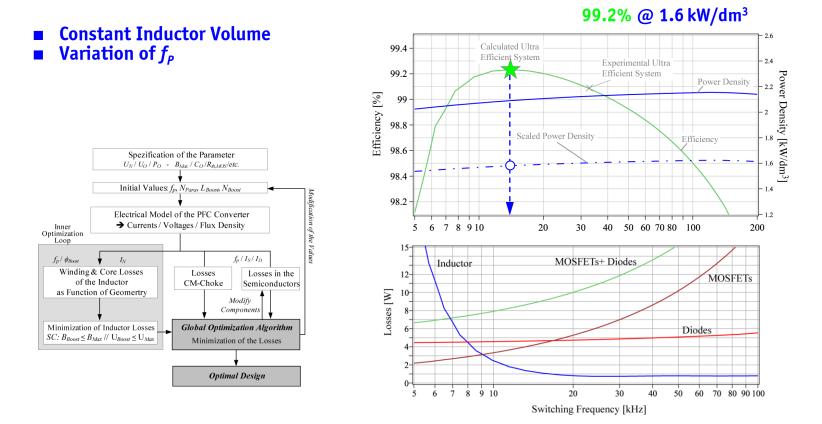

#### Converter Performance Evaluation Based on η-ρ-Pareto Front

#### KEYS for Achieving the Performance Improvement

- **Basic Topology**

- **ZVS Only Achieved by Modified Operation Mode**

- Active ZVS

- Triangular Current Mode (TCM)

- Variable Switching Frequency No Diode On-State Voltage Drop

- Continuously Guided u, i Waveforms

- Interleaving

- Utilization of Low Superjunct. R<sub>DS,(on)</sub> Utilization of Digital Signal Processing

- ... despite Using "Old" Si Technology

- Low Complexity

- No Aux. Circuits

- No (Low) Switching Losses

No Direct Limit of # of Parallel Trans.

- Simple Symm. of Loading of Modules

- Spread & Lower Ampl. EMI Noise

- Synchr. Rectification

- No Free Ringing  $\rightarrow$  Low EMI Filter Vol.

- Low EMI Filter Vol. & Cap. Curr. Stress

- Low Cond. Losses despite TCM

- Low Control Effort despite 6x Interl.

... the Basic Concept is Known since 1989 (!)

#### Is Another Step of Massive Improvement Possible ?

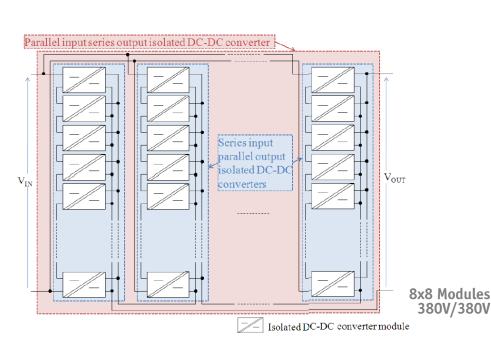

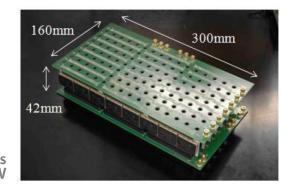

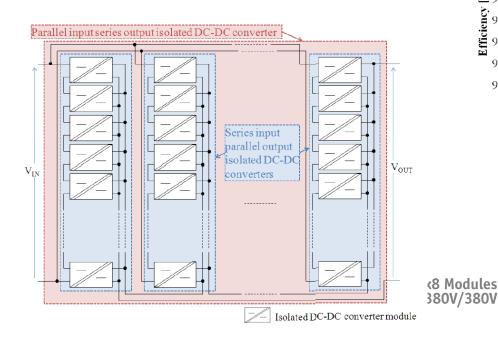

# ► Solution: **ISOP** Multi-Cell Approach (!)

Isolated 380V/48V Telecom DC-DC Converter 8 x 300W 48V/48V VICOR Modules 96.5% Efficiency @ 16kW/l Power Density (!)

Hayashi, NTT; 2012

| Parameter            | Value                |

|----------------------|----------------------|

| Total Output Power   | 2400W                |

| Rated Input Voltage  | 384V                 |

| Rated Output Voltage | 48V                  |

| Manufacturer         | VICOR                |

| Part Number          | V048F480T006         |

| Rated Power          | 336W                 |

| Size (W, D, Ht)      | 22mm, 32.5mm, 6.73mm |

| Input Voltage        | 26V - 55V            |

| Output Voltage       | 26V - 55V            |

| Efficiency           | 96.4% (at Full Load) |

ECPE Roadmap 2025 Workshop

# ► Solution: **ISOP** Multi-Cell Approach (!)

- Isolated 380V/48V Telecom DC-DC Converter 8 x 300W 48V/48V VICOR Modules 96.5% Efficiency @ 16kW/l Power Density (!)

ECPE Roadmap 2025 Workshop

#### "Killer"- Semiconductor Technologies

#### **WBG Power Semiconductors**

... Not a Merit of Power Electronics but of Power Semiconductor Research

ECPE Roadmap 2025 Workshop

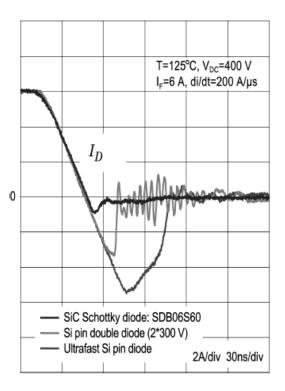

# **WBG Power Semiconductors**

Example: SiC Schottky Diode – Zero Recovery Rectifiers

- General Capabilities

- Higher Switching Frequency

- Higher Operating Temperature

- Higher Blocking Capability

# But ...

#### Today the Capabilities of SiC Cannot be Utilized

- Fast Switching Capability

- High Temp. Capability

- High Blocking Capability

- Limit by Package (Layout) Parasitics

- Missing High Temp. Package (Therm. Cycles)

- Missing High Temp. Passives

- Multi-Level Topologies !

- Missing MV / Low Inductance Package

ECPE Roadmap 2025 Workshop

# Higher Switching Speed

# Missing HF Package Missing Integrated Gate Drive (Active Control of Switching Trajectory)

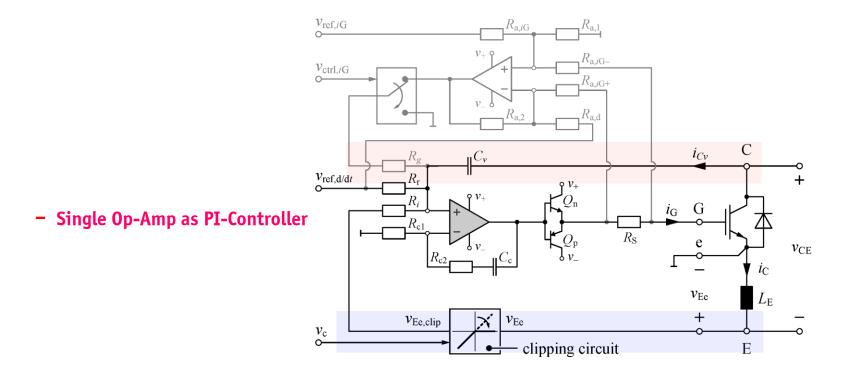

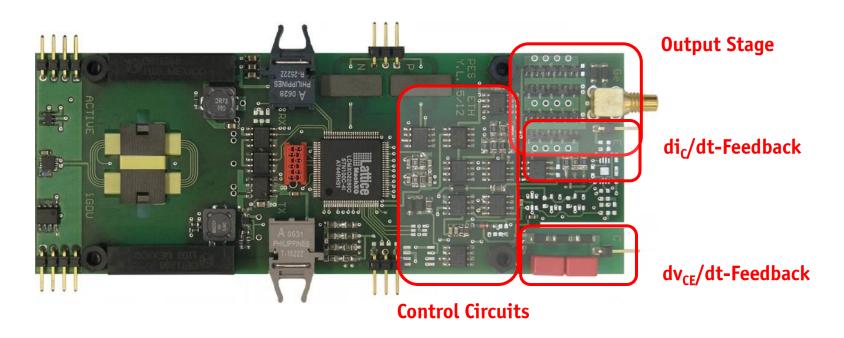

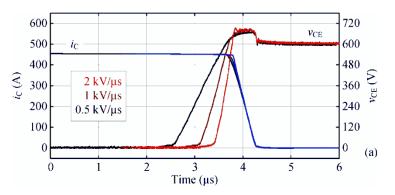

#### Active Closed Loop Gate Drive

Continuous (!) Control of the Switching Trajectory incl. Short Circuit

Options for Monitoring / Reliability Prediction etc.

### Hardware Prototype

**PCB Dimensions** 50 mm x 130 mm (2 in x 5.1 in)

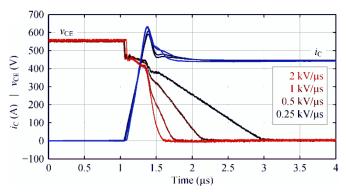

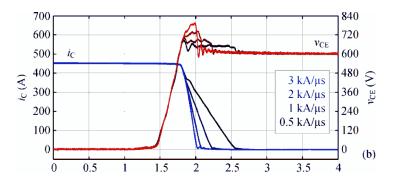

#### Experimental Results – Individual Variation of References

700 600  $v_{CE}$ 500 i<sub>c</sub>  $i_{\rm C}$  (A) |  $\nu_{\rm CE}$  (V) 400 3 kA/µs 300  $2 kA/\mu s$ 1 kA/µs 200 0.67 kA/µs 100 0 -1000.5 1.5 2 2.5 3 3.5 0 4

■ Turn-On: Variation of di<sub>c</sub>/dt

**Turn-On:** Variation of dv<sub>CE</sub>/dt

#### **Turn-Off:** Variation of di<sub>c</sub>/dt

**Turn-Off:** Variation of dv<sub>CF</sub>/dt

ECPE Roadmap 2025 Workshop

**Power Electronic Systems** Laboratory 61/102

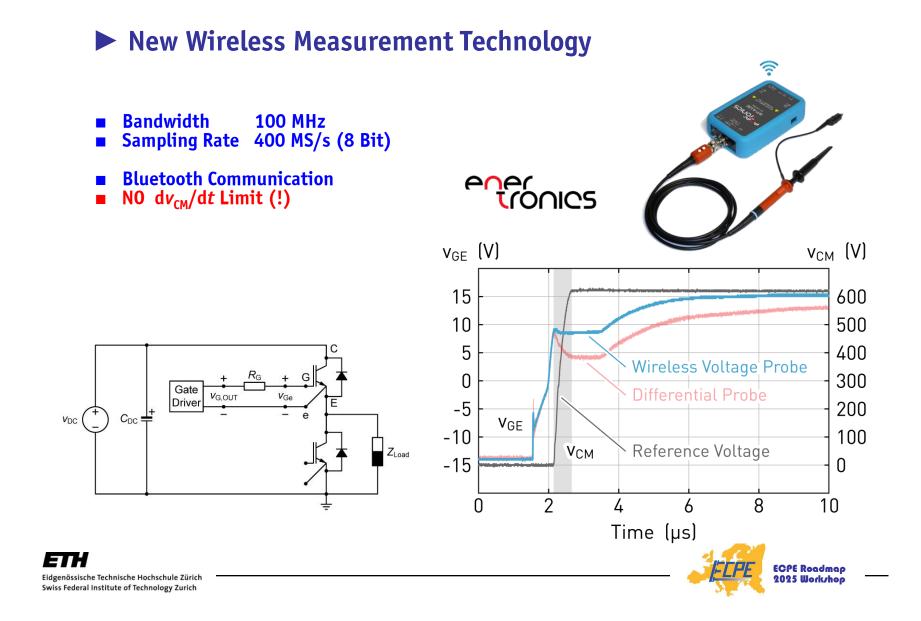

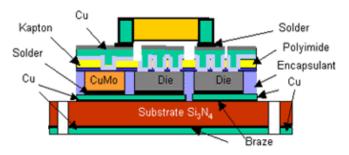

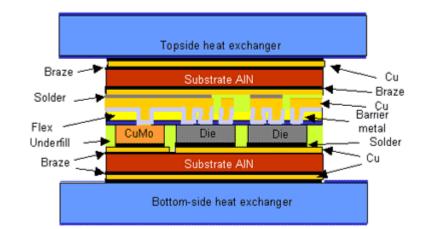

#### ► GE <u>Planar</u> <u>Power</u> <u>Polymer</u> <u>Packaging</u> (P4<sup>TM</sup>)

Oriented Toward High Power Devices <2400V / 100A...500A <200W Device Dissipation

Wire-Bonded Die on Ceramic Substrate Replaced with Planar Polymer-Based Interconnect Structure

**Direct High-Conductivity Cooling Path**

#### GE Global Research United States - India - China - Germany

ECPE Roadmap 2025 Workshop

#### ► GE <u>Planar</u> <u>Power</u> <u>Polymer</u> <u>Packaging</u> (P4<sup>TM</sup>)

#### CROSS SECTION OF A POWER OVERLAY MODULE

#### DOUBLE-SIDED COOLING OF A POWER OVERLAY MODULE

- Reduces Wire Bond Resistance by Factor 100

- Significantly Lower Switching Overvoltages

- Reduced Switching Losses

- No Ringing

- Reduces EMI Radiation

- Enables Topside Cooling

- No Mechanical Stress of Wire Bond Process

- Reduces CTE Wire Bond Stress on Chip Pads

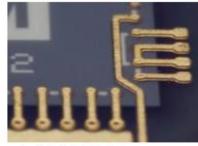

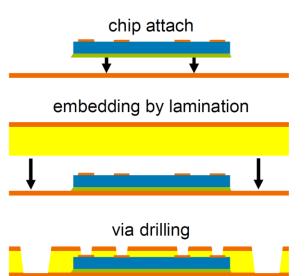

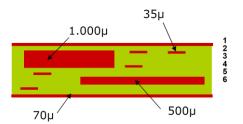

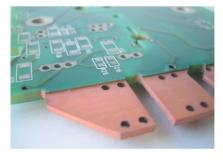

#### Novel PCB Technologies for **High Power Density Systems**

#### Chip in Polymer Process / Multi-Functional PCB

embedded chip in PCB structure.

- Chip Embedding by PCB Technology

- Direct Cu Contact to Chip / No Wires or Solder Joints

Thin Planar Packaging enables 3D Stacking

Improved Electrical Performance and Reliability

65/102

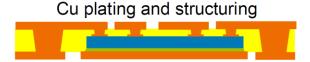

### Planar Power Chip Package

Novel Concepts for Power Packages and Modules

Module with Power and Logic Devices

Single Chip Package for MOSFETs and IGBTs

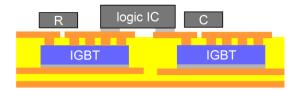

### Multi-Functional PCB

- Multiple Signal and High Current Layers

- **Thermal Management**

- "Fab-Less" Power Electronics

- Testing is Challenging (Only Voltage Measurement) Advanced Simul. Tools of Main Importance (Coupling with Measurem.)

67/102

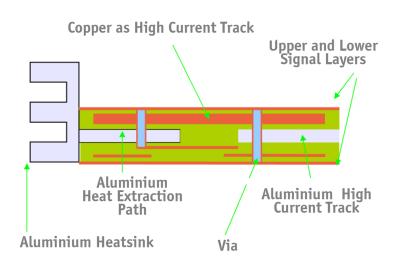

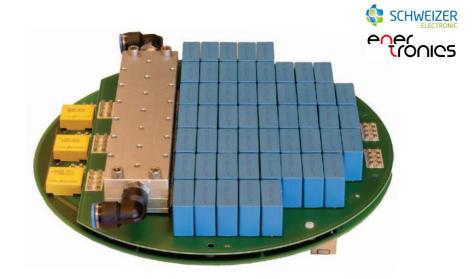

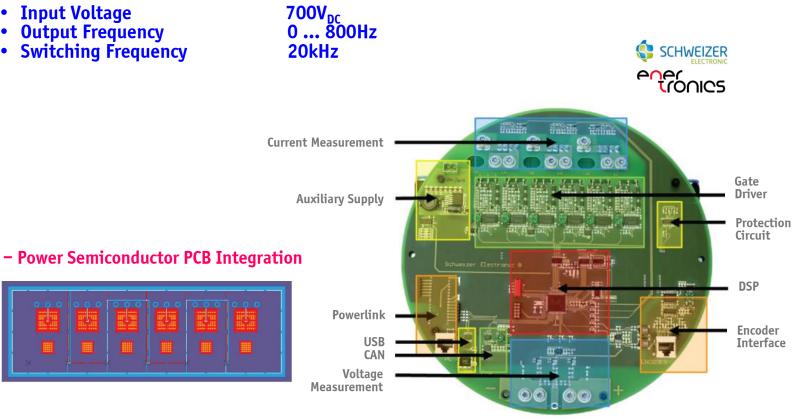

# ► 3ph. Inverter in p<sup>2</sup>pack-Technology

- **Rated Power** •

- Input Voltage •

- •

- Output Frequency Switching Frequency •

32kVA 700V<sub>DC</sub> 0 ... 800Hz 20kHz

# ► 3ph. Inverter in p<sup>2</sup>pack-Technology

- **Rated Power** •

- Input Voltage •

- •

- Output Frequency Switching Frequency •

32kVA 700V<sub>DC</sub> 0 ... 800Hz 20kHz

ECPE Roadmap 2025 Workshop

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

ETH

# ► 3ph. Inverter in p<sup>2</sup>pack-Technology

- **Rated Power** •

- **Input Voltage** •

- •

- Output Frequency Switching Frequency •

32kVA

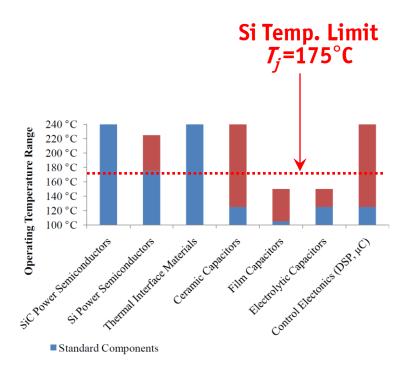

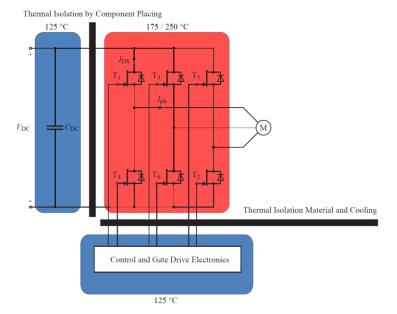

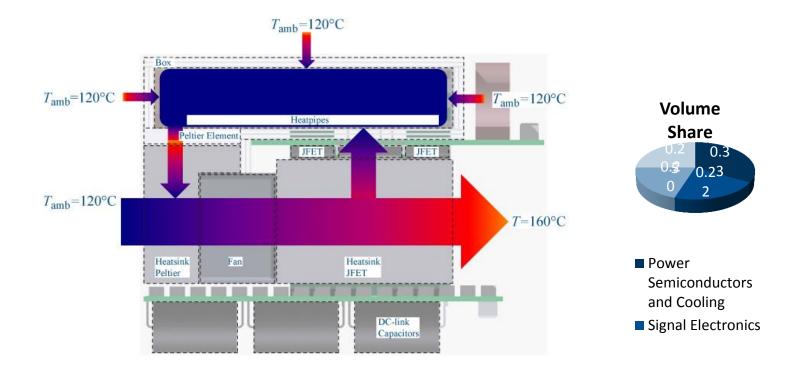

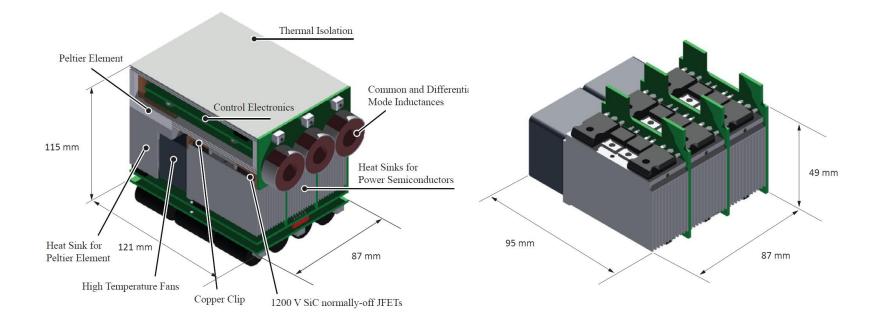

# High Temperature (I)

Special Components with Significantly Increased Cost and Derated Performance

#### 120°C Ambient Air Cooled Automotive Inverter

# High Temperature (II)

#### Thermal Concept of Inverter System

ECPE Roadmap 2025 Workshop

# High Temperature (III)

Missing HT Package (Reliability)

Missing HT Sensors & Control Electronics & Fans etc.

ECPE Roadmap 2025 Workshop

#### Power Semiconductors Load Cycling Capability

New Die Attach Technologies, e.g. Low-Temperature Sinter Technology

### Observation

— SiC... Not Yet a "Killer" TechnologyFuture:U > 1.7 kV— GaN (!)... Cost AdvantageOnly forU < 600V in  $1^{\text{st}}$  Step

(

- Do Not Forget the Continuous Improvement of Si Devices (!)

- System Level Adv.e of SiC Still to be Clarified (More Basic Topologies, Smaller Passives)

- SiC for High Efficiency (e.g. for PV or for High Power Density / Low Cooling Effort)

**Example: Efficiency Optimization**

#### ■ "Flat" Optima for Practical (Robust) Systems → Good Engineering – Similar Result

Power Elect Laboratory

**Power Electronic Systems**

Virtual Prototyping

- Reduces Time-to-Market

- More Application Specific Solutions (PCB, Power Module, and even Chips)

- Only Way to Understand Mutual Dependencies of Performances / Sensitivities

- Simulate What Cannot Any More be Measured (High Integration Level)

#### **Resulting Research Topics**

≻

### Potential Research Topics

- **Components** -

- Converters

- **Systems**

- WBG

- Interconnections

- Packaging

- MF Insulation

- Cooling Concepts

- Active Gate Control

- Magn. Flux Meas.

- Acoustic Noise of Mag. Comp.

- Wireless Sensing / Monitoring.

- etc.

- Integration

- → Benchmark SiC / GaN  $\rightarrow$  High Frequ. / High Curr.

- $\rightarrow$  Low Ind. MV Package

- $\rightarrow$  Partial Discharge@MF

- $\rightarrow$  Airbearing Cooler etc.

- $\rightarrow$  d/dt Feedback and u,i-Limit

- $\rightarrow$  Magnetic Ear

- $\rightarrow$  Influence of DC Magn.

- $\rightarrow$  Wireless Voltage Probe

- → Inductor/Transformer

- $\rightarrow$  Interph. Transf., Coupl. Ind.

- $\rightarrow$  CM/DM EMI Filter  $\rightarrow$  RB<sup>-</sup>, RC-IGBTs

- \* Semicond.

\* Magnetic

- \* Power &

- Information

- Hybridization \* Act./Passive  $\rightarrow$  Hybrid Filters / SSTs etc.

- More Oriented to Spec. Application

- Important but Mostly Incremental

#### Potential Research Topics

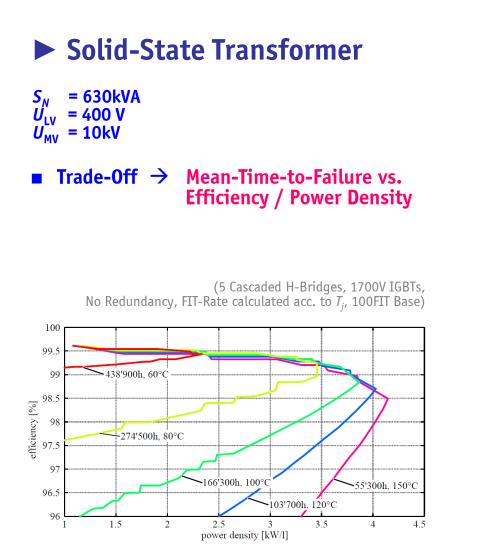

Components - New Topologies & Modularization **Converters** \* MV/MF DC/DC  $\rightarrow$  Const. V-Transf. Ratio **Systems** \* MV-Connect.  $\rightarrow$  Inp. Series / Outp. Parall.  $\rightarrow$  Series Conn. of Switches  $\rightarrow$  Aux. Supplies \* Extr. Conv. Ratio \* Extr. Efficiency  $\rightarrow$  Datacenters / DC Distr. \* High Curr.  $\rightarrow$  Parallel Operat. of Conv. \* High Pressure  $\rightarrow$  Subsea Appl.  $\rightarrow$  Supply & Filtering etc. \* Integr. of Funct. \* Fault Tolerance - Control → Traction/Ship/Aircraft/Subsea \* Distr. Conv. Syst.  $\rightarrow$  Circul. Curr. / CM Curr. etc. \* Parasitic Curr. \* Highly Dyn. Conv.  $\rightarrow$  High Bandw., incl. Res. Conv. - Comp. Evaluation \* Multi-Objective  $\rightarrow$  Cost Models  $\rightarrow$  Reliability / Lifetime Models  $\rightarrow$  Circ. / Magn. Models  $\rightarrow$  Interact. Opt. Tools More Oriented to Spec. Application

#### Potential Research Topics

- ComponentsConverters

- **Systems**

#### Systems incl. Hybrid Systems

- Converter & Load - Power & Inf.

- Hydraulic/El. Wireless Power

- etc.

- $\rightarrow$  Losses Conv. vs. Machine

- $\rightarrow$  Smart Houses

- $\rightarrow$  Smart Batteries etc.

- $\rightarrow$  Hybrid Cranes/Constr. Mach.  $\rightarrow$  Ind. Power Transfer incl. Inf.

#### **Important** → Large Future Potential !

ECPE Roadmap 2025 Workshop

← "Optimistic" View

Barriers can be Shifted, New Converter Technologies etc.

## \_ "Pessimistic" View \_\_\_\_

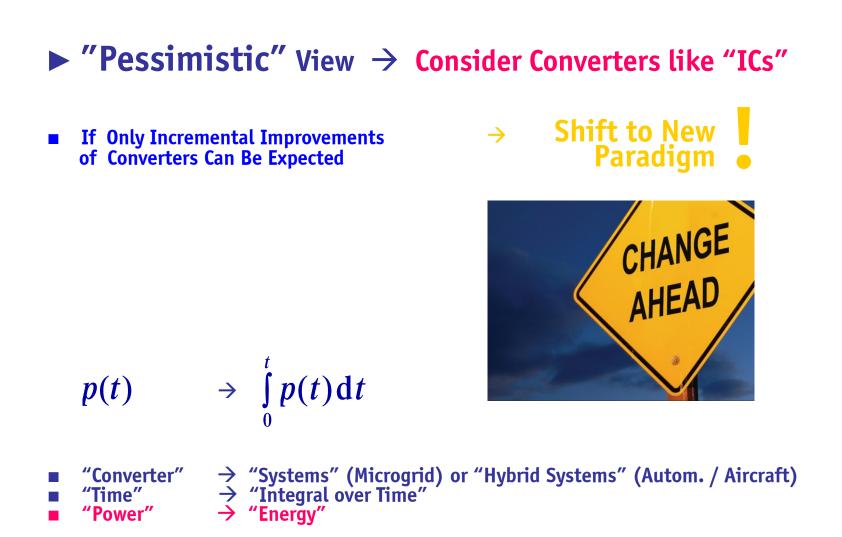

## ► "Pessimistic" View → Consider Converters like "ICs"

If Only Incremental Improvements of Converters Can Be Expected

→ Shift to New Paradigm

# **p(t)**

- Cap. Filtering

- etc.

- Power Conversion  $\rightarrow$  Energy Management / Distribution

$\rightarrow \int_{n}^{t} p(t) \mathrm{d}t$

- Converter Analysis → System Analysis (incl. Interactions Conv. / Conv. or Load or Mains)

Converter Stability → System Stability (Autonom. Cntrl of Distributed Converters)

- → Energy Storage & Demand Side Management

- Costs / Efficiency  $\rightarrow$  Life Cycle Costs / Mission Efficiency / Supply Chain Efficiency

**Power Electronic Systems** Laboratory

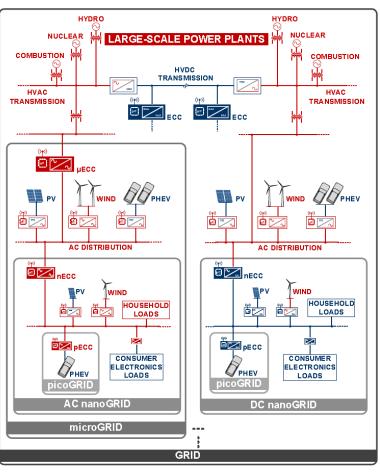

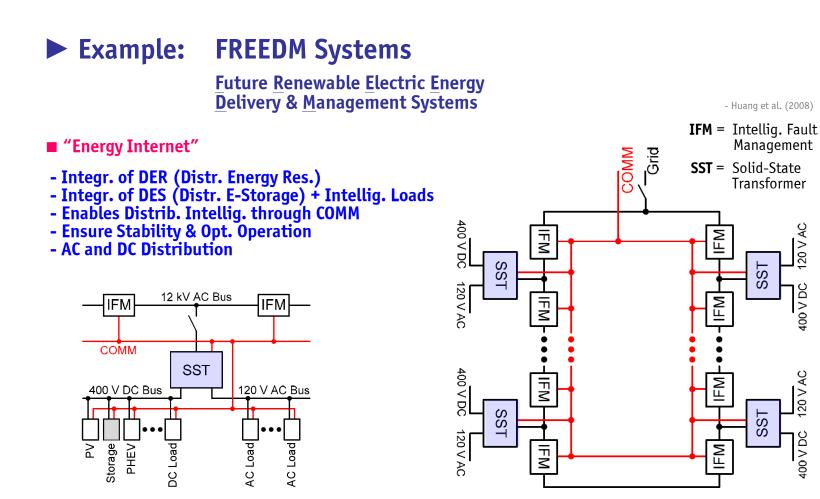

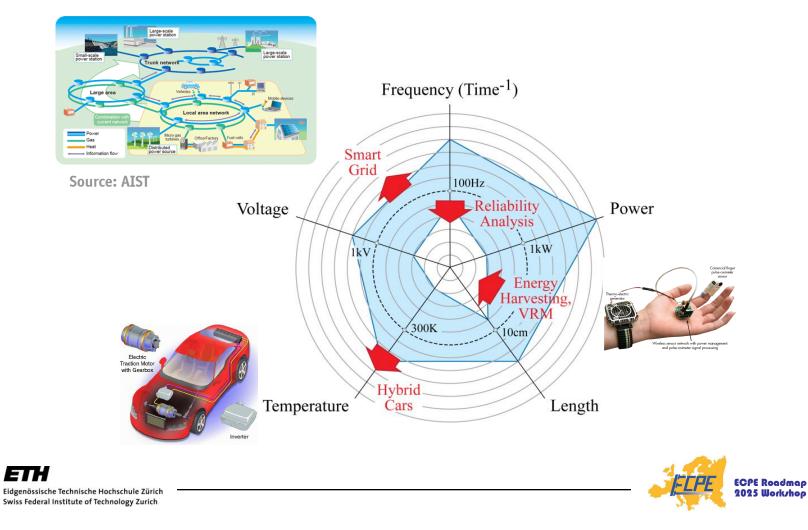

#### **Example:** Smart Grid

- Borojevic (2010)

- Hierarchically Interconnected Hybrid Mix of AC and DC Sub-Grids

- Distr. Syst. of Contr. Conv. Interfaces

- Source / Load / Power Distrib. Conv.

- Picogrid-Nanogid-Microgrid-Grid Structure

- Subgrid Seen as Single Electr. Load/Source

- ECCs provide Dyn. Decoupling

- Subgrid Dispatchable by Grid Utility Operator

- Integr. of Ren. Energy Sources

- ECC = Energy Control Center

- Energy Routers

- Continuous Bidir. Power Flow Control

- Enable Hierarchical Distr. Grid Control

- Load / Source / Data Aggregation

- Up- and Downstream Communic.

- Intentional / Unintentional Islanding for Up- or Downstream Protection

- etc.

#### ■ Bidirectional Flow of Power & Information / High Bandw. Comm. → Distrib. / Local Autonomous Cntrl

**Power Electronic Systems** Laboratory

ECPE Roadmap 2025 Workshop

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

#### Power Electronics <u>Systems</u> Performance Figures/Trends

**Power Electronic Systems** Laboratory

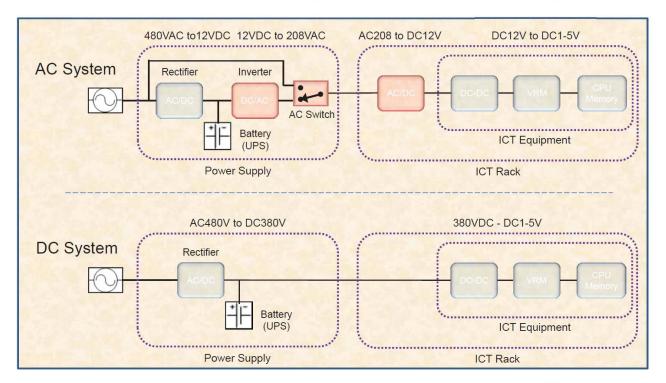

# AC vs DC Power Systems for Data Centers

Reduce Loss, Footprint; Improve Reliability, Power Quality

© 2011 EMerge Alliance

#### Possible Future Extensions of Power Electronics Systems Applications

90/102

#### Remarks on University Research \_\_\_\_\_

ETTH Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

$\rightarrow$

**General Observations**

- Gap between Univ. Research and Industry Needs In Some Areas Industry Is Leading the Field —

- \_\_\_\_

#### Gap between Univ. Research and Industry Needs

3. Costs

- Industry Priorities 1. Costs 2. Costs

- Multiple Objectives ...

- Low Complexity

Modularity / Scalability

- Robustness

- Ease of Integration into System

- Basic Discrepancy !

Most Important Industry Variable, but **Unknown Quantity to Universities**

In Some Areas Industry Is Leading the Field !

- Industry Low-Power Power Electronics (below 1kW) Heavily Integrated PCB Based Demonstrators Do Not Provide Too Much Information (!) Future: "Fab-Less" Research

- Same Situation above 100kW (Costs, Mech. Efforts, Safety Issues with Testing etc.)

- Talk AND Build Megawatt Converters (!)

Establish (Closer) University / Industry (Technology) Partnerships

Establish Cost Models, Consider Reliability as Performance

## University Education Orientation

#### Need to Insist on High Standards for Education

- Introduce New Media \*

- Show Latest Stat of the Art (requires New Textbooks) \*

- \*

- Interdisciplinarity Introduce New Media (Animation) Lab Courses! \*

- \*

- → The Only Way to Finally Cross the Borders (Barriers) to Neighboring Disciplines !

ECPE Roadmap

Finally, ...

#### Power Electronics 2.0

ETTH Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

$\rightarrow$

# **Power Electronics 2.0**

#### **New Application Area**

**Paradigm Shift**

**Enablers / Topics**

- Smart XXX (Integration of Energy/Power & ICT)

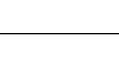

- Micro-Power Electronics (VHF, Link to Microelectronics)

- MEGA-Power Electronics (MV, MF)

- From "Converters" to "Systems"

- From "Inner Function" to "Interaction" Analysis

- From "Power" to "Energy" (incl. Economical Aspects)

- New (WBG) Power Semiconductors (and Drivers)

- Adv. Digital Signal Processing (on all Levels Switch to System)

PEBBs / Cells & Automated (+ Application Specific) Manufaturing

- Multi-Cell Power Conversion

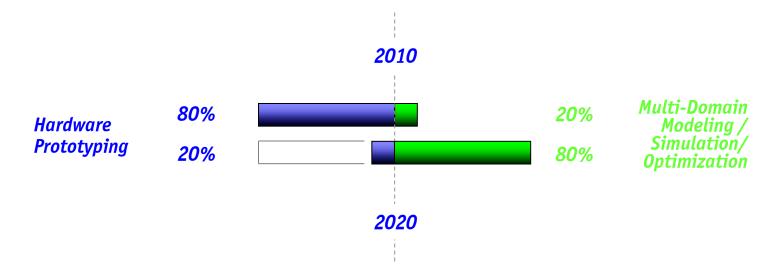

- Multi-Domain Modeling / Multi-Objective Optim. / CAD

- Cybersecurity Strategies

**Power Electronic Systems** Laboratory

But, to get there we must ...

# "Bridge the Gaps"

- Univ. / Ind. Technology Partnerships

Power Electronics + Power Systems

- Vertical Competence Integration (Multi-Domain)

Comprehensive Virtual Prototyping (Multi-Objective)

- Multi-Disciplinary / Domain Education

# **Thank You !**

# **Questions ?**