ECPE Roadmap 2025 Workshop

Munich, March 26, 2015

# **Roadmap Power Electronics 2025**

J.W. Kolar / E. Hoene\* / Th. Harder\*\*

Swiss Federal Institute of Technology (ETH) Zurich \* Fraunhofer IZM, Berlin \*\* ECPE, Nuremberg

## Summary of 1<sup>st</sup> Roadmap Team Meeting

- → Magnetic Components are the Highest Cost Factor in Power Supplies

- → EMI and Semiconductor Oscillations are #1 Risk for Time to Market

- → Robustness is Often More Important than Reliability

- → Modularity Made it Never Into the Market

- $\rightarrow$  External Manufacturing Results in Too High Costs

- → Only 6-8 Weeks Development Time Requires Finished Building Blocks

- $\rightarrow$  Need for Fast Simulation Models

- → Digital Control Issues (Safety Requirements / Redundancy)

- → Efficiency is also a Political Issue / Depends on Standardization

- → Efficiency is not a Selling Argument (only for Last Person in Supply Chain)

- → Ranking: Costs / Reliability / Ease of Manufacturing / Robustness

### $\rightarrow$ Some Challenges / Limitations Identified

Jan. 2014

## Summary of 2<sup>nd</sup> Roadmap Meeting

### ... see Summary presented by Th. Harder

ECPE Roadmap 2025 Workshop

## Summary of 3<sup>rd</sup> Roadmap Team Meeting

- → 2025 Performance Target Values

- → Evaluation of Current Research Level Technologies

- → Enabling Technologies

- $\rightarrow$  Technology / Research Gaps

### ... see Following Summary

**Key Performance Indices** which Must be Considerably **Improved until 2025**

- $\rightarrow$  Costs

- $\rightarrow$  Power Density

- $\rightarrow$

- Efficiency Reliability / Robustness Time-to-Market

4/34

$\rightarrow$

# Main Components / Concepts / Processes Determining the Performance Limits

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

2025 Workshop

Ston #1

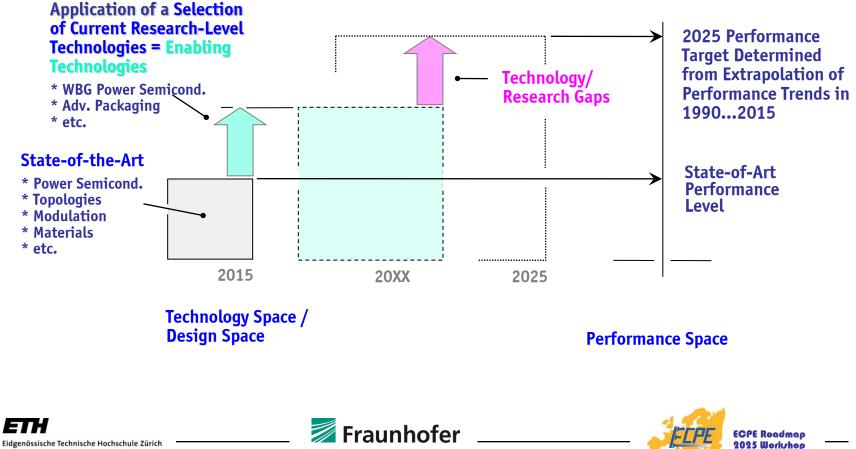

## **Roadmap Approach**

|         | Consid                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------|

| Step #2 | <ul> <li>→ Curre</li> <li>→ High</li> <li>→ High</li> <li> Consider</li> <li>Order</li> <li>of a S</li> </ul> |

| Step #3 | → <b>"Enat</b><br>Select                                                                                      |

Step #4

#### **Define 2025 Performance Targets** $\rightarrow$ dering Past Trend Lines

## ent Research Level Technologies

- **Switching Frequency Operating Temperature**

- dered for Each Component in to Check for Potential Improvements elected Performance Index

### bling Technologies"

ted Subset of "Current Research Technologies" which Potentially Enable a **Considerable Performance Improvement**

## $\rightarrow$ "Technology / Research Gaps"

... Technologies Crucial for Reaching the 2025 Performance Target but Currently Not Considered in Research

ECPE Roadman

Swiss Federal Institute of Technology Zurich

## Roadmap Approach

\_\_\_\_

IZM

## General Remark

- → Pragmatic Approach

- → Only Already Known Research Concepts are Considered

- → No Speculations on Unknown Disruptive Concepts (e.g. Nanomaterials)

- → Identified Barriers are Indicating Future Research Needs

- → Trivial Requirements (e.g. Higher Energy Density of Caps) are not Listed

#### **Power Density** - Expected Impr. until 2025 - Factor 2 ... 5 (10) **Filter Components** ( $\rightarrow$ Minimize Volume) $\rightarrow$ Increase Switching Frequency **Challenges:** \* Higher Switching Losses \* Higher HF Losses of Passives / Thermal Managmnt \* Increased EMI Noise (for Hard Switching) \* Low Switching Loss WBG Semiconductors **Enablers:** \* Adv. Inductor Concepts (e.g. Distributed Gaps) \* Adv. Packaging – Min. Parasitics (Gate & Power) \* ZVS / Resonant Converter Concepts \* High Clock Frequency Digital Control \* Maq. Materials (Permeability /Losses at HF) **Barriers:** \* Conductor Types / Winding Arrangements \* Thermal Management \* Adv. Design Tools (Layout, Magnetics) \* Adv. Measurem. Tools Integrated with Simulation \* Engineering Experience \* Interleaving for Frequency Multiplication **Detour: Remark:** \* Only Basic Converter Topologies are of Interest are Taken from the List of "Current Research Technologies" $\rightarrow$ "Enablers" $\rightarrow$ "Barriers" are Indicating "Technology Gaps"

| ightarrow Increase Operating Temp.   | Challenges: | <ul> <li>* Reliability of Interconnection Technologies</li> <li>* Higher Losses</li> </ul>                                                                                       |

|--------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | Enablers:   | <ul> <li>* High Temperature Passive Components</li> <li>* Interconnection Technologies for Higher Temp.</li> <li>* WBG Semiconductors</li> </ul>                                 |

|                                      | Barriers:   | * Requirement to Enable all Used Components and<br>Technologies for High Temp.                                                                                                   |

|                                      | Remark:     | * Especially Effective for High Temp. Environment                                                                                                                                |

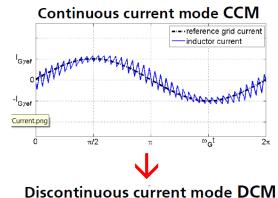

| $\rightarrow$ Change from CCM to DCM | Challenges: | * Higher Conduction Losses<br>* Higher Filtering Effort                                                                                                                          |

|                                      | Enablers:   | <ul> <li>* Low On-Resistance Power Switches (CoolMOS, WBG)</li> <li>* Advanced Digital Control</li> <li>* Interleaving for Red. of Filter Effort</li> </ul>                      |

|                                      | Barriers:   | <ul> <li>* New Circuit Topologies / Modulation Schemes</li> <li>* Magnetic Materials (High Flux Swing, High Frequ.)</li> <li>* Conductor Types / Winding Arrangements</li> </ul> |

| $\rightarrow$ etc., etc.             | Remark:     | * Only Basic Conv. Topologies with Modified Control /<br>Min. Auxiliary Circuits are of Interest                                                                                 |

| ■ EMI Filter (→ Minimize Volume)                  |                                                  |

|---------------------------------------------------|--------------------------------------------------|

| ightarrow Increase Switching Frequ. Beyond 500kHz | Challenges:<br>Enablers:<br>Barriers:<br>Remark: |

$\rightarrow$  etc., etc.

••••

....

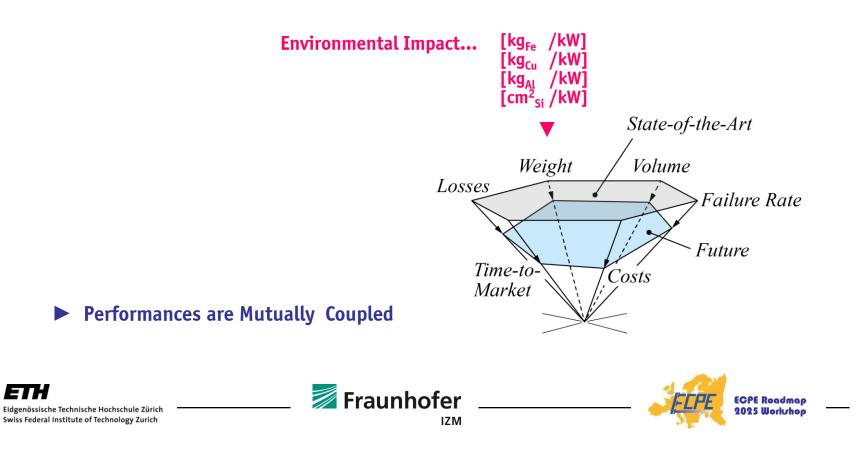

# Efficiency

- Expected Loss Reduction until 2025 Factor 2 ... 3

- Evaluation of Contributions to Loss Reduction of the Main Components Employing Current Research Level Technologies

Utilized Current Research ConceptsRequired Additional New Technologies

- $\rightarrow$  Switching Circuit and Gate Drive

- $\rightarrow$  Transformers

- → Filter Components

- → EMI Filter Components

- $\rightarrow$  Heatsink

- $\rightarrow$  Interconnections

- $\rightarrow$  Sensors

- $\rightarrow$  Control Circuit

- Enabling Technologies

- Technology Gaps

# Costs

- Expected Reduction until 2025 Factor ... 2

- Evaluation of Contributions to Loss Reduction of the Main Components Employing Current Research Level Technologies

Utilized Current Research ConceptsRequired Additional New Technologies

- $\rightarrow$  Switching Circuit and Gate Drive

- → Transformers

- → Filter Components

- → EMI Filter Components

- $\rightarrow$  Heatsink

- $\rightarrow$  Interconnections

- $\rightarrow$  Sensors

- $\rightarrow$  Control Circuit

- Enabling Technologies

- Technology Gaps

ECPE Roadmap 2025 Workshop

IZM

#### 14/34

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

IZM

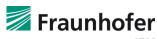

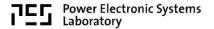

Enabling Technologies (2)

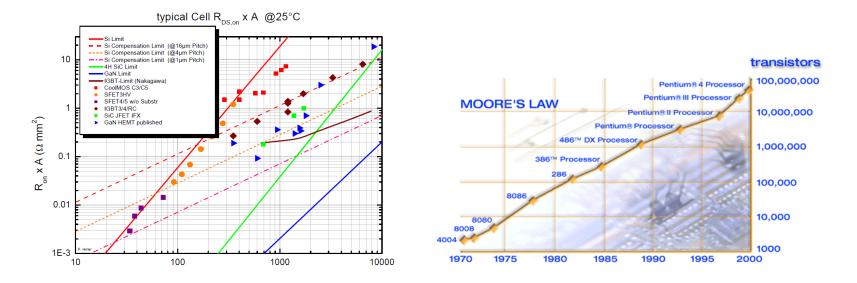

- → Wide Bandgap Semiconductors \* Low Switching Losses

- \* Low Conduction Losses

- $\rightarrow$  Next Generation (LV) Si Semiconductors

- \* Low Conduction Losses

### Enabling Technologies (3)

- → Adv. Packaging of Power Semicond (Chip Scale etc.) \* Low Power Path Parasitics

- \* Low Gate Drive Parasitics

- \* Low Coupling of Power and Gate Drive Path

- \* Low Thermal Resistance

- \* 3D Interconnection

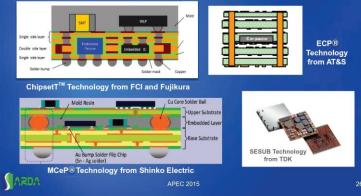

- \* PCB Embedding (incl. Therm. Management)

- \* Minimizing DM and CM EMI (Integr. Switch. Cell)

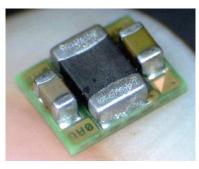

**Ultra Low Inductance Package**

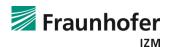

DC/DC Converter with Embedded Chip

## **Enabling Technologies (4)**

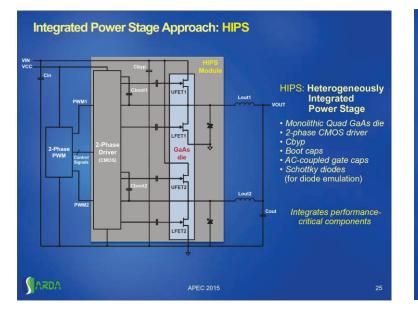

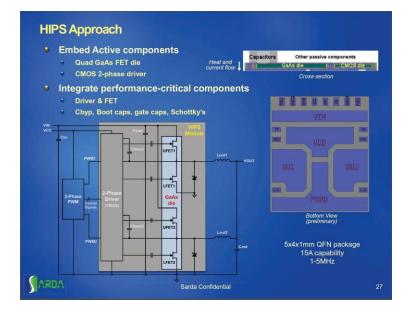

- → Heterogeneous Integration

- \* Switching Cell in a Package \* Drivers with Integrated Power Supply \* DC/DC Converter in a Package

X-Ray Image (Video)

## Enabling Technologies (5)

$\rightarrow$  Heterogeneous Integration

- Enabling Technologies (6)

- $\rightarrow$  Heterogeneous Integration

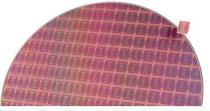

Information Processors Are Sawn Out of Scalable Wafers

ChiP Power Components Are Sawn Out of Scalable Magnetic Panels

ECPE Roadmap 2025 Workshop

## Enabling Technologies (7)

## $\rightarrow$ Heterogeneous Integration

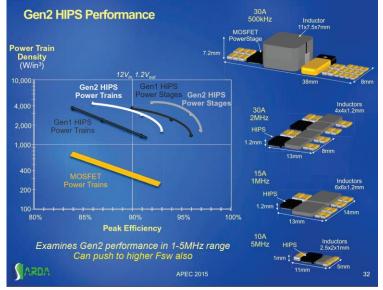

### Presented @ APEC 2015

## Enabling Technologies (8)

## $\rightarrow$ Heterogeneous Integration

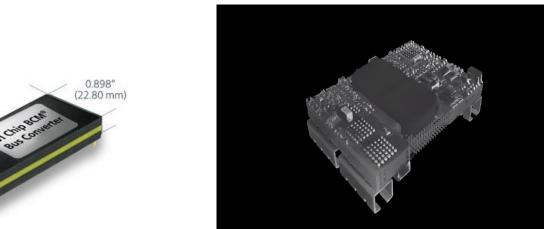

#### **HIPS Module** Available technology to enable compact multi-chip HIPS module: **Embedded Die in Substrate**

Two motivations: (1) Performance (minimize parasitics for multi-MHz operation) (2) PowerStage package size

### Presented @ APEC 2015

## Enabling Technologies (9)

## → Heterogeneous Integration

### Presented @ APEC 2015

## Enabling Technologies (10)

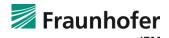

- $\rightarrow$  Adv. Inductor Concepts

- \* Magnetic Integration (CM/DM)

- \* Multi-Gapped Magnetic Cores

- \* Constant Flux Density Magnetic Cores

- \* Integrated Cooling

- \* Parasitic Capacitance Cancellation

- \* 3D Interconnection

#### $\rightarrow$ Adv. Capacitor Concepts \* Low Parasitic Ind. 3D Interconnection

\* Integrated Cooling / High Current Concepts

#### $\rightarrow$ Adv. Component Interconnection Concepts \* Low DC and HF Loss Interconnection

\* Integrated Concepts (Cooling, Sensing)

### $\rightarrow$ Adv. Cooling Concepts

- \* Heat Spreading Concepts

- \* Two-Side Cooling

- \* Two Phase Cooling

- \* Integr. Concepts (El. and Thermal Interconn.)

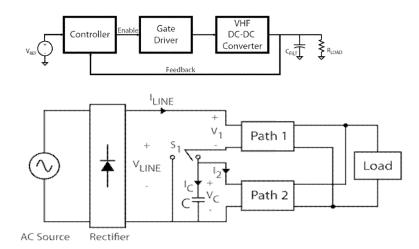

#### $\rightarrow$ Adv. Low Frequency Energy Buffer Concepts \* Replace Electrolytic Cap. by Conv. And High ∆v Cap.

- Enabling Technologies (11)

- $\rightarrow$  Advanced Inductor Concepts

ETH Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

## Enabling Technologies (12)

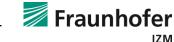

→ Digital Control (Moores Law)

- \* High Calc. Capability / Monitoring / Adv. Control

- \* High Clock Rates / High Sampling Frequ.

- $\rightarrow$  Change from CCM to DCM Operation

- \* DCM Inductors Store Less Energy / Lower Vol.

- \* Facilitates ZVS / Res. Transition Operation

- \* Workaround for Slow Passives Improvement

- \* i=0 Instead of Cont. Current Sensor

- $\rightarrow$  Advanced Modulation

- \* Noise Shaping Variable Switching Freugnecy

- $\rightarrow$  Active ZVS / Resonant Operation

- \* Low Switching Losses

- \* Low EMI / No Free Ringing

- → Interleaving / Multi-Cell / Multi-Level Converters

- \* Increase of Effective Switching Frequency

- \* Cancellation (DM-CM Transfer) instead of Filtering

- $\rightarrow$  Advanced Control

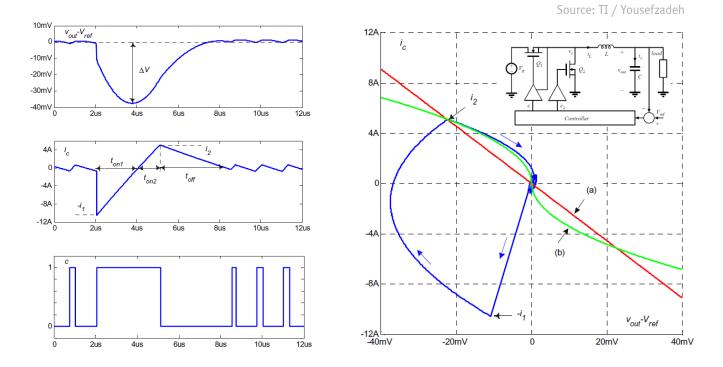

- \* Trajectory-Based Control

- \* Predictive Control

ECPE Roadmap 2025 Workshop

## **Enabling Technologies (13)**

#### Bringing Together Advanced Circuit Concepts / Semiconductors / Packaging $\rightarrow$

\* World Smartest Laptop Charger

\* World Smallest Laptop Charger

## Enabling Technologies (14)

## → Bringing Together Advanced Circuit Concepts / Semiconductors / Packaging

\* World Smallest Laptop Charger

## Enabling Technologies (15)

## $\rightarrow$ Predictive Control and Optimal Trajectory Control

**Consider Individual Switching Instants vs. Average over Numerous Swiching Cycles**

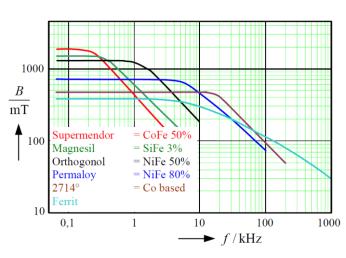

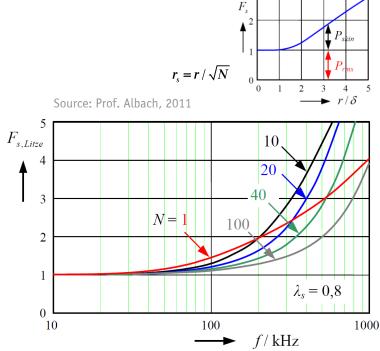

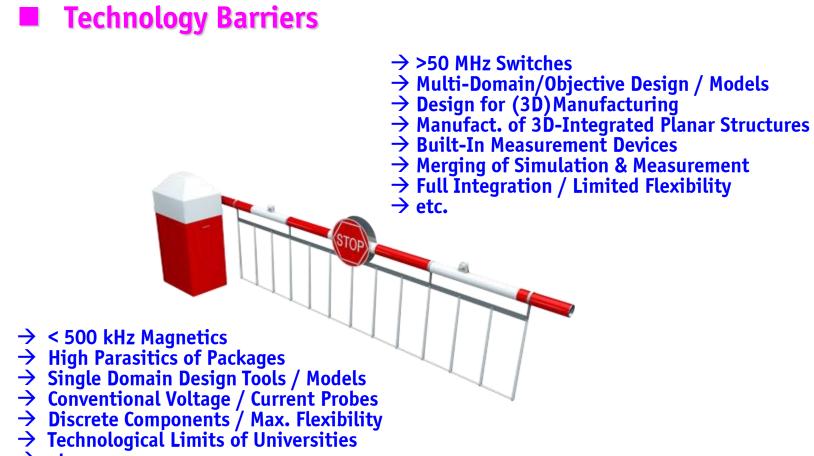

## **Technology Barriers**

- **Example: Serious Limitation of Operating Frequency by HF Losses**

- Core Losses (incr. @ High Frequ. & High Operating Temp.) Temp. Dependent Lifetime of the Core Skin-Effect Losses

- **Proximity Effect Losses**

Adm. Flux Density for given Loss Density

Skin-Factor F<sub>s</sub> for Litz Wires with N Strands

- $\rightarrow$  etc.

- Chicken & Egg Problem of New Technologies / Identification of Killer Applications

## Example of Advanced Power Electronics Design Platform

**3D-Electromagn. 3D-Thermal Fast Circuit Parasitics** Simulator FEM Extraction Solver **HF Magnetics EMC** Filter Reliability Heatsink Design Design Analysis Design Toolbox Toolbox Toolbox Toolbox Post Processing **Design Metrics Calculation**

Input Topology | Device Models | Control Circuit | 3D-Geometry | Materials

- Modeling & Design

- Circuit Simulation

- Thermal Simulation

- EM Simulation

# Summary (1)

- WBG Semiconductor Technology Microelectronics (Moore's Law)

- Adv. Design / Adv. Packaging (Manufacturing) / Adv. Measurement

## $\rightarrow$ Enabling an up to Factor of 10 Performance Improvement

ECPE Roadmap 2025 Workshop

# Summary (2)

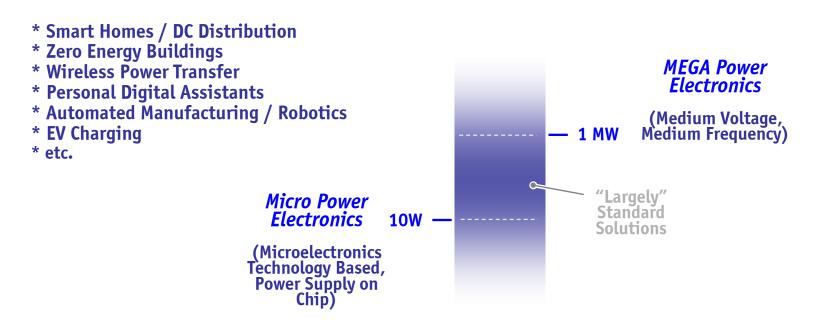

Considerable Future Extension of Power Electronics Application Area

- Bridge to Power Systems

- Establish (Closer) University / Industry (Technology) Partnerships

- Establish Cost Models, Consider Reliability as Performance

# Thank you!