# Google Little-Box Reloaded

#### Advances In Ultra-Compact GaN Based Single-Phase DC/AC Power Conversion

#### **Dominik Neumayr**

Swiss Federal Institute of Technology (ETH) Zurich Power Electronic Systems Laboratory www.pes.ee.ethz.ch

## **Google Little-Box Reloaded**

#### **Advances In Ultra-Compact GaN Based Single-Phase DC/AC Power Conversion**

D. Neumayr, D. Bortis, M. Guacci, J. Azurza, J. W. Kolar

Swiss Federal Institute of Technology (ETH) Zurich Power Electronic Systems Laboratory www.pes.ee.ethz.ch

#### **Outline**

- ► Google Little Box Challenge

- Requirements

Little Box 1.0

- **Further Analysis & New Approach**

- New Circuit Topology

- Adv. Measurement Techniques

- Little Box 2.0

- Conclusions

M. Kasper 0. Knecht F. Krismer

Acknowledgement

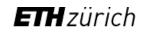

### Google Little Box Challenge

Requirements Little Box 1.0 Other Finalists

- Design / Build the 2kW 1-OSolar Inverter with the Highest Power Density in the World

- Power Density > 3kW/dm<sup>3</sup> (50W/in<sup>3</sup>)

- Efficiency > 95%

- Case Temp. < 60°C

- EMI FCC Part 15 B

■ Push the Forefront of New Technologies in R&D of High Power Density Inverters

### **The Grand Prize**

- Highest Power Density (> 50W/in<sup>3</sup>)

Highest Level of Innovation

- Timeline

- Challenge Announced in Summer 2014

2000+ Teams Registered Worldwide

100+ Teams Submitted a Technical Description until July 22, 2015

- 18 Finalists (3 No-Shows)

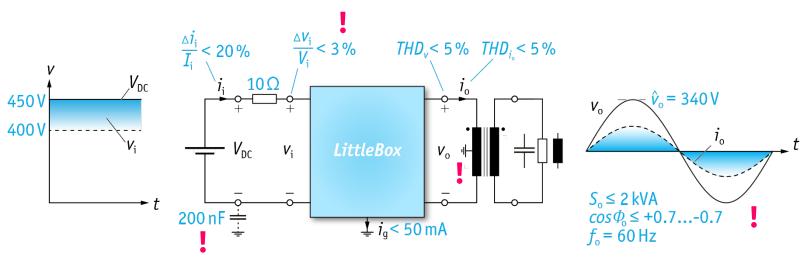

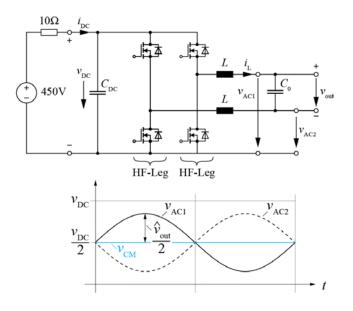

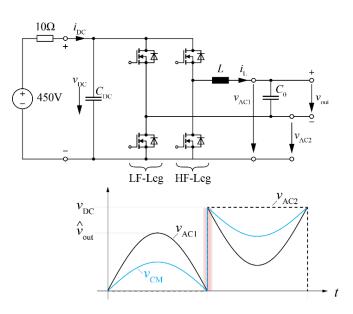

## **Selected Converter Topology**

- Full-Bridge Output Stage

- Modulation of Both Bridge Legs

- DM Component of  $u_1$  and  $u_2$  Defines Output Voltage  $u_0$ No Low-Frequency CM Component of  $u_1$  and  $u_2$  (Different to e.g. 1- $\Phi$  PFC Rectifier Systems !)

4/92

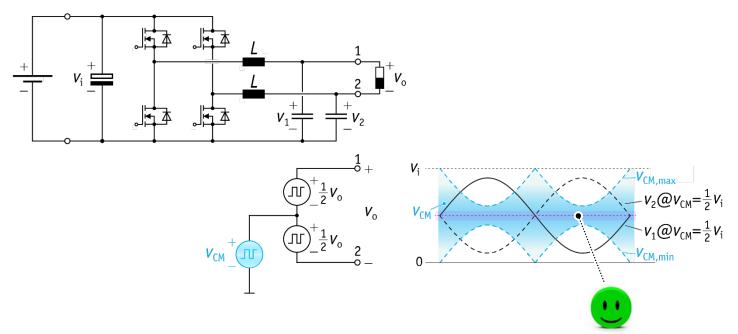

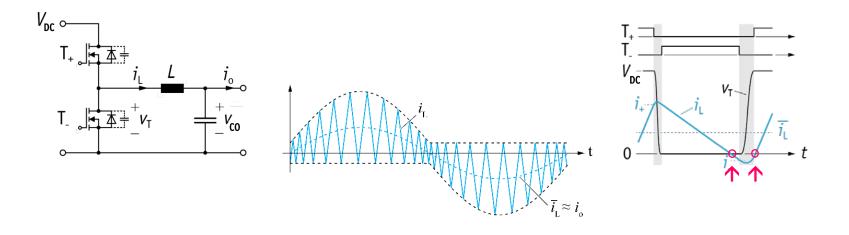

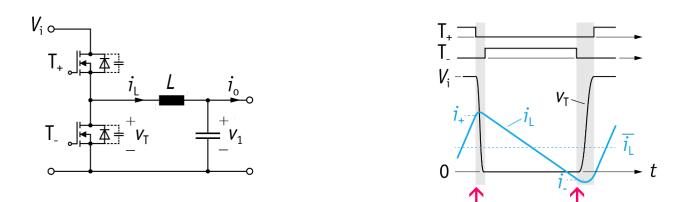

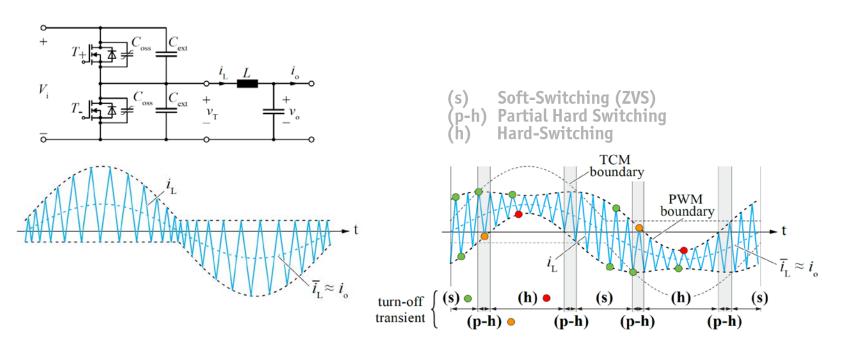

#### **Triangular Current Mode (TCM) ZVS Operation**

• TCM Operation for Resonant Voltage Transition @ Turn-On/Turn-Off

- Requires Only Measurement of Current Zero Crossings, i = 0High  $f_s$  Around i = 0 Challenging for Digital Control Variable Sw. Freq.  $f_s$  Lowers EMI

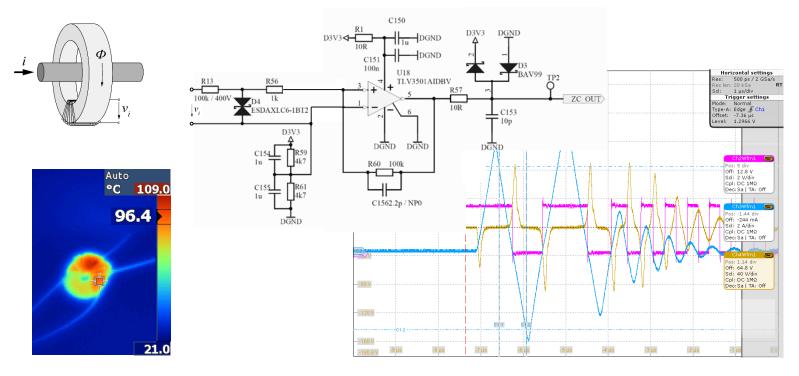

#### *i=0* Detection

• Saturable Inductor – Toroidal Core R4 x 2.4 x 1.6, EPCOS (4mm Diameter) – Core Material N30, EPCOS

Operation Tested up to 2.5MHz Switching Frequency

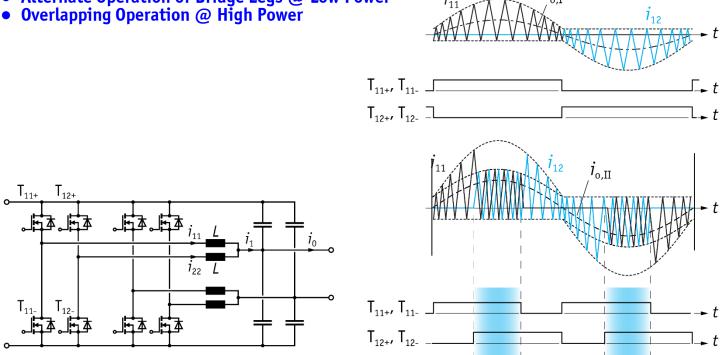

Interleaving of 2 Bridge Legs per Phase - Volume / Filtering / Efficiency Optimum

Interleaving in Space & Time - Within Output Period

Alternate Operation of Bridge Legs @ Low Power

• •

Opt. Trade-Off of Conduction & Switching Losses / Opt. Distribution of Losses

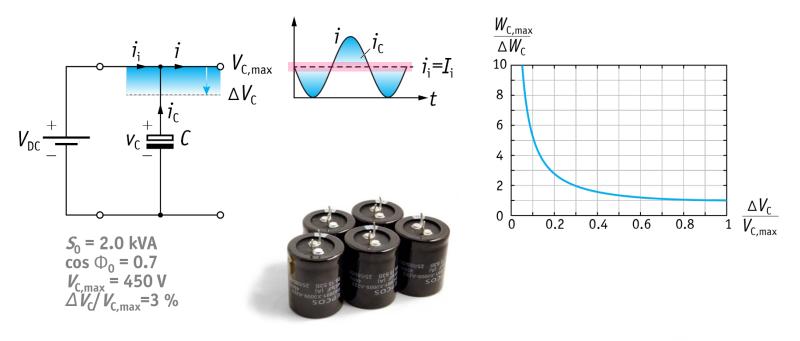

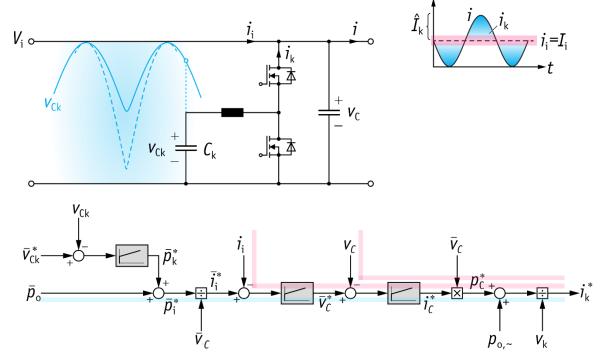

#### **DC-Side Passive Power Pulsation Buffer**

• Electrolytic Capacitor

**C** > 2.2mF / 166 cm<sup>3</sup>  $\rightarrow$  Consumes 1/4 of Allowed Total Allowed Volume !

8/92

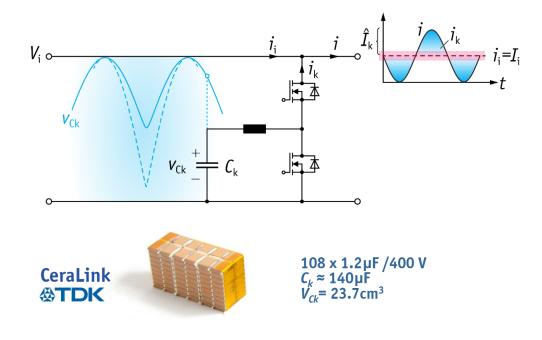

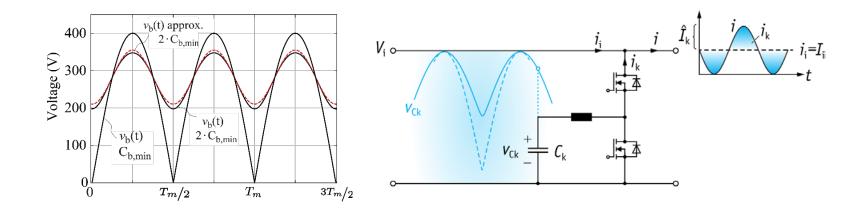

#### **DC-Side Active Power Pulsation Buffer**

- Large Voltage Fluctuation Foil or Ceramic Capacitor

- Buck-Type (Lower Voltage Levels) or Boost-Type DC/DC Interface Converter

Significantly Lower Overall Volume Compared to Electrolytic Capacitor

9/92

#### **DC-Side Active Power Pulsation Buffer**

• Cascaded Control Structure

- P-Type Resonant Controller

- Feedforward of Output Power Fluctuation

- Underlying Input Current  $(i_i)$  / DC Link Voltage  $(u_c)$  Control

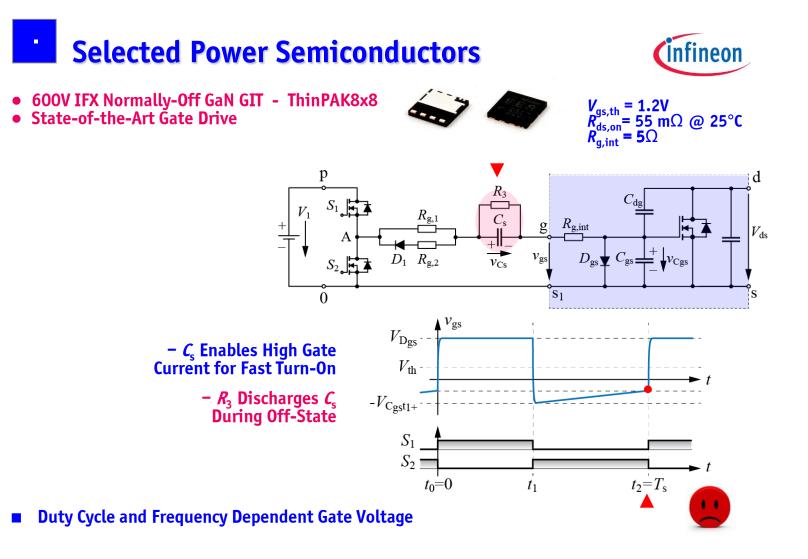

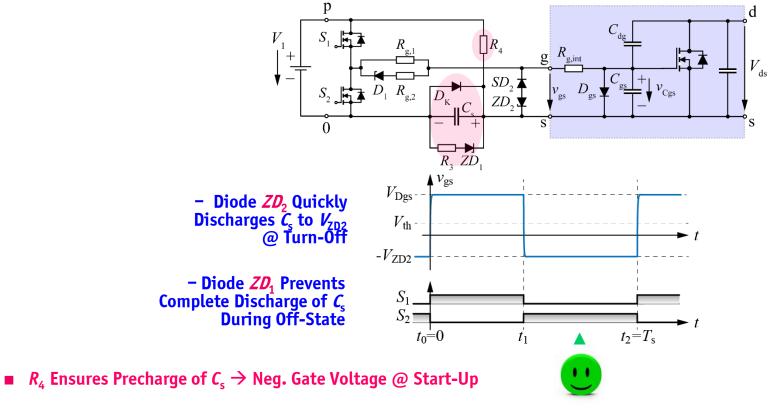

#### High dv/dt-Immunity Gate Drive

- Fixed Negative Turn-Off Gate Voltage Independent of Sw. Frequency and Duty Cycle

- Extreme dv/dt-Immunity (500 kV/µs) Due to CM Choke at Signal Isolator Input

- < 30ns Overall Prop. Delay

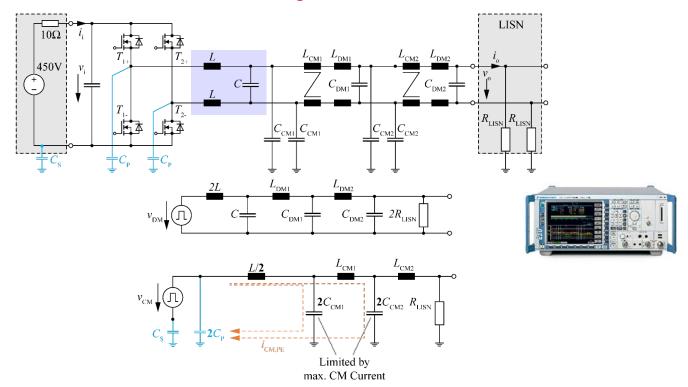

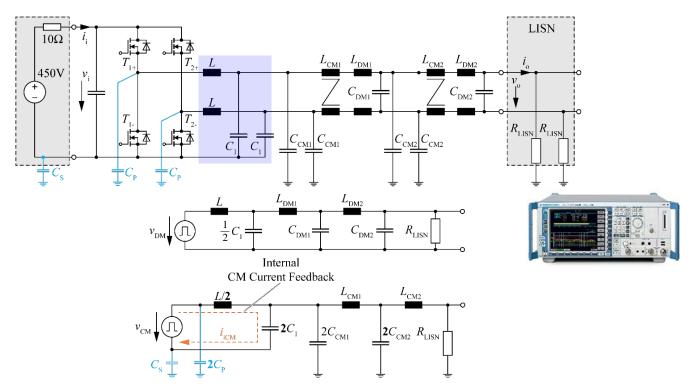

#### EMI Filter Topology (1)

• Conventional Filter Structure

- CM Cap. Limited by Earth Current Limit Typ. 3.5mA for PFC Rectifiers (GLBC: 5mA, later 50mA !)

- Large CM Inductor Needed Filter Volume Mainly Defined by CM Inductors

- Filter Structure with Internal CM Capacitor Feedback

- Filtering to DC- (and Optional to DC+)

- No Limitation of CM Capacitor  $C_1$  Due to Earth Current Limit  $\rightarrow \mu$ F Instead of nF Can be Employed

- Allows Downsizing of CM Inductor and/or Total Filter Volume

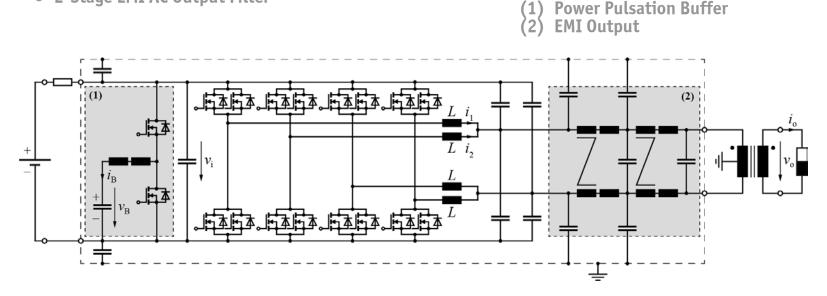

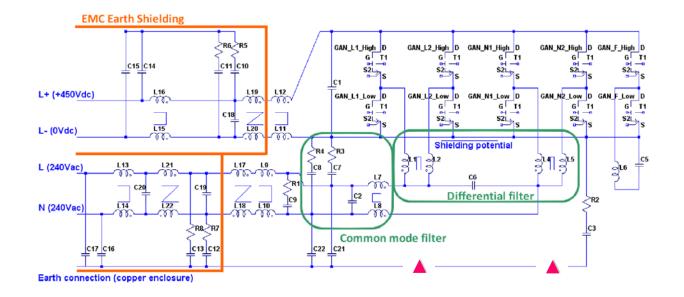

#### **Final Converter Topology**

- Interleaving of 2 Bridge Legs per Phase

- Active DC-Side Buck-Type Power Pulsation Buffer

- First Stage AC Filter Caps Connected to DC-

- 2-Stage EMI AC Output Filter

- ZVS of All Bridge Legs @ Turn-On/Turn-Off in Whole Operating Range (4D-TCM-Interleaving) Heatsinks Connected to DC Bus / Shield to Prevent Cap. Coupling to Grounded Enclosure

**Power Electronic Systems** Laboratory

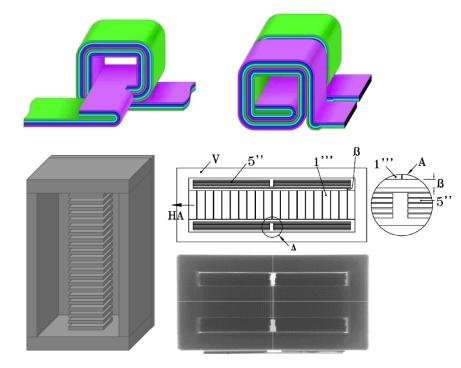

#### **High Frequency Inductors (1)**

- Multi-Airgap Inductor with Multi-Layer Foil Winding Arrangement Minim. Prox. Effect

- Very High Filling Factor / Low High Frequency Losses Magnetically Shielded Construction Minimizing EMI

- Intellectual Property of F. Zajc / Fraza

- L= 10.5µH

- 2 x 8 Turns

- 24 x 80µm Airgaps

- 24 x 80µm Alrgaps

Core Material DMR 51 / Hengdian

0.61mm Thick Stacked Plates

20 µm Copper Foil / 4 in Parallel

7 µm Kapton Layer Isolation

20mΩ Winding Resistance / Q≈600

Terminals in No-Leakage Flux Area

Dimensions - 14.5 x 14.5 x 22mm<sup>3</sup>

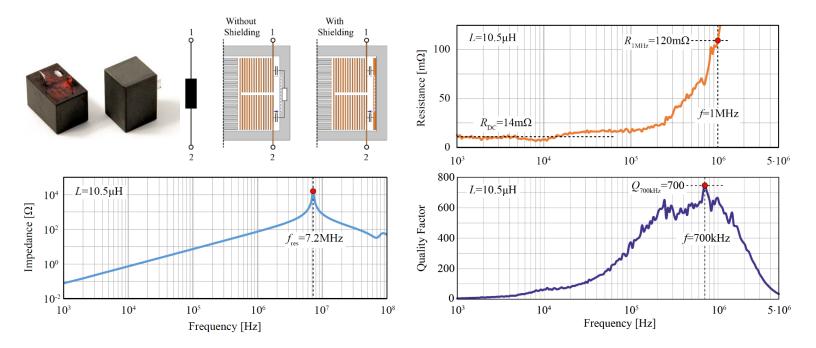

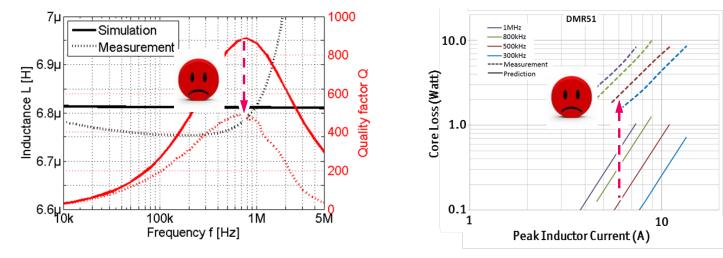

#### **High Frequency Inductors (2)**

**公TDK**

- High Resonance Frequency → Inductive Behavior up to High Frequencies

Extremely Low AC-Resistance → Low Conduction Losses up to High Frequencies

- High Quality Factor

**Shielding** Eliminates HF Current through the Ferrite  $\rightarrow$  Avoids High Core Losses Shielding Increases the Parasitic Capacitance

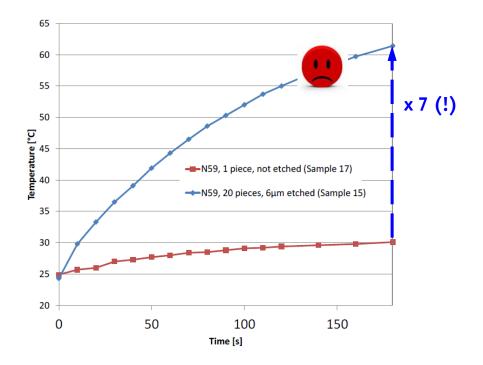

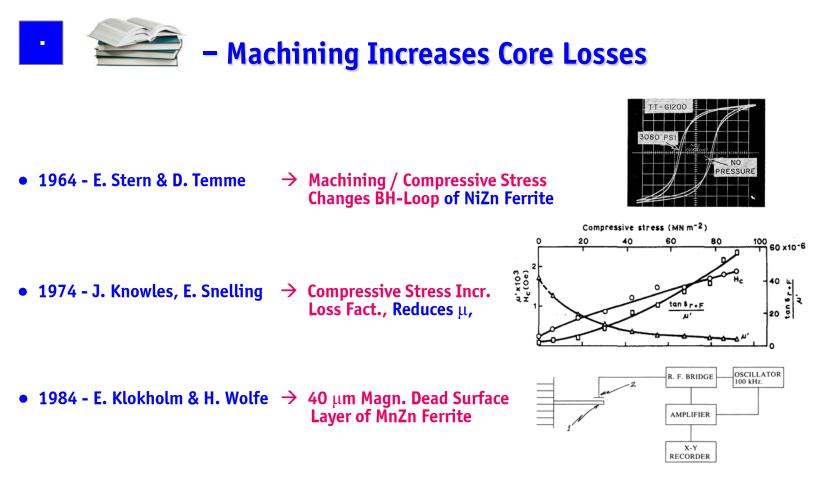

#### **High Frequency Inductors (3)**

- \* **Knowles (1975!)**

- **Cutting of Ferrite Introduces Mech. Stress**

- Significant Increase of the Loss Factor Reduction by Polishing / Etching (5 µm)

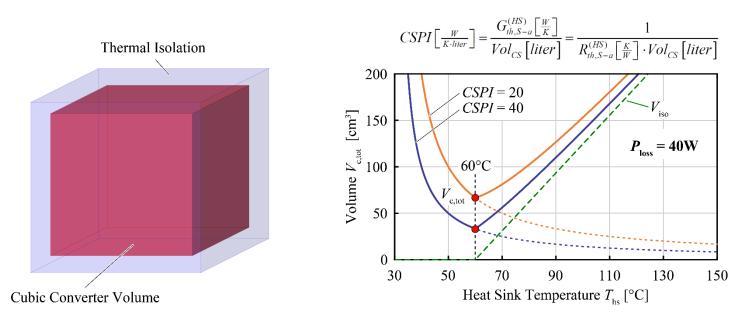

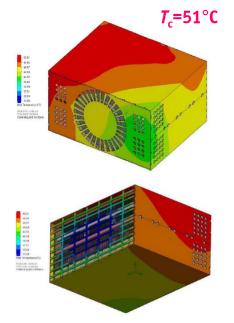

#### Thermal Management (1)

- 30°C max. Ambient Temperature

60°C max. Allowed Surface and Air Outlet Temperature

- **Evaluation of Optimum Heatsink Temp. for Thermal Isolation of Converter**

Minimum Volume Achieved w/o Thermal Isolation with Heatsink @ max. Allowed Surface Temp.

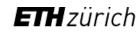

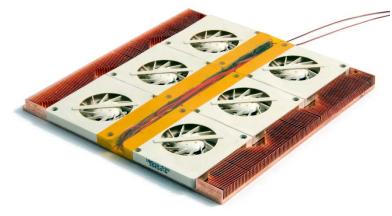

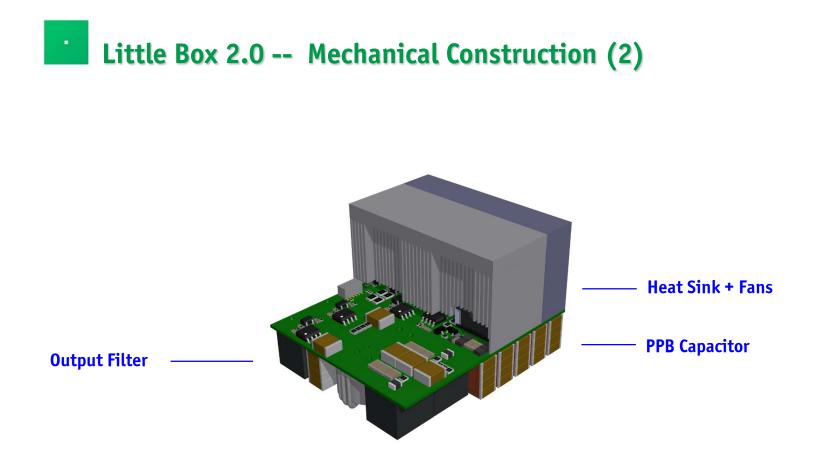

#### **Thermal Management (2)**

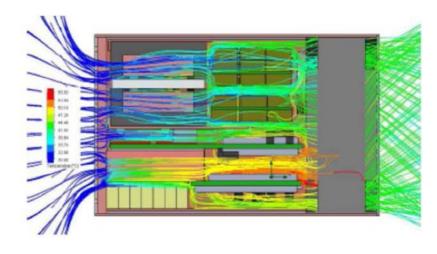

• Overall Cooling Performance Defined by Selected Fan Type and Heatsink

- Optimal Fan and Heat Sink Configuration Defined by Total Cooling System Length

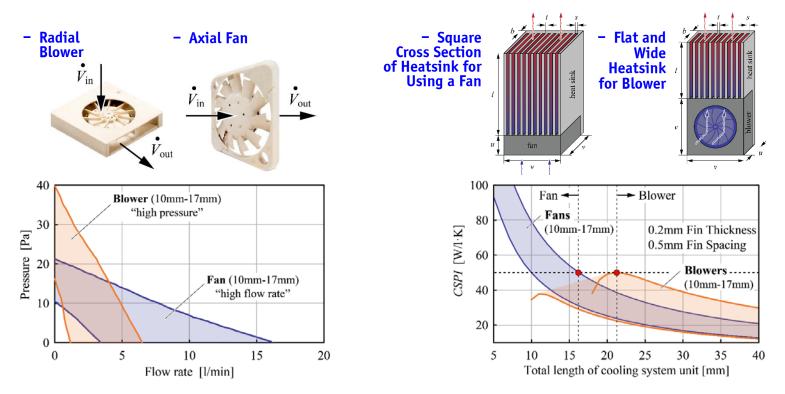

Cooling Concept with Blower Selected → Higher CSPI for Larger Mounting Surface

- 30mm Blowers with Axial Air Intake / Radial Outlet

- Full Optimization of the Heatsink Parameters •

- 200um Fin Thickness

- 500um Fin Spacing

- 3mm Fin Height

- 10mm Fin Length

- CSPI = 37 W/(dm<sup>3</sup>.K) 1.5mm Baseplate

- CSPI<sub>eff</sub>= 25 W/(dm<sup>3</sup>.K) Considering Heat Distribution Elements

Two-Side Cooling → Heatsink Temperature = 52°C @ 80W (8W by Natural Convection)

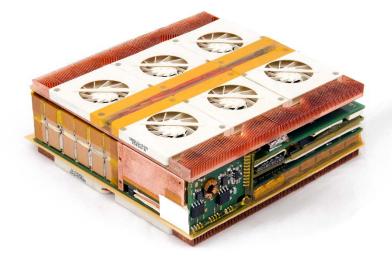

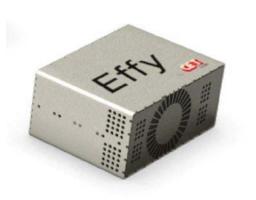

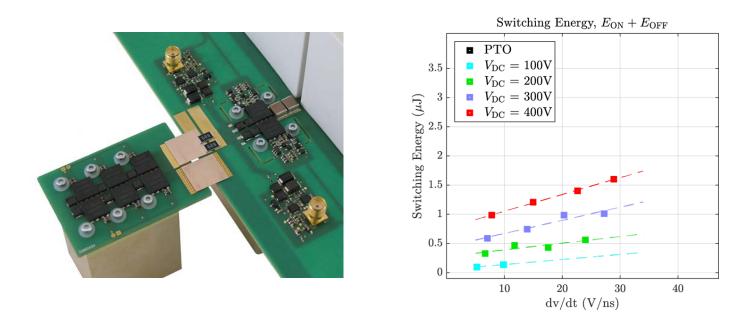

## Little Box 1.0

- System Employing Active CeraLink<sup>™</sup> 1-⊕ Power Pulsation Buffer

- 8.2 kW/dm<sup>3</sup>

- 8.9cm x 8.8cm x 3.1cm

- *f<sub>s</sub>* = 250kHz ... 1MHz 96,3% Efficiency @ 2kW

- T\_=58°C @ 2kW

- $\begin{array}{l} \Delta u_{\rm DC} = \ 1.1\% \\ \Delta i_{\rm DC} = \ 2.8\% \\ \ THD + N_U = \ 2.6\% \\ \ THD + N_I = \ 1.9\% \end{array}$

- Compliant to All "Original" Specifications (!)

- $i_{and}$  < 5mA (!)

- No Low-Frequ. CM Output Voltage Component

No Overstressing of Components

- All Own IP / Patents

## Little Box 1.0

- System Employing Active CeraLink<sup>™</sup> 1-⊕ Power Pulsation Buffer

- 8.2 kW/dm<sup>3</sup>

- 8.9cm x 8.8cm x 3.1cm

- f<sub>s</sub> = 250kHz ... 1MHz 96,3% Efficiency @ 2kW T<sub>c</sub>=58°C @ 2kW

- $\begin{array}{l} \Delta u_{\rm DC} = \ 1.1\% \\ \Delta i_{\rm DC} = \ 2.8\% \\ \ THD + N_U = \ 2.6\% \\ \ THD + N_I = \ 1.9\% \end{array}$

- Compliant to All "Original" Specifications (!)

- $i_{qnd}$  < 5mA (!)

- No Low-Frequ. CM Output Voltage Component

No Overstressing of Components

- All Own IP / Patents

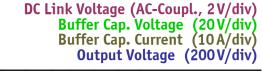

### Measurement Results (1)

- System Employing Active CeraLink<sup>™</sup> 1-⊕ Power Pulsation Buffer

- Ohmic Load / 2kW

**Compliant to All Specifications**

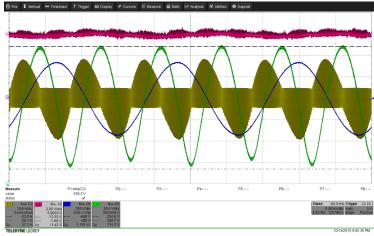

#### Measurement Results (2)

• System Employing Active CeraLink<sup>™</sup> 1-⊕ Power Pulsation Buffer

- Buffer Cap. Voltage (50 V/div) Buffer Cap. Current (10 A/div) Conv. Inp. Curr. (AC Coupl. 500 mA/div) DC Link Voltage (AC Coupl. 1 V/div)

- Stationary Operation @ 2kW Output Power

#### Measurement Results (3)

• System Employing Active CeraLink<sup>™</sup> 1-⊕ Power Pulsation Buffer

**Compliant to All Specifications**

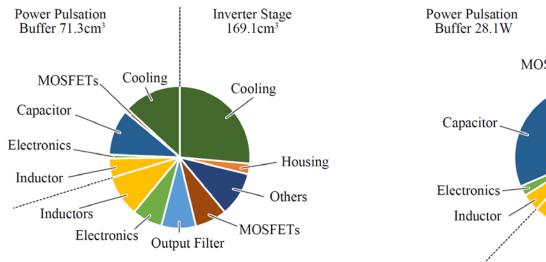

#### **Volume & Loss Distribution**

Volume Distribution (240cm<sup>3</sup>)

#### Inverter Stage

46.3W

- **MOSFETs MOSFETs** Output Filter Electronics Inductor

- Large Heatsink (incl. Heat Conduction Layers)

- Large Losses in Power Fluctuation Buffer Capacitor (!)

TCM Causes Relatively High Conduction & Switching Losses @ Low Power

Relatively Low Switching Frequency @ High Power Determines EMI Filter Volume

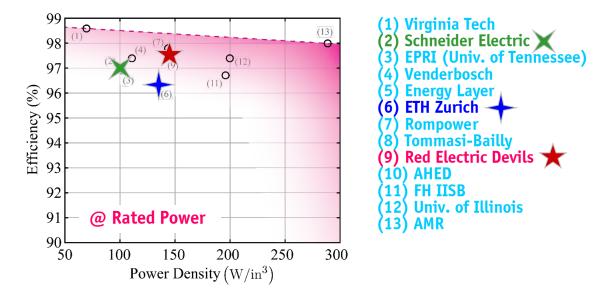

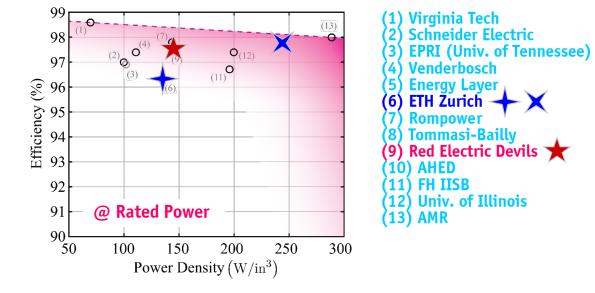

#### Finalists - Performance Overview

**18 Finalists (3 No-Shows)** 7 Groups of Consultants / 7 Companies / 4 Universities

- 70...300 W/in<sup>3</sup>

- **35 kHz...500kHz...1 MHz (up to 1MHz: 3 Teams)**

- Full-Bridge or DC/|AC|Buck Converter + Unfolder

- Mostly Buck-Type Active Power Pulsation Filters (Ceramic instead of Electrolytic Caps)

- GaN (11 Teams) / SiC (2 Teams) / Si (2 Teams)

ETH zürich

*Note:* Numbering of

**Teams is Arbitrary**

**Power Electronic Systems** Laboratory

#### **Google** Little Box Challenge Grand Prize Winner

#### **Red Electric Devils**

Olivier Bomboir, Paul Bleus, Fabrice Frebel, Thierry Joannes, Francois Milstein, Pierre Stassain, Christophe Geuzaine, Carl Emmerechts, Philippe Laurent

- No Low-Frequ. Common-Mode Output Voltage Comp.  $\rightarrow i_{gnd} < 5mA$  (!) Buck-Type DC-Side Active Power Pulsation Filter (MLCC Cap. <150µF, 200V<sub>pp</sub>)

- **2** x Interleaved Bridge Legs for Each Half-Bridge

- **DM** Inductors  $(L_1/L_2 \text{ and } L_4/L_5)$  and Series Connected CM Inductor  $(L_7/L_8)$ **Single Open-Loop Hall Sensor Outp. Curr.** Measurement + Observer-Based Curr. Reconstruction

#### **Red Electric Devils**

- No Low-Frequ. Common-Mode Output Voltage Comp.  $\rightarrow i_{gnd} < 5mA$  (!) Buck-Type DC-Side Active Power Pulsation Filter (MLCC Cap. <150µF, 200V<sub>pp</sub>)

- DSP & CPLD Control

- GaN Systems @ ZVS (35kHz ... 240kHz)

- Shielded Multi-Stage EMI Filter @ DC Input & AC Output

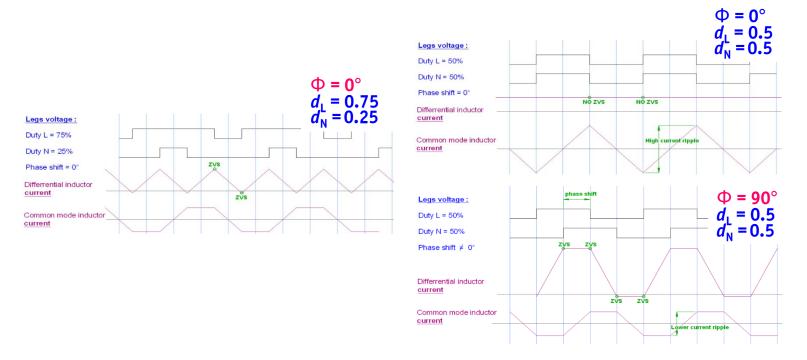

#### **Red Electric Devils**

**★** 145 W/in<sup>3</sup>

• Variable Phase-Shift of the Half-Bridges (0° or 90°) Dep. on Duty Cycle

■ Selection of Opt. Phase Shift & Sw. Frequency for ZVS & Min. Size of Filter Ind. L<sub>CM</sub> & L<sub>DM</sub>

- **145 W/in<sup>3</sup>**

- 95.4 % CEC Efficiency

- *i*<sub>gnd</sub> < 5mA (!)

- ČŠPI = 22.6 W/(dm<sup>3</sup>.K) Heatsink & Axial Fan

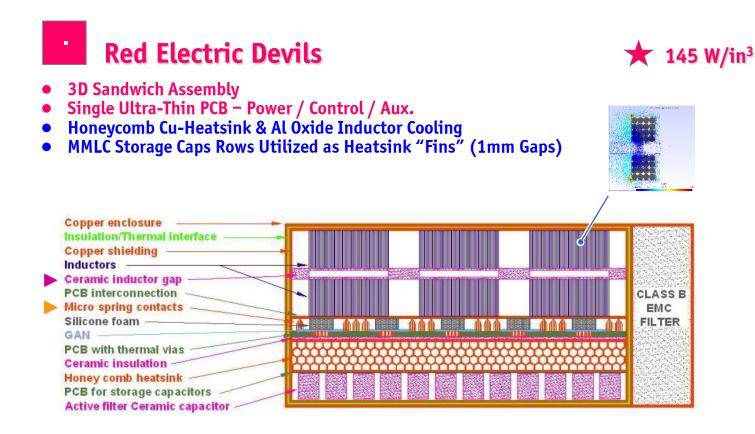

# **Red Electric Devils**

★ 145 W/in<sup>3</sup>

- **3D Sandwich Assembly**

- Single Ultra-Thin PCB Power / Control / Aux.

- Honeycomb Cu-Heatsink & Al Oxide Inductor Cooling

- MMLC Storage Caps Rows Utilized as Heatsink "Fins" (1mm Gaps)

- 145 W/in<sup>3</sup>

- 95.4 % CEC Efficiency

- *i*<sub>gnd</sub> < 5mA (!)</li>

CSPI = 22.6 W/(dm<sup>3</sup>.K) Heatsink & Axial Fan

#### Google Little Box Challenge Top 3 Finalist

#### Schneider Gelectric Team

Miao-xin Wang, Rajesh Ghosh, Srikanth Mudiyula, Radoslava Mitova, David Reilly, Milind Dighrasker, Sajeesh Sulaiman, Alain Dentella, Damir Klikic, Michael Hartmann

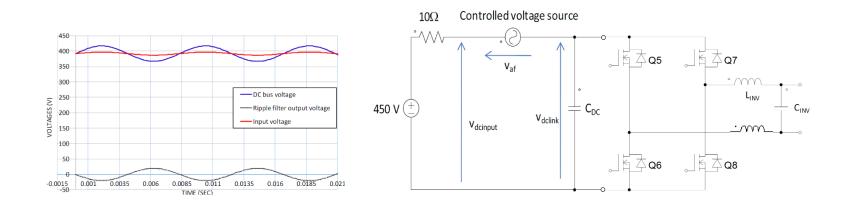

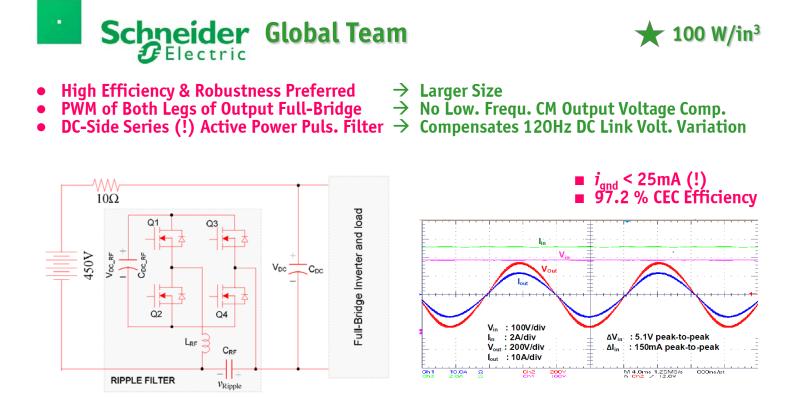

- High Efficiency & Robustness Preferred

- **PWM of Both Legs of Output Full-Bridge** •

- **DC-Side Series** (!) Active Power Puls. Filter  $\rightarrow$  Compensates 120Hz DC Link Volt. Variation •

- $\rightarrow$  Larger Size

- $\rightarrow$  No Low. Frequ. CM Output Voltage Comp.

ETH zürich

- C<sub>DC</sub> = 400uF / 450V 1/5 Volume Comp. to only Bulk Capacitors V<sub>dcinput</sub> Ripple <10% (<30V<sub>pp</sub>) @ Full Load

- Nanocrystalline CM Choke

- DC-Side & AC-Side EMI/RF Filter

Q<sub>5...8</sub> T0247 SiC MOSFETs, 45kHz of Both Legs

- $C_{DC_{RF}}=2 \times 1500 \text{uF}/25\text{V}, U_{DC_{RF}}=15\text{V}$ Only 52VA Processed Ripple Filter Power @ Rated Output (!)  $Q_1/Q_2 \& Q_3/Q_4 R_{ds,on} = 2.2 \text{m}\Omega$  MOSFETs (40V, 100A), w/o Heatsink,  $f_S = 130 \text{kHz}$  of Both Legs TI Piccolo DSP Control of Entire System / Open Loop Control of 120Hz Comp. Filter

#### Optimization of Little-Box 1.0

Adv. Modulation / Circuit Concepts Measurement of Buffer Cap. Performance Measurement of GaN ZVS & On-State Losses Measurement of Multi-Airgap Core Losses np-Pareto Optimization

- TCM → ZVS but Large Current Ripple & Wide Frequency Variation

- PWM → Const. Sw. Frequency but Hard Sw. @ Current Maximum

- Opt. Combination of TCM & PWM  $\rightarrow$  Optim. Frequ. Variation Over Output Period

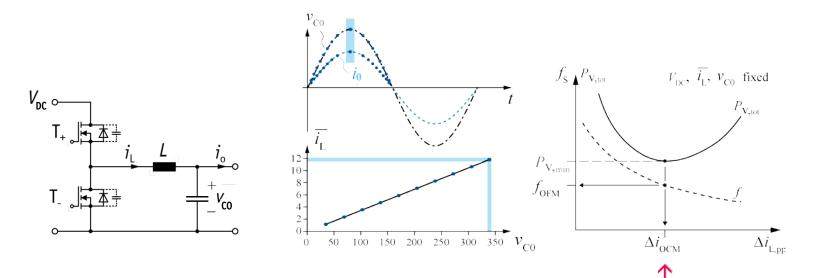

- Exp. Determination of Loss-Opt. Sw. Frequency  $f_{0FM}$  Considering DC/DC Conv. Stage

- DC/AC Properties Calculated Assuming Local DC/DC Operation

- Loss-Optimal Local Sw. Frequ.  $f_{OFM}$  for Given  $V_{DC}$  & Local  $i_0$  &  $v_{CO}$

- TCM → ZVS but Large Current Ripple & Wide Frequency Variation

- PWM → Const. Sw. Frequency but Hard Sw. @ Current Maximum

- Opt. Combination of TCM & PWM  $\rightarrow$  Optim. Frequ. Variation Over Output Period

- Exp. Determination of Loss-Opt. Sw. Frequency  $f_{OFM}$  Considering DC/DC Conv. Stage

- DC/AC Properties Calculated Assuming Local DC/DC Operation

- Loss-Optimal Local Sw. Frequ.  $f_{OFM}$  for Given  $V_{DC}$  & Local  $i_0$  &  $v_{CO}$

37/92

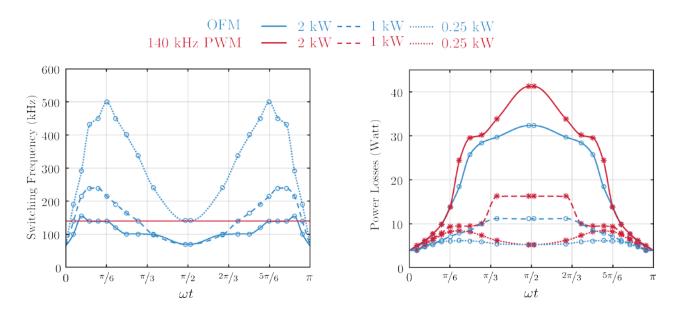

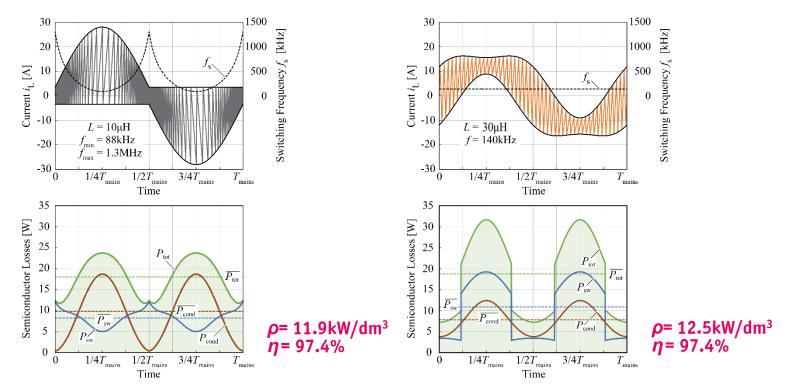

## **Eff. Optimal** *f*<sub>s</sub>-Modulation

- Resulting Time-Dependency of Optimal Sw. Frequ. & Power Loss

- Comparison with 140 kHz Const. Sw. Frequency PWM

Higher Average Switching Frequency f<sub>s</sub> @ Light Loads

Reduction of f<sub>s</sub> @ Mains Voltage Peak (for Ohmic Load) for Sustaining ZVS

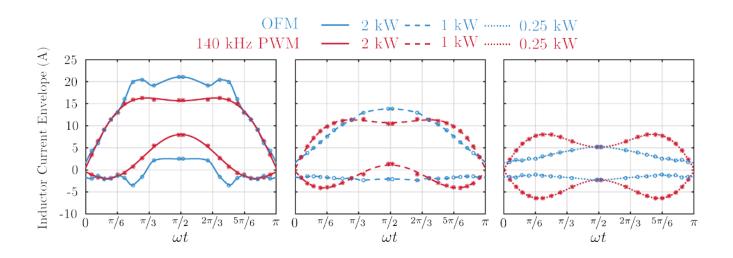

### **Eff. Optimal** *f*<sub>s</sub>-Modulation

• Optimal Inductor Current Envelope for Diff. Output Power Levels

Higher Average Switching Frequency f<sub>s</sub> @ Light Loads

Reduction of f<sub>s</sub> @ Mains Voltage Peak (for Ohmic Load) for Sustaining ZVS

#### Measurements

Buffer Capacitor Losses / Cap. Power Semicond. ZVS & On-State Losses Ferrite Multi-Airgap Core Losses

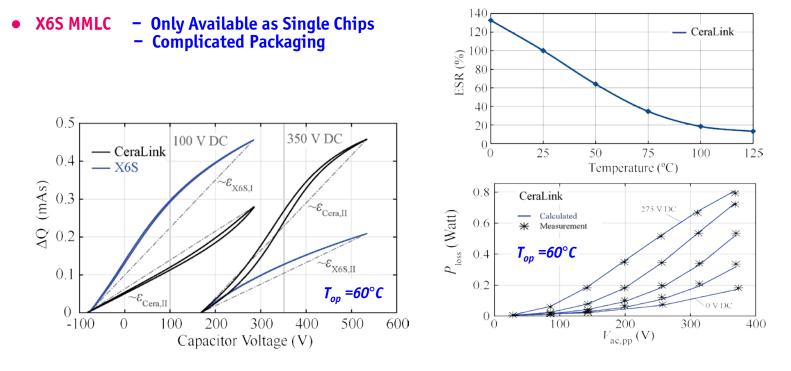

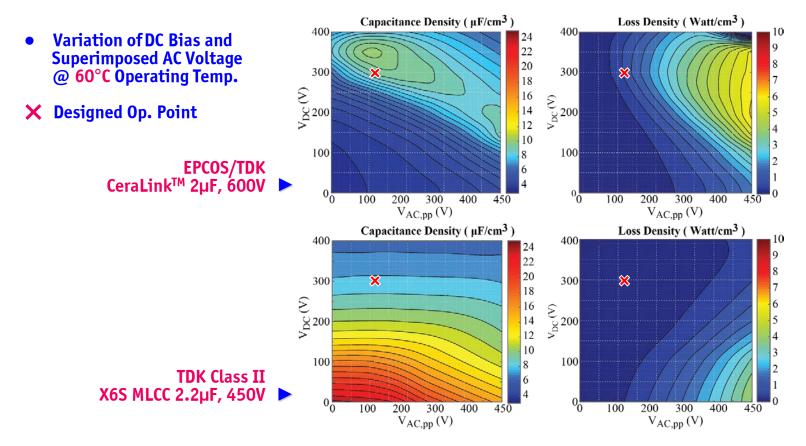

## **CeraLink vs. X6S**

- **Electrolytic Capacitors**

- X6S MLCC, 2.2μF, 450 V Class II CeraLink<sup>™</sup>,1μF /2μF, 650 V CeraLink<sup>™</sup> Allows Op. @ 125°C

- $\rightarrow$  Limited by Lifetime Current Limit

- → Highest Energy Density but Low Cap. @ High DC Bias

→ PLZT Ceramic, High Cap. @ High DC Bias

→ Very Low ESR @ High Frequencies

PPB Design Optimiz. Requires Large-Signal Capacitance and Power Loss Data in All Operating Points

- **Electrolytic Capacitors**

- X6S MLCC, 2.2μF, 450 V Class II CeraLink<sup>™</sup>,1μF /2μF, 650 V CeraLink<sup>™</sup> Allows Op. @ 125°C

- $\rightarrow$  Limited by Lifetime Current Limit

- → Highest Energy Density but Low Cap. @ High DC Bias

→ PLZT Ceramic, High Cap. @ High DC Bias

→ Very Low ESR @ High Frequencies

**Experimental Setup for Generation of DC Bias & Superimposed AC Voltage**

- **CeraLink vs. X6S**

- Large-Signal 120Hz Excitation Reveals Large Hysteresis

Significantly Higher Losses @ 120Hz Comp. to X6S MLCC

ESR Drops Significantly @ Higher Temp.

36μF (27μF) Blocks of Prepackaged Single Chips CeraLink<sup>™</sup>

- Reliable Mech. Construction

**ETH** zürich

PPB Design Optimiz. Requires Large-Signal Capacitance and Power Loss Data in All Operating Points

**ETH** zürich

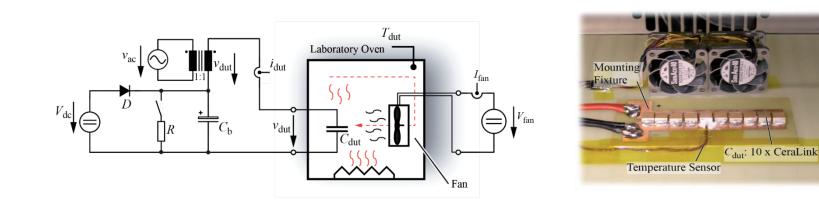

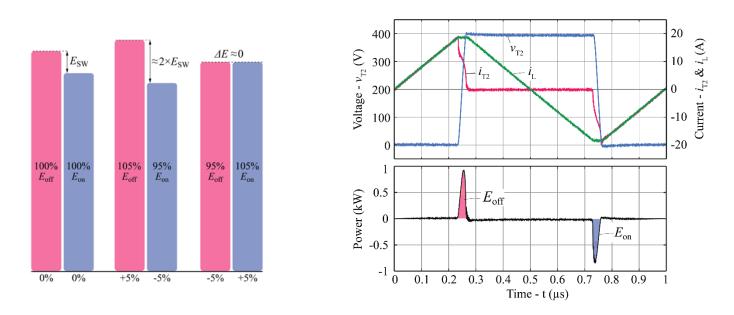

# Analysis of GaN Power Transistor ZVS Losses

- Little-Box 1.0 Experiments Indicated *Residual ZVS Losses of GaN Power Transistors*

- Losses Cannot be Explained by Remaining  $i_D$ ,  $u_{DS}$  Overlap / Non-Ideal Gate Drive etc.

- Potentially Large Measurement Error for Electric Double-Pulse Sw. Loss Measurement

- Accuracy only Guaranteed by Direct Loss Measurement  $\rightarrow$  Calorimetric Approach

## Analysis of GaN Power Transistor ZVS Losses

- Little-Box 1.0 Experiments Indicated Residual ZVS Losses of GaN Power Transistors

- Losses Cannot be Explained by Remaining  $i_D$ ,  $u_{DS}$  Overlap / Non-Ideal Gate Drive

Potentially Large Measurement Error for Electrical Double-Pulse Sw. Loss Measurement

Accuracy only Guaranteed by Direct Loss Measurement → Calorimetric Approach

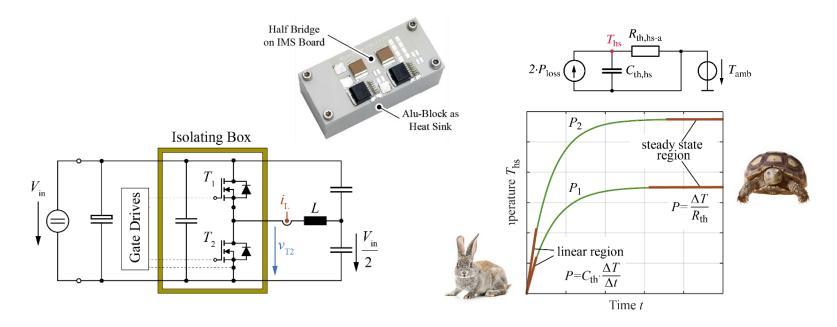

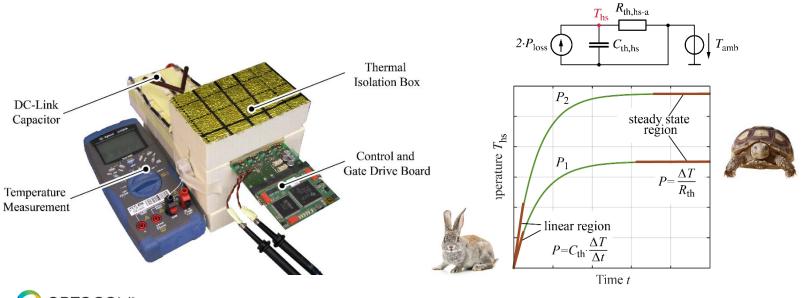

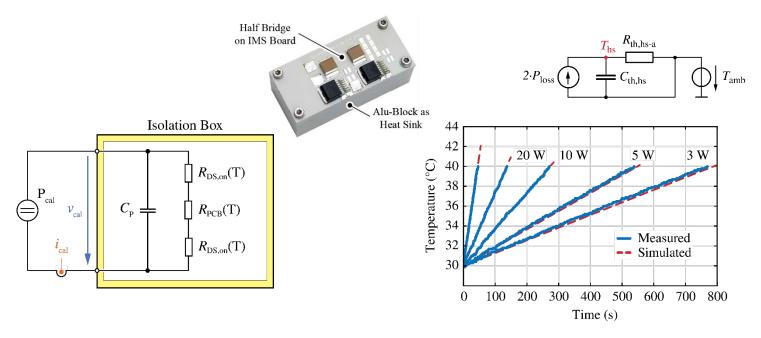

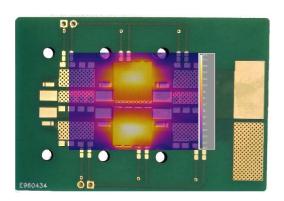

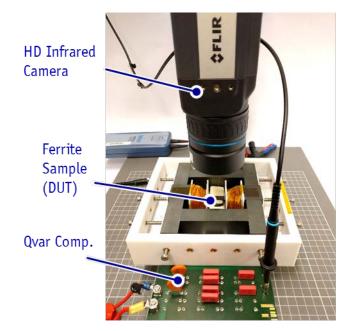

# **Calorimetric Measurement of ZVS Losses**

- "Inductor in the Box" → Accurate DC Inp. & Outp. Power Measurement, Subtr. on Ind. Losses

"Bridge Leg in the Box" → Direct Measurement of the Sum of Cond. & Sw. Losses

- "Bridge Leg in the Box" & Fast Measurement by C<sub>th</sub>.∆T/∆t Evaluation

DC/DC Operation @ High Sw. Frequency for Large Ratio of Sw. and Conduction Losses

Subtraction of the Cond. Losses from Datasheet or Dir. Measurement

**ETH** zürich

#### **Calorimetric Measurement of ZVS Losses**

- "Bridge Leg in the Box" & Fast Measurement by  $C_{th}$ . $\Delta T/\Delta t$  Evaluation Subtraction of the Cond. Losses from Datasheet or Direct Measurement

- DC/DC Operation @ High Sw. Frequency for Large Ratio of Sw. and Conduction Losses •

- Isolated Temp. Measurement with Optical Fiber (GaAs Crystal) Instead of Thermocouple Calibration by On-State of  $T_1$  and  $T_2$  & DC Current Operation / DC Power Loss Measurement

## **Calibration of "Bridge Leg in the Box" Setup**

- **Calibration** by On-State of  $T_1$  and  $T_2$  & DC Current Operation / DC Power Loss Measurement Identification of Thermal Cap.  $C_{th}$  and Thermal Resistance  $R_{th}$

- **DC Power Loss Measurement Ensures High Accuracy**

- Thermal Behavior for Short Measurement Times Mainly Determined by C<sub>th</sub>

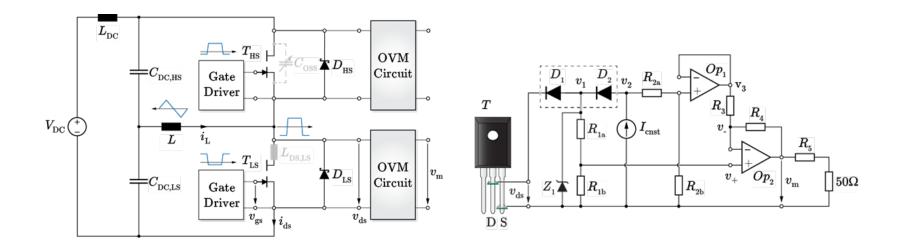

#### Accurate On-State Voltage Measurement

- Clamping Diode for Limiting the On-State Voltage Measurement (OVM) to 2V

- Subtraction of the SiC Diode Forward Voltage Drop for High Accuracy (2mV)

Only 50ns Blanking Time – OVM Circuit Can also be Used for Dynamic R<sub>DS,on</sub> Measurement

Accurate On-State Voltage Measurement

- Clamping Diode for Limiting the On-State Voltage Measurement (OVM) to 2V

- Subtraction of the SiC Diode Forward Voltage Drop for High Accuracy (2mV)

Only 50ns Blanking Time – OVM Circuit Can also be Used for Dynamic R<sub>DS,on</sub> Measurement

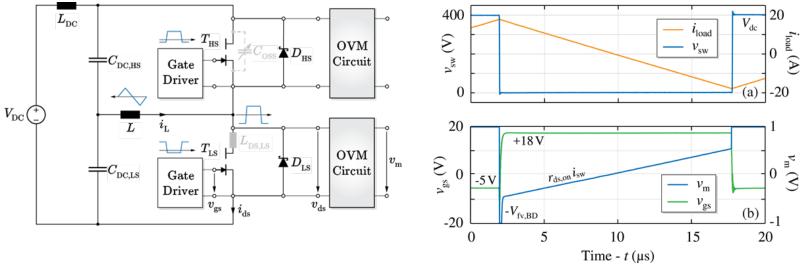

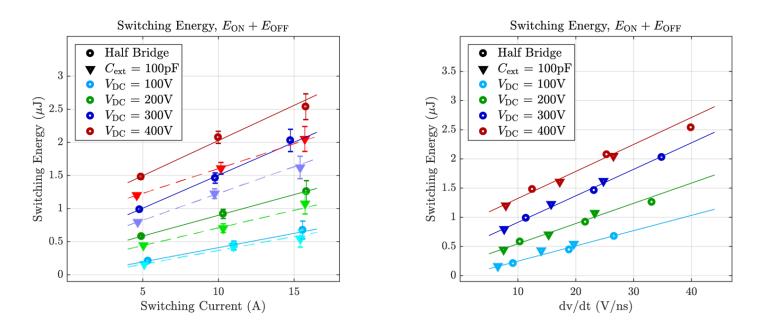

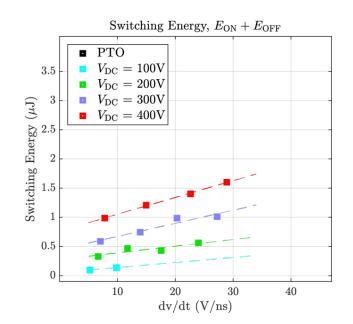

**ZVS Loss Measurement Results (1)**

- Measurement of Energy Loss per Switch and Switching Period

- GaN Enhancement Mode Power Transistor (600V,  $70m\Omega@25^{\circ}C$ ) Antiparallel CREE SiC Schottky Freewheeling Diode (600V, 3.3A)

- Switching w/ and w/o 100pF Parallel Low-Loss SMD Multilayer Ceramic Chip Capacitor (450V) dv/dt Measured in 10%...90% of Turn-off Voltage, Behavior @ at Low dv/dt Still to be Clarified

## **ZVS Loss Measurement Results (2)**

- Analysis of a *Permanently-Off Half-Bridge* Excited with Switch Node Voltage

- Measurement of Energy Loss per Switch and Switching Period

- Heating Indicates Losses in the Permanently-Off Devices

- Losses Comparable to the Losses of the Switching Half Bridge for Same dv/dt

**Power Electronic Systems** Laboratory

## ZVS Loss Measurement Results (2)

- Analysis of a *Permanently-Off Half-Bridge* Excited with Switch Node Voltage

- Measurement of Energy Loss per Switch and Switching Period

- Heating Indicates Losses in the Permanently-Off Devices

- Losses Comparable to the Losses of the Switching Half Bridge for Same dv/dt

55/92

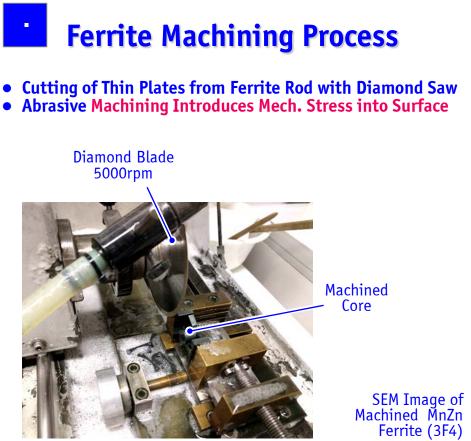

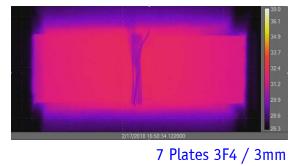

# Multi-Airgap Inductor

- Ferrite E-Core with 50 x 0.3mm Thick Stacked Plates as Center Post

- Power Loss of TCM Inductors Sign. Higher than Expected

• Analysis by Fraunhofer Shows Up to Factor 10 High Core Losses (!)  $\rightarrow$  "Mystery" Losses

● 1987 - S. Chandrasekar et al. → Lapping Causes Greater Residual Stress than Grinding

Ferrite Plate

**Residual Surface Stress**

■ Ferrite Properties in Surface Altered → Increase of Loss Factor

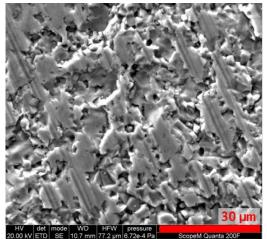

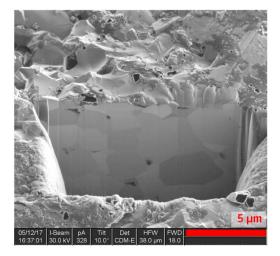

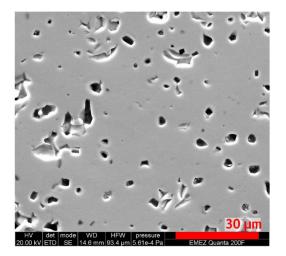

# Subsurface Condition of Machined Ferrite Sempa

Materials Science and Technology

- Focused Ion Beam (FIB) Cut into Ferrite (3F4) Sample & Scanning Electron Microscopy (SEM)

Polishing of Surface with Grain Sizes 2400 SiC → 4000 SiC → Colloidal Silica SiO<sub>2</sub>

**Polishing Removes 500** $\mu$ m of Surface  $\rightarrow$  Bulk Material Exposed

Bulk Ferrite also Exhibits Cavities  $\rightarrow$  Result of (Imperfect) Sintering Process

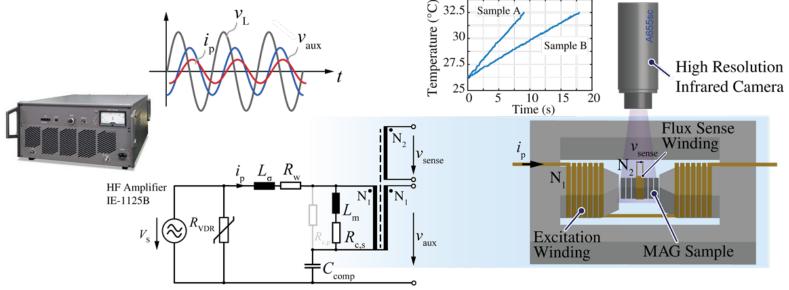

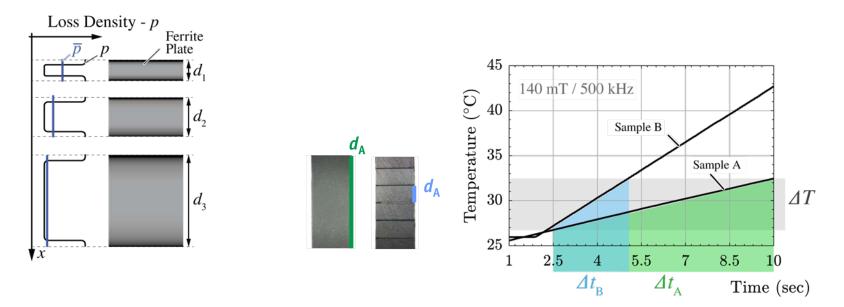

#### **Thermometric Surface Loss Measurement**

- Impression of Homogeneous Sin. Flux Density of Desired Ampl. / Frequ.

Cap. Series Comp. for Lowering Impedance @ High Frequencies

Measurement of *Transient* Temp. Change → Calcul. of Losses

- Sample A Sample B 32.5 Sample A

• Temperature Rise of  $\Delta T$ = 1.5°...5°C Sufficient (Accuracy ±0.2°C), Fast Measurement (!)

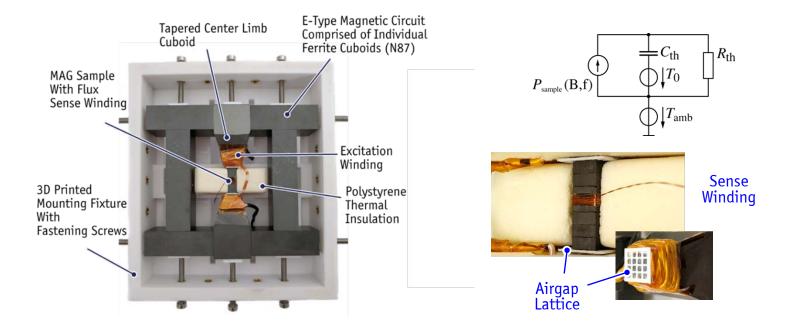

## Test Fixture / Magnetic Circuit

- E-Type Fixture for Swift Installation of Diff. Samples (7mm x 6.4mm x 21.6mm)

- FEM Optimiz. of Dimensions Large Core Cross Section / Tapered Outer Limbs

- Therm. Insul. & Airgap Lattice Ensure Low Heat Flux to Ambient

- Measurement of Temp. Increase Over Time Allows to Verify Homog. Flux Density in Sample

62/92

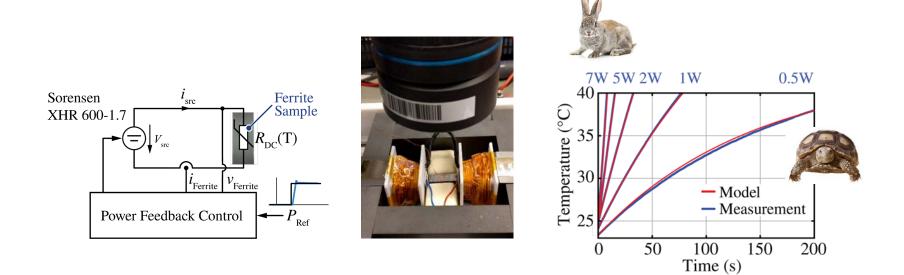

## Identification of Therm. Parameters $R_{th}$ , $C_{th}$

- DC Current Impressed in Ferrite, Voltage Control for Const. Power Dissipation as R<sub>DC</sub>=R<sub>DC</sub>(Temp.)

Temperature Response of Sample Recorded (*FLIR A655sc W* with Close-Up Lens)

- Emissivity of Ferrite Determined Using Heat Plate ( $\varepsilon$ = 0.86)

- *R*<sub>th</sub> = 37.8 K/W Can be Neglected

Obtained Parameter *C*<sub>th</sub>=3.83J/K Close to *C*<sub>th</sub> Calc. Based on Vendor Data (*C*<sub>th</sub> = 3.6J/K)

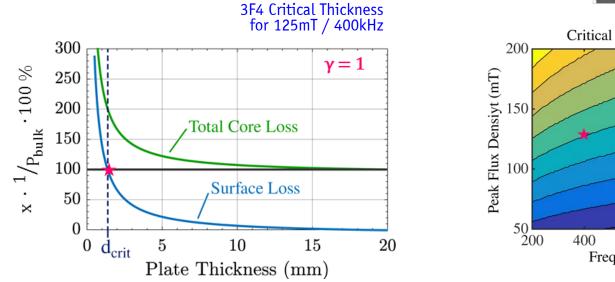

#### **Surface Loss Measurement Principle** FERROXCUBE

- Hypothesis: Core Loss Density in Surface Layer Higher than in Bulk

- Thinner Plates → Higher Average Losses / Faster Temp. Rise

Stacking of Plates Does NOT Affect Temperature Rise (!)

Surface Loss Density Can be Directly Calc. from Mat. Parameters / Geometry &  $\Delta t_{A}$  and  $\Delta t_{B}$

## **Temperature Rise Recording**

- Comparison of Solid 3F4 Sample (1 x 21.6mm) and Stacked Plates Sample (7 x 3mm) Sinusoidal Excitation *100mT / 400kHz* •

- •

3F4 Solid Sample / 21.6mm

■ Thermal Image shown 25 Seconds After Turn-On of Magnetic Excitation

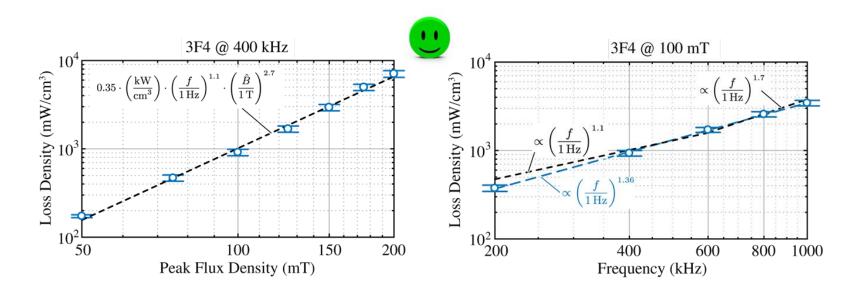

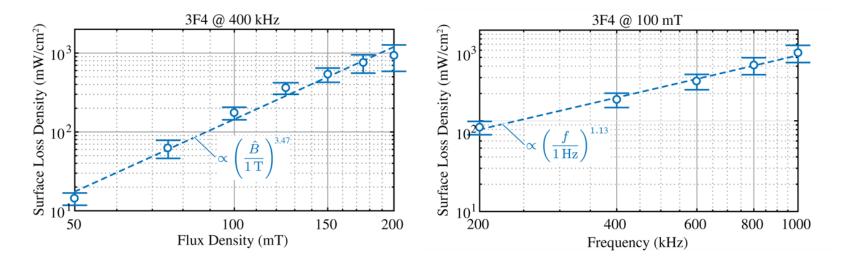

#### Measurement Results – Bulk Losses

- Comparison of Measurement Results and Datasheet Values, 3F4 @ 25°C

- Measurement Error Approx. ±10% (Worst Case)

**Good Agreement with Datasheet Values / Vendor Steinmetz Parameters**

**Measurement Results – Surface Losses**

- •

- Measurement Error Approx. ±25% (Worst Case) Error Determined by Meas. Time & Temp. Reading Accuracy •

$$p_{Surf} = 0.0615 \times \left(\frac{f}{1 \text{Hz}}\right)^{1.13} \times \left(\frac{\hat{B}}{1 \text{T}}\right)^{3.47} \left(\frac{\text{mW}}{\text{cm}^2}\right)$$

Comp. of Steinmetz Parameters of Surface Losses & Bulk Losses BS > B, aS < a

*"Critical Thickness"* of Ferrite Plates

- "Critical Thickness" Reached for Equal Losses in Bulk & Surface

- Critical Plate Thickness is INDEPENDENT of Cross Section (!)

Dependence on Flux Density Ampl. & Frequency !

Dependence on Material / Machining Process / Power Processing Treatment

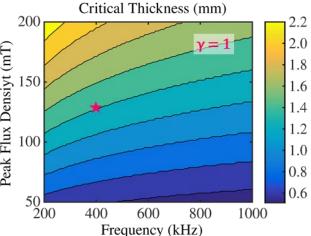

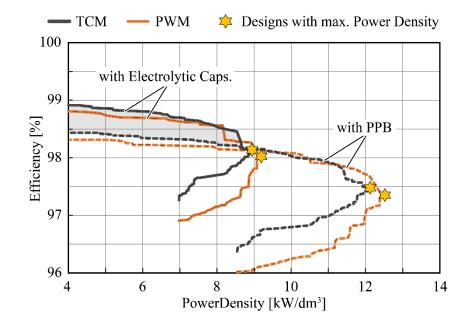

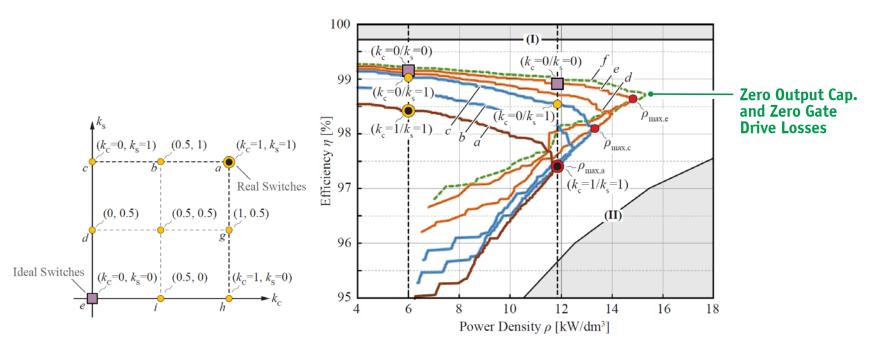

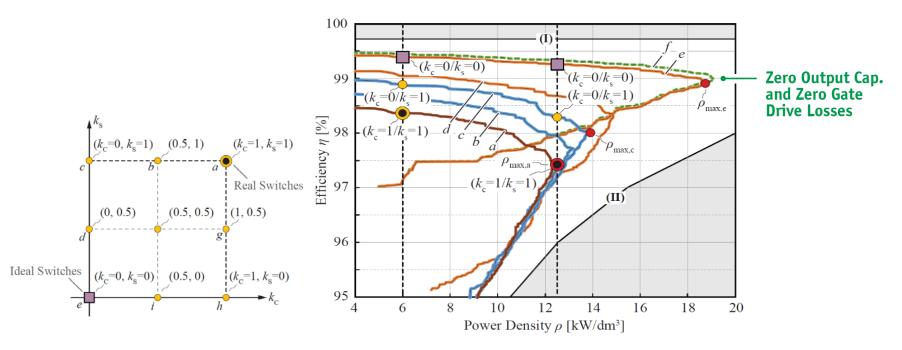

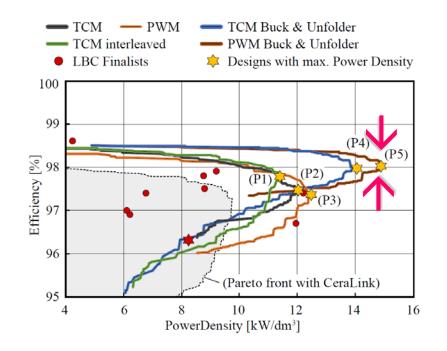

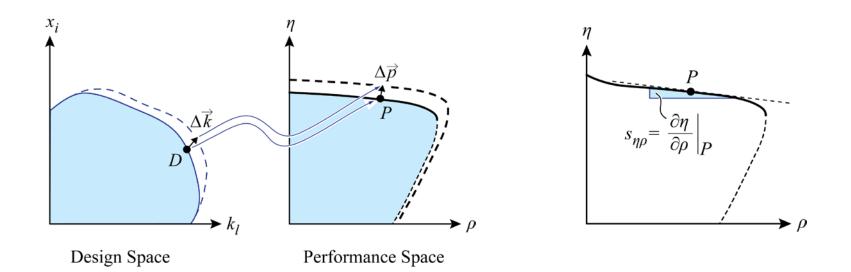

#### ηρ-Pareto Optimization of Little Box 1.0

ηρ-Pareto Front TCM vs. Large Ripple PMW The Ideal Switch is Not Enough (!) Design Space Diversity

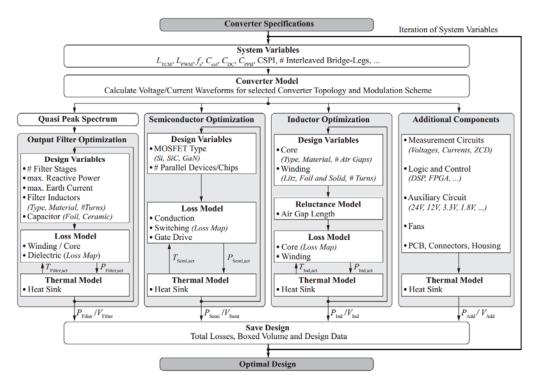

#### **Multi-Objective Optimization**

- **Detailed** System Models  $\rightarrow$  Power Buffer/Output Stage/EMI Filter Multi-Domain Component Models  $\rightarrow$  Passives & GaN & SiC Semicond.

- Consideration of Very Large # of Degrees of Freedom

Pareto Optimization Shows Trade-Off Between Power Density and Efficiency

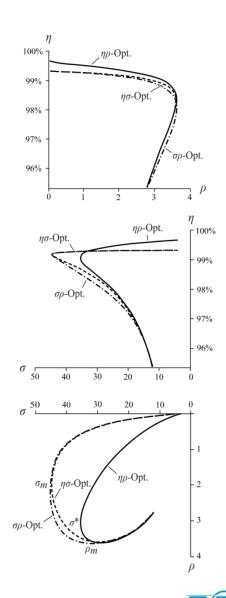

## Little Box 1.0 np-Performance Limits

- $\begin{array}{ll} \mbox{Multi-Objective Optimization of Little-Box 1.0 (incl. CeraLink \rightarrow X6S)} \\ \mbox{Absolute Performance Limits (I) DSP/FPGA Power Consumption} \\ (II) Heatsink Volume @ (1-\eta) \end{array}$ ٠

100 (a) **Transform** Realized Prototype **(I)** 99 (b)---(c) Efficiency η [%] 26  $+1.65\frac{kW}{k}$ dm<sup>3</sup> kW +0.65% $\rho_{\rm max,X6S}$ dm<sup>3</sup> +0.43% $\rho_{\rm max,Ceralink}$ **(a)** (II)96 Realized LBC Prototype (b) CeraLink Power Pulsation Buffer **(c)** X6S **Power Pulsation Buffer** 95 6 8 10 12 14 16 4 PowerDensity  $\rho$  [kW/dm<sup>3</sup>]

• Further Performance Improvement for Triangular Current Mode (TCM)  $\rightarrow$  PWM

#### Little Box 1.0 -- TCM $\rightarrow$ PWM

- Very High Sw. Frequency *f<sub>s</sub>* of TCM Around Current Zero Crossings Efficiency Reduction due to Residual TCM Sw. Losses & Gate Drive Losses Reduction

- Wide  $f_s$  -Variation Represents Adv. & Disadvantage for EMI Filter Design •

PWM -- Const. Sw. Frequency & Lower Conduction Losses PWM @ Large Current Rippel -- ZVS in Wide Intervals

#### Little Box 1.0 -- TCM $\rightarrow$ PWM

- Optimization for GaN GIT & No Interleaving

- Resulting Opt. Inductance of Output Inductor L=10µH (TCM), L=30µH (PWM@140 kHz)

• PWM vs. TCM  $\rightarrow$  Slightly Higher Max. Power Density @ Same Efficiency

# Little Box 1.0 -- Electrolytic Cap. / Active PPB

- Analysis for Google Little Box Challenge Specification ΔV/V < 3%</li>

Efficiency Benefit of PPB only for ρ > 9kW/dm<sup>3</sup>

- **Electrolytics Favorable for High Efficiency** @ Moderate Power Density ( $\Delta \eta$ = +0.5%)

- Electrolytics Show Lower Vol. & Lower Losses if Large △V/V is Acceptable (e.g. for PFC Rectifiers)

#### The Ideal Switch is Not Enough (!)

## Little Box 1.0 @ Ideal Switches -- TCM

- Multi-Objective Optimization of Little-Box 1.0 (X6S Power Pulsation Buffer)

- Step-by-Step Idealization of the Power Transistors Ideal Switches:  $k_c$ = 0 (Zero Cond. Losses);  $k_s$ = 0 (Zero Sw. Losses)

Analysis of Improvement of Efficiency @ Given Power Density & Maximum Power Density

73/92

## Little Box 1.0 @ Ideal Switches -- PWM

- Multi-Objective Optimization of Little-Box 1.0 (X6S Power Pulsation Buffer)

- Step-by-Step Idealization of the Power Transistors Ideal Switches:  $k_c$ = 0 (Zero Cond. Losses);  $k_s$ = 0 (Zero Sw. Losses)

Analysis of Improvement of Efficiency @ Given Power Density & Maximum Power Density

**Power Electronic Systems** Laboratory

Little Box 1.0 @ Ideal Switches -- PWM

*L* & *f<sub>s</sub>* are Independent Variables (Dependent for TCM) Large Design Space Diversity (Mutual Compensation of HF and LF Loss Contributions)

**ETH** zürich

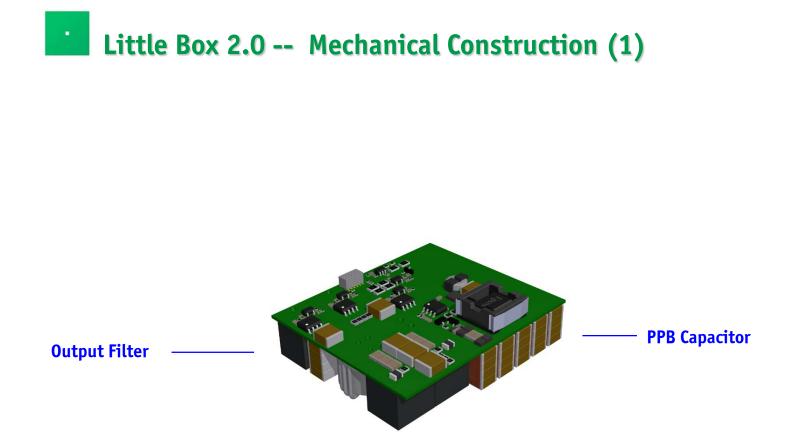

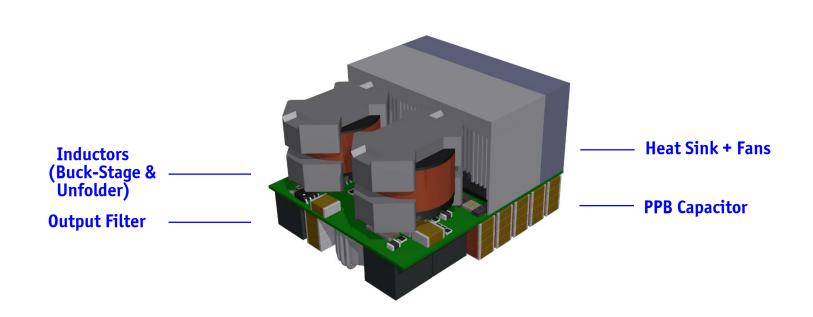

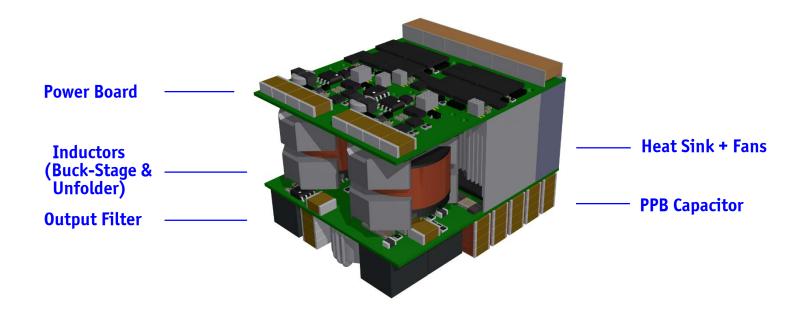

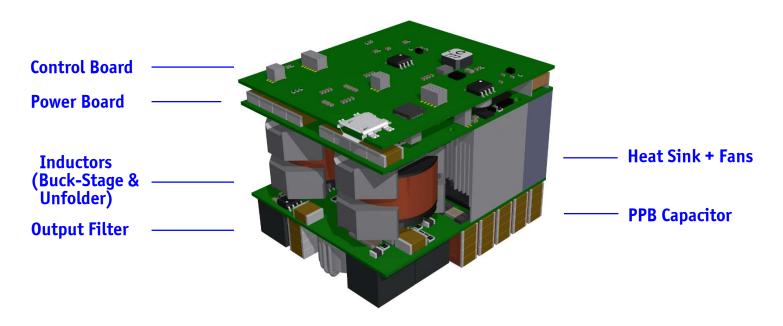

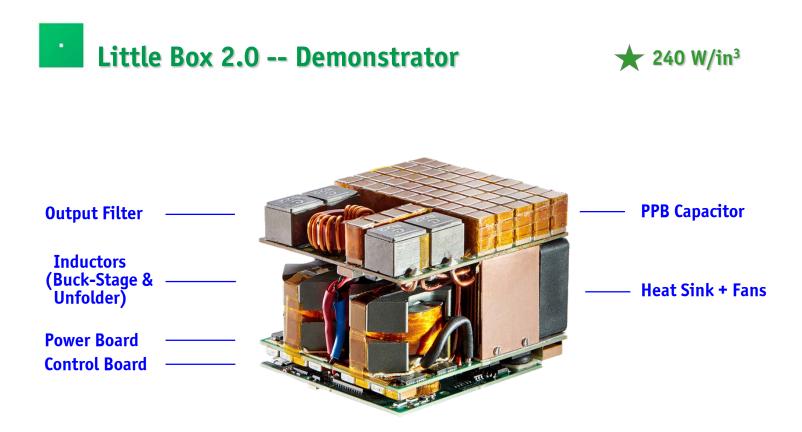

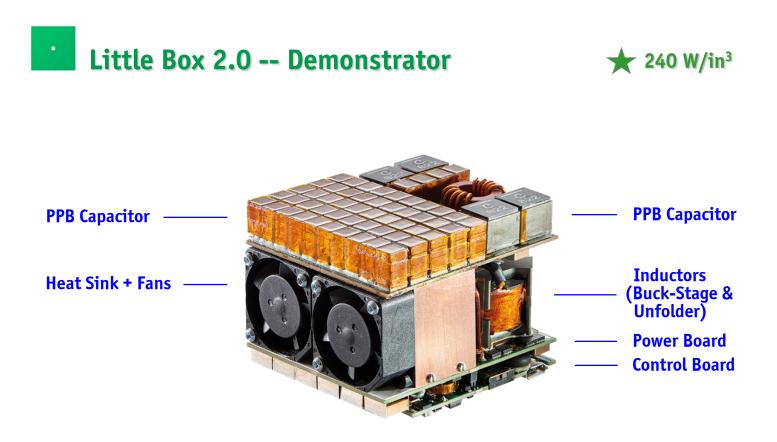

# Little Box 2.0

DC/ AC Converter + Unfolder PWM vs. TCM incl. Interleaving ηρ-Pareto Limits for Non-Ideal Switches Preliminary Exp. Results Final 3D-CAD

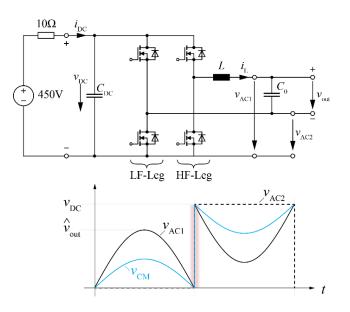

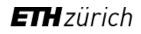

## Little Box 2.0 -- New Converter Topology (1)

- Alternative Converter Topology  $\rightarrow$  Only Single HF Bridge Leg + 60Hz-Unfolder

- DC/ AC Buck Converter + Full-Bridge Unfolder OR HF Half-Bridge & Half-Bridge Unfolder

- *v*<sub>AC1</sub>, *v*<sub>AC2</sub> More Diff. to Gen. but Add. DOF

Higher Sw. & Gate Drive Losses

ETHzürich

- Zero Low-Frequ. CM-Noise (DC Comp. Only)

- C<sub>CM</sub> Not Limited by Allowed Gnd Current

- *v*<sub>AC1</sub> More Difficult to Generate/Control

- Lower Conduction Losses

- Higher CM-Noise (DC and n x 120Hz-Comp.)

- C<sub>CM</sub>=150nF Allowed for 50mA Gnd Current

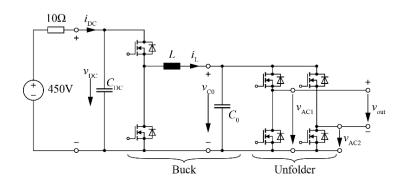

## Little Box 2.0 -- New Converter Topology (2)

- Alternative Converter Topology  $\rightarrow$  Only Single HF Bridge Leg + 60Hz-Unfolder

- DC/ AC Buck Converter + Full-Bridge Unfolder OR HF Half-Bridge & Half-Bridge Unfolder

- *v*<sub>c0</sub> Easy to Generate/Control

Higher Cond. Losses Due to FB-Unfolder

- Lower CM-Noise (DC & n x 120Hz-Comp.)

- C<sub>CM</sub>=700nF Allowed for 50mA Gnd Current

- *v*<sub>AC1</sub> More Difficult to Generate/Control

Lower Cond. Losses

- Higher CM-Noise (DC and n x 120Hz-Comp.)

- C<sub>CM</sub>=150nF Allowed for 50mA Gnd Current

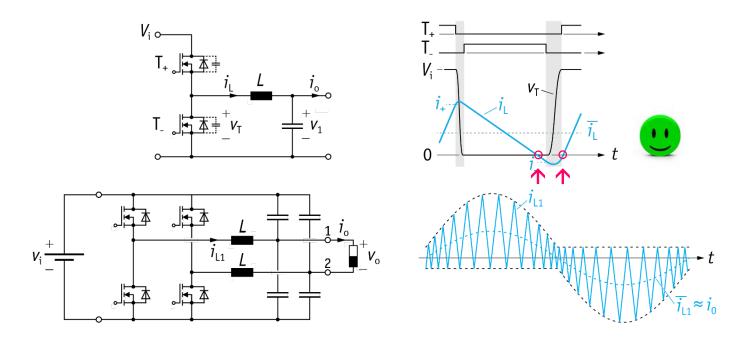

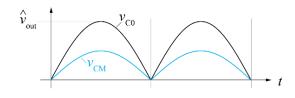

## Little Box 2.0 -- New Converter Topology (3)

- Alternative Converter Topology DC/ | AC | Buck Converter + Unfolder 60Hz-Unfolder (Temporary PWM for Ensuring Cont. Current Control) TCM or PWM of DC/ | AC | Buck-Converter

Full Optimization of All Converter Options for Real Switches / X6S Power Pulsation Buffer

**Power Electronic Systems** Laboratory

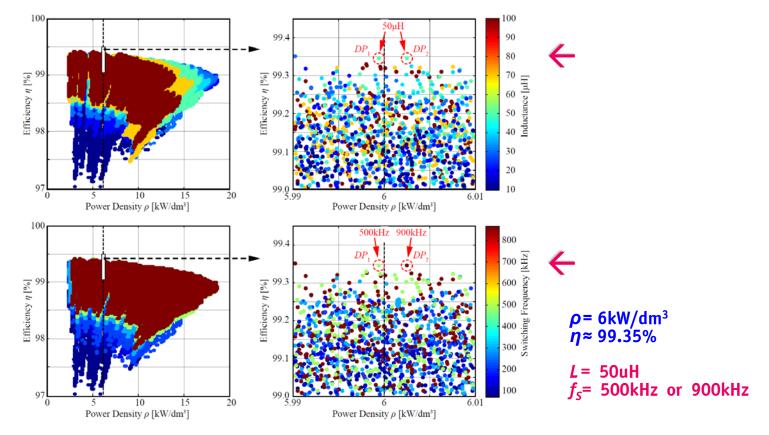

## Little Box 2.0 -- Multi-Objective Optimization

- DC/ AC Buck Converter (Single PWM Bridge Leg) + Unfolder Shows Best Performance Full-Bridge Would Employ 2 Switching Bridge Legs Larger Volume & Losses Interleaving Not Advantageous Lower Heatsink Vol. / Larger Vol. of Switches and Inductors

•  $\rho$ = 250W/in<sup>3</sup> (15kW/dm<sup>3</sup>) @  $\eta$ = 98% Efficiency Achievable for Full Optimization

**ETH** zürich

**ETH** zürich

Little Box 2.0 -- Mechanical Construction (5)

#### Experimental Results

Control Block Diagram Output Voltage / Input Current Quality Efficiency

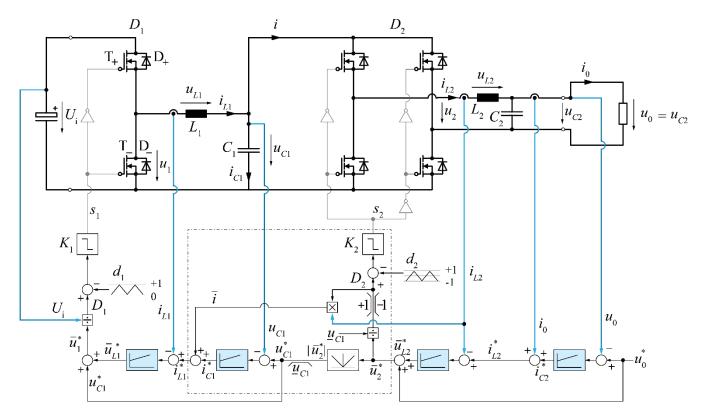

Little Box 2.0 – Control Structure

Each Stage (Buck & Unfolder) Controlled with Cascaded Current and Voltage Loop

Without Switching of Unfolder Control Like for Conventional Boost PFC Rectifier

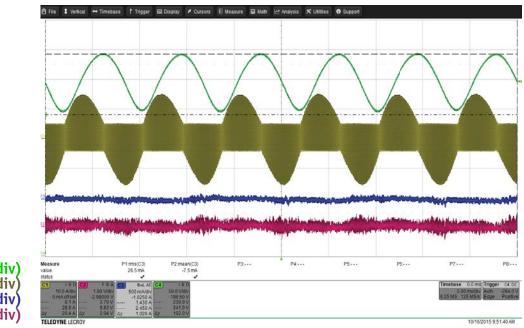

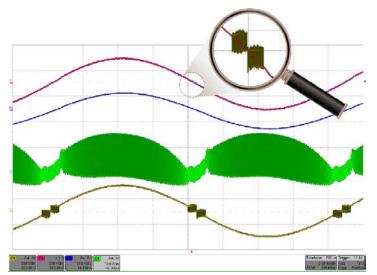

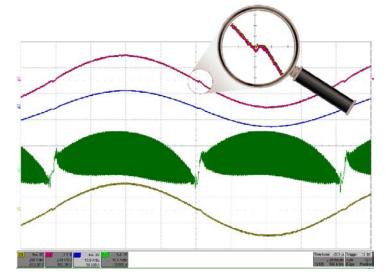

## Little Box 2.0 – Experimental Results (1)

• Voltage Zero Crossing Behavior With (Right) & Without (Left) Switching of Unfolder

Output Voltage (200V/div) Output Current (10A/div) Buck Inductor Current (10A/div) Unfolder Output Voltage (200V/div)

- Output Voltage & Current Fully Controlled Around Voltage Zero Crossings

- Slope of Buck Conv. Outp. Curr. can be Decreased Adv. for React. Loads (No Step-Change of DC Curr.)

**ETH** zürich

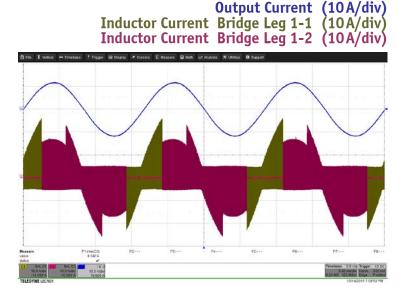

# Little Box 2.0 – Experimental Results (2)

• DC/|AC| Buck-Stage Output Voltage & Inductor Current

Resistive Load

Inductive Load

Capacitive Load

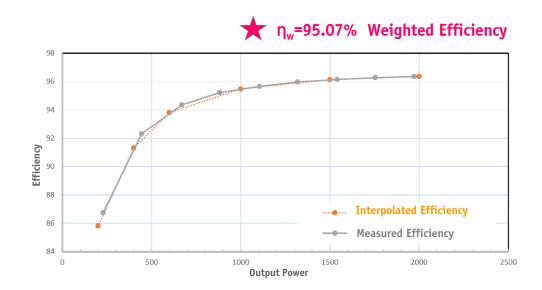

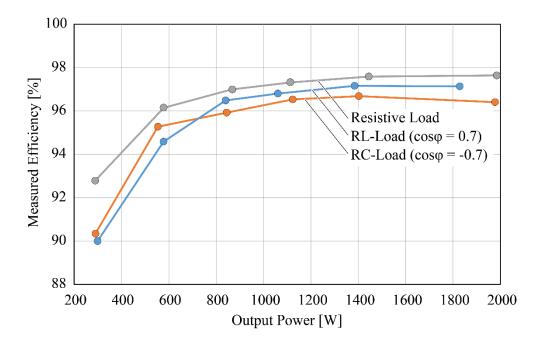

## Little Box 2.0 – Experimental Results (3)

- **Performance of First DC**/ | AC | Buck Converter + Unfolder Prototype

- PWM Operation

- Without Power Pulsation Buffer

■ 98% for Res. Load Achievable if Cond. Losses of PCB (Copper Cross Sect.) & Unfolder (*R*<sub>ds,on</sub>) are Red.

#### Litte Box 2.0 - Performance Comparison

**18 Finalists (3 No-Shows)** 7 Groups of Consultants / 7 Companies / 4 Universities

#### *Note:* Numbering of **Teams is Arbitrary**

#### 70...300 W/in<sup>3</sup>

- 35 kHz... 500kHz... 1 MHz (up to 1MHz: 3 Teams)

- Full-Bridge or DC/|AC|Buck Converter + Unfolder

- Mostly Buck-Type Active Power Pulsation Filters (Ceramic Caps of Electrolytic Caps)

- GaN (11 Teams) / SiC (2 Teams) / Si (2 Teams)

ETHzürich

Source: whiskeybehavior.info

## Performance Limits / Future Requirements

- 220...250W/in<sup>3</sup> for Two-Level Bridge Leg + Unfolder

- 250...300W/in<sup>3</sup> for Highly Integrated Multi-Level Approach

- Isol. Distance Requirements Difficult to Fulfill

- Fulfilling Industrial Inp. Overvoltage Requirem. would Signific. Reduce Power Density

- Low Frequency (20kHz...120kHz) SiC vs. HF (200kHz...1.2MHz) GaN

- Multi-Cell Concepts for LV Si (or GaN) vs. Two-Level SiC (or GaN)

- New Integr. Control Circuits and *i*=0 Detection for Sw. Frequency >1MHz

- Integrated Gate Drivers & Switching Cells

- High Frequency Low Loss Magnetic Materials

- High Bandwidth Low-Volume Current Sensors

- Low Loss Ceramic Capacitors Tolerating Large AC Ripple

- Passives w. Integr. Heat Management and Sensors

- 3D Packaging

- New U-I-Probes Required for Ultra-Compact Conv. R&D

- Specific Systems for Testing  $\rightarrow$  Devices Equipped with Integr. Measurement Functions

- Convergence of Sim. & Measurem. Tools  $\rightarrow$  Next Gen. Oscilloscope

- New Multi-Obj. Multi-Domain Simulation/Optim. Tools

# **Thank You!**

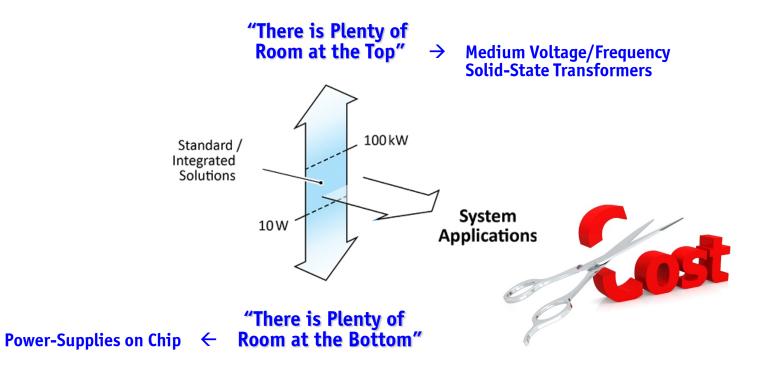

#### **Future Development 1/2**

- **Commoditization / Standardization**

- Extreme Cost Pressure (!)

**Key Importance of Technology Partnerships of Academia & Industry**

ETHzürich

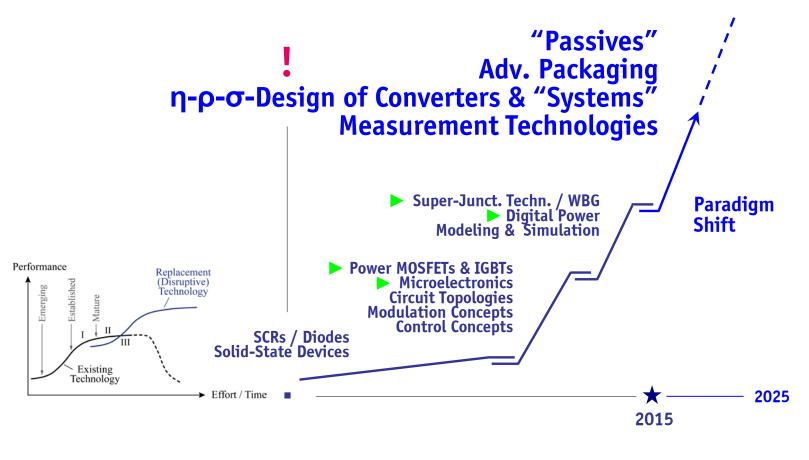

#### **Future Development 2/2**

**Extrapolation of Technology S-Curve**

STS-

#### **Technology Progress – Technology Push**

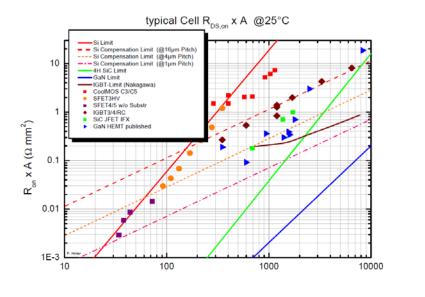

- WBG Semiconductor Technology

Microelectronics

- → Higher Efficiency, Lower Complexity

→ More Computing Power

$\rightarrow$  + Advanced Packaging (!)

**ETH** zürich

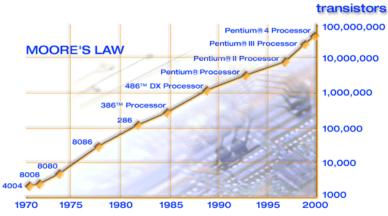

→ Moore's Law

#### System / Smart Grid Drivers

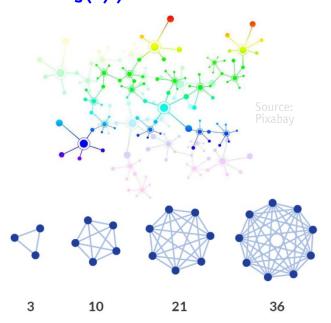

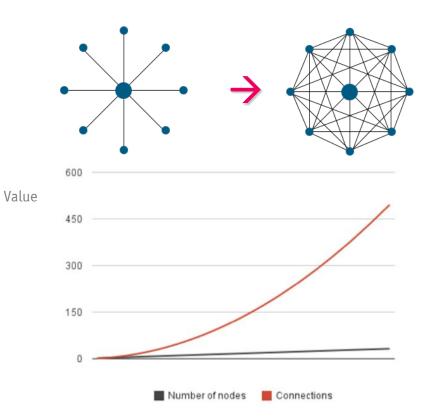

- Metcalfe's Law

- Moving form Hub-Based Concept to Community Concept Increases Potential Network Value Exponentially (~n(n-1) or ~n log(n) )

#### Technology Sensitivity Analysis Based on η-ρ-Pareto Front

# Sensitivity to Technology Advancements Trade-off Analysis

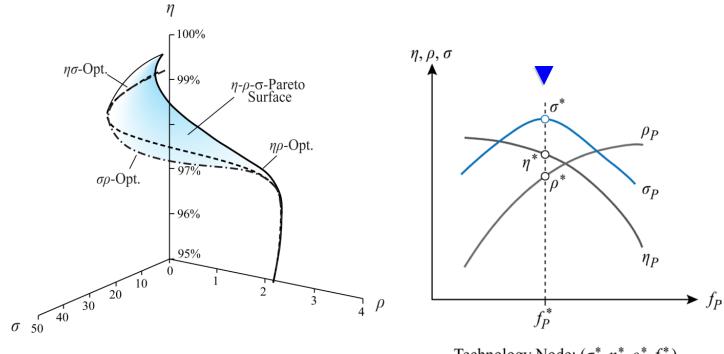

# Converter Performance Evaluation Based on $\eta$ - $\rho$ - $\sigma$ -Pareto Surface

**σ**: kW/\$

# Converter Performance Evaluation Based on $\eta$ - $\rho$ - $\sigma$ -Pareto Surface

#### 'Technology Node'

Technology Node:  $(\sigma^*, \eta^*, \rho^*, f_P^*)$

#### **Future Development**

|            | <ul> <li>Minimize / Avoid Packages → (PCB) Embedding</li> <li>Integrate Driver Stage</li> <li>Integrate Sensors / Monitoring</li> <li>Multiple Use of Isolated Gate Drive Communication Channel</li> <li>Offer Test Devices with Integrated Measurement Function</li> <li>Facilitate (Double Sided) Heat Extraction</li> </ul> |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Converters | <ul> <li>Standardized Very Low Cost Building Blocks</li> <li>"Application Specific" = Wide Operating Range Standardized Blocks</li> <li>Self-Parametrization</li> <li>Bidirectional Converters</li> </ul>                                                                                                                      |

| 5          | <ul> <li>AC and DC Distribution</li> <li>Single Converter vs. Combination of Modules / Cells</li> <li>Initial Costs / Life Cylce Cost Trade-off</li> <li>Grid 4.0</li> </ul>                                                                                                                                                   |

| -          | <ul> <li>Minimize Design Time / Fully Computerized</li> <li>Maximize Design Flexibility for Appl. Specific Solution (PCB)</li> <li>Maximize Design Insight for Trade-off Analysis</li> <li>Design for Manufacturing (Planar / PCB Based)</li> </ul>                                                                            |

| Literature | - More & More "White Noise"                                                                                                                                                                                                                                                                                                    |