# 98.5% / 1.5kW/dm<sup>3</sup> Multi-Cell Telecom Rectifier Module (230VAC/48VDC) – Breaking the Pareto Limit of Conventional Converter Approaches

#### M. Kasper and J. W. Kolar

Swiss Federal Institute of Technology (ETH) Zurich Power Electronic Systems Laboratory www.pes.ee.ethz.ch **G. Deboy** Infineon Technologies Austria AG www.infineon.com

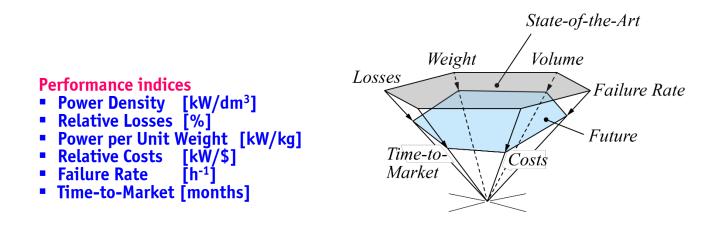

### Motivation

Leverage advantages of the multi-cell approach

- higher effective switching frequency due to phase shift

- Iower filtering effort due to the cancellation of harmonics

- use of low-rated semiconductor devices

- improved thermal behavior due to a better surface-to-volume ratio

in order to shift the performance indices of power electronic converters to new levels.

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

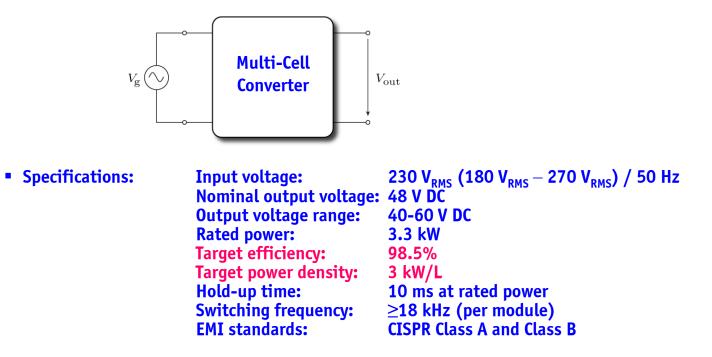

### Target Application

Telecom Rectifier Module

24/7 Always ON operation > driver for high efficiency

Output characteristics: Voltage source and current source

### Benchmark: "Conventional" 3.3kW Telecom Rectifier Module

3x Interleaved TCM PFC Rectifier Stages

2x Interleaved Full-Bridge Phase-Shift DC/DC Conv. / Full-Bridge Synchr. Rectifier

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

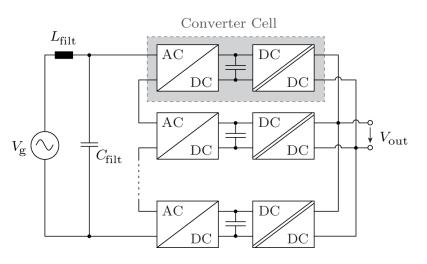

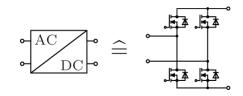

# Multi-Cell Telecom Rectifier

# Multiple converter cells connected in Input Series Output Parallel (ISOP) connection Natural step down ratio of 1/N<sub>cell</sub>

- Each converter cell consisting of a

- Full bridge rectification

- Isolated DC-DC converter

Totem Pole

Phase Shift Full Bridge w/ sync. rect.

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

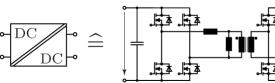

# Degrees of Freedom in Multi-Cell Converters Optimizations

Converter realization possibilities

Calculation of <u>losses</u> and <u>volumes</u> for all (!) design combinations

# Optimization Setup and Converter Modelling

Analytic modelling of losses and volumes necessary for optimization

#### **MOSFET**s

- Conduction losses

- Switching losses

- Heat sink volume

#### **Inductive components**

- Core losses

- Winding losses

#### **Electrolyte DC-link capacitors**

ESR and leak. curr. losses

#### **Input filter**

#### **Auxiliary losses**

RMS current values

$$\begin{array}{c} U_{Sw}, I_{Sw}, T_{Sw} \\ \hline C_{OSS}(A_{Chip}), Q_{rr}(A_{Chip}), C_{GD}(A_{Chip}) \\ \hline P \\ \hline \end{array}$$

$$\blacktriangleright R_{\text{Th,JC}}(A_{\text{Chip}}), \text{CSPI}$$

Find optimal A<sub>Chip</sub>

- ► iGSE (improved generalized Steinmetz equation)

- DC and AC losses (skin & proximity effect)

- ▶ RMS current @ 100Hz & *f*<sub>sw</sub>

- Volume

- **Central controller and aux. electronics per module**

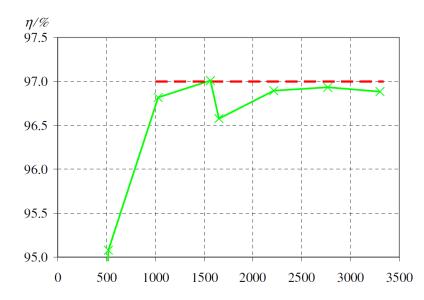

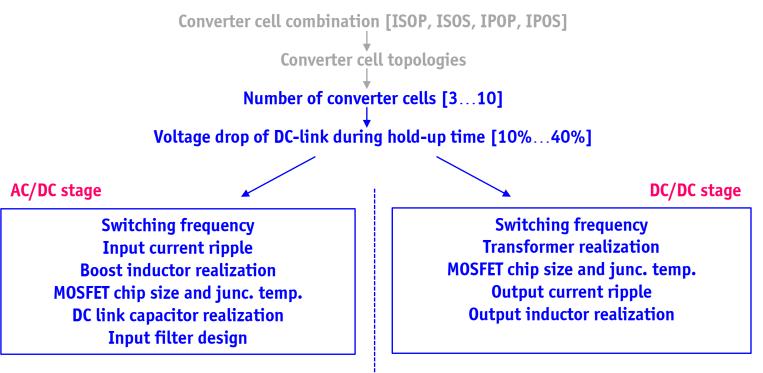

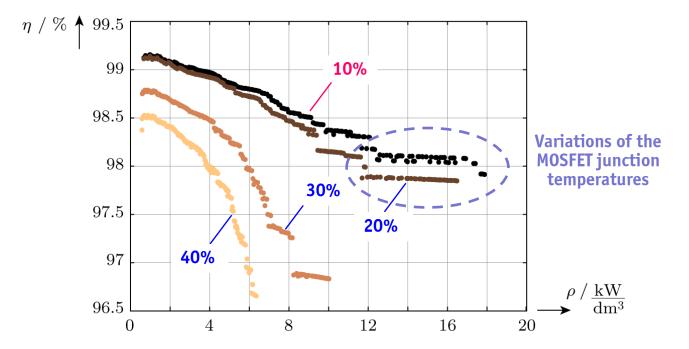

# **Full System Optimization Results**

- Pareto optimal results for full load operation.

- Determination of the optimal number of converter cells.

- Voltage drop of the DC-link voltage during hold-up time 20%.

Choose N = 6 due to lower communication and hardware realization efforts.

# **Full System Optimization Results**

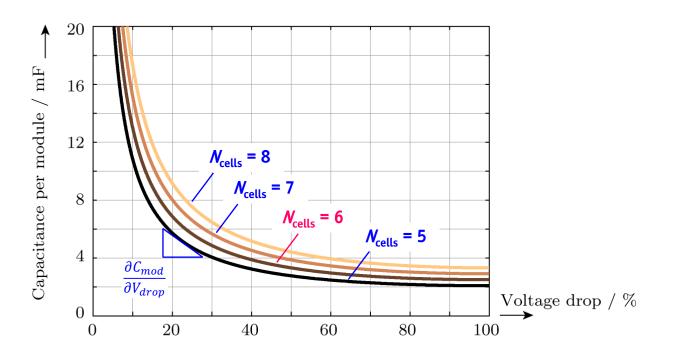

- Determination of Pareto optimal voltage drop of the DC-link voltage during 10 ms hold-up time

- Number of converter cells *N* = 6

Which trade-offs lead to 20% voltage drop of the DC-link during the hold-up time as best value?

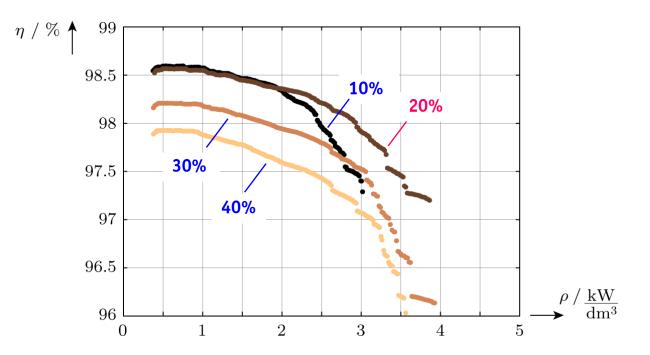

# Optimization Results: AC/DC Rectifier Stage

- Pareto-optimal results for the PFC stage for different permissible DC-link voltage drops

- Number of cells N = 6

Main influence on efficiency/power-density by DC-link electrolyte capacitors.

# Optimization Results: AC/DC Rectifier Stage

Required capacitance per module for different number of cells N<sub>cells</sub> vs. the voltage drop during the hold-up time.

A voltage drop of 20% ... 30% is a reasonable choice with respect to the required capacitance.

Larger voltage drop → lower capacitance (and volume) → larger ESR (and losses)

# **Summary of Results for the AC/DC Rectifier Stage**

#### A larger voltage drop leads to

- ► larger capacitor losses due to a larger ESR.

- a smaller capacitor volume since less capacitance is needed.

- no change in MOSFET losses.

- no change in inductor losses.

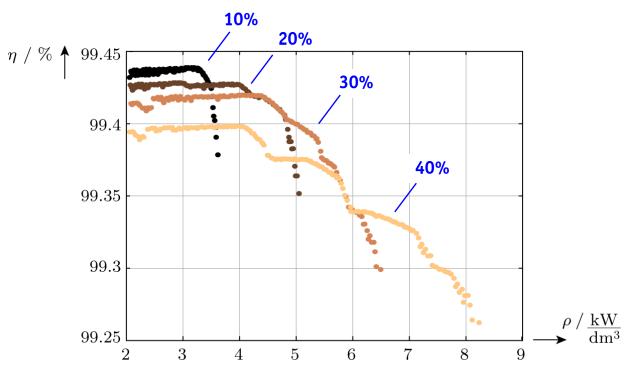

# Optimization Results: DC/DC Converter Stage

- Pareto-optimal results of the Phase-Shift Full Bridge converter stage.

- Number of converter cells N = 6.

► The performance improves with lower permissible voltage drop values during the hold-up time.

### Summary of Results for the DC/DC Converter Stage

#### A larger voltage drop leads to

- ► a larger output inductance and thus either higher losses or a larger volume.

- ▶ higher transformer losses since a lower duty cycle and a larger turns ratio are required (→ less winding area per turn and higher RMS currents).

- ▶ larger RMS current values in the primary full-bridge MOŚFETs.

- larger reverse recovery losses due to a higher blocking voltage.

### **Final System**

#### Parameters of the final system

- Efficiency: 98.5% @ P<sub>load</sub> = 0.8 P<sub>rated</sub>

- Power density: 1.5 kW/L

- $\blacktriangleright$   $N_{\rm cells} = 6$

- Voltage drop during hold-up time: 20 %

- AC/DC rectifier stages

- Sw. freq.: 18 kHz (per cell)

- Boost inductor: 8 µH, 2x E 34/14/9, Metglas

- DC-bus capacitors: 4x 2.2 mF

- Total DC link voltage: 400V

- MOSFETs: BSC046N10NS3 / Infineon @ T<sub>i</sub> = 75°C

- Isolated DC/DC converters

- Sw. freq.: 100 kHz

- Transformer: 2x E 47/20/16, N87

- Inductor: 41 μH, E 47/20/16, N87

- MOSFETs: BSC046N10NS3 / Infineon @ T<sub>i</sub> = 60°C

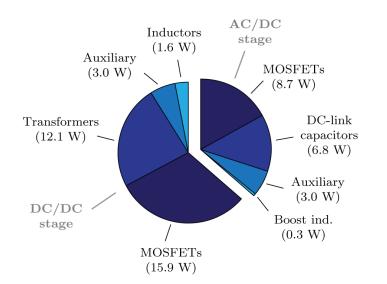

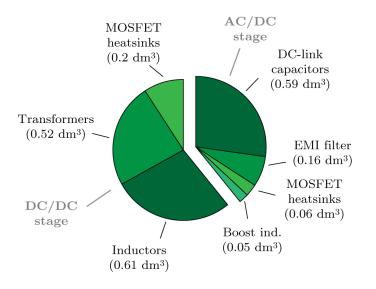

### **Final System**

Loss distribution (at full load operation)

Volume distribution

|             |       | Losses | Volumes                     |

|-------------|-------|--------|-----------------------------|

| AC/DC stage |       |        | <b>0.86</b> dm <sup>3</sup> |

| DC/DC stage |       | 32.6 W | <b>1.33</b> dm <sup>3</sup> |

|             | Total | 51.4 W | <b>2.19</b> dm <sup>3</sup> |

### Conclusions and Outlook

- The benefits of the ISOP multi-cell converter approach allow to achieve efficiencies beyond the barriers of state-of-the-art systems.

- ► A comprehensive system optimization yields

- an optimum number of converter cells

- an optimum permissible voltage drop in the DC-link

- an efficiency/power-density Pareto front for the entire system for all possible combinations of AC-DC rectifier and DC-DC converter stages.

- A design with an efficiency of 98.5% at a power density of 1.5 kW/dm<sup>3</sup>

**Future work**

Experimental verification of optimization results

### Thank you very much for your attention!

### Please feel free to ask questions