Expert Discussion on "Design Automation and Next Generation Measurement Technologies in Power Electronics"

# **Power Electronics Design 4.0**

#### Johann W. Kolar

Swiss Federal Institute of Technology (ETH) Zurich Power Electronic Systems Laboratory www.pes.ee.ethz.ch

July 19, 2019

# **Outline**

Power Electronics Performance Trends

X-Concepts / "Moon-Shot" Technologies

Power Electronics Design 4.0

J. Azurza T. Guillod Acknowledgement: F. Krismer

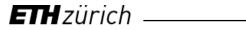

#### **Required Performance Improvements**

■ Future → Cost / Cost / Cost & Robustness & Availability & Recyclability

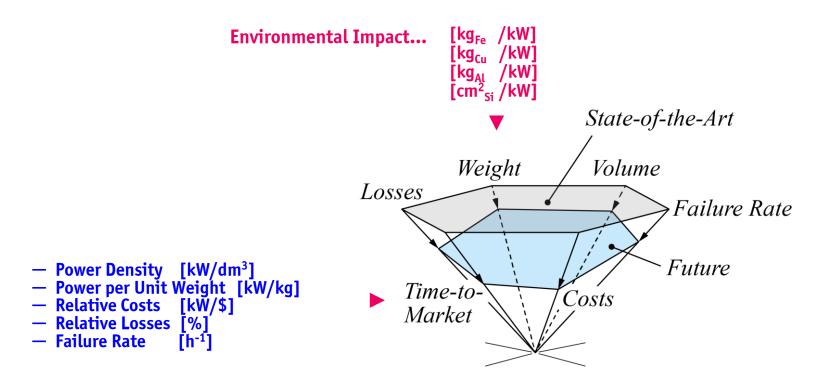

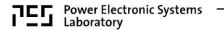

#### S-Curve of Power Electronics

- **Power Electronics 1.0**  $\rightarrow$  **Power Electronics 4.0**

- Identify "X-Concepts" / "Moon-Shot" Technologies 10 x Improvement NOT Only 10% !

Power Electronic Systems בבה Laboratory

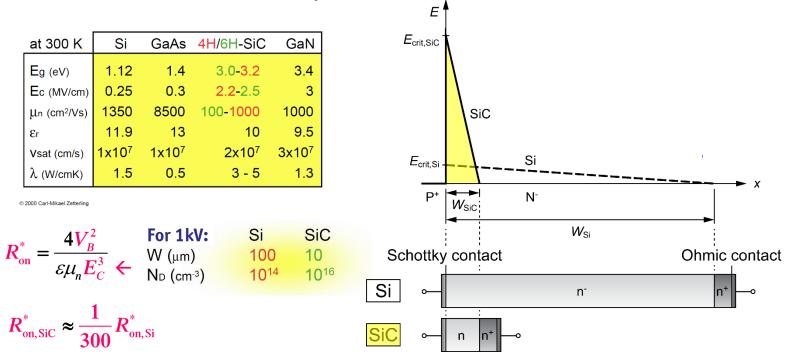

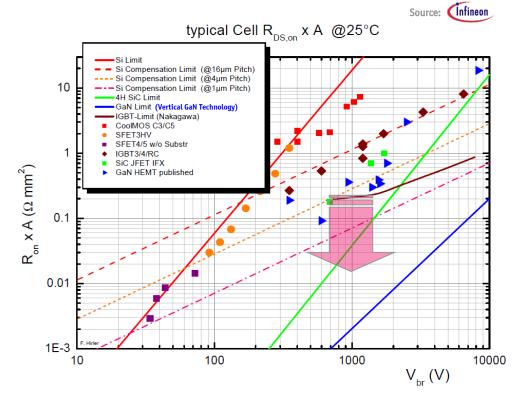

## Low R<sub>DS(on)</sub> High-Voltage Devices 1/2

- High Critical E-Field of SiC  $\rightarrow$  Thinner Drift Layer High Maximum Junction Temperature  $T_{j,max}$

Massive Reduction of Relative On-Resistance  $\rightarrow$  High Blocking Voltage Unipolar Devices

**ETH** zürich

## Low R<sub>DS(on)</sub> High-Voltage Devices 2/2

- SiC / GaN (Monolithic AC-Switch & Integration)

Low Circuit Complexity

- High Efficiency

• High Heat Conductivity & Excellent Switching Performance

4/30

**ETH** zürich

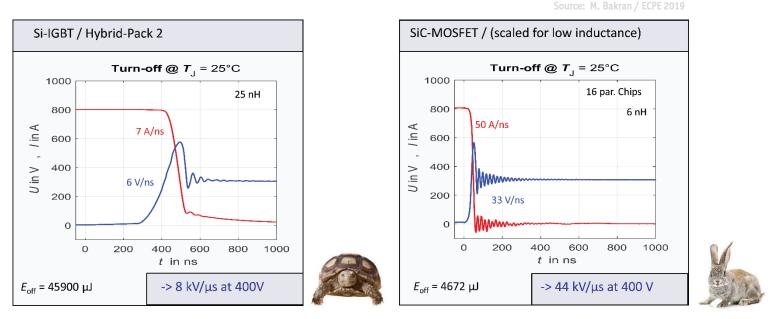

#### Low Switching Losses

- Si-IGBT  $\rightarrow$  Up to 6.5kV / Rel. Low Switching Speed SiC-MOSFETs  $\rightarrow$  Up to 15kV (1<sup>st</sup> Samples) / Factor 10...100 Higher Sw. Speed Si-IGBT

Extremely High di/dt & dv/dt  $\rightarrow$  Challenges in Packaging / EMI •

Idea: F.C. Lee

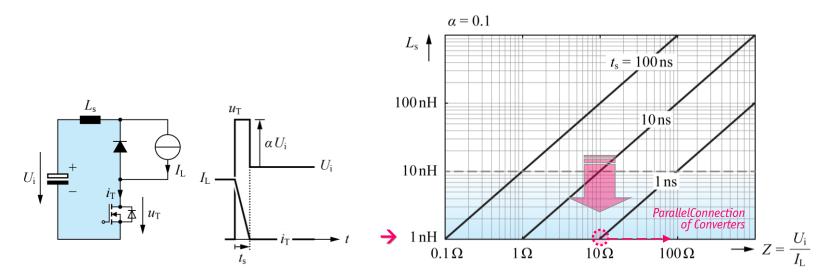

#### **Circuit Parasitics**

- Extremely High di/dt

- **Commutation Loop Inductance L**<sub>s</sub> Allowed L<sub>s</sub> Directly Related to Switching Time  $t_s \rightarrow$

Advanced Packaging / Design & Parallel Interleaving for Partitioning of Large Currents

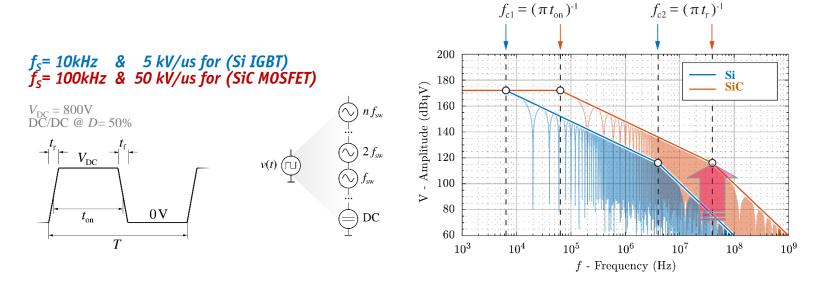

#### **EMI Emissions**

- Higher dv/dt  $\rightarrow$  Factor 10

- Higher Switching Frequencies → Factor EMI Envelope Shifted to Higher Frequencies  $\rightarrow$  Factor 10

• Influence of Filter Component Parasitics and Couplings  $\rightarrow$  Advanced Packaging / Design

7/30

Idea: M. Schutten

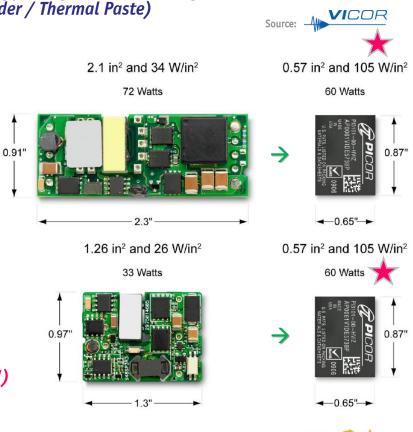

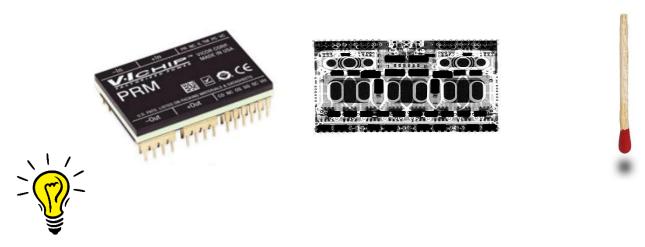

#### **3D-Packaging / Heterogeneous Integration**

- System in Package (SiP) Approach Minim. of Parasitic Inductances / EMI Shielding / Integr. Thermal Management Very High Power Density (No Bond Wires / Solder / Thermal Paste)

- Automated Manufacturing

- Future Application Up to 100kW (!)

- New Design Tools & Measurement Systems (!)

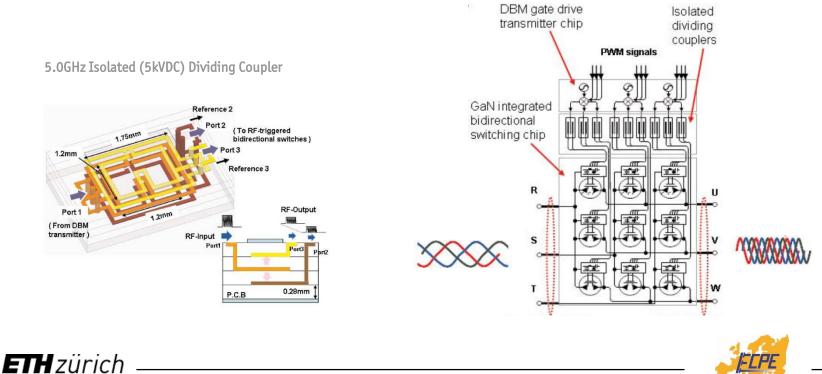

#### Monolithic 3D-Integration

Source: Panasonic ISSCC 2014

- GaN 3x3 Matrix Converter Chipset with Drive-By-Microwave (DBM) Technology

- 9 Dual-Gate GaN AC-Switches

- DBM Gate Drive Transmitter Chip & Isolating Couplers

- Ultra Compact  $\rightarrow 25 \times 18 \text{ mm}^2$  (600V, 10A 5kW Motor) \_

No Access to Inner Details / Only Terminal Waveforms Available for Measurement (!)

- Convergence of Design / Simulation & Measurement Tools  $\rightarrow$  Augmented Reality Oscilloscope

- *Measured* Signals & *Simulated* Inner Voltages/Currents/Temp. Displayed Simultaneously Automatic Tuning of Simulation Parameter Models for Best Fit of Simulated/Measured Waveforms

#### **Digital Integrated Circuits**

- Exponentially Improving uC / Storage Technology (!)

- Extreme Levels of Density / Processing Speed Software Defined Functions / Flexibility

- Cont. Relative Cost Reduction

- *Fully Digital Control of Complex Systems (Capability of Managing Complexity)*

- Massive Comput. Power & Cloud  $\rightarrow$  Fully Automated Design & Manufacturing / Industrial IoT (IIoT)

Automated Design \_\_\_\_\_

\_\_\_\_\_

#### Automated Design 1/4

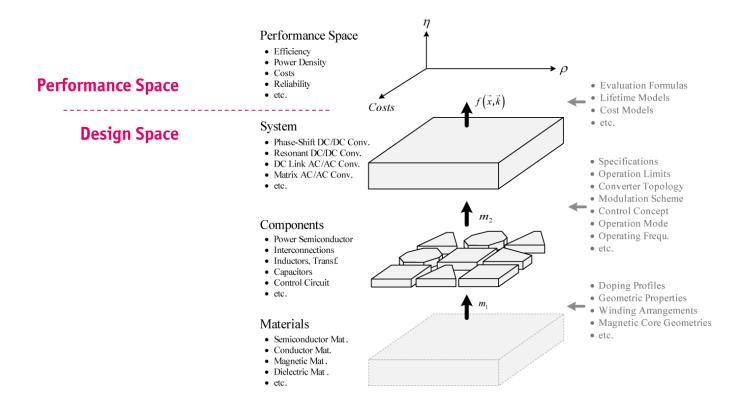

• Mathematical Description of the Mapping "Technologies"  $\rightarrow$  "System Performance"

#### Automated Design 2/4 Specifications $V_I, V_O, P_O, \Delta v_O, \text{CISPR } 11/22 \text{ A,B}$ Mathematical Models of Main Converter Topology Modulation Scheme Converter Components & **Interactions** Component Values, fp Electric Power Circuit Model $\hat{I}_L / I_{L,rms}$ I<sub>C.rms</sub> Irms /Iavg $i_i(t) / v_i(t)$ CM Noise DM Noise Transformer / Inductor Semiconductor Capacitor Model Model · Windings Geom. Type Type Minimum Losses or Volume • Wire Type $A_{CM}^*$ $A_{DM}^*$ · Core Geom. Off-line Optimized DM/CM • Core Type Filter Topology Loss Model $C_{DM}$ $C_{CM}$ $L_{DM}/L_{CM}$ Reluctance Model Loss Model $T_i$ Filter Filter Inductor Capacitor Geometry $\Phi / \Phi_{rms}$ Material Type Thermal Model Loss Model Min. Windings Losses $R_{th}^*$ • Core Loss Model Loss Model $B \leq B_S$ $T_C / T_W$ $T \leq T_{Max}$ Off-line $T_C/T_W$ $V \leq V_{Max}$ Optimized Thermal Min. Thermal Model Heat Sink Model Vol. Heat Transformer Semic Capacitor Capacitor Inductor Sink EMI Filter EMI Filter EMI Filter EMI Filter Losses Volume Losses Volume Volume Cap. Vol Cap. Losses Ind. Losses Ind. Vol. Summation of Component Volumes and Losses Total Converter Volume / Losses

• Multi-Objective Optimization - Guarantees Best Utilization of All Degrees of Freedom (!)

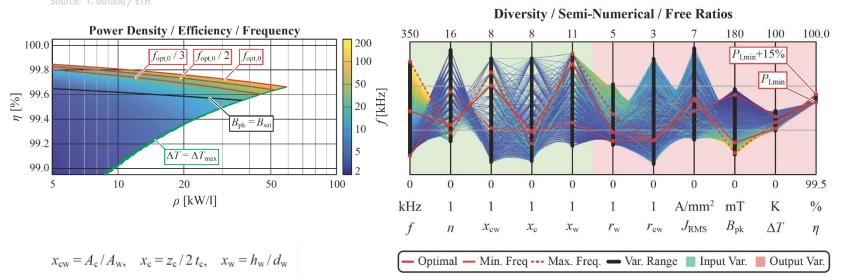

#### Automated Design 3/4

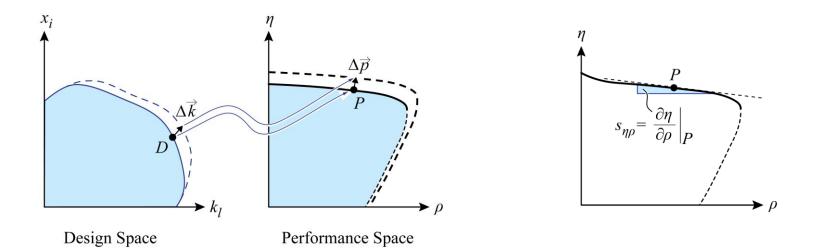

- Based on Mathematical Model of the Technology Mapping Multi-Objective Optimization  $\rightarrow$  Best Utilization of the "Design Space" Identifies Absolute Performance Limits  $\rightarrow$  Pareto Front / Surface

- Clarifies Sensitivity  $\Delta \vec{p} / \Delta \vec{k}$  to Improvements of Technologies & Power Density Limit

- Trade-Off Analysis

**ETH** zürich

#### Automated Design 4/4

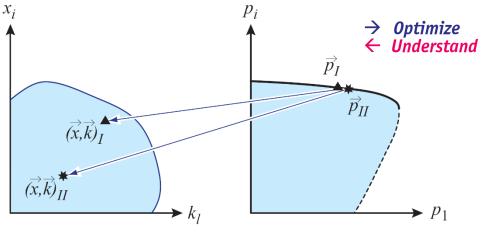

- **Design Space Diversity**

- Equal Performance for Largely Different Sets of Design Parameters (!)

**Design Space**

Performance Space

- E.g. Mutual Compensation of Volume and Loss Contributions (e.g. Cond. & Sw. Losses) Allows Optimization for Further Performance Index (e.g. Costs)

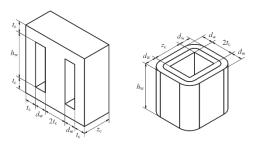

- **Design of a Medium-Frequency Transformer**

- Wdg./Core Loss Ratio, Geometry, n etc. as Design Parameters

- Power Level & Power Density = const.

- Mutual Compensation Core & Winding Losses Changes

- Limit on Part Load Efficiency / Costs / Fixed Geometry → Restricts Diversity

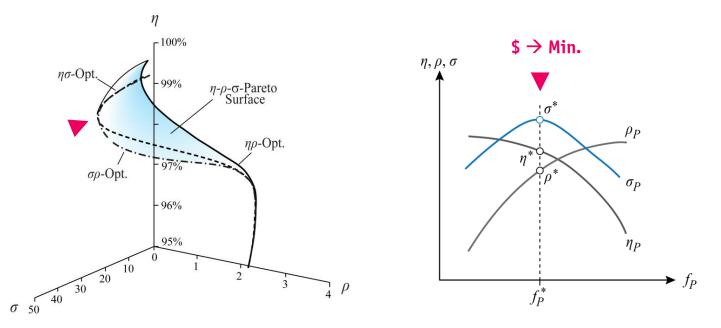

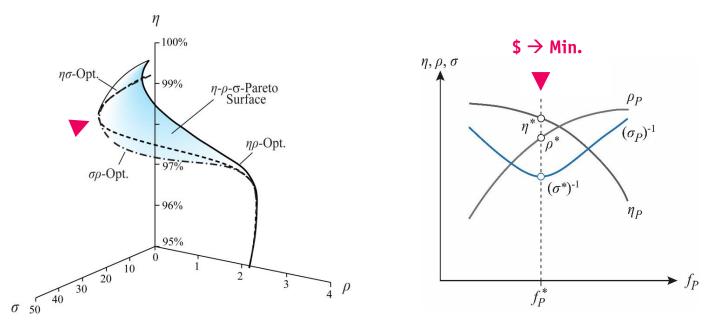

# Converter Performance Evaluation Based on $\eta$ - $\rho$ - $\sigma$ -Pareto Surface

- **Definition of a Power Electronics "Technology Node"**  $\rightarrow$  ( $\eta^*, \rho^*, \sigma^*, f_{\rho^*}$ )

- Maximum σ [kW/\$], Related Efficiency & Power Density

- Specifying Only a Single Performance Index is of No Value (!)

- Achievable Perform. Depends on Conv. Type / Specs (e.g. Volt. Range) / Side Cond. (e.g. Cooling)

# Converter Performance Evaluation Based on $\eta$ - $\rho$ - $\sigma$ -Pareto Surface

- **Definition of a Power Electronics "Technology Node"**  $\rightarrow$  ( $\eta^*, \rho^*, \sigma^*, f_{\rho^*}$ )

- Maximum σ [kW/\$], Related Efficiency & Power Density

- Specifying Only a Single Performance Index is of No Value (!)

- Achievable Perform. Depends on Conv. Type / Specs (e.g. Volt. Range) / Side Cond. (e.g. Cooling)

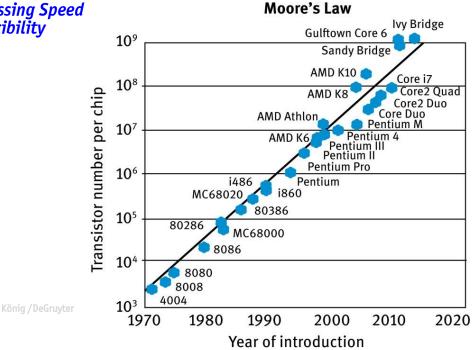

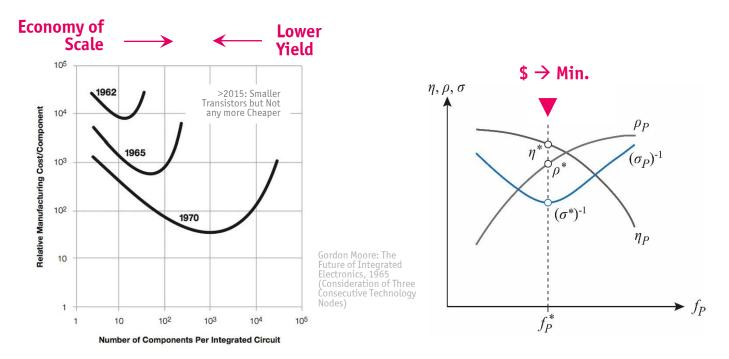

#### Comparison to "Moores Law"

- "Moores Law" Defines Consecutive Techn. Nodes Based on Min. Costs per Integr. Circuit (!)

- Complexity for Min. Comp. Costs Increases approx. by Factor of 2 / Year

• Definition of " $\eta^*, \rho^*, \sigma^*, f_{\rho}^*$ -Node" Must Consider Conv. Type / Operating Range etc. (!)

Digital Twin / Industry 4.0 \_\_\_\_\_

\_\_\_\_\_

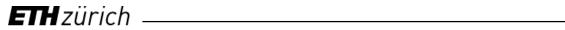

#### **IIoT in Power Electronics**

- Digital Twin → Physics-Based Digital Mirror Image

- **Digital Thread**  $\rightarrow$  "Weaving" Real/Physical & Virtual World Together

- Requires Proper Interfaces for Models & Automated Design

- Model of System's Past/Current/Future State → Design Corrections / Prev. Maintenance etc.

#### History and Development of the **Electronic Power Converter**

E. L. PHILLIPI

NONMEMBER AIEE

E. F. W. ALEXANDERSON FELLOW AIEE

THE TERM "electronic power converter" needs some definition. The object may be to convert power from direct current to alternating current for d-c power transmission, or to convert power from one frequency into another. or to serve as a commutator for operating an a-c motor at variable speed, or for transforming high-voltage direct current into low-voltage direct current. Other objectives may be mentioned. It is thus evidently not the objective but the means which characterizes the electronic power converter. Other names have been used tentatively but have not been accepted. The emphasis is on electronic means and the term is limited to conversion of power as distinguished from electric energy for purposes of communication. Thus the name is a definition.

Paper 44-143, recommended by the AIEE committee on electronics for presentation at the AIEE summer technical meeting, St. Louis, Mo., June 26-30, 1944. Manuscript submitted April 25, 1944 made available for printing May 18, 1944.

E. F. W. ALEXANDERSON and E. L. PHILLIPI are with the General Electric Company, Schenectady, N. Y.

**ETH** zürich

Alexanderson, Phillipi-Electronic Converter

ELECTRICAL ENGINEERING

4143-D-C LINK OR TRANSMISSION LINE

- Basic Topologies Known > 30...40 Years

Min. Complexity Circuits Used in Industry

Optimization of Modulation / Control "Completed"

Several Solutions of Equal Performance

... "Refinements" & Interleaving & Hybrid SCCs & Comparative Evaluation (!)

22/30

SCC ... Switched Capacitor Converters

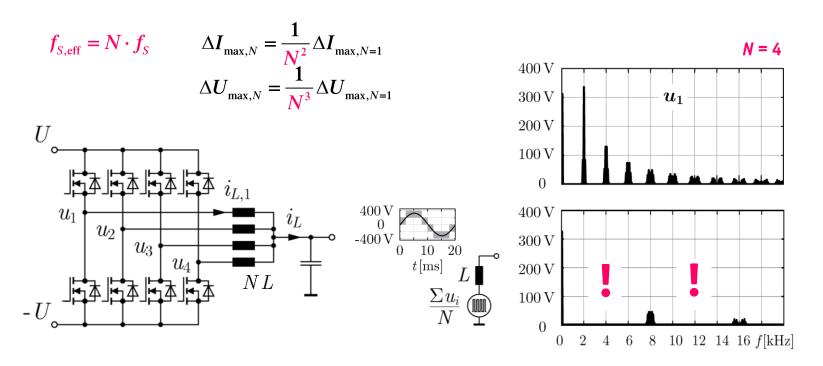

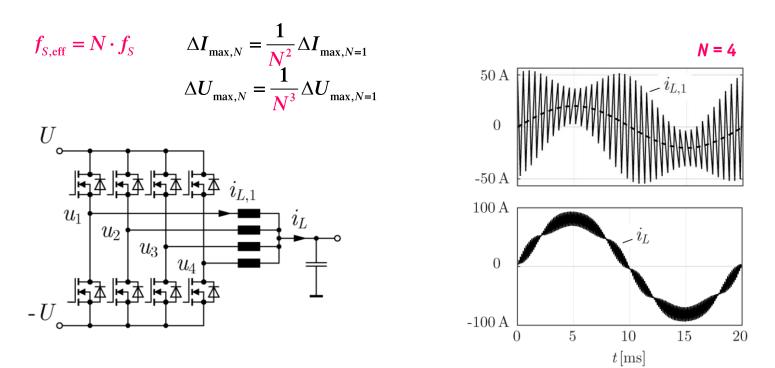

#### Parallel Interleaving 1/2

Loss-Neutral Multiplication of Switching Frequency Reduced Ripple @ Same (!) Switching Losses

• Scalability / Manufacturability / Standardization / Impedance Matching / Redundancy

#### Parallel Interleaving 2/2

- Loss-Neutral Multiplication of Switching Frequency Reduced Ripple @ Same (!) Switching Losses

• Scalability / Manufacturability / Standardization / Impedance Matching / Redundancy

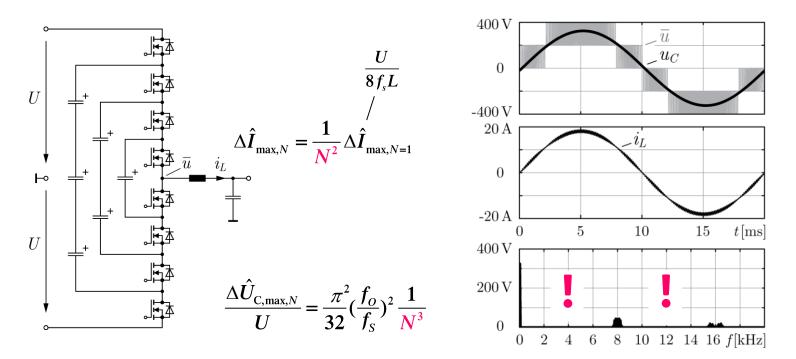

#### Series Interleaving 1/2

- Reduced Ripple @ Same (!) Switching Losses Lower On-Resistance @ Given Blocking Voltage  $\rightarrow$  1+1=2 NOT 2<sup>2</sup> = 4 (!) Extends LV Technology to HV

• Scalability / Manufacturability / Standardization / Impedance Matching / Redundancy

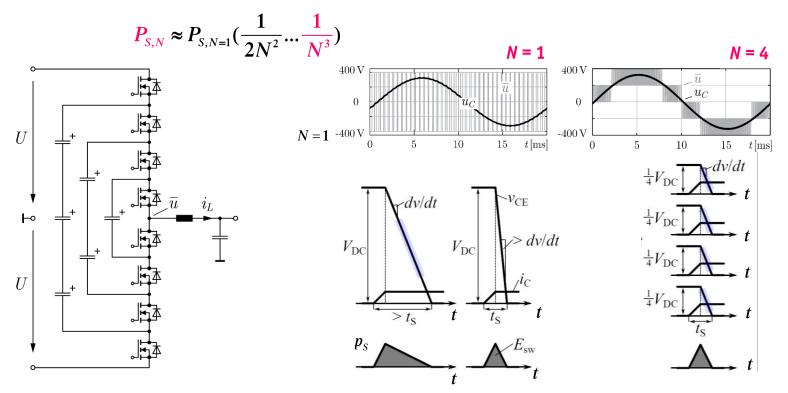

#### Series Interleaving 2/2

Dramatically Reduced Switching Losses (or Harmonics) for Same di/dt and dv/dt

● High Efficiency @ High Effective Switching Frequency → High Power Density

FEPE

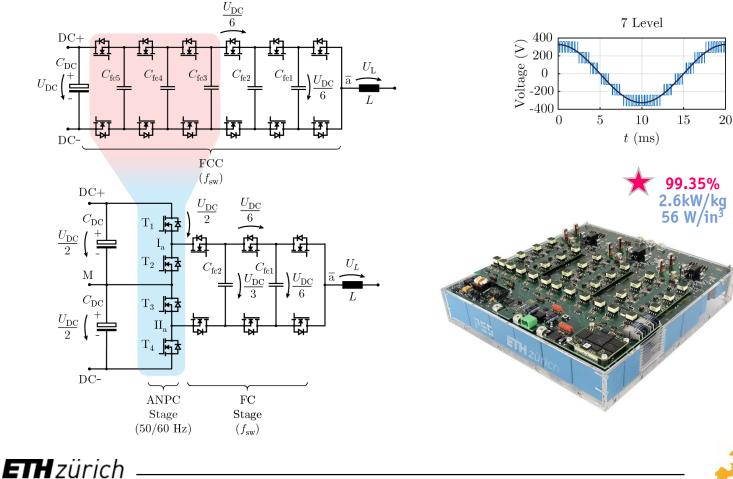

#### Series Interleaving – Example

■ Realization of a 99%++ Efficient 10kW 3-Φ 400V<sub>rms,ll</sub> Inverter System

■ 7-Level Hybrid Active NPC Topology / LV Si-Technology

#### 28/30

#### S-Curve of Power Electronics

- Power Electronics  $1.0 \rightarrow$  Power Electronics 4.0

- Identify "X-Concepts" / "Moon-Shot" Technologies 10 x Improvement NOT Only 10% !

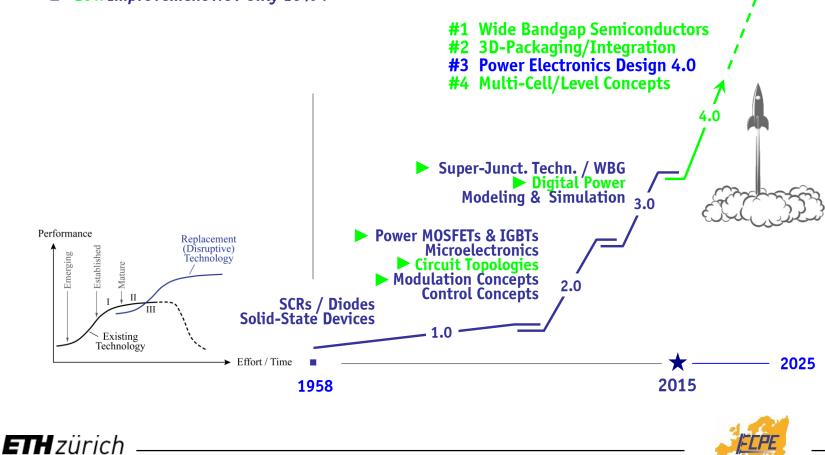

#### Automated Design Roadmap

- **End-to-End Horizon** of Modeling & Simulation

- Design for Cost / Volume / Efficiency Target / Manufacturing / Testing / Reliability / Recycling

• AI-Based "Summaries" → No Other Way to Survive in a World of Exp. Increasing # of Publications (!)

### Conclusions

**Challenges in Modeling & Simulation**

- Improvement & Combination of Analytic, Equiv. Circuit, FEM, Hybrid Red. Order Models Models in Certain Areas Largely Missing (Costs, EMI, Reliability, Manufacturability, etc.) \_

- Strategies for Hierarchical Structuring of Modeling (Doping Profile  $\rightarrow$  Mission Profile)

- Strategies for Comput. Efficient Design Space Exploration & Multi-Obj. Simulation

- Sensitivity of Performance Prediction to Model Inaccuracies Largely Unknown

- Design Space Diversity and Performance Sensitivities Not Utilized -

- AI Not Yet Utilized

- **Challenges of Company-Wide Introduction**

- No Readily Available Software -

- Company-Wide Model Updates & Software Updates

- Complete Restructuring of Engineering Departments

- License Costs

- etc.

... "The Train Has Just Left the Station" (!)

30/30

ETH zürich

# Thank you!

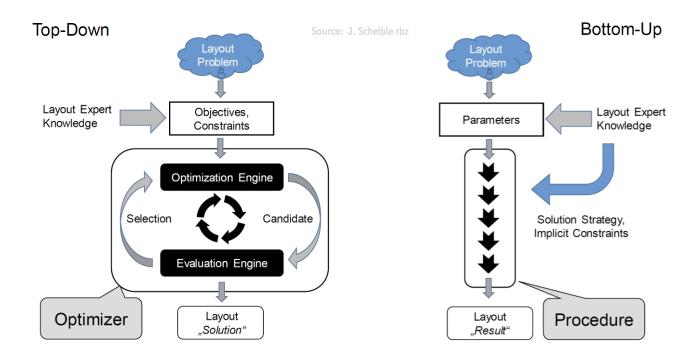

#### Manual Design Automation Strategies

- Example of Analog Integrated Circuit Design Automation

- "Top-Down" Optimization (Repetitive Refinement) vs. "Bottom-Up" Procedures

- Top-Down  $\rightarrow$  Limited to Aspects Described in the Models / All Parasitics Must be Modelled ! • Pattern Up  $\rightarrow$  Manual Design Process Translated into Executable Script Steered by an Expert

- Bottom-Up  $\rightarrow$  Manual Design Process Translated into Executable Script Steered by an Expert

A-1

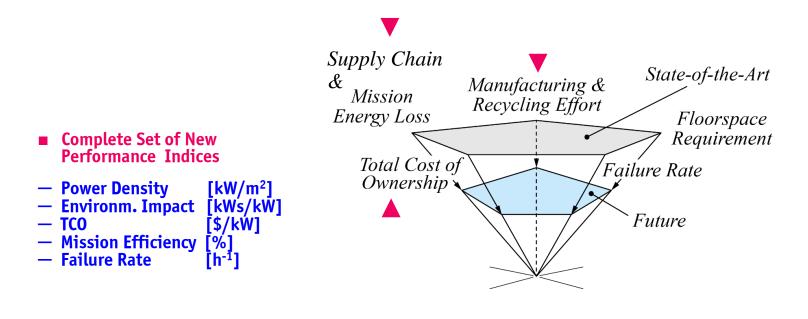

#### Power Electronics $\rightarrow$ Energy Electronics

Source: www.roadtrafficsigns.com

### "Energy" Electronics

- Design Considering Converters as "Integrated Circuits" (PEBBs)

- Extend Analysis to Converter Clusters / Power Supply Chains / etc.

- "Converter" "Time"

"Power"

$\rightarrow$  "Systems" (Microgrid) or "Hybrid Systems" (Automation / Aircraft)  $\rightarrow$  "Integral over Time"  $\rightarrow$  "Energy"

$$p(t) \rightarrow \int_{0}^{t} p(t) dt$$

- Power Conversion

- Converter Analysis

- Converter Stability

- Cap. Filtering

- Costs / Efficiency

- etc.

- → Energy Management / Distribution

- → System Analysis (incl. Interactions Conv. / Conv. or Load or Mains)

→ System Stability (Autonom. Cntrl of Distributed Converters)

→ Energy Storage & Demand Side Management

→ Life Cycle Costs / Mission Efficiency / Supply Chain Efficiency

**Power Electronic Systems** Laboratory

#### *New Power Electronics Systems Performance Figures/Trends*

A-3

ETH zürich