Diss. ETH No. 26935

## Analysis and Multi-Objective Evaluation of New Three-Phase PWM Inverter System

A thesis submitted to attain the degree of

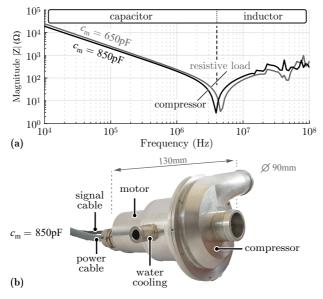

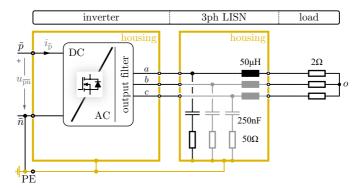

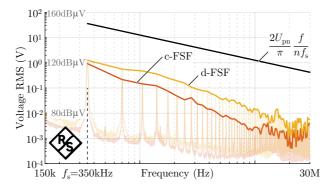

DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

presented by MICHAIL MARIOS ANTIVACHIS

> MSc ETH born on 19.08.1991 citizen of Greece

accepted on the recommendation of

Prof. Dr. Johann W. Kolar, examiner Prof. Dr. Hans-Peter Nee, co-examiner

2020

ETH Zurich Power Electronic Systems Laboratory Physikstrasse 3 | ETL H23 8092 Zurich | Switzerland

http://www.pes.ee.ethz.ch

© 2020, Michael Antivachis

To my Parents Nikolaos and Kalliopi

## Acknowledgments

**F**<sup>IRST I</sup> would like to thank Prof. Dr. Johann W. Kolar for giving me the opportunity to conduct my Ph.D. studies at the Power Electronic Systems Laboratory (PES) of ETH Zurich. I am thankful for the valuable ideas, discussions and especially the unlimited energy resources and contagious excitement for power electronics. I want to thank him especially for the opportunity to present my research results as part of international scientific tutorials at his side. Furthermore, I would like to thank Prof. Dr. Hans-Peter Nee of the KTH Royal Institute of Technology for his interest in my thesis and for being part of the examination committee.

I want to also express my sincere gratitude to the Swiss Innovation Agency (Innosuisse) for the financial funding of my PhD project. In addition, I would like to thank the industry partner of this Ph.D. thesis, Celeroton AG, for making this project possible and for the scientific support. In particular, Christof Zwyssig, Andreas Looser, Christoph Gammeter, Timon Achtnich and Maurice Fardel.

A big part of the whole experience is also the fantastic and motivating atmosphere at PES, to which my colleagues have contributed a major part. Here, I would like to thank especially my office mate Jannik Schafer for the engaging discussions and numerous laughs and memories we shared. Special thanks belong to Pantelis Papamanolis for the fantastic inductor script, and for being not only my colleague but also my flatmate since the first moment I came to Switzerland. I also thank Mattia Guacci, Jon Azurza and Pascal Niklaus for helping me solve the mysteries of power electronics and always keeping up the good mood. I would also like to thank Dominik Bortis for the guidance throughout the thesis and for sharing his deep knowledge in many discussions.

I will always remember our good times at PES, not only during the coffee breaks but also during the various PES festivities and conferences around the world. My thanks belong to my colleagues Pedro Bezerra, Julian Bohler, Reto Bonetti, Piotr Czyz, Michael Flankl, Christoph Gammeter, Rosario Giuffrida, Thomas Guillod, Michael Haider, Morris Heller, Emanuel Hubmann, Matthias Kasper, Gustavo Knabben, Oliver Knecht, Florian Krismer, Yunni Li, Mario Mauerer, David Menzi, Spasoje Miric, Dominik Neumayr, Gwendolin Rohner, Marc Rothlisberger, Daniel Rothmund, Marcel Schuck, Lukas Schrittwieser, Arda Tuysuz and Daifei Zhang.

My gratitude and appreciation goes to the PES administration for their continuous support, namely Monica Kohn-Müller, Roswitha Coccia, Peter

Seitz, Prisca Maurantonio, Yvonne Schnyder-Lieberherr and Marina Eisenstat.

I have also had the pleasure to supervise numerous talented students during their master or semester projects, which contributed to this thesis with their work. In particular, Ander Aliva, Nicolas Kleynhans, David Lehmann, David Menzi, Daniel Ritzmann, Andrej Stankovski and Dan Wu.

I would also like to thank all my friends in Zurich and Greece with whom we had many adventures and trips together, and made my life colourful. A special thank you belongs to my girlfriend Irina for the support during this intense phase of my life. Last but not least, I wish to thank my parents for everything.

> Zurich, June 2020 Michael Antivachis

## Abstract

C URRENTLY the transportation sector accounts for a quarter of global  $CO_2$  emissions. In order to decarbonize the transportation, a transition from internal combustion engine vehicles (ICV) to fully electric vehicles (EV) is necessary. Motor drive systems are a key component of EVs, thus innovation in power electronics and motor technology will partly determine the adoption rate of EVs.

This thesis focuses on the energy storage system of a fuel-cell electric vehicle (FCEV). In particular, each fuel-cell unit requires a continuous supply of oxygen, which is provided by means of an auxiliary, electric compressor. A compressor drive system, supplied by the fuel-cell or a battery controls the electric compressor. The examined compressor drive is placed onboard a FCEV, thus is expected to be compact and lightweight. It is well documented in literature, that high-speed motors/compressors benefit from a small volume, thus are ideal for power dense drive systems. However, until now there is no comprehensive analysis of inverter systems tailored to the special characteristics of high-speed motors. This thesis aims to bridge this technical gap, by exploring the performance limits of high-speed motor drives.

In the first part of the thesis, a conventional voltage source inverter (VSI) is paired with a high-speed motor. High-speed motors are sensitive to poor stator current quality, that induces high rotor losses. For this reason, an output filter must be added at the inverter AC output-side. Different types of output filter are discussed here, concluding that a full sine-wave output filter (FSF) fits best the needs of high-speed motor drives. An FSF adds volume/losses, thus negatively affects the inverter stage performance. Two new modulation strategies that take into account the special properties of an FSF, and reduce the inverter losses, are proposed in **Chapter 2**.

A high switching frequency is used for the VSI pulse width modulation (PWM), in order to guarantee a dynamic control of the high-speed motor. This requirement for high switching frequency is achieved by employing the latest generation of wide-bandgap (WBG) semiconductor devices. However, the combination of a high switching frequency and WBG devices, causes electromagnetic interference (EMI) concerns. The electromagnetic compatibility (EMC) of high-speed motor drives is analysed in **Chapter 3**. The motor drive is part of a larger system, thus should not cause EMI noise that disrupts nearby electronic equipment. In order to mitigate the EMI emissions, a filter is placed at the inverter DC input-side, in addition to the output FSF. Several EMI aspects are discussed here, culminating in a new filter design algorithm, that takes into account interrelations between the input and output filters.

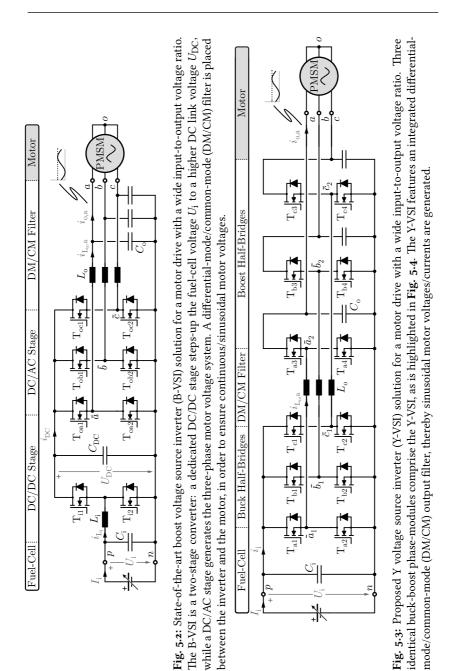

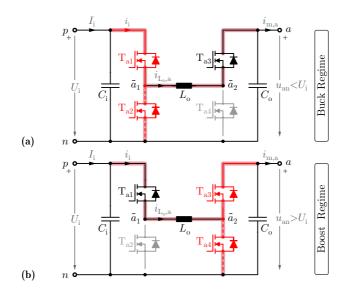

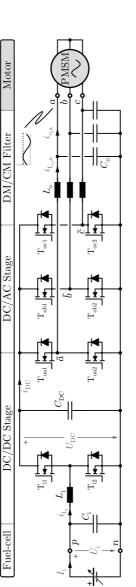

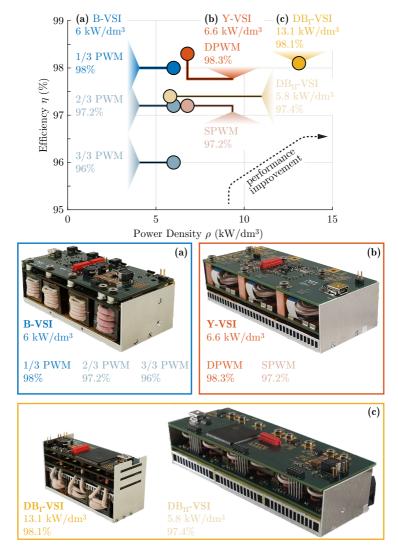

In the second part of the thesis, buck-boost inverter topologies are investigated. High-speed motor drive systems supplied by a fuel-cell/battery are especially demanding when it comes to the design of the inverter. Besides a high performance requirement, the inverter has to cope with the wide DC voltage variation of the fuel-cell/battery. Several buck-boost inverter concepts are evaluated by means of multi-objective optimization tools. Hardware prototypes are built for the most promising inverter topologies, and are compared to state-of-the-art solutions, with respect to the achievable efficiency and power density. In Chapter 4, a conventional buck-boost inverter topology is examined, which features two energy conversion stages. As a result of the two energy conversion stages, this inverter topology suffers from a low efficiency and a relatively low power density. A new modulation strategy that synergetically combines the operation of the two inverter stages, and hence improves the inverter efficiency, is proposed. Subsequently, in Chapter 5, innovation in the inverter topology is pursued. A new buck-boost inverter topology is presented, based on the idea of modular three-phase systems. This inverter topology achieves buck-boost capability by using only a single energy conversion stage, and thus achieves a high performance. Finally, in an effort to improve the motor drive as a whole, inverter innovation is combined with motor innovation, in Chapter 6. As a result, the double-bridge inverter technology is proposed, where two VSIs are connected to the opposite sides of an open-end winding motor (no floating neutral point).

**Chapter 7** briefly summarizes the key findings of this thesis and gives an outlook on future research.

# Kurzfassung

**D**<sup>ERZEIT</sup> verursacht der Transportsektor rund ein Viertel der weltweiten CO<sub>2</sub>-Emissionen. Um diesen Anteil zu reduzieren ist ein Übergang von Fahrzeugen mit konventionellen Verbrennungsmotoren (ICV) zu Fahrzeugen mit komplett elektrischen Antrieben (EV) unerlässlich. Um diesen Übergang voranzutreiben und für den Endverbraucher attraktiver zu gestalten, sind insbesondere im Bereich der Leistungselektronik und der Motorentechnik grundlegende Innovationen erforderlich.

Die vorliegende Dissertation fokussiert auf Brennstoffzellen-Elektrofahrzeuge (FCEV), in welchen die Brennstoffzelleneinheit eine kontinuierliche Sauerstoffversorgung benötigt. Die Sauerstoffzufuhr wird mit Hilfe eines elektrischen Kompressors sichergestellt, welcher von einer leistungselektronischen Schaltung gespeist wird. Diese Schaltung bzw. das Antriebssystem bildet den zentralen Gegenstand der Arbeit und wird hinsichtlich Anforderungen und Betriebsverhalten im Detail untersucht. Da das Antriebssystem im Fahrzeug untergebracht werden muss, ist ein geringes Gewicht, sowie ein hohes Mass an Kompaktheit unerlässlich. Da Hochgeschwindigkeits-Motoren/Kompressoren hohe Kompaktheit aufweisen, sind sie für die gegenständliche Anwendung vorteilhaft einsetzbar, allerdings liegt in der Literatur bisher noch keine umfassende Analyse von Antriebssystemen, welche auf die speziellen Eigenschaften von Hochgeschwindigkeitsmotoren zugeschnitten sind, vor. Diese Lücke soll durch diese Arbeit geschlossen werden, indem die Grenzen der Leistungsdichte und Effizienz von Antriebssystemen für Hochgeschwindigkeitsmotoren im Detail untersucht werden.

Im ersten Teil der Arbeit wird ein konventioneller spannungsgespeister Wechselrichter (VSI) verwendet, um einen Hochgeschwindigkeitsmotor anzutreiben. Da oberschwingungsbehaftete Statorströme in Hochgeschwindigkeitsmotoren hohe Rotorverluste verursachen, muss zwingend ein Ausgangsfilter zwischen den Wechselrichter und den Motor geschaltet werden. Es werden unterschiedliche Ausgangsfilter-Schaltungen untersucht, wobei der Schluss gezogen wird, dass ein Voll-Sinus-Ausgangsfilter (FSF) den Anforderungen von Hochgeschwindigkeitsmotoren am besten gerecht wird. Da ein zusätzliches FSF jedoch sowohl die Verluste als auch das Gesamtvolumen des Systems erhöht, werden in **Kapitel 2** zwei neue Modulationsverfahren vorgestellt, welche die speziellen Eigenschaften von FSF berücksichtigen und eine Reduktion der auftretenden Verluste im Wechselrichter erreichen.

Um eine hohe Dynamik der Steuerung des Hochgeschwindigkeitsmotors zu gewährleisten, wird eine hohe Schaltfrequenz der VSI-Pulsweitenmodulation (PWM) verwendet. Um bei hoher Schaltfrequenz hohe Effizienz sicherzustellen, wird die neuste Generation von Wide-Bandgap (WBG) Halbleiterbauelementen eingesetzt, deren hohe Schaltgeschwindigkeit potentiell elektromagnetische Störungen (EMI) verursacht welche umliegende Systemkomponenten beeinträchtigen könnten. Entsprechend wird die elektromagnetische Verträglichkeit (EMV) von Hochgeschwindigkeitsantrieben in **Kapitel 3** im Detail untersucht. Um Störungen zufolge EMI sicher zu vermeiden, wird zusätzlich zum ausgangsseitigen FSF ein EMI-Filter am Eingang des Wechselrichters angeordnet. Um eine Grundlage für die Optimierung der gesamten EMI-Filterung zu schaffen, werden die EMI-Störaussendungen im Detail analysiert. Auf Basis dieser Analysen wird ein neuer Filterdesign-Algorithmus entwickelt, welcher auch die Wechselbeziehungen zwischen dem Eingangs- und dem Ausgangsfilter berücksichtigt.

Im zweiten Teil dieser Arbeit werden kombinierte Hoch-/Tiefsetz-Wechselrichter-Topologien untersucht. Da das Antriebssystem, je nach Betriebsmodus, entweder direkt von der Brennstoffzelle oder von einer Batterie gespiesen wird, muss der Wechselrichter nicht nur eine hohe Leistungsanforderung erfüllen, sondern auch einen weiten Eingangsspannungsbereich beherrschen. Dies erschwert das Design, weshalb verschiedene Hoch-/Tiefsetz-Wechselrichter-Topologien mittels Mehr-Ziel-Optimierung verglichen und bewertet werden. Die vielversprechendsten Wechselrichtertopologien werden anschliessend als Hardwareprototypen aufgebaut und hinsichtlich Effizienz und Kompaktheit mit bestehenden Lösungen verglichen. In Kapitel 4 wird eine konventionelle Hoch-/Tiefsetz-Wechselrichter-Topologie untersucht, welche aus zwei in Serie geschalteten Energieumwandlungsstufen besteht. Aufgrund der zweifachen Energiekonversion weist diese Topologie jedoch eine relativ geringe Effizienz und Leistungsdichte auf. Um die Effizienz zu steigern, wird ein neues Modulationsverfahren vorgestellt, welches den Betrieb der beiden Stufen synergetisch kombiniert. Nachfolgend wird in Kapitel 5 eine neue Wechselrichtertopologie vorgeschlagen, welche auf der Idee modularer Dreiphasensysteme basiert. Diese Topologie weist eine einstufige Energieumformung auf, wodurch eine deutlich höhere Effizienz der Energieumwandlung resultiert. Desungeachtet kann die neue Wechselrichterschaltung sowohl als Hoch- als auch als Tiefsetzsteller betrieben werden. Im Bestreben den Antrieb als Ganzes zu verbessern, wird abschliessen der Wechselrichter und der Hochgeschwindigkeitsmotor gemeinsam betrachtet, und in Kapitel 6 eine Doppel-Brücken-Wechselrichtertopologie vorgestellt, in welcher zwei VSI-Schaltungen die gegenüberliegenden Statorwicklungsenden eines Motors mit offenen Wicklungen, d.h. ohne Sternpunkt speisen.

**Kapitel 7** fasst die wesentlichen Ergebnisse der Arbeit zusammen und gibt einen Ausblick auf zukünftige Forschungsthemen.

# Abbreviations

| AC     | Alternating Current                   |

|--------|---------------------------------------|

| ACCMM  | AC Common-Mode Modulation             |

| B-VSI  | Boost Voltage Source Inverter         |

| BEV    | Battery Electric Vehicle              |

| c-FSF  | Combined Full Sine-Wave Output Filter |

| СМ     | Common-Mode                           |

| CMF    | Common-Mode Output Filter             |

| CSI    | Current Source Inverter               |

| DB-VSI | Double-Bridge Voltage Source Inverter |

| d-FSF  | Discrete Full Sine-Wave Output Filter |

| DC     | Direct Current                        |

| DCCMM  | DC Common-Mode Modulation             |

| DM     | Differential-Mode                     |

| DMF    | Differential-Mode Output Filter       |

| DPWM   | Discontinuous Pulse Width Modulation  |

| EMC    | Electromagnetic Compatibility         |

| EMI    | Electromagnetic Interference          |

| EV     | Electric Vehicle                      |

| FCEV   | Fuel-Cell Vehicle                     |

| FSF    | Full Sine-Wave Output Filter          |

| GaN    | Gallium Nitride                       |

| ICV    | Internal Combustion Engine Vehicle    |

| IMD    | Integrated Motor Drive                |

| IMMD   | Integrated Modular Motor Drive        |

| LISN   | Line Impedance Stabilization Network  |

| OCMM   | Optimal CM modulation                 |

| PAM    | Pulse Amplitude Modulation            |

| PWM    | Pulse Width Modulation                |

| SB-VSI | Single-Bridge Voltage Source Inverter |

| Si     | Silicon                               |

| SiC    | Silicon Carbide                       |

| SM     | Sinusoidal Modulation                 |

| SPWM   | Sinusoidal Pulse Width Modulation     |

| THM    | Third Harmonic Injection Modulation   |

| VSI    | Voltage Source Inverter               |

| WBG    | Wide-Bandgap                          |

| Y-VSI  | Y Voltage Source Inverter             |

| ZSI    | Z Source Inverter                     |

## Contents

| Acknowledgments v |                                                            |           |                                                    | v    |

|-------------------|------------------------------------------------------------|-----------|----------------------------------------------------|------|

| Ab                | stract                                                     | :         |                                                    | vii  |

| Ku                | rzfass                                                     | sung      |                                                    | ix   |

| Ab                | brevi                                                      | ations    |                                                    | xiii |

| 1                 | Intro                                                      | duction   |                                                    | 1    |

|                   | 1.1                                                        |           | nges                                               | 3    |

|                   | 1.2                                                        |           | nd Contributions                                   | 5    |

|                   | 1.3                                                        |           | nance Benchmark                                    | 7    |

|                   | 1.4                                                        | Thesis (  | Outline                                            | 10   |

|                   | 1.5                                                        | List of I | Publications                                       | 12   |

| 2                 | 2 Voltage Source Inverter - Advanced Modulation Strategies |           |                                                    | 17   |

|                   | 2.1                                                        | Modula    | tion Strategies                                    | 21   |

|                   |                                                            | 2.1.1     | Drawbacks of Sinusoidal Modulation (SM)            | 23   |

|                   |                                                            | 2.1.2     | DC CM Injection Modulation (DCCMM)                 | 25   |

|                   |                                                            | 2.1.3     | AC CM Injection Modulation (ACCMM)                 | 28   |

|                   | 2.2                                                        | Compos    | nent Stresses                                      | 31   |

|                   |                                                            | 2.2.1     | DC CM Injection Modulation (DCCMM)                 | 31   |

|                   |                                                            | 2.2.2     | AC CM Injection Modulation (ACCMM)                 | 35   |

|                   |                                                            | 2.2.3     | Remaining Component Stresses                       | 36   |

|                   |                                                            | 2.2.4     | Optimal CM Modulation (OCMM)                       | 38   |

|                   | 2.3                                                        | Experin   | nental Validation                                  | 39   |

|                   | 2.4                                                        | Summa     | ry                                                 | 44   |

| 3                 | Volta                                                      | ige Sour  | ce Inverter - Electromagnetic Compatibility        | 47   |

|                   | 3.1                                                        | Theoret   | tical EMI Analysis                                 | 53   |

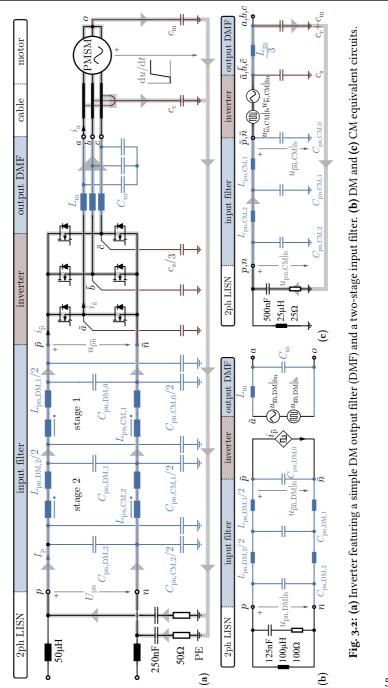

|                   |                                                            |           | Drawbacks of Differential-Mode Output Filter (DMF) | 54   |

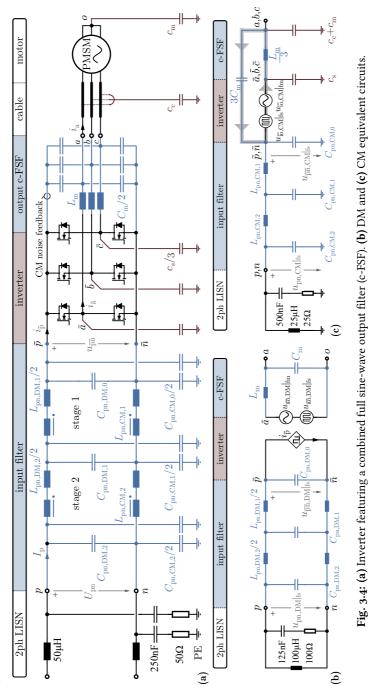

|                   |                                                            | 3.1.2     | Combined Full Sine-Wave Output Filter (c-FSF)      | 56   |

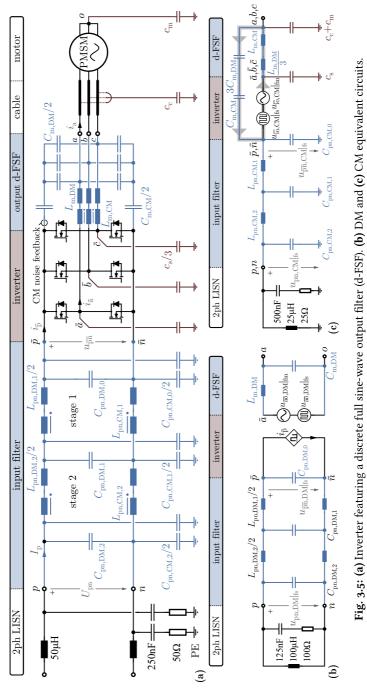

|                   |                                                            | 3.1.3     | Discrete Full Sine-Wave Output Filter (d-FSF)      | 59   |

|                   |                                                            | 3.1.4     | Input Filter                                       | 62   |

|                   | 3.2                                                        | •         | lesign                                             | 63   |

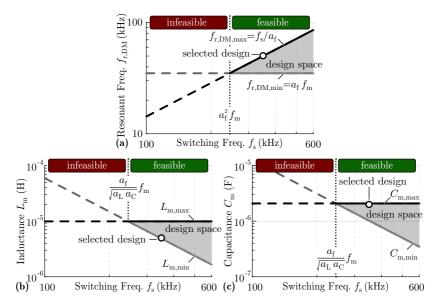

|                   | -                                                          | 3.2.1     | Output Filter Design                               | 63   |

|                   |                                                            | 3.2.2     | Output Filter Design for High-Speed Drives         | 66   |

|                   |                                                            | •         | Input Filter Design                                | 69   |

|                   |                                                            |           |                                                    |      |

|   | 3.3  | Experimental Validation                                                  | 70   |  |

|---|------|--------------------------------------------------------------------------|------|--|

|   |      | 3.3.1 Filter Attenuation Measurements                                    | 73   |  |

|   |      | 3.3.2 Parasitic CM Impedance Measurements                                | 78   |  |

|   |      | 3.3.3 Conducted EMI Measurements                                         | 80   |  |

|   | 3.4  | Summary                                                                  | 87   |  |

| 4 | Boo  | st Voltage Source Inverter - Advanced Modulation Strategy                | 89   |  |

| т | 4.1  | Modulation Strategies                                                    | 95   |  |

|   | 1    | 4.1.1 1/3 PWM Modulation Strategy                                        | 95   |  |

|   |      | 4.1.2 Alternative 2/3 PWM Modulation Strategy                            | 102  |  |

|   | 4.2  | Component Stresses for $\cos(\phi) = 1$                                  | 104  |  |

|   | 4.3  | Component Stresses for $\cos(\phi) < 1$                                  | 118  |  |

|   | 4.4  | Experimental Validation                                                  | 121  |  |

|   | 4.4  | 4.4.1 Design Procedure                                                   | 121  |  |

|   |      | 4.4.2 Experimental Results                                               | 123  |  |

|   | 4 5  | Summary                                                                  | 132  |  |

|   | 4.5  | Summary                                                                  | 132  |  |

| 5 | Y-In | /-Inverter                                                               |      |  |

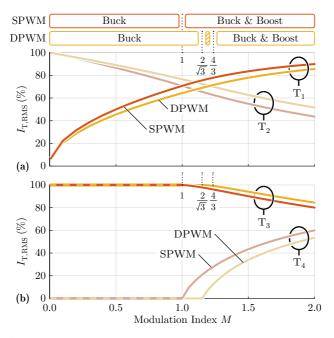

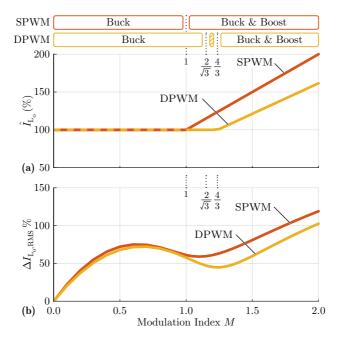

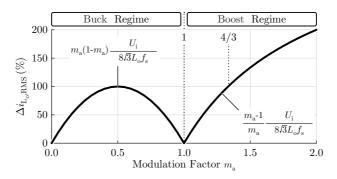

|   | 5.1  | Modulation Strategies                                                    | 139  |  |

|   |      | 5.1.1 Sinusoidal Modulation (SPWM)                                       | 141  |  |

|   |      | 5.1.2 Discontinuous Modulation (DPWM)                                    | 147  |  |

|   |      | 5.1.3 Control System                                                     | 151  |  |

|   | 5.2  | Component Stresses for a High Modulation Index                           | 153  |  |

|   |      | 5.2.1 Sinusoidal Modulation (SPWM)                                       | 154  |  |

|   |      | 5.2.2 Discontinuous Modulation (DPWM)                                    | 160  |  |

|   |      | 5.2.3 Remaining Component Stresses                                       | 163  |  |

|   | 5.3  | Component Stresses for a Low Modulation Index                            | 164  |  |

|   |      | 5.3.1 Sinusoidal Modulation (SPWM)                                       | 164  |  |

|   |      | 5.3.2 Discontinuous Modulation (DPWM)                                    | 165  |  |

|   | 5.4  | Experimental Validation                                                  | 165  |  |

|   | • -  | 5.4.1 Design Procedure                                                   | 165  |  |

|   |      | 5.4.2 Experimental Results                                               | 169  |  |

|   | 5.5  | Summary                                                                  | 175  |  |

| 6 | Dav  | hla Bridge Voltage Source Investor                                       | 1.50 |  |

| 6 |      | ble-Bridge Voltage Source Inverter                                       | 179  |  |

|   | 6.1  | Modulation Strategies                                                    | 186  |  |

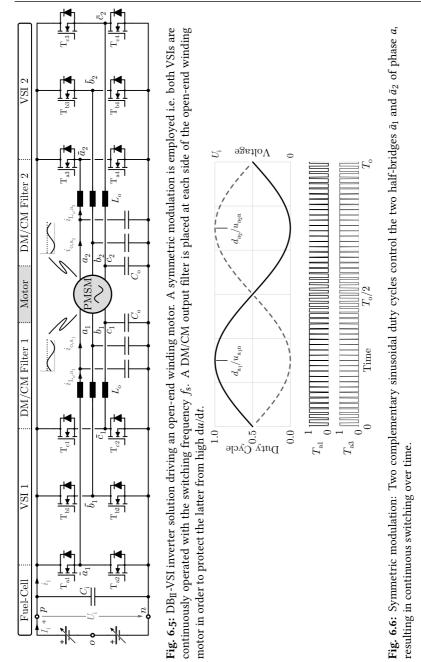

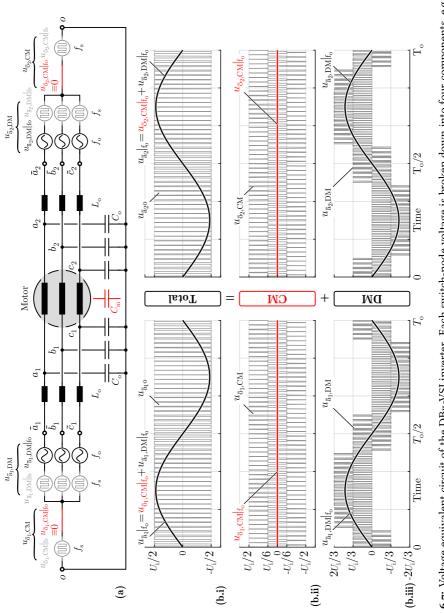

|   |      | 6.1.1 DB <sub>II</sub> -VSI Inverter - Symmetric Modulation              | 187  |  |

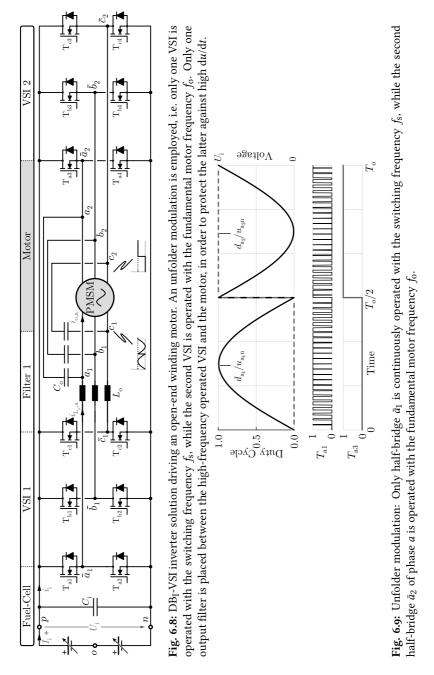

|   |      | 6.1.2 DB <sub>I</sub> -VSI Inverter - Unfolder Modulation                | 192  |  |

|   | ,    | 6.1.3 DB <sub>II</sub> -VSI Inverter - Alternative Modulation Strategies | 196  |  |

|   | 6.2  | Component Stresses                                                       | 199  |  |

|     |         | 6.2.1   | DB <sub>II</sub> -VSI Inverter - Symmetric Modulation |   | 201 |

|-----|---------|---------|-------------------------------------------------------|---|-----|

|     |         | 6.2.2   | DB <sub>I</sub> -VSI Inverter - Unfolder Modulation   |   | 203 |

|     | 6.3     | Experi  | mental Validation                                     |   | 205 |

|     |         | 6.3.1   | Design Procedure                                      |   | 205 |

|     |         | 6.3.2   | Experimental Results                                  |   | 208 |

|     | 6.4     | Summa   | ary                                                   |   | 217 |

|     |         |         |                                                       |   |     |

| 7   | Conc    | clusion |                                                       |   | 219 |

|     | 7.1     | Summa   | ary                                                   |   | 219 |

|     | 7.2     | Outloo  | ok & Future Research                                  | • | 223 |

| Bił | oliogra | aphy    |                                                       |   | 227 |

| Cu  | rricul  | um Vit  | ae                                                    |   | 247 |

# Introduction

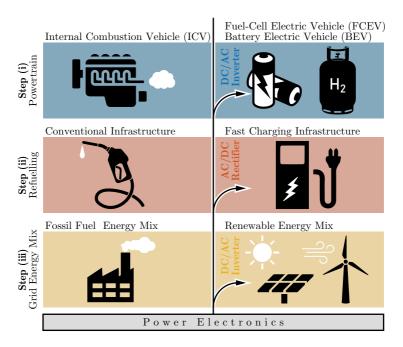

C LIMATE change is one of the biggest challenges of the next decades. The transportation sector accounts for 24% of the global  $CO_2$  emissions [1]. Furthermore, the transportation sector emissions are expected to grow at a faster rate than other sectors, posing a major challenge to the efforts to reduce emissions. The decarbonization of transportation requires three key steps as visualized in **Fig. 1.1**. Power electronics constitutes a main enabling technology in all three decarbonization steps.

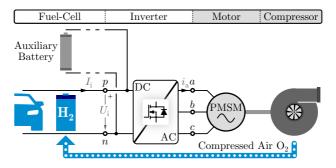

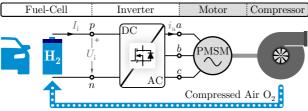

- (i) **Electrification of vehicles.** There are two main types of pure electric vehicles (EV): Fuel-cell electric vehicles (FCEV), which employ a fuel-cell electrochemical system that produces electricity onboard, and battery electric vehicles (BEV), which use a grid-charged battery pack. The main structure of FCEVs and BEVs is similar, since in either case the propulsion is achieved by the combination of a DC/AC inverter and an electric motor. Several power electronics converters are used in EVs. For example, in the case of FCEVs the fuel-cell DC bus supplies a DC/AC inverter, which in return controls an electric motor (powertrain). The fuel-cell requires continuous oxygen supply, which is provided by an onboard electric compressor. An auxiliary DC/AC converter, also supplied by the fuel-cell DC bus, controls this electric compressor [2-4]. FCEVs also include a small battery pack that provides the peak power demand, e.g. during acceleration. A DC/DC converter is needed in order to connect the battery DC bus with the fuel-cell DC bus [5,6]. It is therefore evident, that power electronics technology is a main enabler of innovation in EVs.

- (ii) **Charging infrastructure.** The EVs must be supported by an appropriate refuelling network. That is, hydrogen refuelling retail network

**Fig. 1.1:** Key steps leading to the decarbonization of the transportation sector. Power electronics is a main enabling technology.

for FCEVs and fast electric chargers for the case of BEVs. In the latter case of fast electric chargers, innovation in power electronics is necessary, in order to increase the power rating of the on-board/off-board chargers and accordingly reduce the charging time of a BEV [7–9].

(iii) Renewable energy generation. The EVs emit no CO<sub>2</sub> during use, but still contribute indirectly to carbon emissions. The BEVs rely on electricity, therefore the real emissions of BEVs depend on the energy mix of the grid. Similarly, FCEVs use hydrogen (H<sub>2</sub>), whose production requires an energy-intensive process. Therefore, the carbon footprint of FCEVs depends on the power grid energy mix. In order to achieve a true decarbonization of the transportation sector, a renewable generation base [10,11] and a modernization of the power grid [12] is needed. Power electronics technology is a key component of this endeavour. For example, efficient and flexible DC/AC converter systems

are needed, in order to deliver the renewable power from solar panels or wind turbines to the current AC power grid.

This thesis focuses on the energy storage system of a FCEV. In particular, the auxiliary compressor drive, that is responsible for the oxygen supply of the fuel-cell, is investigated. More details regarding the exact application follow in **Sec. 1.3**.

## 1.1 Challenges

Inverter systems placed onboard EVs are expected to be compact and lightweight. Therefore, the power density  $\rho$  is the most important performance objective for inverters, for this application. The pursuit of high power density is assisted by recent developments in the power semiconductor technology. Wide-bandgap (WBG) semiconductor devices (SiC/GaN) allow to increase the inverter switching frequency by a factor of ten, compared to Si counterparts [13–15]. Accordingly, a drastic reduction of the passive components' volume can be achieved without compromising the inverter efficiency. A high inverter efficiency  $\eta$  is also desirable, since it allows for a better utilization of the battery/fuel-cell energy and reduces the size of the thermal management system.

The traditional requirement for high efficiency and power density does not suffice for modern drive systems. Besides a high performance, the inverter is expected to provide additional features:

- (i) High fundamental frequency. The motor nominal speed (fundamental frequency) is directly related to the motor volume/weight [16–18]. By shifting towards higher rotational speeds the volume of the electric motor and the rotating mechanical components (e.g. compressor) can be drastically reduced and bulky gearboxes can be eliminated. Thereby, significant savings in terms of material cost can be achieved. Besides a challenging motor design, able to withstand the mechanical stress originating from the high rotational speeds [19, 20], the inverter must be able to generate voltages/currents with a fundamental frequency in the range of several kHz.

- (ii) Continuous output voltages. Typically, slotless permanent magnet motors are used in high-speed applications, which are especially sensitive to poor stator current quality, that causes rotor losses [21-23]. In this case, the thermal management of the rotor is a main concern, due

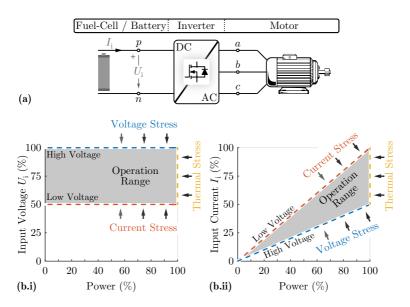

**Fig. 1.2:** (a) Drive system supplied by fuel-cell/battery, which must feature a wide voltage transfer ratio. (b) Voltage characteristics and (c) current characteristics of the fuel-cell/battery.

to the small rotor surface. In order to facilitate the motor cooling, the inverter must generate sinusoidal motor currents, that minimize the induced rotor losses.

(iii) Electromagnetic compatibility. The latest generation of WBG semiconductors allows for significantly better inverter performance but at the same time causes electromagnetic compatibility (EMC) concerns [24]. The high switching speeds of WBG semiconductor devices cause high du/dt [25-27], which stresses the motor insulation and induces bearing currents [28-33]. As a result, the motor reliability is jeopardised. The inverter must mitigate the du/dt, in order to ensure a safe motor operation [34-40].

An EV features several ancillary electronic systems such as driving aids, active suspension, and various sensors. These electronic systems are directly or indirectly supplied by the same DC bus as the inverter, and are sensitive to electromagnetic interference (EMI). In comparison to Si inverters, which employ a switching frequency in the tens of kHz, an inverter with WBG semiconductor devices can use a switching frequency in the range of several hundred kHz [14,41]. These high switching frequencies of WBG inverters are within the regulated conducted EMI emissions frequency range of 150 kHz...30 MHz [42]. Therefore, WBG inverters intensify EMI emission problems. The inverter must mitigate the generated EMI noise in order to protect nearby equipment.

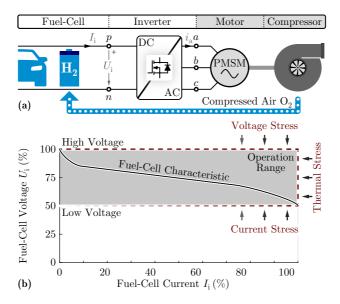

(iv) Buck-boost functionality. Motor drives supplied by a fuelcell/battery have to cope with a wide DC input voltage variation, as is visualised in Fig. 1.2. In particular, the voltage of the fuel-cell highly depends on the operating point. A fuel-cell exhibits the highest voltage at no-load condition, while the lowest voltage appears at full-load condition [43]. The voltage of a battery also fluctuates, depending on the charging status and the operating temperature. The ratio between the maximum and the minimum voltage, for either battery or fuel-cell, can be as high as two. The inverter has to always guarantee the full speed range of the motor, independent of the DC input voltage fluctuation, i.e. the inverter must be able to generate the nominal motor voltage, which is proportional to the motor speed.

The demand for additional inverter features, often contradicts the requirement for a high efficiency/power density. For example, electromagnetic compatibility mandates the use of EMI filters which add to the inverter volume, while buck-boost functionality leads to over-dimensioning of the inverter components and hence additional losses. The interdependencies between the different inverter features, complicate the design process. It is particularly challenging to achieve a balance among the various inverter features and a high performance.

## 1.2 Aims and Contributions

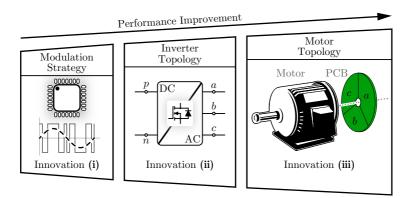

The goal of this thesis is to research and apply innovative technical solutions, to fuel-cell powered, high-speed motor drives. Three innovation paths are investigated:

(i) **New modulation strategies.** There is a large number of operational motor drives, which feature conventional Si inverters. In fact, 40% of the worldwide electricity is consumed by motor drives [44, 45]. In this case, it is not desirable to only replace the Si inverter with a new

Fig. 1.3: Motor drive innovation roadmap.

WBG counterpart, but also improve the efficiency of the existing system. This goal can be achieved by means of new modulation strategies, which can be uploaded to the inverter, as a simple firmware update. New modulation strategies are proposed in this thesis, that improve the performance of state-of-the-art inverters.

- (ii) New inverter topologies. The most readily available inverters are Sibased voltage source inverters (VSI). VSIs are well suited for Si devices, and thus utilize this semiconductor technology optimally. However, the performance of such inverter solutions is inherently limited by the inferior properties of Silicon. Recent advances in WBG semiconductor devices, bring in the forefront alternative inverter topologies. Literature shows that conventional VSIs might not be the best suited option for WBG semiconductor devices [45]. For this reason, new inverter topologies are investigated in this thesis.

- (iii) New motor topologies. In order to achieve the best performance on a system level, it is desirable to coordinate the design of the inverter and the motor. A very efficient inverter could lead to a bulky motor and vice-versa, which is a sub-optimal solution [46]. Therefore, it is important to consider the efficiency and power density of the motor drive system as a whole (i.e. inverter and motor). The integration of the inverter and the motor in the same housing is the natural next step in inverter/motor design [45, 47, 48]. Thereby, the inverter is directly attached on the motor terminals and cumbersome/costly interconnect-

ing cables are eliminated. A common thermal management system can be used for the inverter and the motor, provided that the inverter is able to operate reliably in the high-temperature environment of the motor. An integrated motor drive (IMD) adds value for the end user, because the latter is not any more burdened with the complicated inverter/motor installation.

## 1.3 Performance Benchmark

This thesis focuses on two high-speed motor drive applications, supplied by a DC source. The specifications are defined according to the needs of the industry partner of this thesis: Celeroton AG.

**Application I** is presented in **Fig. 1.4** and summarized in **Tab. 1.1**. A  $U_i = 48$  V battery supplies the inverter, which in return controls the high-speed n = 500 krpm, P = 70 W electric compressor of **Fig. 1.5(b**). The electric compressor houses internally the electric motor of **Fig. 1.5(a**).

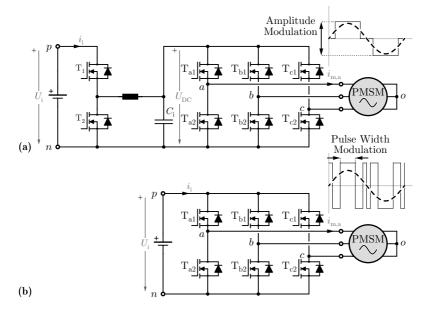

A commercially available inverter system based on Si semiconductor technology already exists for this motor drive application, and employs pulse amplitude modulation (PAM). The existing PAM system is visualized in **Fig. 1.6(a)**. According to PAM modulation, the VSI applies 120° voltage blocks to the motor, with an amplitude equal to the DC link voltage  $U_{\rm DC}$ . The motor fundamental voltage/current is controlled, by adjusting the DC link voltage  $U_{\rm DC}$ , by means of a dedicated DC/DC buck converter. The PAM modulation causes block shaped motor currents, which result in high eddy current losses in the rotor [46]. In high-speed motors it is especially difficult to dissipate rotor losses due to the small rotor surface. This is a significant drawback of PAM inverters that needs to be addressed.

The main target for this application is to replace the PAM inverter with a pulse width modulated (PWM) inverter, in an effort to improve the motor current quality. A typical PWM inverter is shown in **Fig. 1.6(b)**. By employing a high switching frequency, a PWM inverter significantly improves the motor current quality, thus allows the reduction of the critical rotor losses. However, a high switching frequency inevitably leads to high switching losses of the semiconductor devices. In order to limit the switching losses, the latest GaN semiconductor technology is used. Even though a PWM inverter may be less efficient than a PAM inverter, the former allows to shift losses from the motor to the inverter, resulting in a better performance of the motor drive system as a whole. The performance limits of PWM inverters are explored in this thesis.

**Fig. 1.4:** High-speed motor drive **Application I**. The inverter is supplied with a constant DC voltage  $U_i$ , and controls the high-speed electric compressor of **Fig. 1.5(b**).

Tab. 1.1: Specifications of high-speed motor drive Application I.

| Inverter input voltage    | $U_{\rm i} = 48  {\rm V}$                                |

|---------------------------|----------------------------------------------------------|

| Inverter power            | P = 0 W330 W                                             |

| Inverter power density    | $\rho \ge 1.32  \mathrm{kW/dm^3}  (0.25  \mathrm{dm^3})$ |

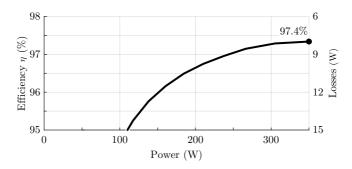

| Inverter efficiency       | $\eta \ge 97\% \ (9.9  \mathrm{W})$                      |

| Motor speed               | n = 0 rpm500 krpm                                        |

| Motor fundamental freq.   | $f_{\rm m} = 0$ Hz8.3 kHz                                |

| Motor power               | P = 0  W200 W                                            |

| Motor voltage (phase, PK) | $\hat{U}_{\rm m} = 0  {\rm V}19  {\rm V}$                |

| ⊗ 22mm                    | Q 48mm                                                   |

(a)

**Fig. 1.5:** (a) High-speed, 500 krpm, 200 W electric motor [49]. (b) High-speed, 500 krpm, 70 W electric compressor (including the motor) with ball bearings [50].

(b)

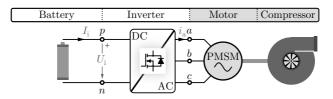

**Application II** is presented in **Fig. 1.7** and summarized in **Tab. 1.2**. A n = 280 krpm electric compressor provides compressed air to a 10 kW fuel-cell unit. An inverter, directly supplied by the fuel-cell DC voltage  $U_i = 40$  V...120 V, controls the electric compressor. The electric compressor consumes approximately 10% of the fuel-cell power, i.e. P = 1 kW. A ball bearing and a gas bearing variant of the n = 280 krpm electric compressor is

**Fig. 1.6:** (a) State-of-the-art inverter employing pulse amplitude modulation (PAM). A dedicated DC/DC buck converter controls the DC link voltage  $U_{DC}$ . (b) Pulse width modulated (PWM) inverter.

shown in Fig. 1.8(b.i) and (b.ii), respectively. A stand alone n = 280 krpm electric motor is depicted in Fig. 1.8(a).

Besides the requirement for high quality motor currents, the inverter has to cope with the wide DC voltage variation of the fuel-cell, in this application. Under no-load condition the fuel-cell features the maximum DC voltage of  $U_i = 120 \text{ V}$ , while under full-load condition the fuel-cell exhibits the lowest DC voltage of  $U_i = 40 \text{ V}$ . The inverter systems must be able to guarantee the nominal motor speed/voltage independent of the fuel-cell voltage variation. To this end, novel buck-boost inverter solutions are developed and new modulation strategies are explored in this thesis.

**Fig. 1.7:** High-speed motor drive **Application II**. The electric compressor of **Fig. 1.8(b.ii)** provides the air supply, needed for the operation of a fuel-cell. An inverter supplied by the fuel-cell, controls the high-speed compressor. An auxiliary battery, parallel to the fuel-cell, is used for the system startup.

Tab. 1.2: Specifications of high-speed motor drive Application II.

| Fuel-cell Power           | $P_{\rm FC} = 0 \mathrm{W}10 \mathrm{kW}$              |

|---------------------------|--------------------------------------------------------|

| Fuel-cell voltage         | $U_{\rm i} = 40  {\rm V}120  {\rm V}$                  |

| Inverter power            | P = 0 W1100 W                                          |

| Inverter power density    | $ ho \ge 1.57  \mathrm{kW/dm^3}  (0.7  \mathrm{dm^3})$ |

| Inverter efficiency       | $\eta \ge 95\% \ (50  { m W})$                         |

| Motor speed               | n = 0 rpm280 krpm                                      |

| Motor fundamental freq.   | $f_{\rm m} = 0$ Hz4.7 kHz                              |

| Motor power               | P = 0 W1000 W                                          |

| Motor voltage (phase, PK) | $\hat{U}_{\rm m} = 0  {\rm V}40  {\rm V}$              |

### 1.4 Thesis Outline

The content of the thesis is divided into five main chapters and the conclusions. All the chapters can be read independently, since the interdependencies have been reduced to the strict minimum.

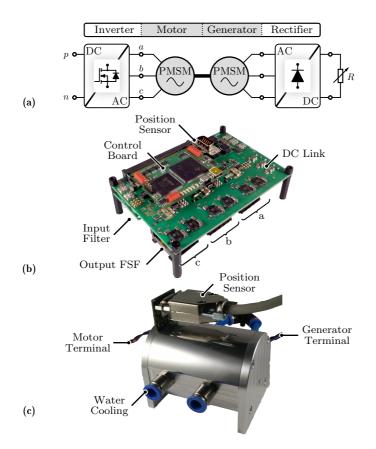

**Chapter 2** focuses on PWM voltage source inverters (VSI), for high-speed motor drives. In order to guarantee sinusoidal motor voltages/currents, a filter is placed between the inverter and the motor. The additional losses and volume of the filter compromise the overall inverter performance. New modulation strategies are proposed, that mitigate the negative impact of the output filter. The proposed modulation concepts are validated on a hardware demonstrator, built for the application I (cf. **Tab. 1.1**).

**Fig. 1.8: (a)** High-speed, 280 krpm, 1 kW electric motor [51]. High-speed, 280 krpm, 1 kW electric compressor (including the motor) with **(b.i)** ball bearings [52] and **(b.ii)** gas bearings [53].

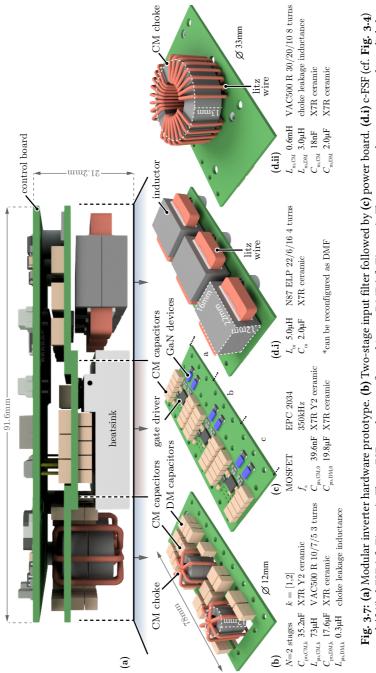

In **Chapter 3** the electromagnetic compatibility challenges, caused by WBG semiconductor devices, are discussed. A comprehensive input/output filter design algorithm is proposed, tailored to the needs of high-speed drives and WBG inverters. The theoretical considerations are verified on a purposely assembled hardware demonstrator, for the application II (cf. **Tab. 1.2**).

From this point on, buck-boost inverter topologies are analysed, which can cope with the wide DC voltage fluctuation of a fuel-cell. The application II (cf. **Fig. 1.7** and **Tab. 1.2**) is considered.

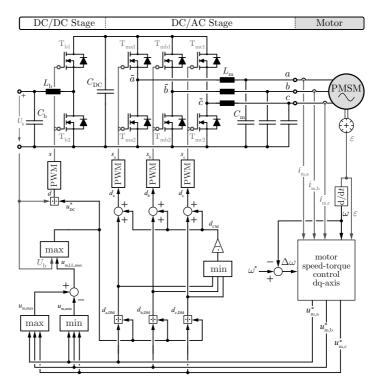

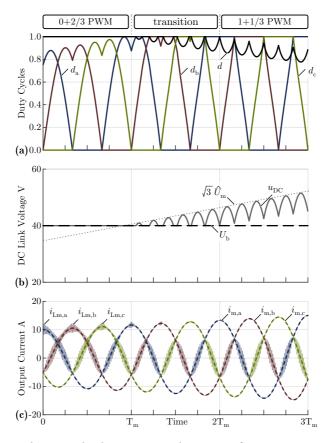

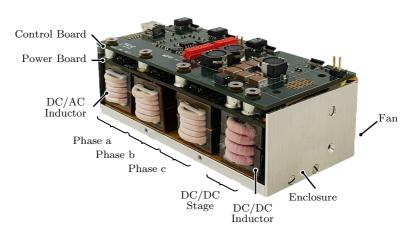

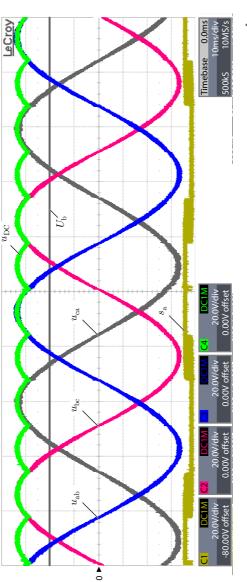

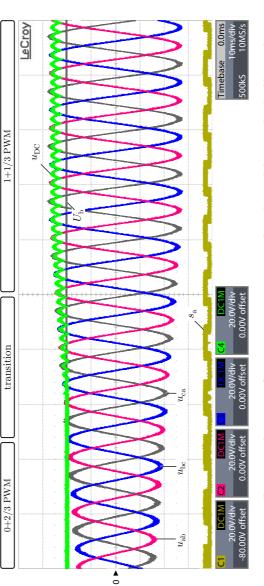

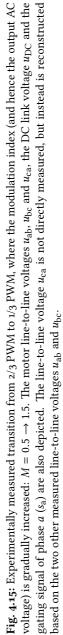

In **Chapter 4** a conventional buck-boost inverter solution is discussed, with two energy conversion stages. As a result of the two conversion stages, this inverter solution suffers from a low efficiency. A new modulation concept, that combines the control of the two conversion stages and results in a higher inverter efficiency, is proposed in this chapter. The performance of the new modulation strategy is verified on a hardware demonstrator.

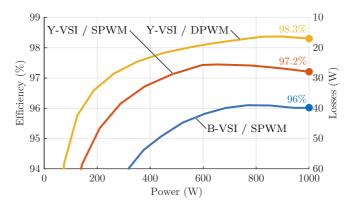

In order to overcome the inherent limitations of two-stage inverters, a single-stage buck-boost inverter topology, denoted as Y-inverter, is proposed in **Chapter 5**. The advantages of the Y-inverter are highlighted in this chapter, while appropriate modulation strategies are developed. A hardware prototype is assembled and tested. The experimental results verify the superior performance of the Y-inverter, compared to a conventional two-stage inverter solution.

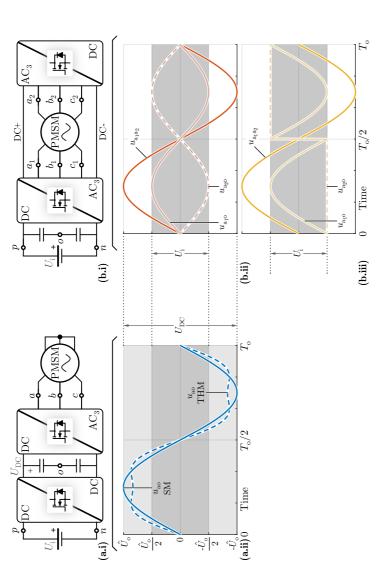

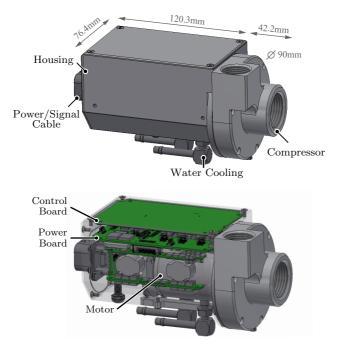

In **Chapter 6** innovation in the inverter stage is combined with innovation in the motor side. As a result, the double-bridge voltage source inverter (DB-VSI) technology is proposed, where two VSIs are connected to the opposite sides of an open-end winding motor (no floating neutral point). This inverter/motor solution achieves excellent efficiency and power density, which is validated by means of two hardware prototypes. Finally, the DB-VSI technology is applied on an IMD, (by the industry partner Celeroton AG), where the inverter is integrated in the compressor housing of **Fig. 1.8(b.ii)**.

**Chapter 7** briefly summarizes key results and findings of this thesis. An outlook on future research is also given.

#### **1.5** List of Publications

Key insights presented in this thesis have already been published or will be published in international scientific journals, conference proceedings, presented at workshops and/or have been protected by patents. The publications developed in the course of this thesis are listed below.

#### **Journal Papers**

- ▶ M. Antivachis, F. Dietz, C. Zwyssig, D. Bortis, and J. W. Kolar, "Novel high-speed turbo compressor with integrated inverter for fuel-cell air supply," *Frontiers in Mechanical Engineering*, 2020, early access.

- M. Antivachis, D. Wu, and J. W. Kolar, "Analysis of double-bridge inverters for drive systems with open-end winding motors," *IEEE Journal* of *Emerging and Selected Topics in Power Electronics*, 2020, early access. DOI: 10.1109/JESTPE.2020.3017085.

- M. Antivachis, N. Kleynhans, and J. W. Kolar, "Three-phase sinusoidal output buck-boost GaN Y-inverter for advanced variable speed AC drives," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 2020, early access. DOI: 10.1109/JESTPE.2020.3026742.

- M. Antivachis, P. Niklaus, D. Bortis, and J. W. Kolar, "Input / output EMI filter design for three-phase ultra-high speed motor drive GaN inverter stage" CPSS Transactions on Power Electronics and Applications, 2020, early access.

- M. Antivachis, J. Azurza Anderson, D. Bortis, and J. W. Kolar, "Analysis of a synergetically controlled two-stage three-phase DC/AC buckboost converter," CPSS Transactions on Power Electronics and Applications, vol. 5, no. 1, pp. 34-53, March 2020. DOI: 10.24295/CPSST-PEA.2020.00004.

- M. Antivachis, D. Bortis, A. Avila, and J. W. Kolar, "New optimal common-mode modulation for three-phase inverters with DC-link referenced output filter," CPSS Transactions on Power Electronics and Applications, vol. 2, no. 4, pp. 331-340, December 2017. DOI: 10.24295/CPSST-PEA.2017.00030.

#### **Conference** Papers

- M. Antivachis, D. Bortis, D. Menzi, and J. W. Kolar, "Comparative evaluation of Y-inverter against three-phase two-stage buck-boost DC-AC converter systems," in *Proc. of International Power Electronics Conference (IPEC-ECCE Asia)*, Niigata, Japan, May 2018, pp. 181-189. DOI: 10.23919/IPEC.2018.8507664.

- M. Antivachis, D. Bortis, L. Schrittwieser, and J. W. Kolar, "Threephase buck-boost Y-inverter with wide DC input voltage range," in *Proc. of IEEE Applied Power Electronics Conference and Exposition* (APEC), San Antonio, TX, USA, March 2018, pp. 1492-1499. DOI: 10.1109/APEC.2018.8341214.

#### Patents

- M. Leibl, L. Schrittwieser, J. W. Kolar, D. Bortis, and M. Antivachis, "Konverter zur Übertragung von elektrischer Energie zwischen einem DC und einem AC-System," Swiss Patent Application No. CH 01159/17, September 2017. .

- J. W. Kolar, D. Bortis, and M. Antivachis, "Verfahren zur Ansteuerung eines mehrphasigen Wechselrichters und Verfahren zur Minimierung des Rippelstromeffektivwertes in der Ausgangsfilterinduktivität von

Dreiphasen-Pulswechselrichtersystemen," Swiss Patent Application No. CH 01071/17, August 2017. .

#### Workshops and Seminars

- J. W. Kolar, M. Guacci, M. Antivachis, and D. Bortis, "Next-generation SiC/GaN three-phase variable-speed drive PWM inverter concepts," Tutorial at the *9th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia)*, Nanjing, China, December 2020.

- ▶ J. W. Kolar, M. Guacci, M. Antivachis, and D. Bortis, "Advanced 3-phase SiC/GaN PWM inverter concepts for future VSD applications," Tutorial at the *35th Applied Power Electronics Conference and Exposition (APEC)*, New Orleans, LA, USA, March 2020. .

- J. W. Kolar, M. Guacci, M. Antivachis, and D. Bortis, "Advanced 3-Φ SiC/GaN PWM inverter & rectifier systems," Tutorial at the 45th Annual Conference of the IEEE Industrial Electronics Society 2019 (IECON), Lisbon, Portugal, October 2019.

- D. Bortis, M. Guacci, M. Antivachis, and J. W. Kolar, "Future SiC/GaN variable speed drive inverter topologies How to handle a double-edged sword," Presentation at the *2nd Wagner Automotive Symposium Inverter Trends & Technology*, Wangen, Germany, November 2019.

- J. W. Kolar, J. Azurza, M. Guacci, M. Antivachis, and D. Bortis, "Advanced 3-phase SiC/GaN PWM inverter and rectifier systems," Presentation at the *Centre for Power Electronics Annual Conference*, Loughborough, United Kindom, July 2019.

- ▶ D. Bortis, J. W. Kolar, M. Antivachis, J. Azurza, M. Guacci, and D. Menzi, "Advanced three-phase PFC-rectifiers," Presentation at the *Presentation at the ECPE Cluster-Seminar*, Augsburg, Germany, May 2019. .

- ▶ J. W. Kolar, M. Antivachis, D. Bortis, D. Menzi, J. Miniböck, F. Krismer, and D. Rothmund, "Latest findings in three-phase AC/DC converter research," Presentation at the *Future Energy Technology Workshop*, Nuremberg, Germany, June 2018. .

#### **Additional Contributions**

- J. W. Kolar, J. Azurza Anderson, S. Miric, M. Haider, M. Guacci, M. Antivachis, G. Zulauf, D. Menzi, P. S. Niklaus, J. Miniböck, P. Papamanolis, G. Rohner, N. Nain, D. Cittantiz, and D. Bortis, "Application of WBG power devices in future 3-Φ variable speed drive inverter systems," in *Proc. of IEEE International Electron Devices (IEDM)*, San Francisco, CA, USA, December 2020.

- P. Niklaus, M. Antivachis, D. Bortis, and J. W. Kolar, "Analysis of the influence of measurement circuit asymmetries on three-phase CM/DM conducted EMI separation," CPSS Transactions on Power Electronics and Applications, 2020, early access. DOI: 10.1109/TPEL.2020.3025122.

2

# Voltage Source Inverter - Advanced Modulation Strategies

This chapter summarizes the key research findings also presented in:

M. Antivachis, D. Bortis, A. Avila and J. W. Kolar, "New optimal commonmode modulation for three-phase inverters with DC-link referenced output filter," *CPSS Transactions on Power Electronics and Applications*, vol. 2, no. 4, pp. 331-340, December 2017. DOI: 10.24295/CPSSTPEA.2017.00030.

Motivation -

Voltage source inverters (VSI) followed by a full sine-wave output filter (FSF) have found broad acceptance in high-speed motor drives. However, the special characteristics of the FSF are usually not taken into consideration by the modulation strategy of the VSI. This chapter addresses this blind spot of literature, by introducing new modulation strategies tailored to an FSF.

#### – Executive Summary ———

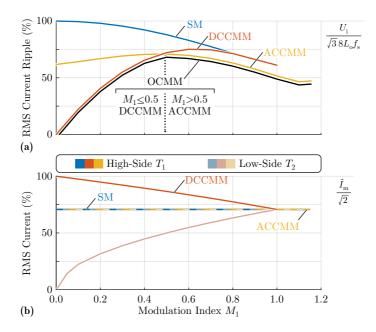

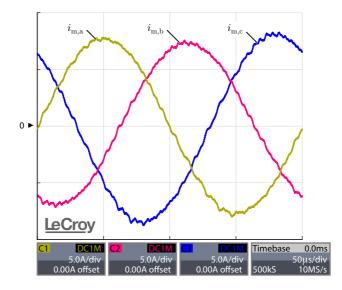

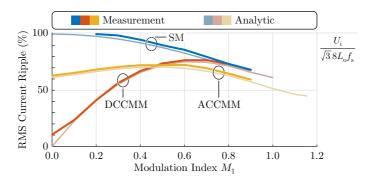

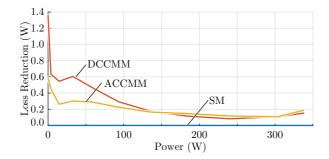

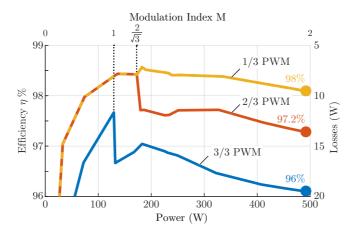

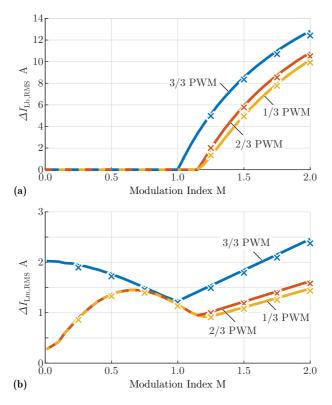

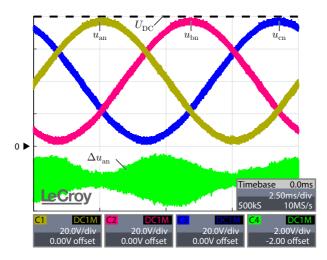

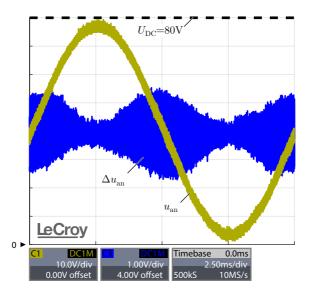

A two-level voltage source inverter (VSI) followed by a full sine-wave output filter (FSF) is typically used for high-speed, low-voltage drive systems. A limitation of this inverter solution lies in the additional losses occurring within the output filter. In particular, the output filter inductors, which suffer high current ripple, are a main driver of losses. This shortcoming can be addressed by means of an appropriate modulation strategy. This chapter details two new modulation strategies, tailored to the specific characteristics of a VSI with an FSF. By utilizing the instantaneous CM voltage as a degree of freedom, the output inductor's current ripple is reduced. It is deduced that a constant (DC) CM voltage injection (DCCMM) or a time varying (AC) CM voltage injection (ACCMM) yields the best performance, depending on the inverter operating point. In an effort to further reduce the inductor current ripple/losses, the two above modulation strategies are combined. The resulting modulation strategy is denoted as optimal CM injection modulation (OCMM). Finally, the proposed modulation strategies are tested on a 330 W hardware prototype driving a 400 krpm motor. There, an up to 11% reduction of the total inverter losses is observed.

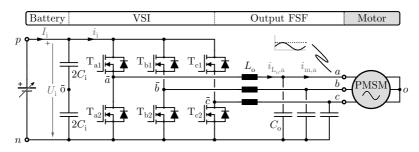

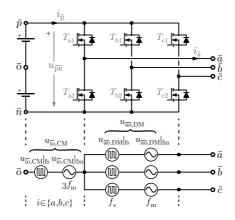

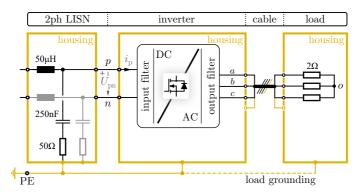

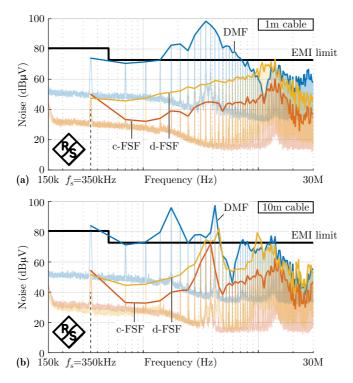

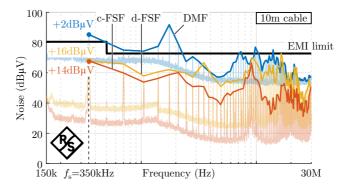

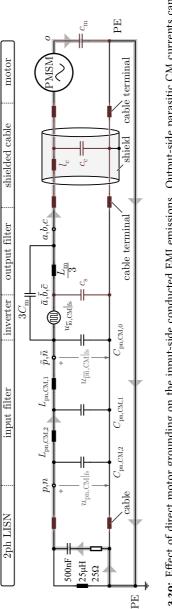

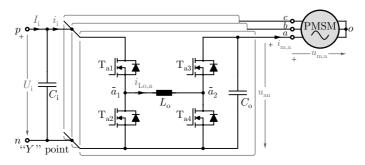

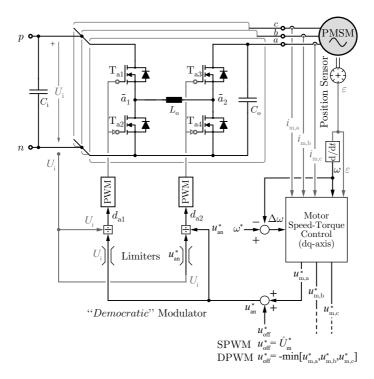

High-speed, low-voltage drive systems spread across a wide range of applications such as turbocompressor systems, drills, medical equipment, and air-conditioning units [16, 17]. Typically, a two-level voltage source inverter (VSI) employing pulse width modulation (PWM) drives the high-speed motor, as illustrated in **Fig. 2.1**. A full sine-wave output filter (FSF), that features both differential-mode (DM) and common-mode (CM) attenuation, is placed between the VSI and the motor in order to ensure high motor voltage quality. An FSF offers two main advantages:

- (i) Reduction of rotor losses. An FSF guarantees sinusoidal motor currents/voltages, that minimize the induced rotor losses [54]. The rotor losses are a main concern in high-speed motors, where it is difficult to extract heat from the rotor, due to its small surface/volume.

- (ii) Suppression of du/dt. An FSF suppresses the CM du/dt generated by wide-bandgap semiconductor devices. Thereby, the motor bearing is protected from excess voltage/current stress [34], which would lead to premature failure.

The selected FSF belongs to the family of DC link referenced filters [ $_{36-38}$ ], i.e. the capacitors  $C_o$  of the filter are connected/referenced to the negative DC rail *n*. The simplicity/low cost of a DC link referenced output filter, renders it a prominent choice in low-voltage drive systems, where cost is a main

**Fig. 2.1:** Two-level voltage source inverter (VSI) with a full sine-wave output filter (FSF) driving a high-speed motor.

**Tab. 2.1:** Motor drive system specifications. The nominal operating condition is highlighted in bold.

.

| Inverter input voltage      | $U_{\rm i}$            | 48 V                  |

|-----------------------------|------------------------|-----------------------|

| Inverter power              | Р                      | 0 W <b>330 W</b>      |

| Inverter switching freq.    | $f_{\rm s}$            | 280 kHz               |

| Inverter filter inductance  | Lo                     | 17 µH                 |

| Inverter filter capacitance | Co                     | 1.4 µF                |

| Motor speed                 | п                      | 0 rpm <b>400 krpm</b> |

| Motor fundamental freq.     | $f_{\rm m}$            | 0 Hz <b>6.6 kHz</b>   |

| Motor power                 | Р                      | 0 W <b>300 W</b>      |

| Motor voltage (phase, PK)   | $\hat{U}_{\mathrm{m}}$ | 0 V <b>19 V</b>       |

design driver. A high switching frequency  $f_s$  is typically preferred, in order to reduce the volume of the output filter's passive components.

The incorporation of an output filter allows for better motor voltage quality at the expense of decreased inverter performance, since the volume and losses of the output filter are added to the inverter stage. There has been extensive research towards modulation strategies that counterbalance the negative impact of an output filter [55–58]. According to literature, the available degree of freedom in the modulation of a VSI is the shape of the CM duty cycle  $d_{CM}(t)$  [59] which is injected to all three phases

$$d_{a}(t) = M_{1} \cos(\omega_{m}t) + d_{CM}(t)$$

$$d_{b}(t) = M_{1} \cos(\omega_{m}t - \frac{2\pi}{3}) + d_{CM}(t),$$

$$d_{c}(t) = M_{1} \cos(\omega_{m}t + \frac{2\pi}{3}) + d_{CM}(t)$$

(2.1)

where  $M_1$  is the modulation index

$$M_1 = \frac{\hat{U}_{\rm m}}{\frac{1}{2}U_{\rm i}},\tag{2.2}$$

and  $\hat{U}_{\rm m}$  is the motor phase voltage amplitude. The CM duty cycle pattern  $d_{\rm CM}(t)$  impacts the performance of the inverter. In the case of a VSI followed by a simple DM filter, for example, the injection of an approximately triangular CM duty cycle (space vector modulation) yields the lowest filter inductor current ripple [60]. A sinusoidal third harmonic injection results in a similar filter inductor current ripple. In contrast, the injection of a roughly rectangular CM duty cycle (discontinuous modulation), leads to a reduction of the switching losses but higher inductor current ripple [61, 62].

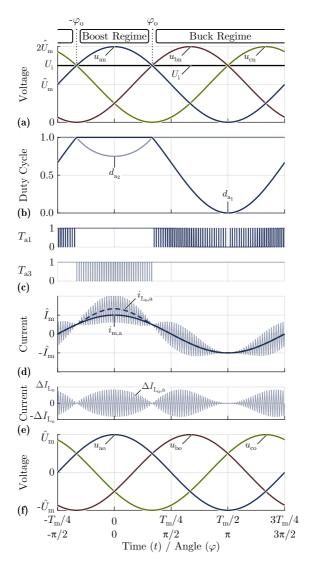

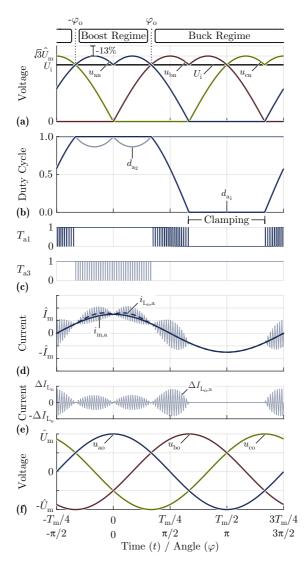

In the case of a VSI with an FSF, the formulation mechanism of the filter inductor current ripple  $\Delta i_{L_0}$  is fundamentally different compared to a simple DM filter. In particular, CM currents flow through the FSF capacitors  $C_0$ from/towards the negative DC rail *n*, resulting in a high overall current ripple across the filter inductor  $L_0$ . A high current ripple  $\Delta i_{L_0}$  results in high losses in the filter inductors. Therefore, a modulation strategy that minimizes the inductor current ripple is needed. However, the previously described modulation strategies correspond to a simple DM filter, and thus do not yield the desired inductor performance for the case of an FSF. Instead, the optimal shape of the CM duty cycle  $d_{CM}(t)$ , that minimizes the current ripple of the filter inductors, must be revisited and redefined according to the special characteristics of the FSF at hand. In response to those concerns, this chapter details the degrees of freedom, when selecting the modulation strategy of a VSI employing an FSF. In particular, two new modulation strategies that reduce the filter inductor current ripple are proposed in **Sec. 2.1**:

- (i) DC CM injection modulation (DCCMM). A constant (DC) CM duty cycle  $d_{CM}(t) = -M_0$  is injected into all three phases.

- (ii) AC CM injection modulation (ACCMM). A time varying (AC) CM duty cycle with arbitrarily large amplitude  $d_{\text{CM}}(t) = -M_{\text{N}} \cos(N\omega_{\text{m}}t)$  (*N* = 3, 6, 9,...) is injected into all three phases.

Subsequently in **Sec 2.2**, the stresses on the different inverter components are calculated. The proposed modulation strategies are tested on a 330 W hardware prototype driving a 400 krpm motor in **Sec. 2.3**. There, an up to 11% reduction of the total inverter losses is observed. Finally, a summary is given in **Sec. 2.4**.

# 2.1 Modulation Strategies

The inverter system shown in **Fig. 2.1**, features a two-level voltage source inverter (VSI), followed by a full sine-wave output filter (FSF). Sinusoidal motor voltages (with respect to the motor floating neutral point *o*) are desirable

$$u_{ao}(t) = u_{m,a}(t) = \hat{U}_{m} \cos(\omega_{m} t)$$

$$u_{bo}(t) = u_{m,b}(t) = \hat{U}_{m} \cos(\omega_{m} t - \frac{2\pi}{3}),$$

$$u_{co}(t) = u_{m,c}(t) = \hat{U}_{m} \cos(\omega_{m} t + \frac{2\pi}{3})$$

(2.3)

where  $\omega_{\rm m} = 2\pi f_{\rm m}$  is the motor angular frequency. The inverter generates the sinusoidal motor voltages by controlling the output terminal voltages  $[u_{\rm a\bar{o}}, u_{\rm b\bar{o}}, u_{\rm c\bar{o}}]$  (with respect to the DC link mid-point  $\bar{o}$ ). In the case of an FSF, the capacitors  $C_{\rm o}$  are connected to the negative DC rail *n*. Each phase-leg is equivalent to a simple buck converter and is independent of the other two phases. This is different from a simple DM filter, where the capacitors  $C_{\rm o}$  are connected to a floating star point, resulting in a coupling among the three phases. From now on, the analysis is focused on phase *a*, when possible, while the results can be easily extended to phases *b* and *c*.

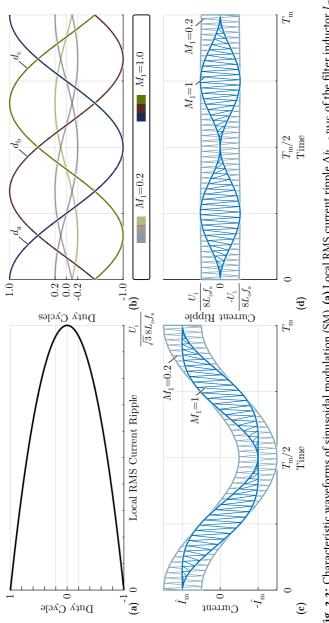

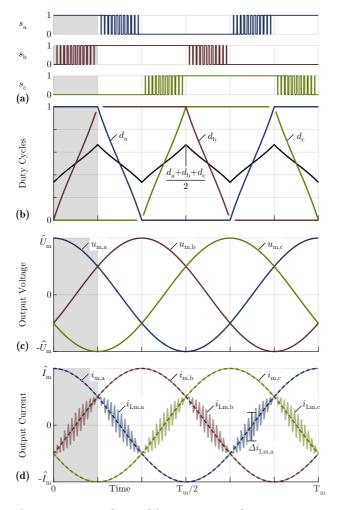

#### 2.1.1 Drawbacks of Sinusoidal Modulation (SM)

According to the conventional sinusoidal modulation (SM), all duty cycles are purely sinusoidal. In this case, the phase a duty cycle is

$$d_{\rm a}(t) = M_1 \cos(\omega_{\rm m} t), \qquad (2.4)$$

and ranges within  $d_a(t) = -1...1$ . The inverter phase *a* output voltage is in general proportional to the duty cycle  $d_a$

$$u_{a\bar{o}}(t) = d_{a}(t)\frac{U_{i}}{2} \stackrel{(2.1)}{=} M_{1}\frac{U_{i}}{2}\cos(\omega_{m}t) + d_{CM}(t)\frac{U_{i}}{2}, \qquad (2.5)$$

and is simplified, in the case of SM, to

$$u_{a\bar{o}}(t) = M_1 \frac{U_i}{2} \cos(\omega_m t).$$

(2.6)

The inductor voltage is equal to the difference between the switch-node voltage and the inverter output voltage

$$u_{L_{o,a}}(t) = u_{\bar{a}\bar{o}}(t) - u_{a\bar{o}}(t).$$

(2.7)

The switch-node  $\bar{a}$  features a two-level PWM voltage  $u_{\bar{a}\bar{o}}(t)$ , which assumes two values  $u_{\bar{a}\bar{o}} = \{-\frac{U_i}{2}, +\frac{U_i}{2}\}$ . As a result, the inductor also features a twolevel PWM voltage  $u_{L_o,a}(t)$ , in the case of an FSF. The two-level PWM inductor voltage induces a high-frequency current ripple across the inductor. Note that, the inductor would feature a five-level PWM voltage in the case of a simple DM filter, which would result in a significantly lower inductor current ripple, compared to an FSF. The local (instantaneous) current ripple amplitude of the inductor  $L_o$  is

$$\Delta i_{\rm L_o,a,PK}(t) = (1+d_{\rm a})(1-d_{\rm a})\frac{U_{\rm i}}{8L_{\rm o}f_{\rm s}}.$$

(2.8)

Accordingly, the local RMS current ripple is

$$\Delta i_{\rm L_{o,a,RMS}}(t) = \frac{\Delta i_{\rm L_{o,a,PK}}(t)}{\sqrt{3}} = (1+d_{\rm a})(1-d_{\rm a})\frac{U_{\rm i}}{8\sqrt{3}L_{\rm o}f_{\rm s}},$$

(2.9)

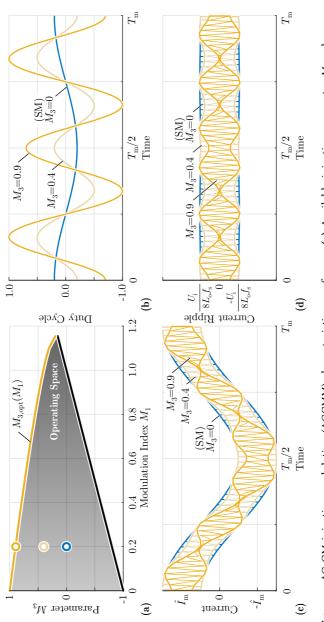

and is visualized in Fig. 2.2(a). The duty cycle  $d_a = 0$  maximizes the local current ripple of the filter inductor

$$\Delta I_{\mathrm{L}_{\mathrm{o}},\mathrm{PK},\mathrm{max}} = \frac{U_{\mathrm{i}}}{8L_{\mathrm{o}}f_{\mathrm{s}}}, \qquad \Delta I_{\mathrm{L}_{\mathrm{o}},\mathrm{RMS},\mathrm{max}} = \frac{U_{\mathrm{i}}}{8\sqrt{3}L_{\mathrm{o}}f_{\mathrm{s}}}, \qquad (2.10)$$

while the local current ripple retains a high values in the area closes to  $d_a = 0$ . In contrast, the current ripple is almost zero when the duty cycle  $d_a$  is in the vicinity of 1 or -1.

For SM and a low modulation index  $M_1 = 0.2$ , the duty cycles of all three phases remain close to zero for the whole fundamental period  $T_m$ , as shown in **Fig. 2.2(b)**. As a results, the current ripple **(2.9)** and hence the losses of the filter inductors are high. The inductor current and current ripple are visualised in **Fig. 2.2(c)** and **(d)**, respectively. For low modulation indexes, where the motor speed, voltage and power are low, high inductor current ripple/losses occur. Then, the ratio between losses and transmitted power is high, leading to a low part-load inverter efficiency. For a high modulation index  $M_1 = 1$ , the overall current ripple reduces (cf. **Fig. 2.2(c)** and **(d)**).

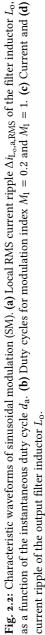

In order to reduce the current ripple occurring for low modulation indexes, the duty cycles should be modified. By moving the duty cycles away from the high current ripple zone of  $d_a = 0$ , it is possible to reduce the inductor current ripple. This can be achieved by means of a CM duty cycle injection, meaning that an identical signal  $d_{CM}(t)$  (either constant or time varying) is added to the duty cycles of all three phases (2.1). The positive impact of a CM duty cycle injection can be also explained from a frequency domain standpoint. In the case of SM modulation, the switch-node voltage  $u_{\bar{a}\bar{o}}(t)$  features a fundamental frequency  $f_{\rm m}$  component, which is related to the modulation index  $M_1$ . Furthermore, the switch-node voltage features switching frequency  $f_s$  harmonics, which are related to the PWM modulation. The switch-node voltage spectrum of a VSI employing SM is illustrated in Fig. 2.3(a). The injection of a low-frequency CM duty cycle advantageously shapes the spectral content of the switch-node voltage: Energy is transferred from the switching frequency  $f_s$  harmonics to the low-frequency that corresponds to the injected CM pattern. By reducing the high-frequency harmonic content of the switch-node voltage, the harmonic content of the inductor voltage is simultaneously decreased. As a result, the current ripple is reduced and accordingly the output filter losses are limited. Two CM duty cycle patterns are proposed in this chapter:

- (i) The constant CM injection (DCCMM) of Fig. 2.3(b.ii), where all three-phase duty cycles are shifted downwards, d<sub>CM</sub>(t) = −M<sub>0</sub>. As shown in Fig. 2.3(b.i), DCCMM shifts parts of the harmonic spectrum from the switching frequency f<sub>s</sub> to the DC frequency component f = 0.

- (ii) The time varying CM injection (ACCMM) of Fig. 2.3(c.ii), where a sinusoidal CM duty cycle  $d_{\text{CM}}(t) = -M_{\text{N}} \cos(N\omega_{\text{m}}t)$  (N = 3, 6, 9,...)

with a repetition frequency  $Nf_m$  and with arbitrarily large amplitude  $M_N$  is added to all three-phase duty cycles. As shown in **Fig. 2.3(c.i)**, ACCMM shifts parts of the harmonic spectrum from the switching frequency  $f_s$  to the low-frequency component  $f = Nf_m$ .

#### 2.1.2 DC CM Injection Modulation (DCCMM)

The DC CM injection modulation (DCCMM) utilizes a constant CM signal  $d_{\text{CM}} = -M_0$  that shifts all instantaneous sinusoidal duty cycle signals  $[d_a, d_b, d_c]$  away from the high current ripple region around d = 0, towards a lower ripple zone close to d = -1. The phase *a* duty cycle is

$$d_{\rm a}(t) = M_1 \cos(\omega_{\rm m} t) - M_0, \tag{2.11}$$

while the inverter phase *a* output voltage (2.5) is proportional to the duty cycle  $d_a$ ,

$$u_{a\bar{o}}(t) = M_1 \frac{U_i}{2} \cos(\omega_m t) - M_0 \frac{U_i}{2}.$$

(2.12)

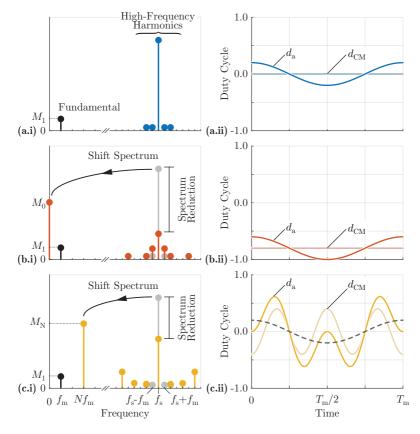

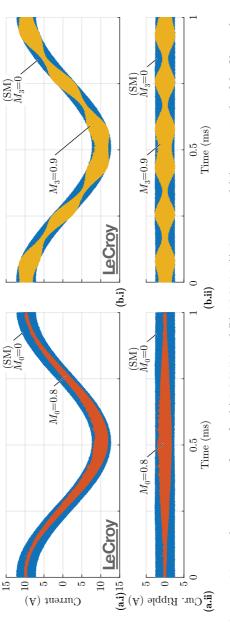

The DCCMM modulation strategy is visualized in Fig. 2.4(b) for a modulation index of  $M_1 = 0.2$ . There, two different injection parameter  $M_0$  values,  $M_0 = 0.4$  and  $M_0 = 0.8$ , are depicted. Furthermore, the case of  $M_0 = 0$  is shown, which is equivalent to simple SM. The effect of DCCMM on the inductor current and current ripple is shown in Fig. 2.4(c) and (d), respectively. The current ripple envelope is contracting with increasing CM injection  $M_0$ , thus DCCMM positively impacts the inductor performance. The parameter value  $M_0 = 0.8$  yields the lowest inductor current ripple, for the example at hand. It is noted, that DCCMM can also use negative injection values, i.e.  $M_0 < 0$ , with symmetric effects on the filter inductor current. For the conventional SM ( $M_0 = 0$ ), the current ripple reaches its maximum value at the zero crossings of the duty cycle, which occur at the time instants  $t = T_{\rm m}/4$ and  $t = 3T_{\rm m}/4$ . However, the time instances of the duty cycle zero crossing are changing for DCCMM. No duty cycle zero crossing occurs for example in 2.4(b) when  $M_0 = 0.4$  or  $M_0 = 0.8$ . In this case, the maximum current ripple is found at t = 0.

The CM injection parameter  $M_0$  represents a degree of freedom, that can be optimized. Depending on the modulation index  $M_1$ , a different range of the injection parameter  $M_0$  is available. The acceptable range of the  $M_0$  can be easily derived by the constraint that all three duty cycle signals must not

**Fig. 2.3:** (i) Spectrum of the switch-node voltage  $u_{\tilde{a}\tilde{o}}$ . (ii) Duty cycle  $d_a(t)$  of phase a and CM duty cycle injection  $d_{CM}(t)$ , into all three phases. (a) Conventional sinusoidal modulation (SM). (b) DC CM injection modulation (DCCMM), where the duty cycle is shifted downwards by  $d_{CM} = -M_0$ . Spectral content is transferred from the switching frequency  $f_s$  to the DC component f = 0. (c) AC CM injection modulation (ACCMM), where a sinusoidal CM duty cycle  $d_{CM}(t) = -M_N \cos(N\omega_m t)$  is injected. Spectral content is transferred from the switching frequency  $f_s$  to the CM duty cycle repetition frequency  $f_s$  to the CM duty cycle repetition frequency  $f = N f_m$ .

Fig. 2.4: DC CM injection modulation (DCCMM) characteristic waveforms. (a) Available injection parameter M<sub>0</sub> value range, depending on the modulation index  $M_1$ . (b) Phase a duty cycle for a modulation index  $M_1 = 0.2$  and different values of the CMinjection parameter  $M_0$ . (c) Current and (d) current ripple of the filter inductor  $L_0$ .

exceed the carrier boundaries (i.e.  $-1 \le d \le 1$ ). Depending on the modulation depth  $M_1$ , the  $M_0$  injection limits are shown in **Fig. 2.4(a)** and are

$$-(1-M_1) \le M_0 \le 1-M_1. \tag{2.13}$$

It is noted, that the feasible  $M_0$  interval becomes wider for low modulation depths  $M_1$ . For the example  $M_1 = 0.2$  of **Fig. 2.4**, the  $M_0$  parameter can be freely selected within the interval  $M_0 = -0.8... + 0.8$ . In contrast, for  $M_1 = 1$ , the  $M_0$  parameter value must be kept at zero, otherwise the instantaneous duty cycles would exceed the carrier boundaries. When  $M_1 > 1$  (i.e. overmodulation), the DCCMM modulation is impractical, since it provokes undesired pulse dropping which in return significantly increases the inductor current ripple. Therefore, DCCMM is only advisable for the limited modulation index region  $M_1 = 0...1$ . The DCCMM is summarized in **Tab. 2.2**.

#### 2.1.3 AC CM Injection Modulation (ACCMM)

In a second step, the AC CM injection modulation (ACCMM) is investigated. There, a time varying CM pattern  $d_{\rm CM}(t) = -M_{\rm N} \cos(2\pi N f_{\rm m} t)$  (N = 3, 6, 9,...) is injected into the duty cycles of all three phases. This CM pattern features a sinusoidal shape, a repetition frequency of  $N f_{\rm m}$  and an amplitude  $M_{\rm N}$ . According to ACCMM, the high-frequency spectrum of the switch-node voltage  $u_{\bar{a}\bar{o}}$  is reduced, and instead more spectral content is concentrated at the CM pattern repetition frequency  $N f_{\rm m}$ , as is illustrated in Fig. 2.3(c). Hence, the high-frequency voltage across the inductor is reduced, resulting in lower current ripple/losses.

The repetition frequency of the CM signal  $Nf_{\rm m}$  is now selected. Special attention should be paid to the reactive current flowing through the filter capacitors  $C_{\rm o}$ . The total  $N^{th}$  order harmonic current  $\hat{I}_{C_{\rm o},N}$ , caused by the ACCMM is

$$\hat{I}_{C_{o},N} = \frac{3}{2} M_{N} U_{i} N \omega_{m} C_{o}.$$

(2.14)

This reactive current is proportional to the amplitude  $M_{\rm N}$  and the repetition frequency  $Nf_{\rm m}$  of the CM duty cycle pattern. Especially for high-speed motor drives, where the fundamental frequency  $f_{\rm m}$  can be in the kHz range, the reactive currents at the frequency  $Nf_{\rm m}$  become significant, hence should be limited. Otherwise, additional conduction losses would occur, degrading the overall system performance. In the course of this research, which focuses on high-speed drive systems, the repetition frequency of the AC CM duty cycle must be set to the lowest possible value of  $3f_{\rm m}$ . Thereby, the ACCMM reduces

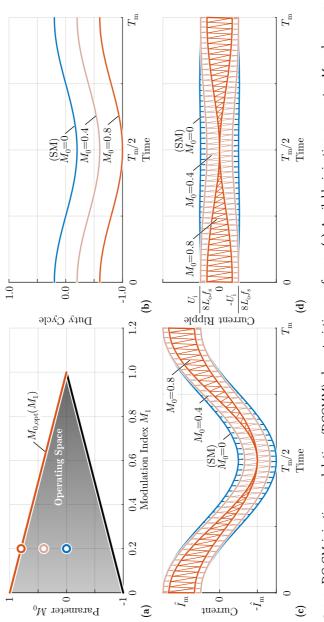

Fig. 2.5: AC CM injection modulation (ACCMM) characteristic waveforms. (a) Available injection parameter M<sub>3</sub> value range, depending on the modulation index  $M_1$ . (b) Phase a duty cycle for a modulation index  $M_1 = 0.2$  and different values of the CM injection parameter  $M_3$ . (c) Current and (d) current ripple of the filter inductor  $L_0$ .

to a generalized version of the third harmonic injection modulation scheme (THM). According to the conventional THM, the amplitude of the third harmonic  $M_3$  is typically set to 1/6 or 1/4, in order to extend the operating range of the inverter in the overmodulation area of  $M_1 = 1...2/\sqrt{3}$ . In contrast, for the proposed ACCMM, the amplitude of the third harmonic  $M_3$  is considered as a degree of freedom that can be optimized. As the conventional THM, AC-CMM can be used in the overmodulation region  $M_1 = 1...2/\sqrt{3}$ . As a result, the ACCMM can be used in a wider modulation index range of  $M_1 = 0...2/\sqrt{3}$ , compared to the restricted operating range of  $M_1 = 0...1$  of the DCCMM.

From now on, an ACCMM where the CM duty cycle pattern features a repetition frequency of  $3f_{\rm m}$  (third harmonic) is exclusively considered. According to ACCMM, the phase *a* duty cycle is

$$d_{a}(t) = M_{1}\cos(\omega_{m}t) - M_{3}\cos(3\omega_{m}t), \qquad (2.15)$$

while the inverter phase *a* output voltage (2.5) is proportional to the duty cycle  $d_a$

$$u_{a\bar{o}}(t) = M_1 \frac{U_i}{2} \cos(\omega_m t) - M_3 \frac{U_i}{2} \cos(3\omega_m t).$$

(2.16)

Therefore, in the case of ACCMM, the duty cycles and the inverter output voltages are non-sinusoidal. However, the difference between two inverter output voltages, which is equal to the motor line-to-line voltage, is still sinusoidal. In other words, it is possible to generate sinusoidal line-to-line motor voltages, by means of non-sinusoidal inverter output voltages. The ACCMM modulation strategy is visualized in Fig. 2.5(b), for a modulation index of  $M_1 = 0.2$ . There, two different  $M_3$  parameter values,  $M_3 = 0.4$  and  $M_3 = 0.9$ , are depicted. Furthermore, the case of  $M_3 = 0$  is shown, which is equivalent to simple SM. The effect of ACCMM on the inductor current and current ripple is shown in Fig. 2.5(c) and (d), respectively. As can be noticed, ACCMM shapes the current ripple envelope in a way that it continuously alternates between high and low current ripple. The overall inductor current stress decreases as the  $M_3$  parameter value increases, and the parameter value  $M_3 = 0.9$  yields the lowest inductor current ripple for the  $M_1 = 0.2$ example at hand. It is noted that, ACCMM can also use negative parameter values  $M_3 < 0$ , but the effect on the current is asymmetric, i.e. a parameter value  $-M_3$  results in a different current ripple stress on the filter inductor  $L_0$ , compared to a parameter value  $+M_3$ .

The CM injection parameter  $M_3$  represents a degree of freedom, that can be optimized. Depending on the modulation index  $M_1$ , a different range of the injection parameter  $M_3$  is available. Similarly to the case of DCCMM, the three duty cycles must be constrained within  $-1 \le d \le 1$ , in order to avoid pulse dropping. The  $M_3$  parameter limits are shown in **Fig. 2.5(a)** and are

$$-(1 - M_1) \le M_3 \le M_{3,\max}(M_1), \tag{2.17}$$

where the maximum allowed parameter value  $M_{3,\max}(M_1)$  is derived by numerically solving the non-linear equation

$$M_{3,\max}(M_1): \begin{cases} M_1 \cos(\phi) - M_{3,\max} \cos(3\phi) = 1\\ \phi = \sin^{-1} \left( \sqrt{\frac{9M_{3,\max} - M_1}{12M_{3,\max}}} \right) \end{cases}$$

(2.18)

In analogy to DCCMM, the available range of  $M_3$  parameter values for AC-CMM, is wider for low modulation depths  $M_1$ . The  $M_3$  parameter is increasingly restricted, for higher modulation indexes  $M_1$ . For the example of **Fig. 2.5**, where  $M_1 = 0.2$ , the  $M_3$  parameter can be freely selected within the interval  $M_3 = -0.8... + 0.9$ . For a modulation index  $M_1 = 1.0$ , the  $M_3$  parameter is restricted within the interval  $M_3 = 0... + 0.4$ . The ACCMM is summarized in **Tab. 2.2**.

# 2.2 Component Stresses

A comprehensive analysis of the component stresses, depending on the employed modulation strategy, is performed in this section. A sinusoidal motor current  $i_{m,a}(t) = \hat{I}_m \cos(\omega_m t - \phi)$ , lagging the motor voltage  $u_{m,a}(t) = \hat{U}_m \cos(\omega_m t)$  by a phase angle  $\phi$  is assumed [55], i.e. non-unity power factor  $\cos(\phi) < 1$ .

# 2.2.1 DC CM Injection Modulation (DCCMM)

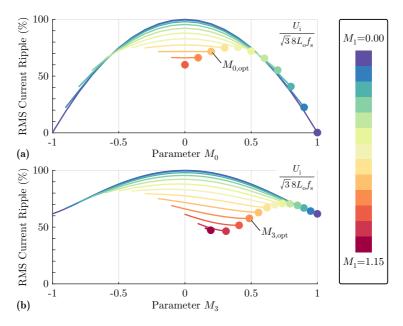

First, the RMS current ripple stress on the filter inductor  $L_0$  is analytically derived. The local RMS current ripple of (2.9) is integrated over the fundamental period  $T_m$  in order to derive the global (total) RMS current ripple

$$\Delta I_{\rm L_o,RMS} = \frac{U_{\rm i}}{8\sqrt{3}L_{\rm o}f_{\rm s}} \sqrt{\frac{1}{\pi} \int_0^{\pi} \left[ (1 + d_{\rm a}(\theta))(1 - d_{\rm a}(\theta)) \right]^2 d\theta}.$$

(2.19)

The resulting global RMS current ripple for DCCCM is

$$\Delta I_{\rm L_o,RMS} = \frac{U_{\rm i}}{8\sqrt{3}L_{\rm o}f_{\rm s}} \sqrt{\frac{3}{8}M_1^4 + M_1^2(3M_0^2 - 1) + (M_0^2 - 1)^2}.$$

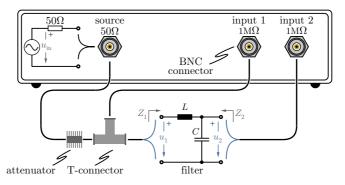

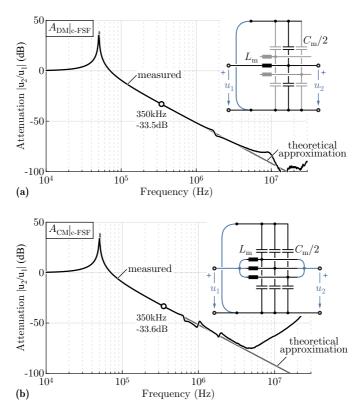

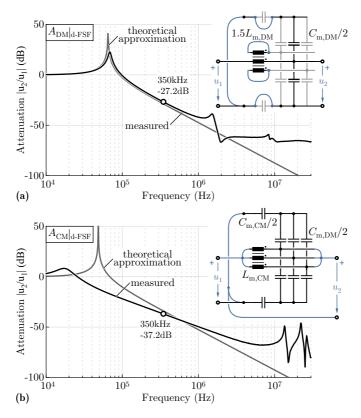

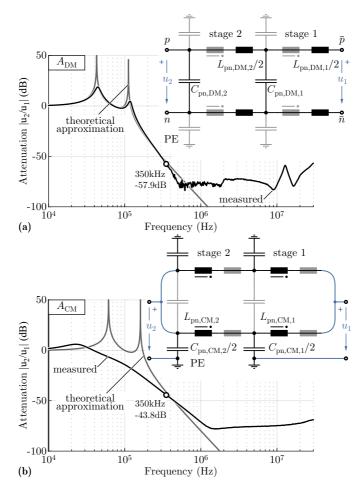

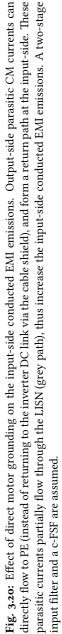

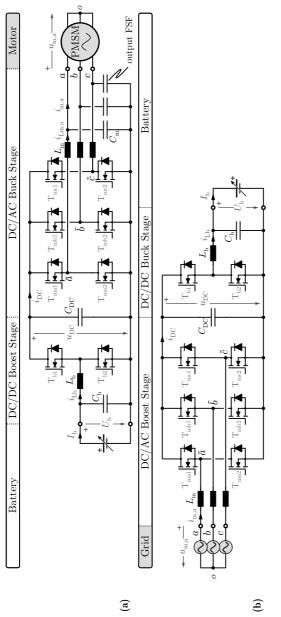

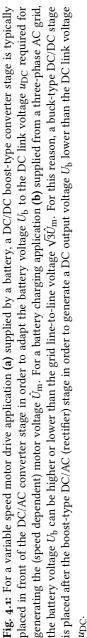

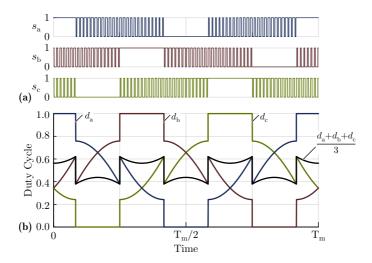

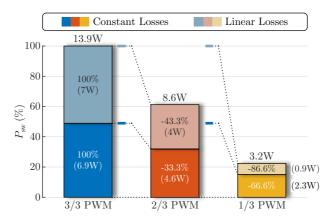

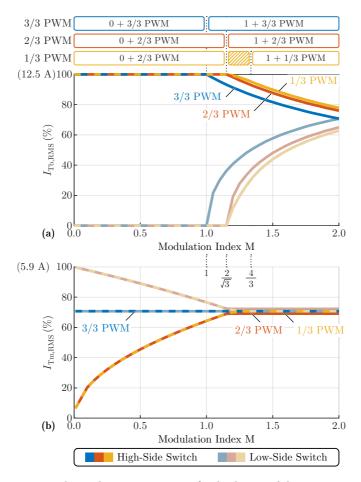

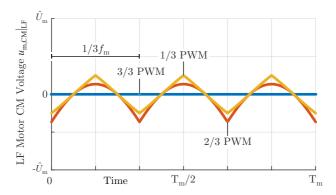

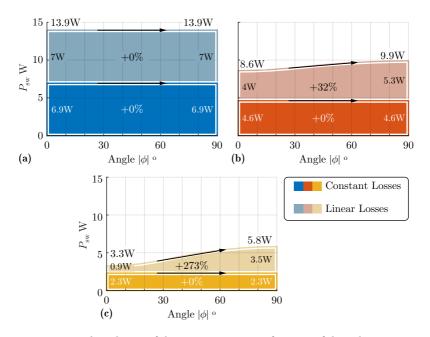

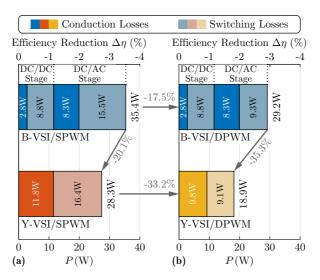

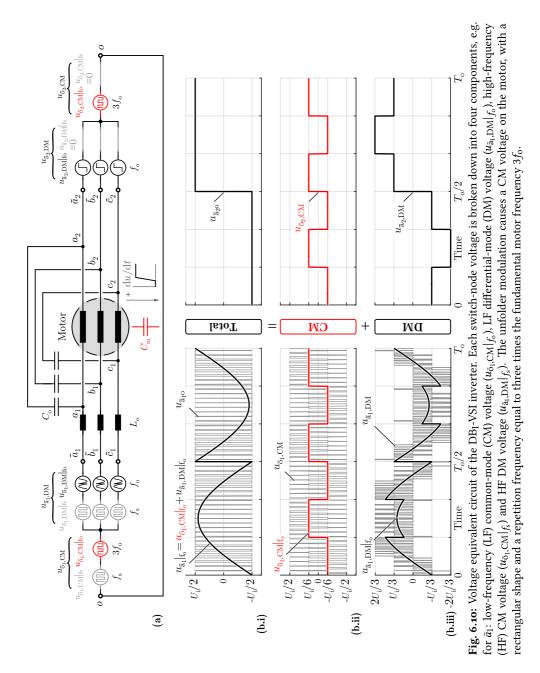

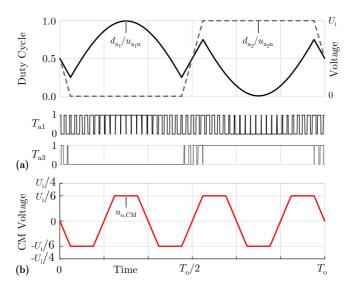

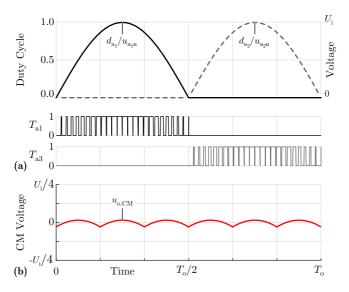

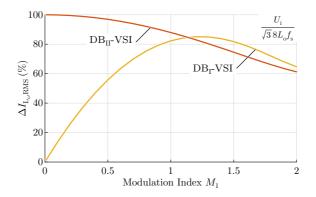

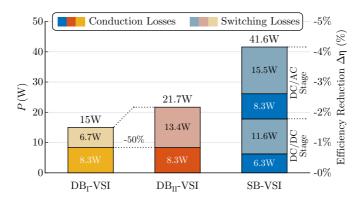

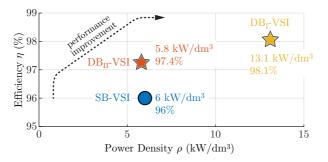

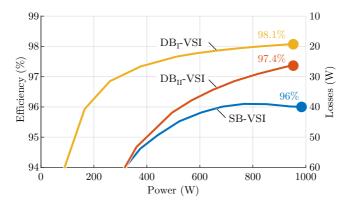

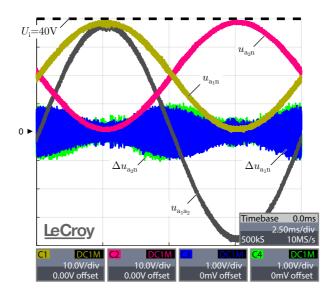

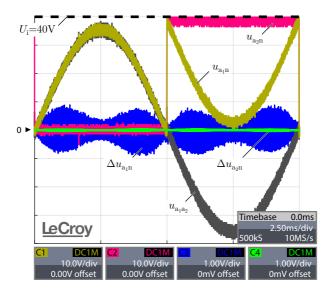

(2.20)