# Netzrückwirkungsarmes Dreiphasen-Pulsgleichrichtersystem mit weitem Eingangsspannungsbereich

# ABHANDLUNG zur Erlangung des Titels DOKTOR DER TECHNISCHEN WISSENSCHAFTEN der EIDGENÖSSISCHEN TECHNISCHE HOCHSCHULE ZÜRICH

vorgelegt von

THOMAS NUSSBAUMER

Dipl.-Ing., TU Wien geboren am 9. Mai 1975 von Österreich

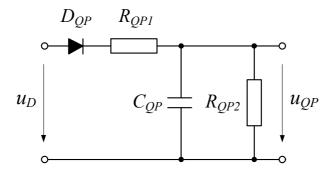

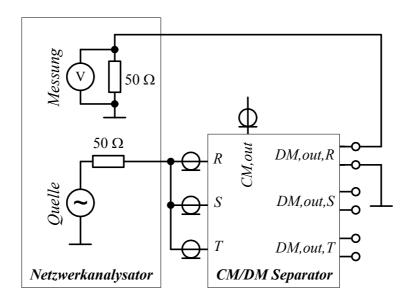

angenommen auf Antrag von Referent: Prof. Dr. J.W. Kolar Korreferent: Prof. Dr. T. Undeland

2004

Es ist nicht genug zu wissen, man muss es auch anwenden. Es ist nicht genug zu wollen, man muss es auch tun.

Johann Wolfgang von Goethe

#### Vorwort

Die vorliegende Arbeit entstand in den Jahren 2001 – 2004 während meiner Tätigkeit als wissenschaftlicher Mitarbeiter und Assistent an der Professur für Leistungselektronik und Messtechnik an der ETH Zürich.

In erster Linie möchte ich Herrn Prof. Dr. J.W. Kolar danken, mir die Möglichkeit gegeben zu haben, in diesem interessanten Forschungsbereich intensiv zu arbeiten. Seine stete Unterstützung und die Schaffung eines überaus produktiven Arbeitsklimas haben wesentlich zum Zustandekommen etlicher Veröffentlichungen und zum Gelingen dieser Arbeit beigetragen.

Grosser Dank gebührt auch Herrn Prof. Dr. T.M. Undeland für die freundliche Übernahme des Korreferates und sein Interesse an dieser Arbeit.

Bei allen Kollegen am Institut möchte ich mich ganz besonders für die entstandenen Freundschaften, die zahlreichen wertvollen Diskussionen, Hilfestellungen und Zusammenarbeiten bedanken, speziell mit meinen Bürokollegen Marcelo und Ahai.

Grosser Dank geht auch an die Mitarbeiter des Elektronik-Labors Peter Seitz und Hansueli Altorfer, mit deren tatkräftiger Hilfe die Hardware-Aufbauten erst möglich wurden.

Schliesslich möchte ich noch allen Studenten danken, die im Rahmen von Semesterund Diplomarbeiten einen Beitrag zu dieser Arbeit geleistet haben.

### Inhaltsverzeichnis

| KURZFASSUNG                                   | 5  |

|-----------------------------------------------|----|

| ABSTRACT                                      | 9  |

| FORMELZEICHEN UND ABKÜRZUNGEN                 | 11 |

| EINFÜHRUNG                                    | 17 |

| 2 FUNKTIONSWEISE                              | 29 |

| 2.1 Buck-Eingangsteil                         | 29 |

| 2.1.1 Grundsätzliche Betrachtungen            |    |

| 2.1.2 Schaltzustände                          |    |

| 2.1.3 Bildung des Soll-Stromraumzeigers       |    |

| 2.1.4 Berechnung der Einschaltdauern          |    |

| 2.2 Hochsetzsteller-Ausgangsteil              | 42 |

| 2.3 Betriebsbereich des Buck+Boost-Konverters | 43 |

| 3 SYSTEMDESIGN                                | 49 |

| 3.1 Auswahl der Leistungshalbleiter           | 49 |

| 3.1.1 Strombelastung                          |    |

| 3.1.2 Sperrspannungsbeanspruchung             | 55 |

| 3.1.3 Auswahl der Leistungshalbleiter         |    |

| 3.2 Analyse des Schaltverhaltens              | 58 |

| 3.2.1 Analyse des Leistungsmoduls             |    |

| 3.2.2 Analyse des PCB-Lavouts                 | 61 |

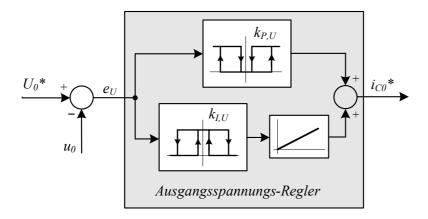

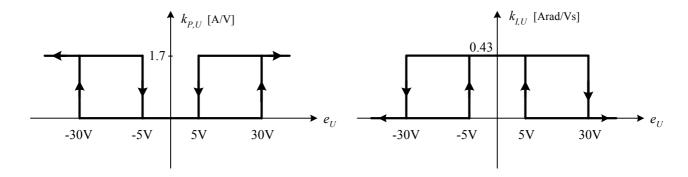

| 6.3 T  | eilblöcke der Regelung                                             | 186 |

|--------|--------------------------------------------------------------------|-----|

| 6.3.1  | Ausgangsspannungs-Regler                                           | 186 |

| 6.3.2  | Laststromvorsteuerung                                              |     |

| 6.3.3  | Amplitudendetektion                                                | 190 |

| 6.3.4  | Sollstrom-Skalierung                                               | 191 |

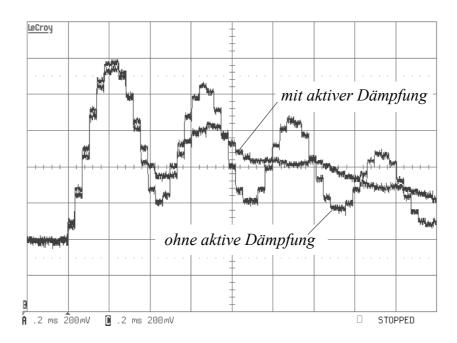

| 6.3.5  | Aktive Dämpfung.                                                   | 193 |

|        | Pigitale Implementierung                                           |     |

| 6.4.1  | Totzeiten des Systems                                              |     |

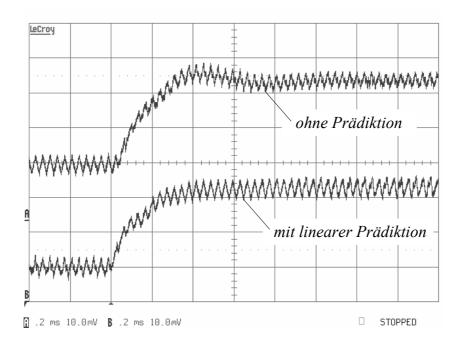

| 6.4.2  | Lineare Prädiktion.                                                |     |

| 6.4.3  | Smith-Prädiktion                                                   | 207 |

| 6.5 A  | Luslegung der Regelung                                             |     |

| 6.5.1  | Bestimmung des kritischen Arbeitspunktes                           |     |

| 6.5.2  | Entwurf des innerer Stromreglers                                   |     |

| 6.5.3  | Entwurf des äusseren Spannungsreglers                              | 217 |

| 7 EX   | PERIMENTELLE ANALYSE                                               | 219 |

| 8 BE   | RWERTUNG DES SYSTEMS                                               | 237 |

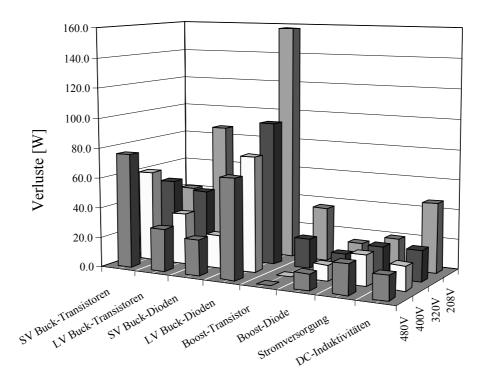

| 8.1 E  | Buck+Boost-Topologie                                               | 240 |

| 8.2 E  | Boost+Buck-Topologie (Vienna Rectifier + Dreipunkt-Buck-Konverter) | 243 |

| 8.3 V  | ergleich der Topologien                                            | 249 |

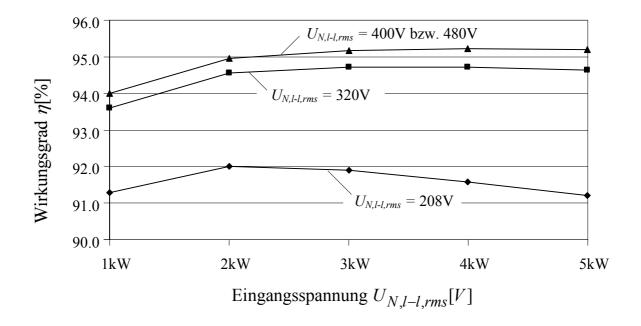

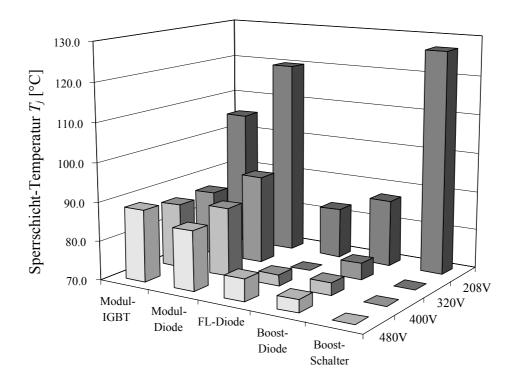

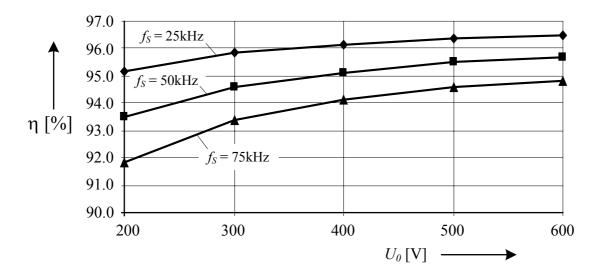

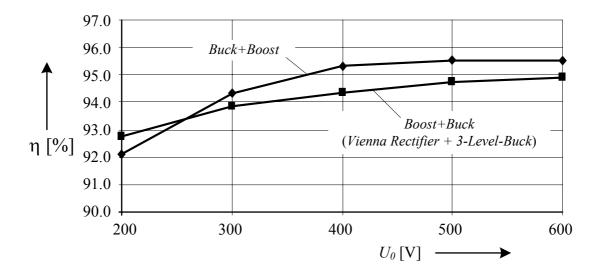

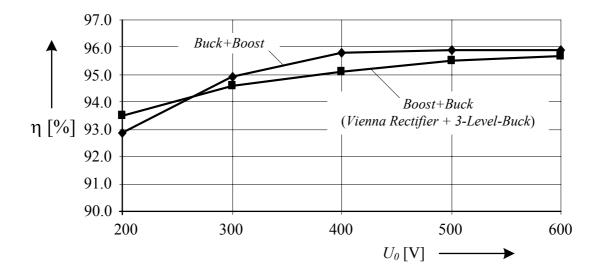

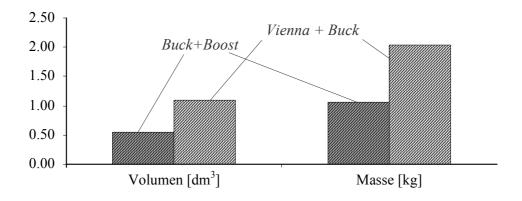

| 8.3.1  | Gesamtwirkungsgrad                                                 | 249 |

| 8.3.2  | Leistungsdichte                                                    | 251 |

| 8.3.3  | Realisierungsaufwand                                               | 253 |

| AUSBL  | ICK                                                                | 255 |

| ZUSAM  | MENFASSUNG                                                         | 259 |

| LITERA | ATURVERZEICHNIS                                                    | 261 |

### Kurzfassung

Zur dreiphasigen Speisung des Spannungszwischenkreises von Drehstromantrieben oder zur Speisung informationsverarbeitender Systeme werden anstelle passiver Gleichrichterschaltungen zunehmend aktive Systeme mit sinusförmigem Eingangsstrom und regelbarer Ausgangsspannung verwendet. Üblicherweise werden dabei Topologien mit eingangsseitigem Hochsetzsteller eingesetzt, wobei für zahlreiche Applikationen genauso auch tiefsetzstellerbasierte Strukturen denkbar wären.

In dieser Arbeit wird eine neuartige Schaltungsfunktion, die durch Integration eines tiefsetzstellerbasierten Dreischalter-Eingangsgleichrichters und eines DC/DC Boost Konverters gebildet wird, vorgestellt und im Detail analysiert. Diese Topologie weist einerseits einen weiten Ein-/Ausgangsspannungsbereich auf, andererseits kann der Betrieb auch bei Ausfall einer Netzphase mit sinusförmigem Eingangsstrom fortgesetzt werden, weshalb das System eine hohe Anwendungsbreite und hohe Fehlertoleranz aufweist und für einen zukünftigen industriellen Einsatz somit von besonderem Interesse ist.

Nach einer kurzen Einführung in die Schaltungsfunktion in **Kapitel 1** werden in **Kapitel 2** die Grundzüge der Modulation und das Betriebsverhalten des Systems auf Grundlage von Raumzeigerrechnung erklärt und die Einschaltdauern der Transistoren für die Einstellung sinusförmiger Eingangsströme hergeleitet.

Anschliessend werden in Kapitel 3 die Bauelementebeanspruchungen der Leistungshalbleiter und passiven Komponenten für den gesamten Betriebsbereich ermit-

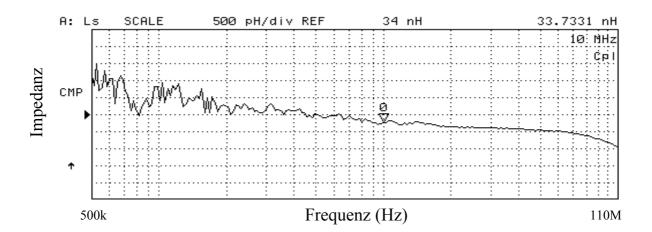

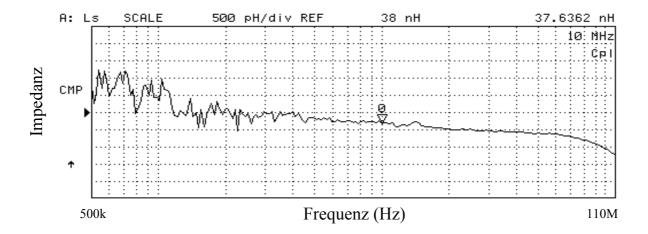

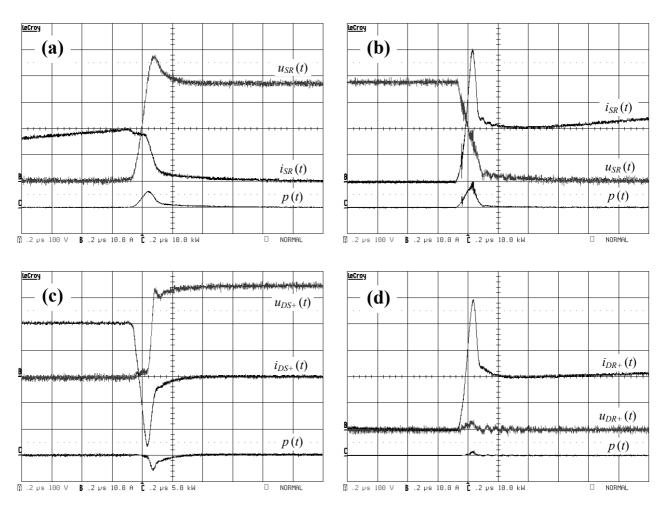

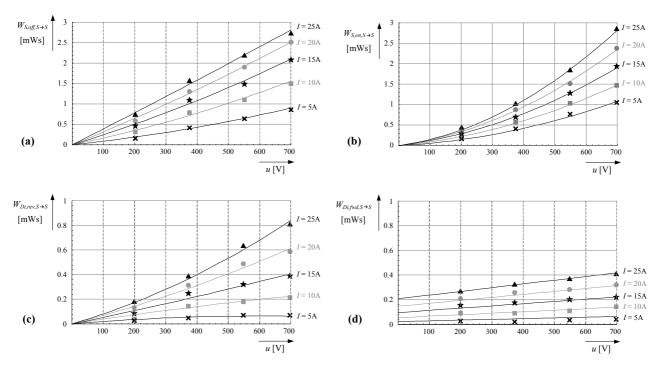

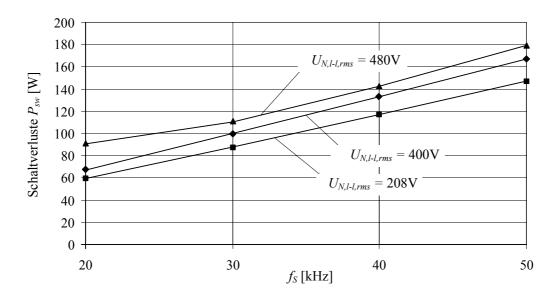

telt und darauf folgend Komponenten für ein System ausgewählt, welches in Kapitel 7 zur experimentellen Analyse herangezogen wird. Zur Ermittlung der Schaltverluste in Abhängigkeit vom Betriebspunkt des Systems werden sämtliche Kommutierungsvorgänge im Detail analysiert, wobei die parasitären, modulinternen Induktivitäten sowie die Induktivitäten der Verbindung der Komponenten über die Leistungsprintplatte eruiert und berücksichtigt werden.

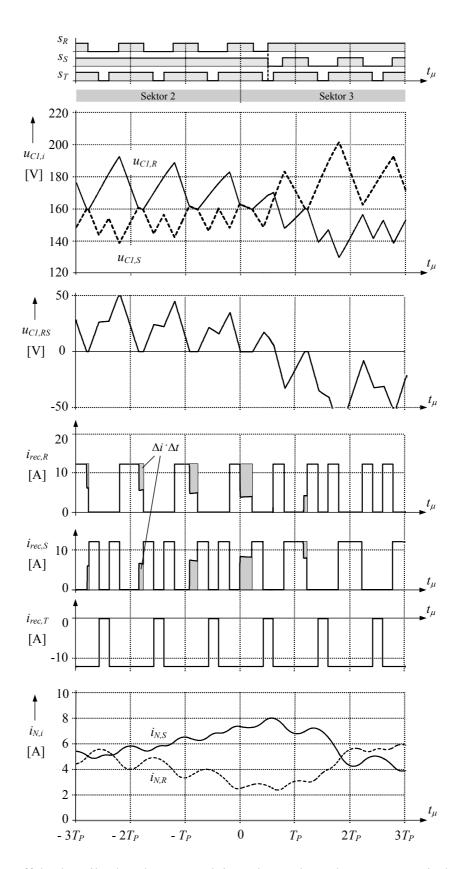

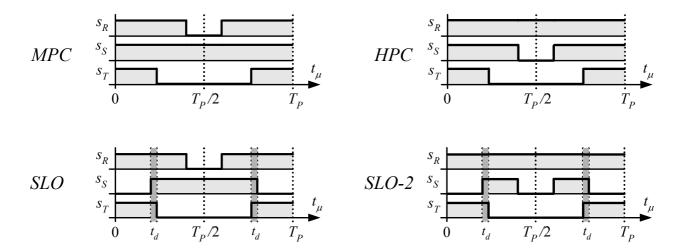

In **Kapitel 4** werden unterschiedliche Modulationsverfahren für die Steuerung des Systems entwickelt und verglichen. Schliesslich wird ein optimales Verfahren gefunden, das minimale Eingangsstromverzerrungen und gleichzeitig minimale Schaltverluste garantiert.

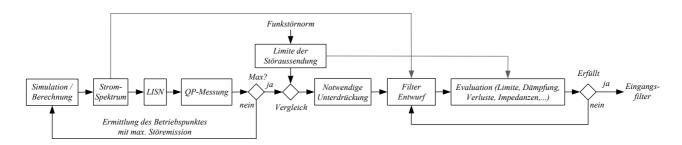

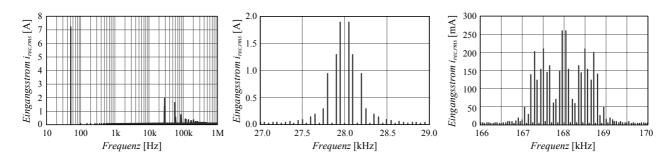

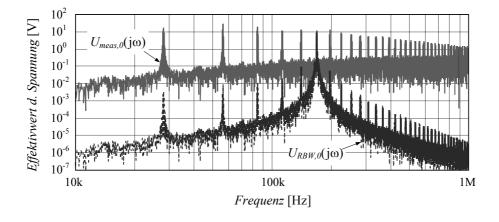

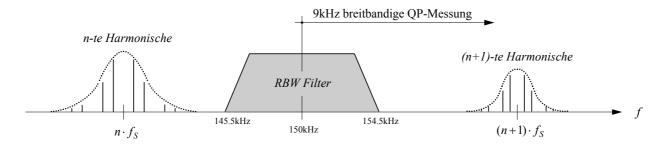

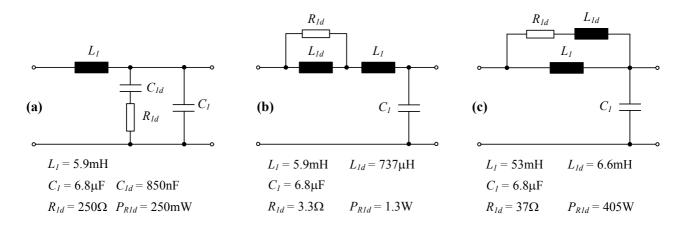

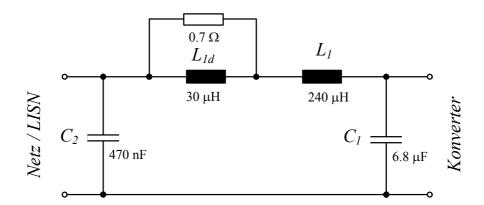

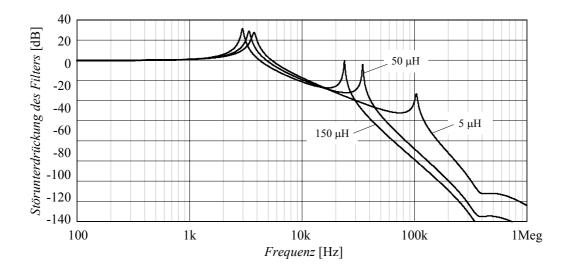

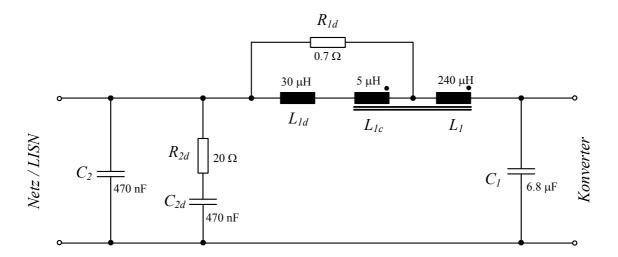

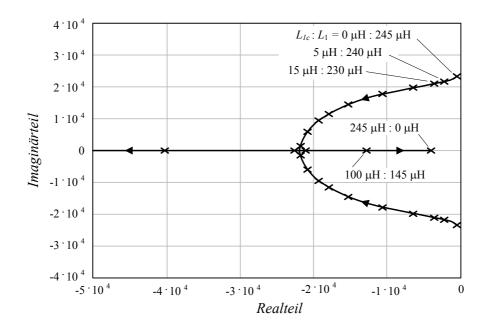

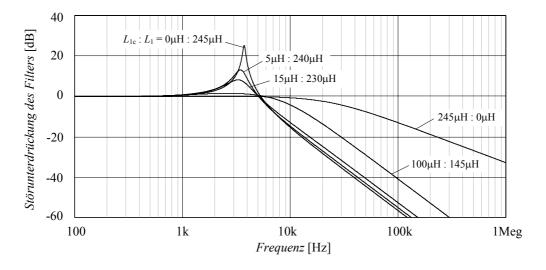

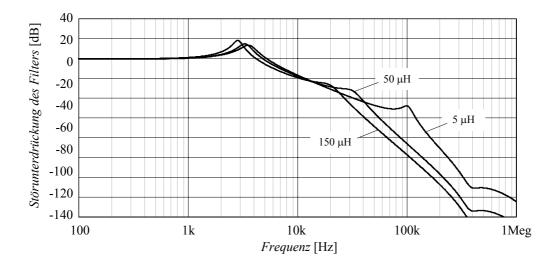

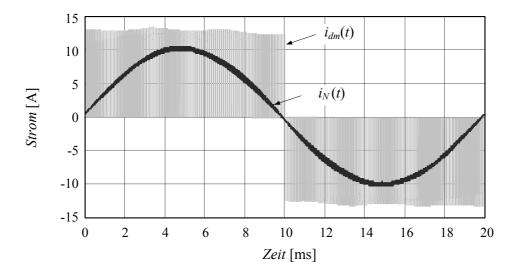

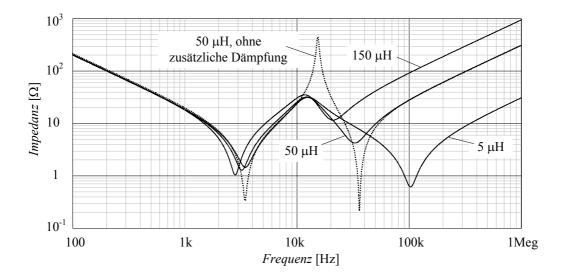

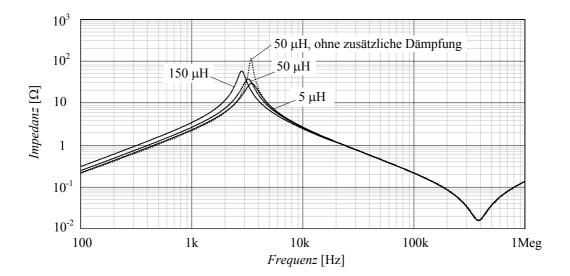

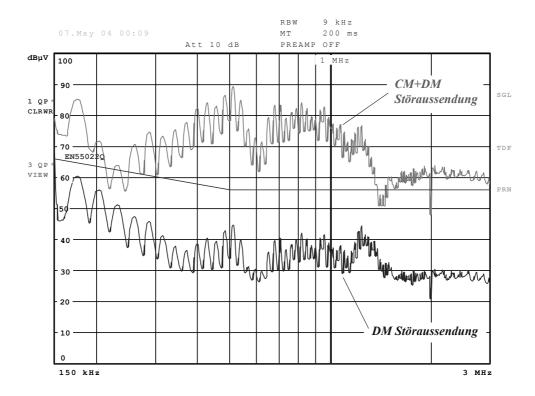

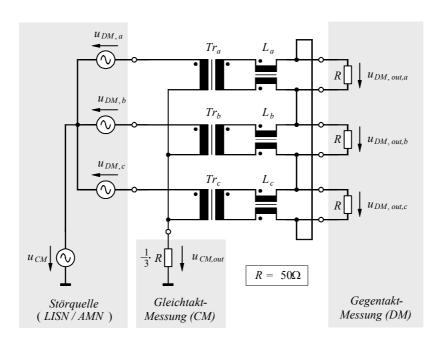

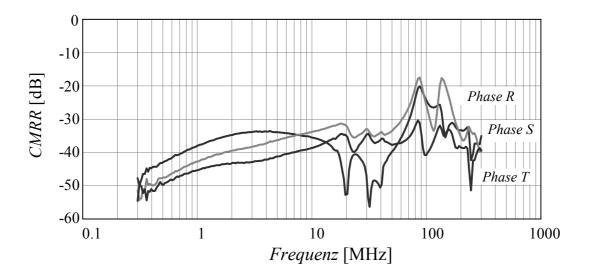

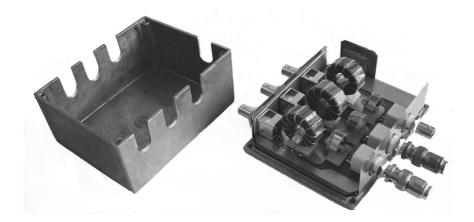

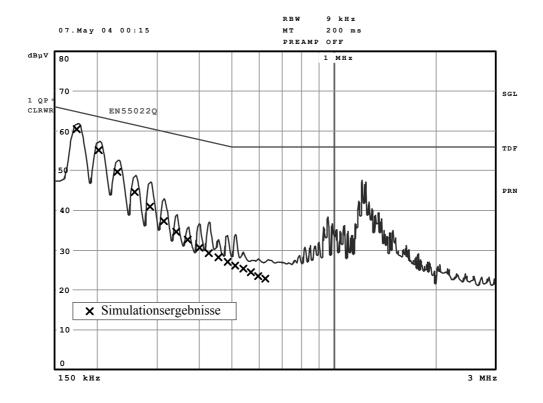

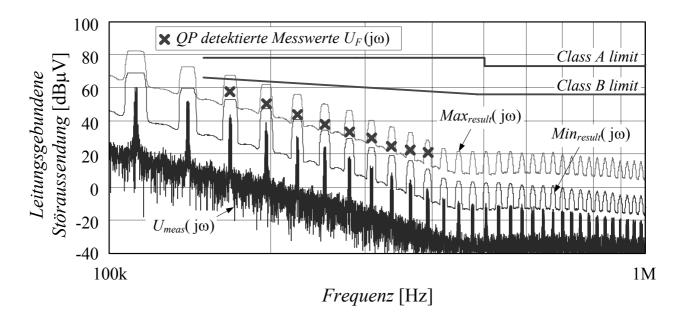

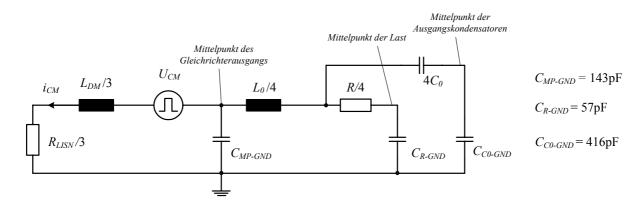

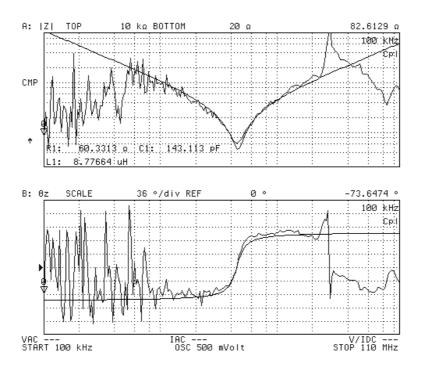

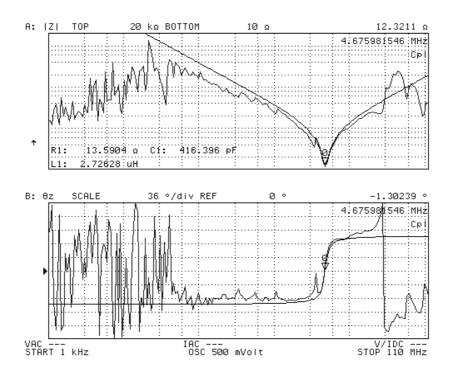

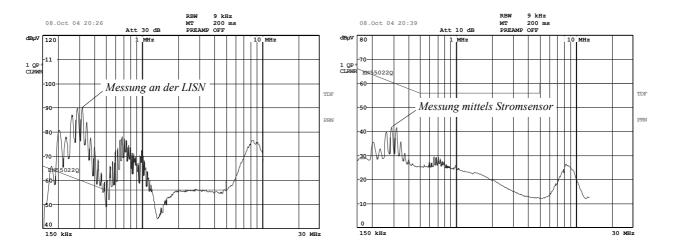

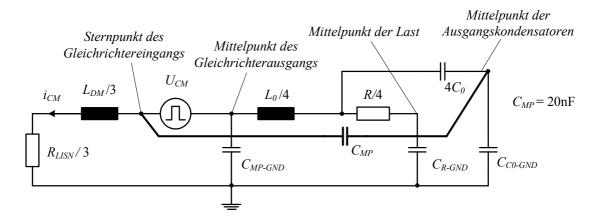

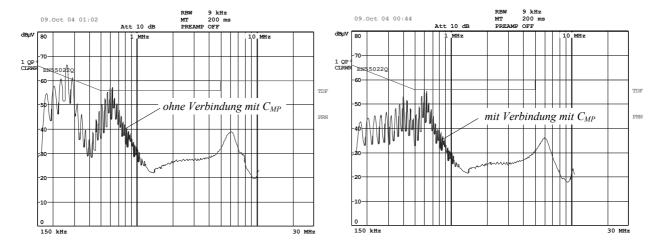

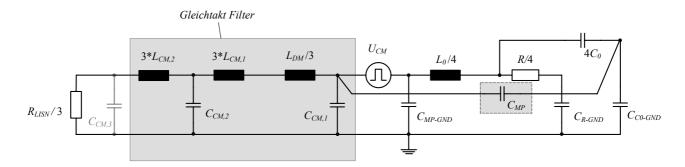

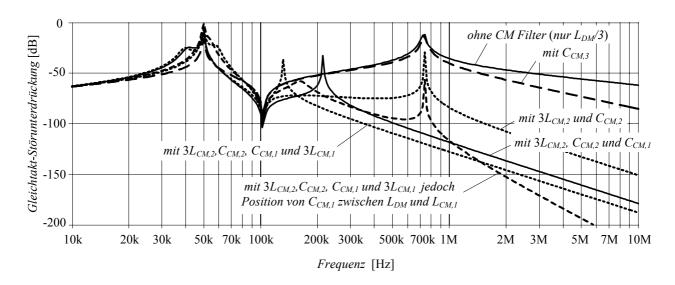

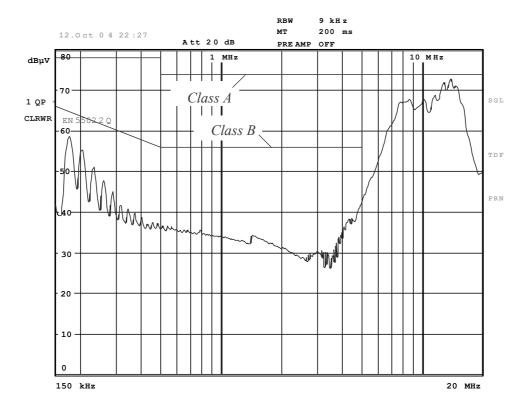

In **Kapitel 5** wird ein mehrstufiges Eingangsfilter entworfen, welches die Einhaltung der Vorschriften bezüglich leitungsgebundener Gleichtakt- und Gegentaktstöraussendung im Bereich 150kHz-30MHz sicherstellt. Dabei wird das Filter hinsichtlich der passive Dämpfung und der Minimierung des Filtervolumens optimiert. Es zeigt sich, dass eine systematische, die Gleichtakt- und Gegentaktstöraussendung separat behandelnde Vorgehensweise beim Filterentwurf sinnvoll ist, und auf Grundlage von Simulationsdaten und Berechnungen das Filter so entworfen werden kann, dass eine hinreichende Dämpfung der Störaussendungen erreicht wird, was durch die Funkstörmessungen schlussendlich bestätigt wird.

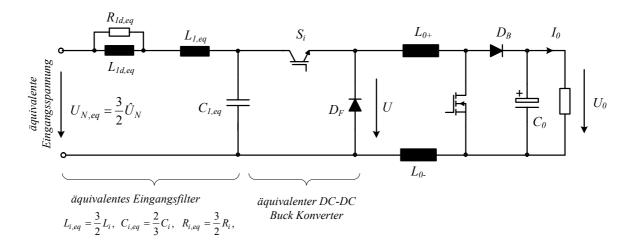

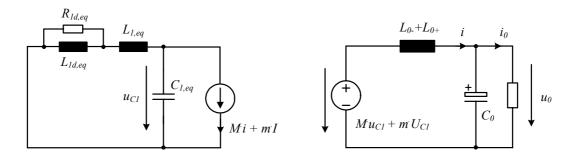

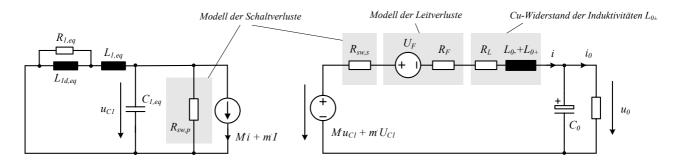

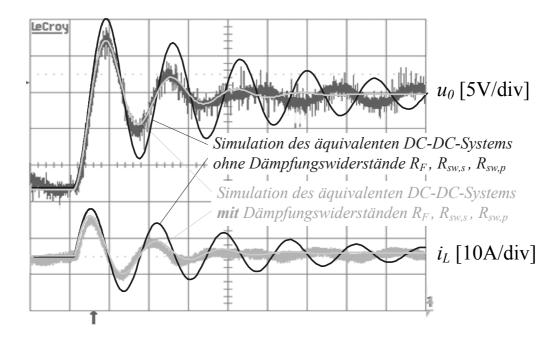

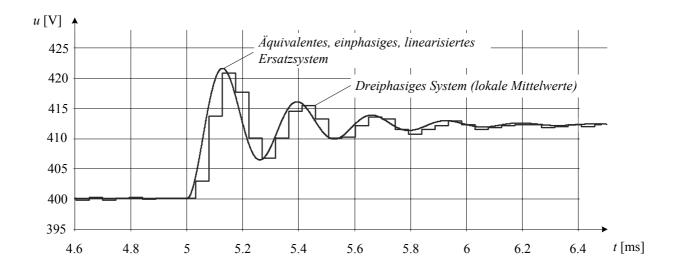

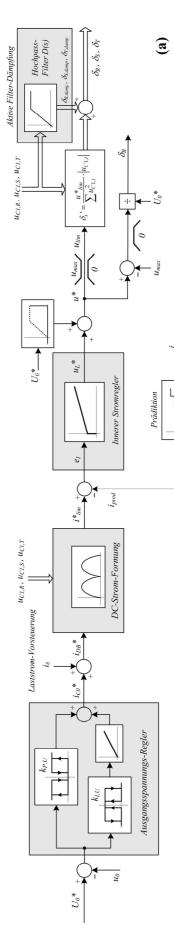

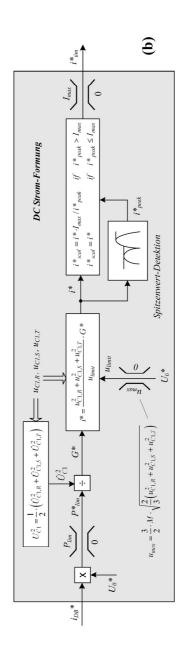

Um die Regelung für das Systems auslegen zu können, wird zu Beginn des Kapitel 6 ein regelungstechnisches Modell unter Einbeziehung des AC-seitigen, dreiphasigen Konverterteiles in Form eines ordnungsreduzierten DC-DC Ersatzmodells entwickelt und verifiziert. Damit wird eine zweischleifige digitale Regelung entworfen, welche die Aufnahme von sinusförmigen Netzströmen auch bei unsymmetrischer Netzspannung oder Phasenausfall des Netzes sicherstellt und eine aktive Dämpfung des Eingangsfilters sowie eine Vorsteuerung des Laststroms beinhaltet. Die Regelung ist so strukturiert, dass die Ablösung zwischen den beiden Betriebsmodi selbsttätig erfolgt. Im Reglerentwurf werden dabei die Verzögerungszeiten durch Abtastung, digitale Regelung und Pulsmusterausgabe ebenso berücksichtigt wie die in der Regelstruktur enthaltene Netzspannungs- und Laststromvorsteuerung.

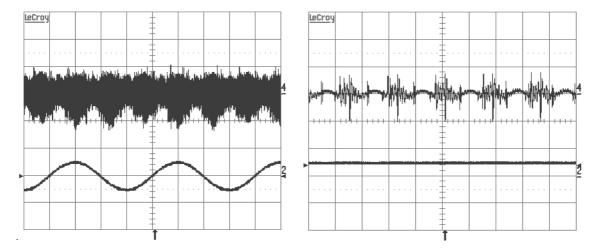

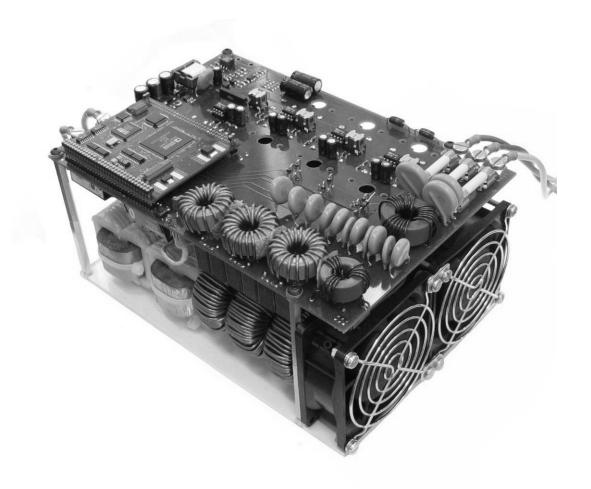

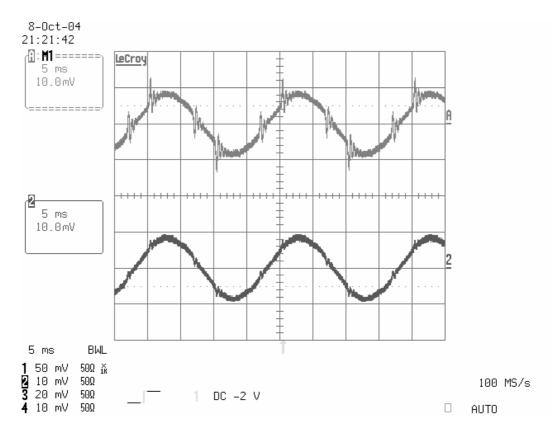

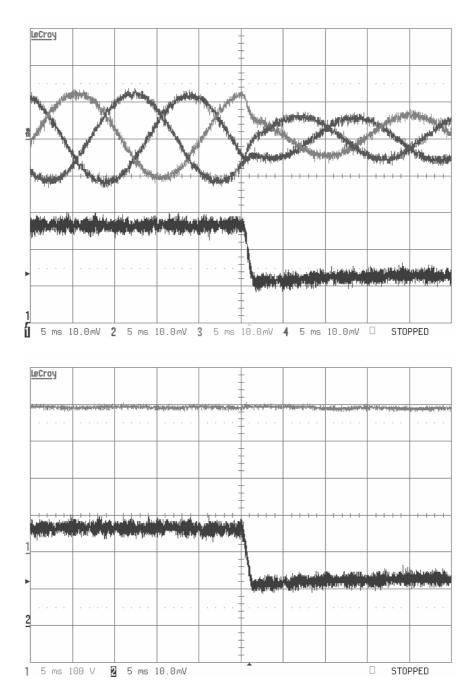

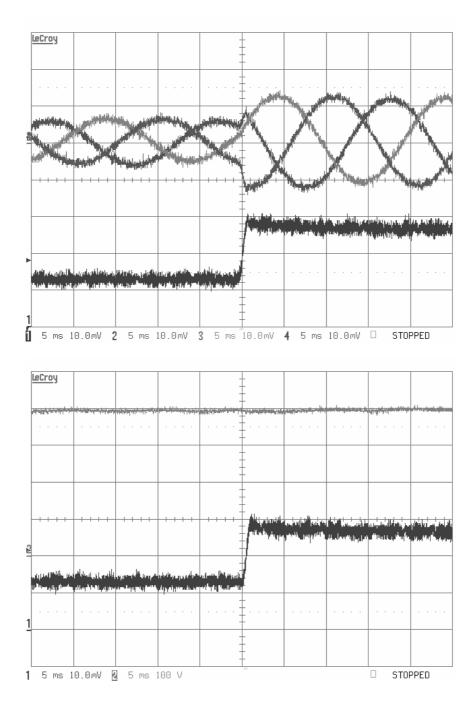

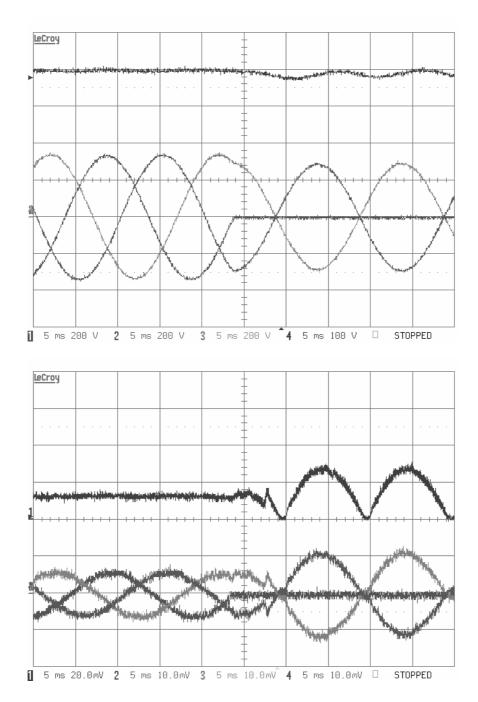

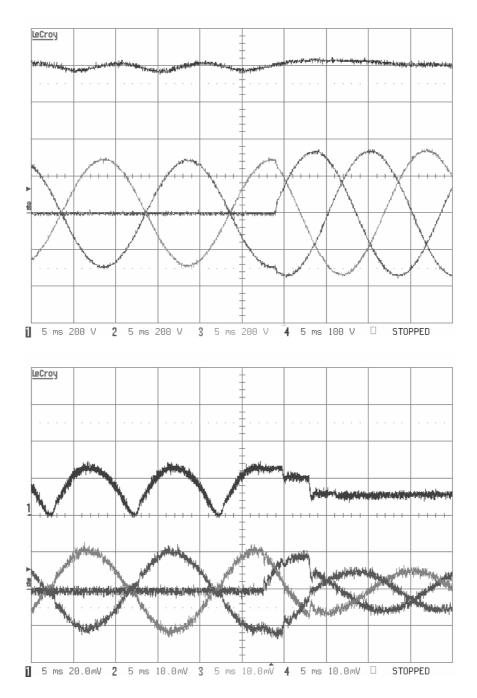

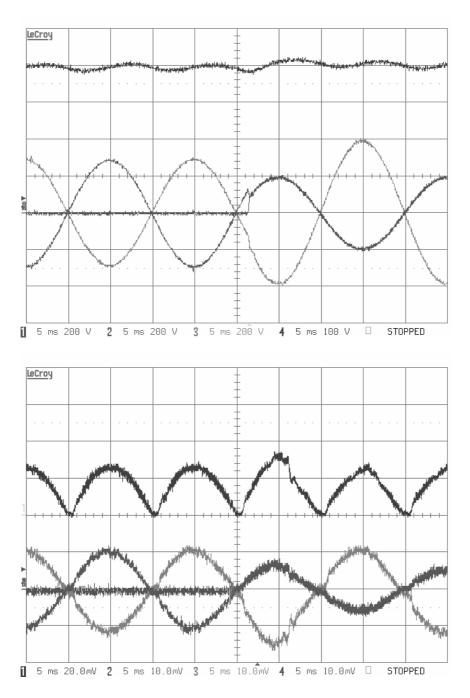

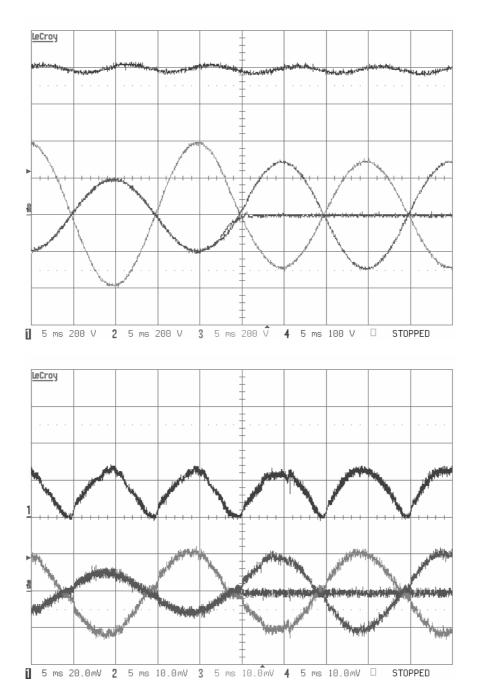

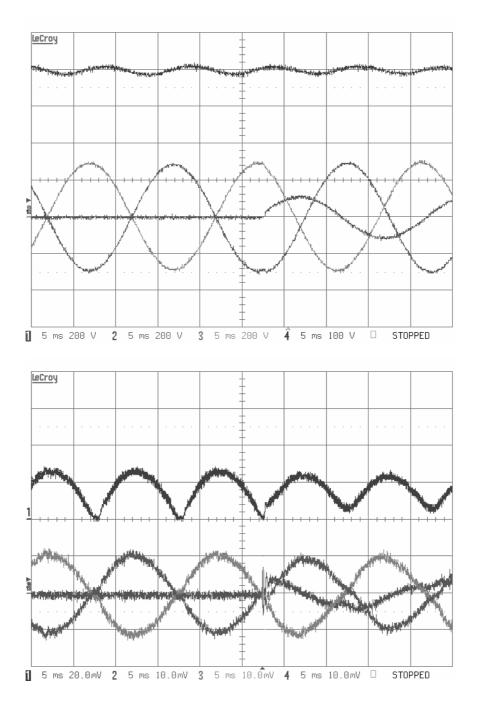

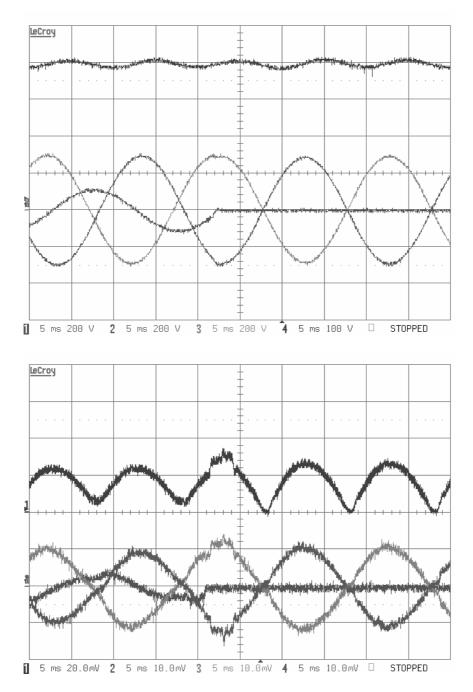

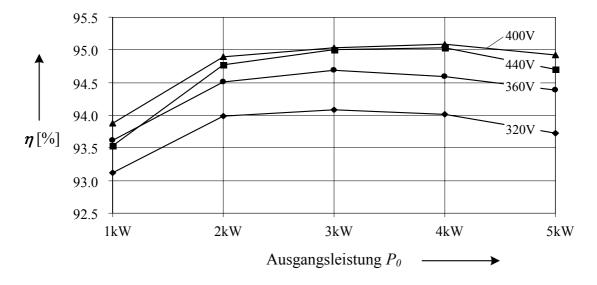

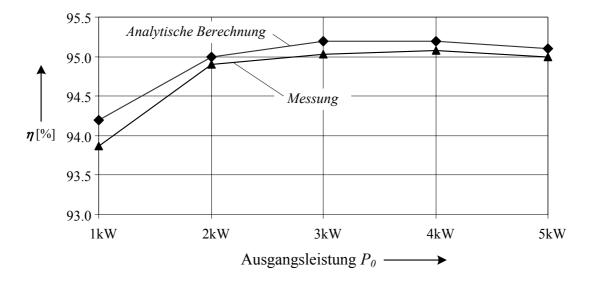

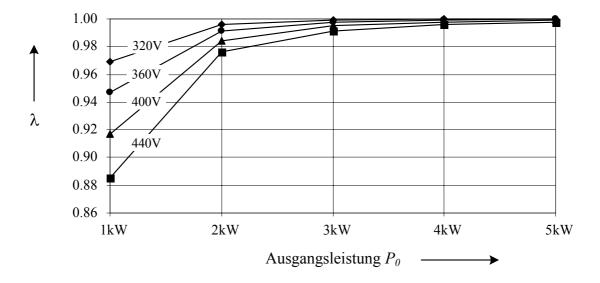

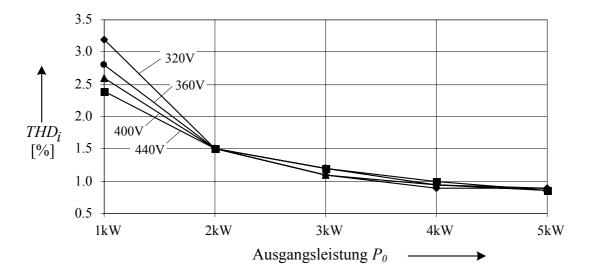

In **Kapitel 7** wird die experimentelle Analyse des Systems anhand eines hochkompakten Hardware-Prototyps mit digitaler Regelung auf einer DSP-Plattform durchgeführt. Insbesondere werden der Wirkungsgrad, der Leistungsfaktor und der Oberschwingungsgehalt der Eingangsströme in Abhängigkeit vom Betriebspunkt des Systems ermittelt und die Beherrschung von beliebigen unsymmetrischen Verhältnissen der Netzphasenspannungen gezeigt. Weiter wird bestätigt, dass die Regelung für transient auftretende Netzphasenfehler wie etwa Phasenausfall, Phasenkurzschluss oder Phasenerdschluss weiterhin eine sinusförmige Stromaufnahme garantiert.

Abschliessend wird das System in **Kapitel 8** mit einem hochsetzstellerbasierten Dreiphasen-Dreischalter-Dreipunkt-Gleichrichtersystems (Vienna Rectifier) mit ausgangsseitigem Tiefsetzsteller verglichen. Das System ist hinsichtlich Realisierungsaufwand, Leistungsdichte und Wirkungsgrad dem hochsetzstellerbasierten System überlegen und somit für zahlreiche zukünftige Applikationen von hohem Interesse.

#### **Abstract**

For the three-phase power supply of motor drives and information technology systems progressively more electronically controlled systems are employed which allow achieving sinusoidal input currents and controllable output voltage in contrast to passive rectifiers. Nowadays, most of the systems employ a boost-type rectifier input stage, whereby for many applications buck-type input stages could be an interesting alternative.

In this work, a novel topology formed by the integration of a buck-type, three-switch rectifier input stage and a DC-DC boost-type output stage is presented and analyzed in detail. Due to the buck-boost operation a wide input and/or output voltage range can be achieved. Furthermore, a reliable operation of the system maintaining sinusoidal input currents under heavily unbalanced mains condition can be ensured, wherefore the topology is of high interest for a future industrial application.

After a short introduction in **chapter 1**, where the system topology is presented, in **chapter 2** the operation of the system is explained on the basis of space vector calculations. The relative on-times of the transistors for generating sinusoidal input currents are derived.

In **chapter 3** the voltage and current stresses of the active and passive components are determined and appropriate components are selected. In order to calculate the system efficiency in dependency of the operating point all commutation processes

during a switching period are analyzed carefully and the inductances of the parasitic paths inside the power modules and on the PCB are measured.

In **chapter 4** several modulation methods are developed and evaluated comparatively. Finally, a modulation technique is selected which ensures good input current quality by preventing the excitation of the input filter at the sector boundaries while maintaining minimum switching losses.

In **chapter 5** a multi-stage input filter is designed, which ensures full compliance with the standards concerning common mode and differential mode conducted emissions. In addition, the filter is optimized concerning passive damping and minimum volume. It is shown that a systematic approach with separate analysis of the common mode and differential mode noise is successful and that the filter design can be completely performed with simulation data and calculations, which is shown by the means of conducted emission measurements.

For the design of the control in **chapter 6**, first a control-orientated, reduced order DC-DC model of the three-phase system is developed and verified. With this, a cascaded, digital control is designed which ensures sinusoidal input currents also for unsymmetrical mains phase condition and includes the active damping of the input filter and a feedforwarding of the load current. For the selection of the controller types and gains the delays caused by the sampling, the digital control and the generation of the pulse patterns are considered as well as precontrol of the mains voltages and the load current.

In **chapter 7** a 5kW hardware prototype with DSP control is analyzed experimentally. Efficiency, power factor and THD of the input currents are measured for different operating points and it is shown that the system can maintain correct operation with sinusoidal input currents for all kinds of phase unbalances, such as phase loss, short circuit of two phases and earth fault of a phase.

Finally, in **chapter 8** the performance of the system is compared with a three phase/level/switch boost-type (Vienna) rectifier with a three-level buck output stage. It is shown that the novel topology is superior concerning realization effort, power factor and efficiency, wherefore it will be of interest for various future applications.

## Formelzeichen und Abkürzungen

| $B_w$        | Reglerbandbreite                                                                   |

|--------------|------------------------------------------------------------------------------------|

| $C_0$        | Ausgangskondensator                                                                |

| $C_{I}$      | Eingangsfilterkondensator der Filterstufe 1                                        |

| $C_2$        | Eingangsfilterkondensator der Filterstufe 2                                        |

| $C_{2d}$     | Eingangsfilterkondensator im Dämpfungspfad der Filterstufe 2                       |

| D            | Filterfunktion der aktiven Dämpfung                                                |

| $D_B$        | Boost-Diode des ausgangsseitigen Hochsetzstellers                                  |

| $D_F$        | Freilaufdiode des eingangsseitigen Tiefsetzstellers                                |

| $D_i$        | Leistungsdioden des eingangsseitigen Tiefsetzstellers, allg.                       |

| $D_{i^\pm}$  | dem Zwischenkreis zugewandte Leistungsdioden des eingangsseitigen Tiefsetzstellers |

| $D_{N,i\pm}$ | dem Netz zugewandte Leistungsdioden des eingangsseitigen Tiefsetzstellers          |

| $e_I$        | Regelfehler des DC-Stromreglers                                                    |

| $e_U$        | Regelfehler des Ausgangsspannungsreglers                                           |

| $f_c$        | Knickfrequenz                                                                      |

| $f_N$        | Netzfrequenz                                                                       |

| $f_S$        | Schaltfrequenz                                                                     |

| G            | Eingangsleitwert                                                                   |

| i            | Strom in der DC-Induktivität $L_0$                                                 |

| $i_0$        | Ausgangsstrom                                                                      |

| $i_{Cl,i}$   | Eingangsseitige Filterkondensatorströme                                            |

Strom in der Hochsetzstellerdiode

Ströme in den eingangsseitigen Filterinduktivitäten

$i_D$

$i_{L1.i}$

| $i_{N,i}$    | Netzphasenströme                                                                     |

|--------------|--------------------------------------------------------------------------------------|

| $i_{rec,i}$  | Gleichrichtereingangsströme                                                          |

| j            | Schaltzustand des Gleichrichters                                                     |

| k            | Verstärkungsfaktor der aktiven Dämpfung                                              |

| k            | Kopplungsfaktor der magnetisch gekoppelten Induktivitäten $L_I$ und $L_{Ic}$         |

| $k_1$        | linearer Schaltverlustterm                                                           |

| $K_i$        | DC-Stromregler                                                                       |

| $K_u$        | Ausgangsspannungsregler                                                              |

| $k_{I,U}$    | Verstärkung des Integralanteils des Ausgangsspannungsreglers                         |

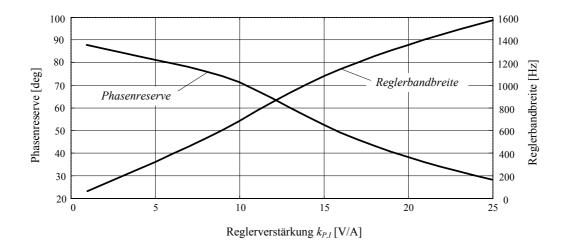

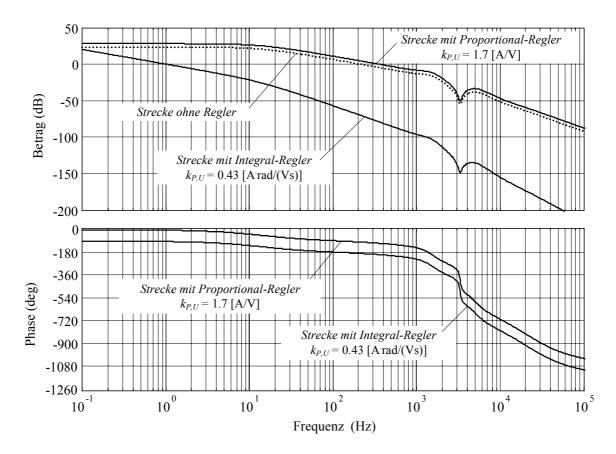

| $k_{P,I}$    | Verstärkung des Proportionalanteils des DC-Stromreglers                              |

| $k_{P,U}$    | Verstärkung des Proportionalanteils des Ausgangsspannungsreglers                     |

| $L_0$        | Gesamtinduktivität des DC-Zwischenkreises                                            |

| $L_{0+}$     | in der positiven Zwischenkreisschiene liegende Induktivität des DC-Zwischenkreises   |

| $L_{0}$ -    | in der negativen Zwischenkreisschiene liegende Induktivität des DC-Zwischenkreises   |

| $L_1$        | Eingangsfilterinduktivität der Filterstufe 1                                         |

| $L_{1c}$     | Kopplungsinduktivität der Filterstufe 1                                              |

| $L_{1d}$     | Induktivität im Dämpfungspfad der Filterstufe 1                                      |

| $L_2$        | Eingangsfilterinduktivität der Filterstufe 1                                         |

| $L_N$        | Netzinduktivität                                                                     |

| M            | Modulationsindex (Aussteuergrad) des eingangsseitigen Tiefsetzstellers               |

| n            | Dämpfungsgrad einer Filterstufe                                                      |

| $n_L$        | Induktivitätsverhältnis der magnetisch gekoppelten Induktivitäten $L_I$ und $L_{Ic}$ |

| $P_{\theta}$ | Ausgangsleistung                                                                     |

| $P_N$        | dem Netz entnommene Leistung                                                         |

| $R_{\theta}$ | Ausgangswiderstand                                                                   |

| $R_{1d}$     | Dämpfungswiderstand der Filterstufe 1                                                |

| $R_{2d}$     | Dämpfungswiderstand der Filterstufe 2                                                |

| $r_{CE}$     | Vorwärtswiderstand eines Leistungstransistors                                        |

| $r_D$        | Vorwärtswiderstand einer Leistungsdiode                                              |

| $R_{DS,on}$  | Vorwärtswiderstand eines Leistungs-MOSFETs                                           |

| $R_{th}$     | thermischer Übergangswiderstand                                                      |

| $S_B$        | Leistungstransistor des ausgangsseitigen Hochsetzstellers                            |

| $S_i$        | Leistungstransistor des eingangsseitigen Tiefsetzstellers                            |

| <b>C</b> .   | Schaltzustandsfunktion des eingangsseitigen Tiefsetzstellers                         |

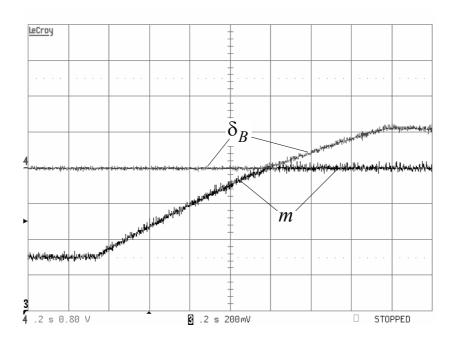

Zeit t  $T_a$ Umgebungstemperatur  $t_d$ Überlappungszeit zwischen zwei Schaltzuständen Kühlkörpertemperatur  $T_{hs}$  $T_i$ Sperrschichttemperatur lokale Zeit, auf eine Pulsperiode bezogene Zeit  $t_{u}$  $T_P$ Pulsperiode  $THD_i$ Total Hormonic Distortion der Netzphasenströme Spannung an der Freilaufdiode и Ausgangsspannung  $u_0$ Filterkondensatorspannung der Filterstufe 1  $u_{C1.i}$  $U_{CE0}$ Vorwärtsspannung eines Leistungstransistors  $U_F$ Vorwärtsspannung einer Leistungsdiode Netzphasenspannungen, allg.  $u_N$ Netzphasenspannung  $u_{N.i}$ verkettete Netzaussenleiterspannungen, allg.  $u_{N.l-l}$ verkettete Netzaussenleiterspannung  $u_{N,l-l,ij}$ für Schaltverlsutberechnung relevante, geschaltete Spannung  $u_{Sw}$ Schaltverlustenergie W  $Z_{in}$ Eingangsimpedanz  $Z_{out}$ Ausgangsimpedanz  $\delta_{\scriptscriptstyle R}$ relative Einschaltdauer des Hochsetzstellers Arbeitspunkt der relativen Einschaltdauer des Hochsetzstellers  $\Delta_B$  $\delta_i$ relative Einschaltdauer des Leistungstransistors  $S_i$  des eingangsseitigen Tiefsetzstellers  $\delta_i$ relative Einschaltdauer des Schaltzustandes j  $\delta_{FL}$ relative Freilaufdeauer des eingangsseitigen Tiefsetzstellers Anteil der relativen Einschaltduaern  $\delta_i$  für aktive Dämpfung  $\Delta \delta_{i,damp}$ λ Leistungsfaktor Wirkungsgrad η Zeitkonstante τ Phasenreserve eines Reglers  $\varphi_M$

Phasenwinkel der Netzgrössen

Netzkreisfrequenz

$\varphi_N$

$\omega$

#### **Indizes**

(1) Grundschwingungswert

avg "average", Mittelwert

BoBu Kombination eines eingangsseitigen Boost- mit einem ausgangsseitigen Buck-Konverter

BuBo Kombination eines eingangsseitigen Buck- mit einem ausgangsseitigen Boost-Konverter

calc auf DSP-Berechnung bezogen

CM Common Mode – Anteil

damp Anteil für aktive Dämpfung

DM Differential Mode - Anteil

$D \rightarrow S$  auf einen Schaltvorgang vom Freilaufzustand zu einem aktiven Schaltzustand bezogen

eq auf das einphasige Ersatzschaltbild bezogen

fwd "forward recovery", auf Vorwärtserholverhalten bezogen

*i* fortlaufende Variable der Netzzuleitungen, i = R, S, T

ij fortlaufende Variable der Netzzuleitungen, ij = RS,ST,TR

*k* k-ter Abtastwert

*lim* Index für einen limitierten Wert

max zulässiger Maximalwert

N auf den Nennpunkt beuogen

off auf das Ausschalten eines Leistungstransistors bezogenon auf das Einschalten eines Leistungstransistors bezogen

p parallel

*peak* detektierter, maximal auftretender Wert

pp ,,peak to peak", Spitze-Spitze-Wert

pred mittels Prädiktion vorausgesagter Wert

*PWM* auf Pulsmusterausgabe bezogen

rev ,reverse recovery", auf Rückwärtserholverhalten bezogen

rms ,,root mean square", Effektivwert

s seriell

sw ,,switched", geschalten

$S \rightarrow S$  auf einen Schaltvorgang zwischen zwei aktiven Schaltzuständen bezogen

$S \rightarrow D$  auf einen Schaltvorgang von einem aktiven Schaltzustand zum Freilaufzustand bezogen

sample abgetasteter Wert skal umskalierter Wert

#### Sonstige Bezeichnungen

$x^*$  Sollwert einer Regelgrösse x

$\underline{x}$  komplexe Grösse in der Raumzeigerebene

$\hat{x}$  Spitzenwert einer Grösse x

#### Abkürzungen

AC "Alternating Current", Wechselstrom, Wechselgrösse

bzw. beziehungsweise

CISPR "Comité International Speciál des Perturbations Radioélectriques", Internationales

Kommitee für Funkentstörung

CM "Common Mode", Gleichtakt

DC "Direct Current", Gleichstrom, Gleichgrösse

d.h. das heisst

DM "Differential Mode", Gegentakt

DSP Digitaler Signalprozessor

ggf. gegebenenfalls

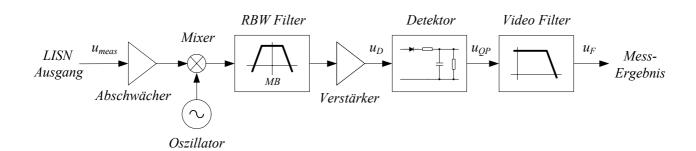

IF "Intermediate Frequency", Zwischenfrequenz

IGBT "Insulated Gate Bipolar Transistor"

LC aus Induktivität und Kondensator bestehend

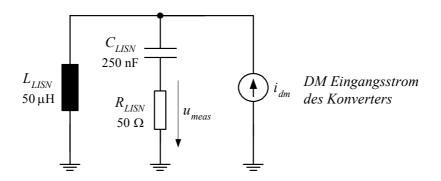

LISN "Line Impedance Stabilization Network", Netznachbildung

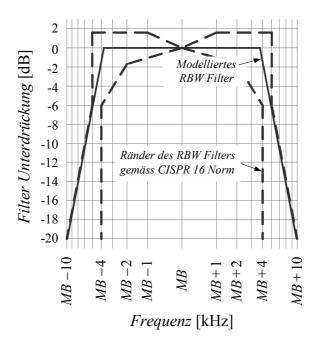

MB "Middle Band", Mittenfrequenz

MOSFET "Metal Oxide Semiconductor Field Effect Transistor"

PWM Pulsweitenmodulation

QP "Quasi Peak", Quasi-Spitzenwert RBW "Resolution Bandwidth", Bandpass

THD "Total Harmonic Distortion", Oberschwingungsgehalt

z.B. zum Beispiel

### Kapitel 1 Einführung

Zur Stromversorgung von DC – Lasten (z.B. für Telekom-Power Supply Units, Batterie-Ladegeräte, DC Strom-/Spannungs-Zwischenkreise zur Speisung von Wechselrichterschaltungen, etc.) aus dem dreiphasigen Netz existieren prinzipiell zahlreiche Systeme. Zur Bewertung und Auswahl eines Systems für eine bestimmte Applikation werden üblicherweise Kriterien wie Wirkungsgrad, Leistungsdichte, Eingangsstromqualität, Netzrückwirkung, Realisierungsaufwand, Komplexität der Steuerung, erreichbare Regeldynamik sowie Robustheit bezüglich netz- und lastseitiger Störungen herangezogen. Diese sich teilweise widersprechenden Forderungen werden dann je nach Anwendungsgebiet unterschiedlich gewichtet, was letztendlich zur Auswahl einer Topologie führt. Eine Klassifizierung der wichtigsten Systeme ist in [1] gegeben.

Im einfachsten Fall werden für die Realisierung der dreiphasigen Gleichrichtung passive Systeme eingesetzt.

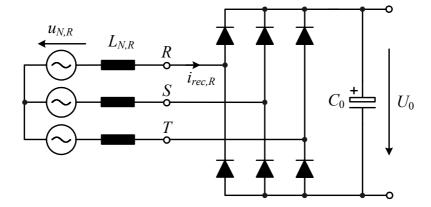

Abbildung 1.1: Passive Dioden-Gleichrichter-Schaltung ohne zusätzliche induktive Glättung am Ein- und Ausgang

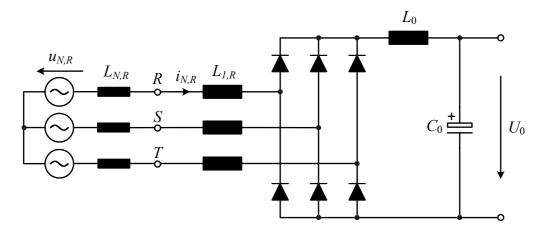

Abbildung 1.2: Passive Dioden-Gleichrichter-Schaltung mit zusätzlicher ausgangsseitiger Glättung durch  $L_0$ .

Diese bestehen wie in Abbildung 1.1 gezeigt im Grunde aus sechs unidirektionalen, nicht abschaltbaren Ventilen (6-Puls-Dioden-Gleichrichter) und zumindest den inneren Netzinduktivitäten und einem Ausgangskondensator. Ein wesentlicher Nachteil dieser Schaltung ist der diskontinuierliche, zwei Nachladeimpulse pro Halbperiode aufweisende Verlauf der Netzströme. Dem kann durch Einfügen einer DC-seitiger Induktivität (siehe Abbildung 1.2) teilweise entgegengewirkt werden, der Leistungsfaktor beträgt jedoch bestenfalls  $\lambda = 96.5\%$  und der Oberschwingungsgehalt  $THD_i = 30.7\%$  [2], was für zahlreiche Anwendungen immer noch inakzeptabel ist. Zusätzlich lässt sich auch die Ausgangsspannung nicht regeln, sie ist im Mittel fix durch

$$U_{D6,avg} = \frac{3 \cdot \sqrt{3} \cdot \hat{U}_N}{\pi}. \tag{1.1}$$

gegeben und hat eine Welligkeit mit sechsfacher Netzfrequenz.

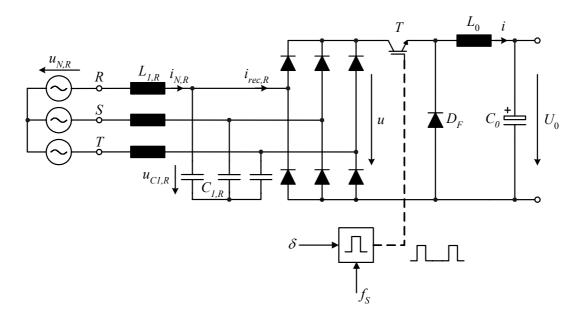

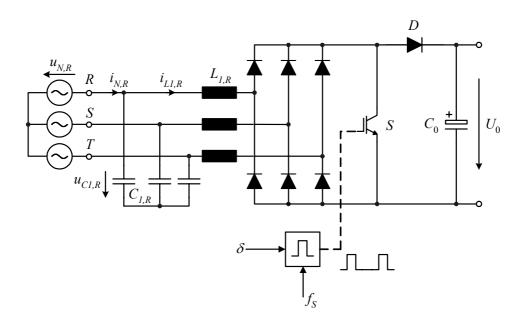

Daher werden vorzugsweise aktive Systems eingesetzt, d.h. Gleichrichterschaltungen, die zumindest einen hochfrequent getakteten Leistungsschalter aufweisen. Dieser kann im einfachsten Fall einer Diodenbrücke in Form einer Tiefsetzstelleroder auch Hochsetzstellerstruktur nachgeschaltet sein (siehe Abbildung 1.3 und Abbildung 1.4). Der Vorteil ist nun, dass die Filterkomponenten nicht bezüglich der sechsfachen Netzfrequenz, sondern der Schaltfrequenz ausgelegt werden und daher wesentlich kompakter ausgeführt werden können. Um den Oberschwingungsgehalt zu reduzieren, muss bei beiden Strukturen eingangsseitig ein LC-Filter vorgesehen werden. Beide Strukturen müssen jedoch im diskontinuierlichen Betrieb arbeiten, d.h. bei der Tiefsetzstellerstruktur sind die Eingangsspannungen an den Filterkondensatoren diskontinuierlich (Discontinuous Capacitor Voltage Mode) und bei der Hochsetzstellerstruktur sind die Eingangsströme in den Filterinduktivitäten diskontinuierlich (Discontinuous Conduction Mode). Damit der lokale Mittelwert der Filterkondensatorspannungen bei der Tiefsetzstellerstruktur den Netzspannungen entspricht, müssen deren Spitzenwerte zumindest die doppelte Netzspannungsamplitude aufweisen. Analog müssen die Ströme in den Filterinduktivitäten der Hochsetzstellerstruktur zumindest doppelte Grundschwingungsstromamplitude besitzen. Die Strukturen sind daher durch sehr hohe Strom- bzw. Spannungsbelastung der Halbleiter gekennzeichnet und sind für Anwendungen höherer Leistung nicht interessant.

Abbildung 1.3: Diodenbrücke mit nachgeschaltetem Tiefsetzsteller und wechselspannungsseitiger Anordnung der Filterkapazitäten

Abbildung 1.4: Diodenbrücke mit nachgeschaltetem Hochsetzsteller und wechselspannungsseitiger Anordnung der Filterinduktivitäten

Abhilfe kann nur geschaffen werden, wenn die Stromaufnahme der drei Phasen getrennt und unabhängig von der Netzspannungssituation geregelt werden kann. Die gängigsten Realisierungen sind in Abbildung 1.5 und Abbildung 1.6 wieder für eine Tief- und eine Hochsetzsetzstellerstruktur gezeigt. Dabei ist für jede Phase eine Gegenserienschaltung von zwei Leistungstransistoren mit in Serie geschalteter Sperrdiode bzw. mit antiparalleler Freilaufdiode vorzusehen. Dadurch kann bei der Tiefsetzstellerstruktur aus Abbildung 1.5 der ausgangsseitig eingeprägte Strom mit entsprechenden Schaltbefehlen beliebig auf die drei Eingangsphasen aufgeteilt werden. Mittels der Filterelemente am Eingang kann dann aus dem pulsförmigen Stromverlauf der grundfrequente Anteil herausgefiltert werden. An den Filterkondensatoren treten hier die Eingangsspannungen plus ein schaltfrequenter Rippel auf, der im Gegensatz zum *Discontinuous Capacitor Voltage Mode* geringe Amplitude aufweist. Daher müssen die Bauelemente daher nicht auf doppelte Spannungsbelastung ausgelegt werden.

Abbildung 1.5: Unidirektionaler Dreiphasen-Sechsschalter-Tiefsetzsteller mit Ein- und Ausgangsfilter

Bei dem Hochsetzsteller aus Abbildung 1.6 wird die ausgangsseitig eingeprägte Spannung durch die Schalthandlungen an die Eingänge geschaltet, die Eingangsströme werden an den Filterinduktivitäten durch die Differenz zwischen der gleichrichterseitigen Spannung und der Netzspannung eingeprägt und haben im Gegensatz zum *Discontinuous Conduction Mode* kontinuierlichen, sinusförmigen Verlauf [3]. Unter der Randbedingung, dass die Summe der drei Eingangsströme null ergeben muss, können sie durch entsprechende Taktung der Leistungsschalter der Brückenzweige getrennt voneinander beeinflusst werden. Daher ermöglichen beide Strukturen eine sinusförmige Stromaufnahme und regelbare Ausgangsspannung bei geringer Belastung der aktiven und passiven Bauteile. Allerdings steigt die Anzahl der benötigten Leistungsschalter.

Abbildung 1.6: Bidirektionaler Dreiphasen-Sechsschalter-Hochsetzsteller mit Ein- und Ausgangsfilter

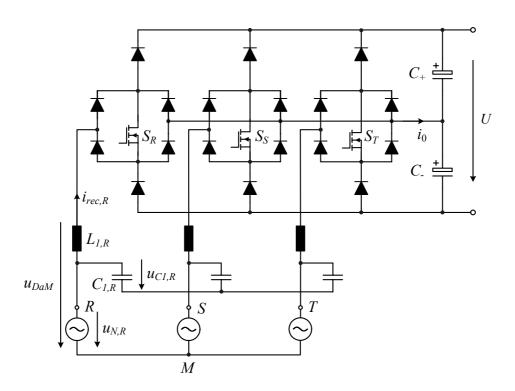

Eine bewährte Struktur, mittels derer die Anzahl der Leistungsschalter auf drei reduziert werden kann, ist der in Abbildung 1.7 gezeigte, auf der Hochsetzstellerstruktur basierende *Vienna Rectifier* [4] . Durch geschickte Anordnung der Leis-

tungsschalter ist in jedem Phasenzweig ein bidirektionaler Schalter realisiert, wodurch die Möglichkeit zur sinusförmigen Stromaufnahme weiterhin bestehen bleibt. Der Zwischenkreismittelpunkt stellt sicher, dass alle Leistungshalbleiter sperrspannungsmässig mit nur halber Zwischenkreisspannung belastet werden, wodurch bei Betrieb am 400V-Netz und bei 800V Zwischenkreisspannung 600V-Elemente (vorzugsweise MOSFETs) zur Realisierung der Schalter eingesetzt werden können. Bei heutigem Stand der Technik ist diese Topologie bezüglich Wirkungsgrad und Leistungsdichte sämtlichen anderen Hochsetzsteller-Schaltungstopologien überlegen [5].

Abbildung 1.7: Unidirektionaler Dreiphasen-Dreischalter-Dreipunkt-Hochsetzsteller (*Vienna Rectifier*) mit Ein- und Ausgangsfilter

Für den Fall, dass ausgangsseitig jedoch eine unterhalb der verketteten Netzspannung liegende Spannung gefordert wird, muss für die Schaltung nach Abbildung 1.7 zusätzlich ein DC-DC-Dreipunkt-Tiefsetzsteller vorgesehen werden. Bei dieser Anordnung wird also die Eingangsspannung für die Leistungsfaktorerhöhung zu-

nächst hochgesetzt und dann wieder auf das gewünschte Spannungsniveau tiefgesetzt.

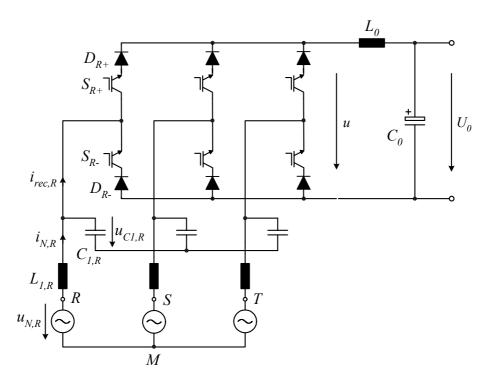

Daher stellt sich die Frage, ob nicht auf Basis der oben erwähnten Tiefsetzstellerstrukturen (Abbildung 1.3 und Abbildung 1.5) ebenfalls eine Dreischalter-Topologie mit Tiefsetzstellereigenschaft gefunden werden kann. In Abbildung 1.8 ist diese Topologie, welche das Kernstück dieser Arbeit bildet, gezeigt [6],[7].

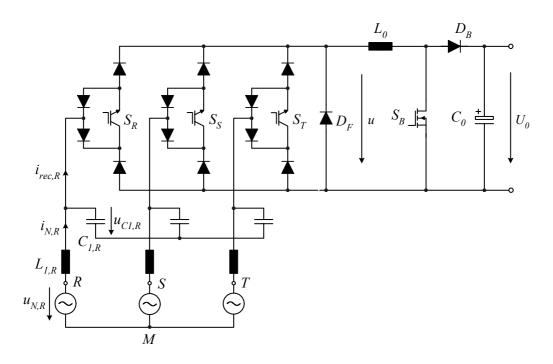

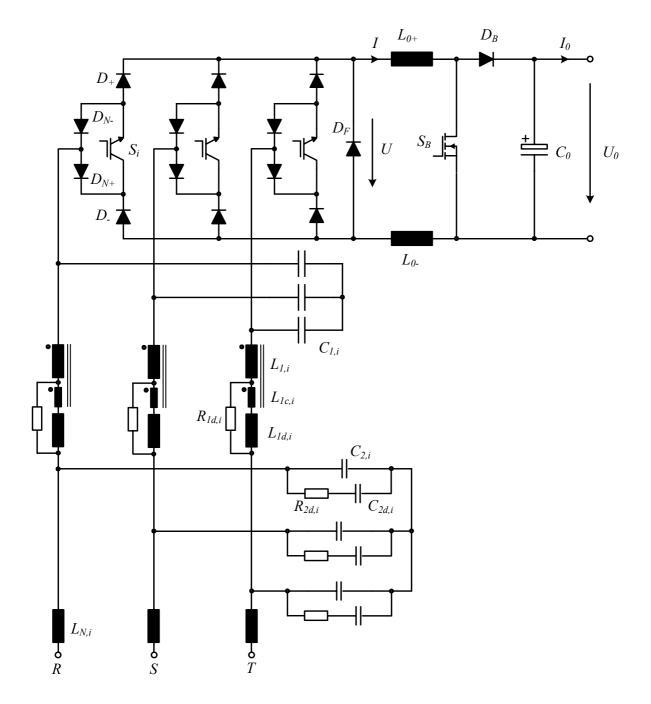

Abbildung 1.8: Unidirektionaler Dreiphasen-Dreischalter-Tiefsetzsteller mit Ein- und Ausgangsfilter und expliziter Freilaufdiode

Durch Betätigen der Schalter von zwei Phasen kann die verkettete Spannung zwischen diesen Phasen in den Zwischenkreis geschaltet werden und der DC-seitig durch  $L_0$  eingeprägte Strom über diese beiden Phasen geführt werden. Wenn nur ein Schalter geschlossen ist oder alle Schalter geöffnet sind, so sind Eingangs- und Ausgangsteil voneinander getrennt und das System befindet sich im Freilauf und der Strom in der Induktivität  $L_0$  fliesst über die explizit vorgesehene Freilaufdiode  $D_F$ . Wenn alle Schalter geschlossen sind, entspricht dies dem Zustand einer einfachen

Diodenbrücke. Damit lassen sich im Mittel sinusförmige Eingangsströme der drei Phasen sowie eine gewünschte Ausgangsspannung gezielt einstellen, wobei der Mittelwert der an den Zwischenkreis geschalteten Spannung auf den  $\sqrt{3}/2$ -fachen Spitzenwert der verketteten Eingangsspannung limitiert ist.

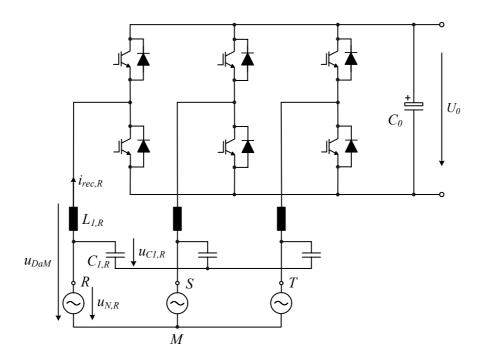

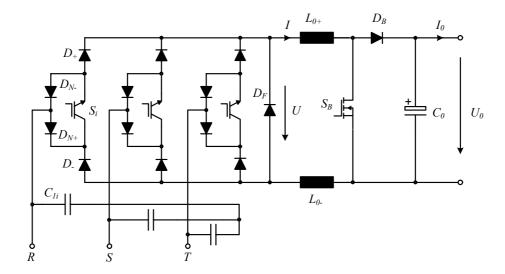

Um nun für geringe Eingangsspannungen, wie z.B. bei Betrieb am 200V-Netz oder auch bei Ausfall einer Phase, eine gewünschte, hohe Ausgangsspannung zu erreichen oder auch um einen weiten Ausgangsspannungsbereich sicherzustellen, wird bei der in dieser Arbeit betrachteten Topologie ausgangsseitig noch wie in Abbildung 1.9 gezeigt ein DC-DC-Boost-Konverter integriert [9],[10],[11]. Der Vergleich mit Abbildung 1.8 zeigt, dass die Erweiterung der Topologie daher lediglich aus der Einfügung eines Schalters und einer Diode zwischen DC-Induktivität und Ausgangskondensator besteht.

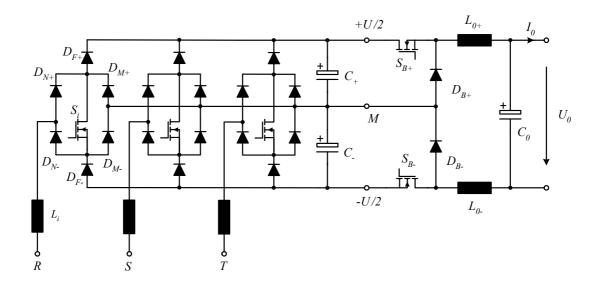

Abbildung 1.9: Dreiphasen-Dreischalter-Tiefsetzsteller mit integriertem Boost-Konverter zur Sicherstellung eines weiten Eingangs- bzw. Ausgangsspannungsbereichs.

Prinzipielle Vorteile dieser Topologie gegenüber auf Hochsetzsteller-Funktion basierenden Schaltungen sind:

• der Wegfall der Hochlaufeinrichtung, d.h. der Ausgangskondensator kann mittels Regelung des Gleichrichters direkt auf den gewünschten Wert hochgeladen werden. Allerdings muss eine ausreichende Dämpfung des Eingangsfilters gewährleistet werden, da sonst durch die Resonanz des LC Filters bei Einschalten des Konverters der Spannungswert an den Filterkondensatoren im schlimmsten Fall (reines LC-Filter) die doppelte Netzspannungsamplitude erreichen und zur Zerstörung der Halbleiter führen kann. Wenn keine genügende Dämpfung garantiert werden kann, müssen in jedem Fall wiederum strombegrenzende Elemente eingefügt werden.

- niedrigere Ausgangsspannung im Vergleich zum Vienna Rectifier [12].

- geringe Anzahl an aktiven und passiven Bauelementen

- Möglichkeit zur direkten Strombegrenzung im Kurzschlussfall [13]

- grosse Robustheit gegenüber Störfällen in der Modulation bzw. Regelung [12],[13]: Es existieren prinzipiell keine verbotenen Schaltzustände und die Zwischenkreisspannung ist stets auf den in (1.1) angegebenen Wert der Eingangsspannung limitiert. Bei dauerhaftem Einschalten aller drei Eingangs-Leistungstransistoren entspricht der Eingangskreis wie erwähnt einer einfachen Diodenbrücken-Schaltung.

Als Nachteil können einerseits die pulsförmigen Eingangsströme genannt werden, die im Gegensatz zu Hochsetzstellern eines grösseren Filteraufwands zur Erreichung eines sinusförmigen Netzstromverlaufs bedürfen [12]. Zusätzlich sind für den Betrieb am 400V-Netz (±20%) 600V-MOSFET-Transistoren bezüglich Sperrspannungsbelastung nicht mehr ausreichend, daher muss auf 1200V-Technologie für Transistoren (IGBTs) und Dioden zurückgegriffen werden, was auf Grund der höheren Leit- und Schaltverluste Einbussen im Wirkungsgrad zur Folge hat.

Ein detaillierter Vergleich mit einer auf Dreischalter-Hochsetzsteller-Funktion basierenden Topologie mit nachgeschaltetem Tiefsetzsteller (siehe Kapitel 8) zeigt jedoch, dass der Buck+Boost-Konverter insgesamt bezüglich Wirkungsgrad, Leistungsdichte und Realisierungsaufwand überlegen ist.

Für alle nachfolgenden Untersuchungen seien folgende Spezifikationen für den Betrieb des Systems vereinbart:

- konstante Ausgangsspannung  $U_0 = 400 \text{V}$

- Nenn-Ausgangsleistung  $P_0 = 5 \text{kW}$

- weiter Eingangsspannungsbereich  $U_{N,l\text{-}l,rms} = 208\text{V}...480\text{V}$  bzw.  $U_{N,rms} = 120\text{V}...280\text{V}$

- sinusförmige Stromaufnahme mit Leistungsfaktor  $\lambda \sim 1$ , auch für den Fall von Netzspannungsunsymmetrien wie z.B. Ausfall einer Netzphase, Kurzschluss zwischen zwei Phasen oder Erdschluss einer Phase

- maximaler Einbruch der Ausgangsspannung von  $\Delta U_0 = \pm 10\%$  bei Laständerungen und Netzspannungseinbrüchen bzw. –unsymmetrien

- Erfüllung der EMV-Funkstörnormen für Gleichtakt- und Gegentaktstörungen.

# Kapitel 2 Funktionsweise

In diesem Kapitel wird die Grundfunktion des Buck+Boost-Konverters vorgestellt. Dabei wird zunächst auf den Buck-Eingangsteil eingegangen, es werden die Leitzustände des Systems analysiert und mittels der Raumzeigerrechnung, die sich für Hochsetzstellerstrukturen [14],[15] und auch 6-Schalter-Tiefsetzstellerstrukturen [16],[17],[18],[19] bereits bewährt hat, gezeigt, wie mit entsprechenden Einschaltdauern der Transistoren sinusförmige Eingangsströme in Phase mit den Eingangsspannungen erzeugt werden können. Danach wird kurz auf die Funktion des Boost-Ausgangsteiles eingegangen und abschliessend wird ausgehend von den Spezifikationen aus Kapitel 1 der Betriebsbereich für das Gesamtsystem gezeigt.

# 2.1 Buck-Eingangsteil

## 2.1.1 Grundsätzliche Betrachtungen

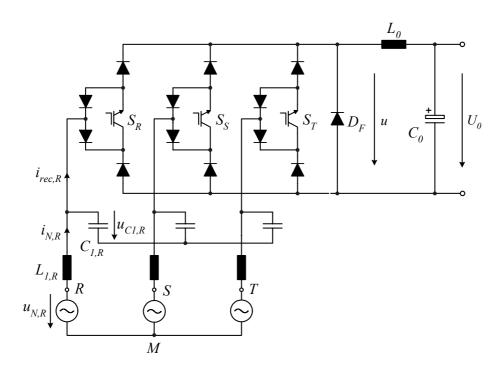

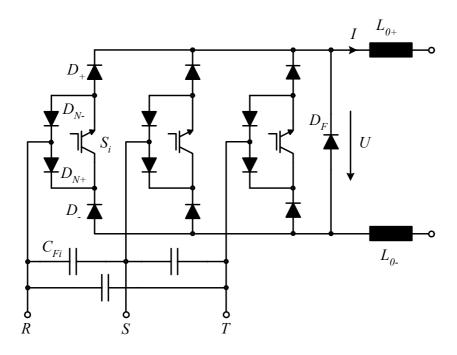

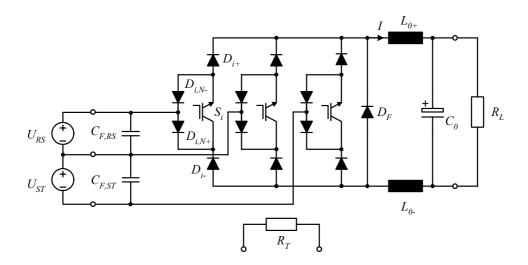

Der Buck-Eingangsteil des Buck+Boost-Konverters besteht wie in Abbildung 2.1 dargestellt im Wesentlichen aus drei Schaltern  $S_i$ , die hier vorzugsweise durch IGBTs realisiert werden, zwölf eingangsseitigen Dioden  $D_i$  und einer expliziten Freilaufdiode  $D_F$ . Da jeweils vier Dioden einer Phase mit einem IGBT in der Praxis in einem Leistungsmodul integriert sind (siehe Kapitel 3, werden diese Dioden in

Zukunft als Moduldioden bezeichnet. Auf die Freilaufdiode könnte prinzipiell verzichtet werden, sie erleichtert die Steuerung jedoch sehr, da für die Einstellung des Freilaufzustandes nicht unbedingt ein Schalter geschlossen bleiben muss.

Abbildung 2.1: Buck-Eingangsteil der Buck+Boost-Topologie

Für den Betrieb ist ausserdem am Eingang pro Phase je ein spannungseinprägender Filterkondensator  $C_{li}$  vorzusehen, der einen genügend grossen Wert aufweisen muss, damit der schaltfrequente Spannungsrippel am Eingang des Konverters noch eine korrekte Detektion des Eingangsspannungssektors zulässt (siehe Kapitel 4). Die Filterkondensatoren können prinzipiell wie in Abbildung 2.1 zwischen die Phasen in Dreieck geschaltet werden oder auch von den Phasen zu einem Sternpunkt. Durch die Schalthandlungen werden nun Ausschnitte aus den am Eingang des Konverters liegenden Spannungen, die im Mittel dem gewünschten Ausgangsspannungswert entsprechen, an den Zwischenkreis geschaltet. Durch Einschalten von allen drei Schaltern wird die momentan grösste verkettete Eingangsspannung am Zwischenkreis auftreten und wenn die Schalter zweier Phasen geschlossen sind, wird die verkettete Spannung zwischen diesen beiden Phasen an den Zwischenkreis geschaltet. Wenn mindestens zwei Schalter geöffnet sind, ist der Ausgangskreis vom Eingang getrennt und die Freilaufdiode leitet, d.h. es tritt keine Spannung am Zwischen Zwischen Zwischen diesen beiden Phasen and Zwischenkreis geschaltet. Wenn mindestens zwei Schalter geöffnet sind, ist der Ausgangskreis vom Eingang getrennt und die Freilaufdiode leitet, d.h. es tritt keine Spannung am Zwischen

schenkreis auf. Im Mittel wird die Spannung am Ausgang gegenüber den verketteten Eingangsspannungen also verringert.

Analog zu den spannungseinprägenden Eingangskondensatoren muss sich am Ausgang des Buck-Gleichrichters eine stromeinprägende Induktivität  $L_{\theta}$  liegen. Diese ist aus Gründen der Unterdrückung des Gleichtakt-Störpegels (siehe Kapitel 5) zu gleichen Teilen  $L_{\theta^+} = L_{\theta^-}$  im positiven und negativen Pfad ausgeführt. Der in erster Näherung konstante DC-Strom I wird nun durch entsprechende Schaltzustände auf die drei Eingangsphasen verteilt.

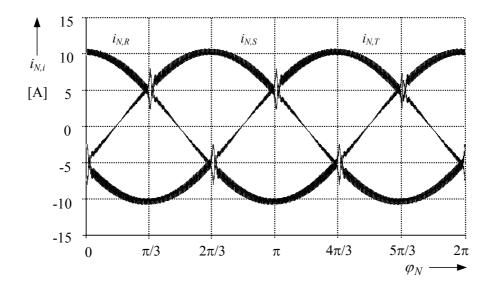

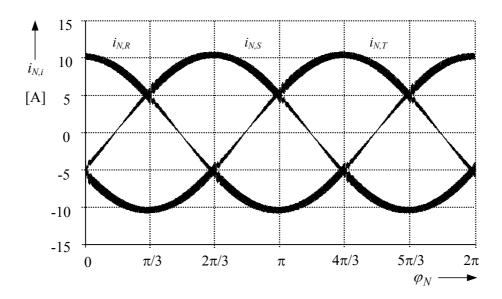

Das Ziel der Modulation ist es, die Einschaltdauern derart einzustellen, dass die Eingangsströme nach Filterung schaltfrequenter Anteile sinusförmigen Verlauf in Phase mit den Eingangsphasenspannungen aufweisen und sich ein ohmsches Verhalten des Konverters

$$u_{N,i} \sim i_{N,i} \tag{2.1}$$

aus Sicht des Netzes ergibt.

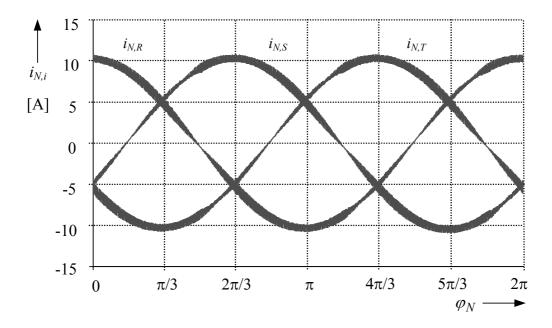

Für die nun folgenden grundsätzlichen Betrachtungen sei angenommen, dass die Phasenspannungen des Netzes rein sinusförmigen Verlauf

$$u_{N,R} = \hat{U}_N \cos(\omega_N t)$$

$$u_{N,S} = \hat{U}_N \cos(\omega_N t - 2\pi/3)$$

$$u_{N,T} = \hat{U}_N \cos(\omega_N t + 2\pi/3)$$

(2.2)

aufweisen

und die Spannungsabfälle an den Filterinduktivitäten des Eingangsfilters (siehe Kapitel 5) und der schaltfrequente Rippel der Filterkondensatorspannungen vernachlässigbar sind, d.h.

$$u_{C1,i} \approx u_{N,i}, \tag{2.3}$$

$$\hat{U}_{C1} \approx \hat{U}_N \tag{2.4}$$

gilt. Die Phasenverschiebung durch das Eingangsfilter wird also hier nicht berücksichtigt, was die Sachverhalte anschaulicher macht und keine Einschränkung der allgemeinen Gültigkeit nach sich zieht.

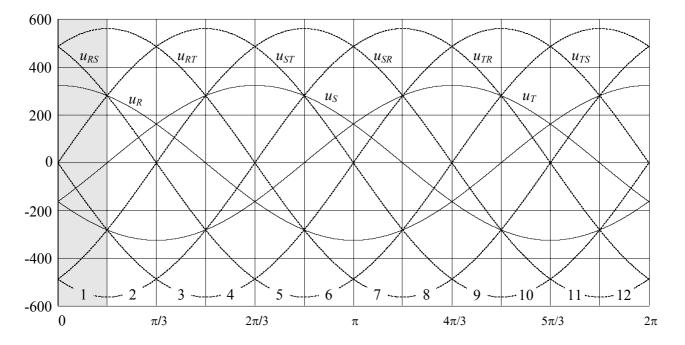

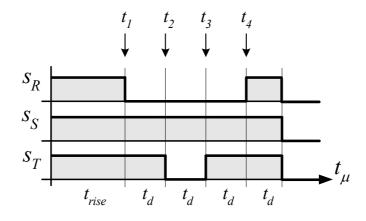

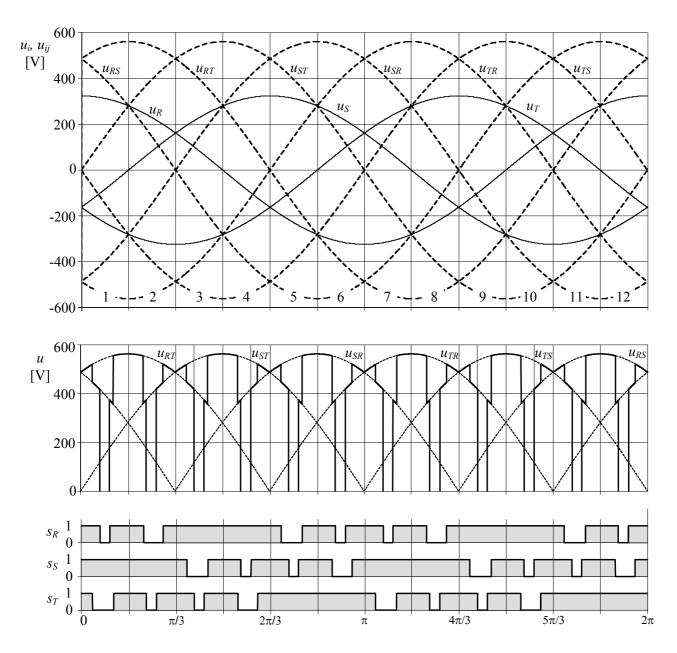

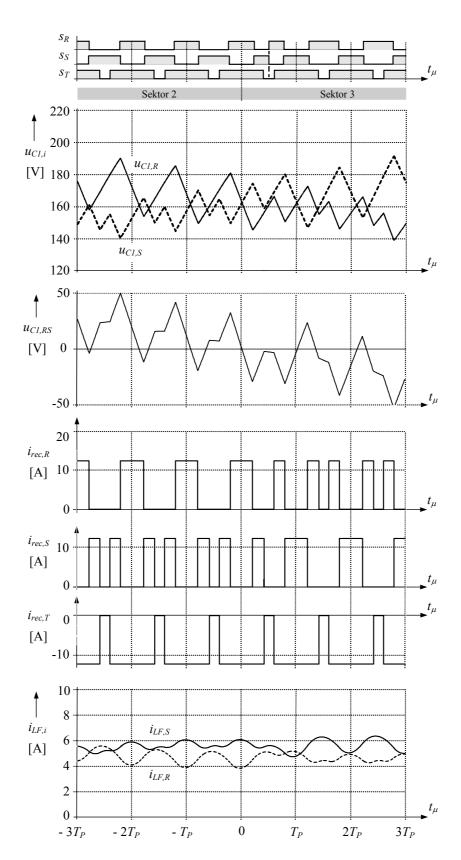

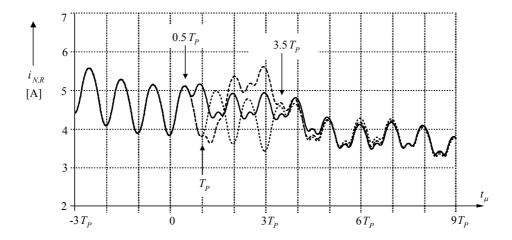

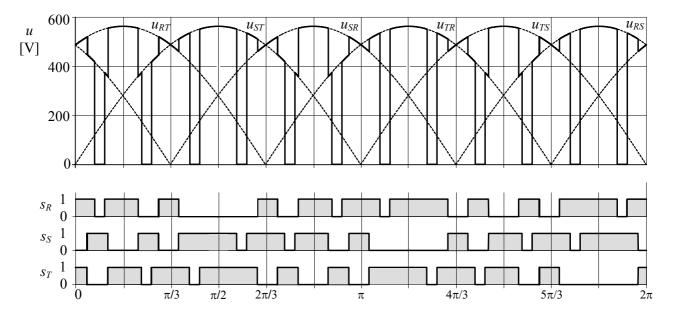

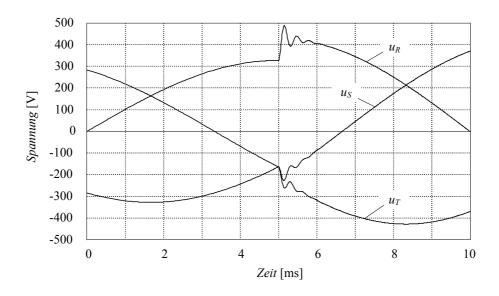

Für die Berechnung der relativen Einschaltdauern ist die momentane Eingangsspannungs-Situation von entscheidender Bedeutung. Abhängig von den Grössenverhältnissen der Phasenspannungen kann eine Netzperiode in 12 Sektoren unterteilt werden

Abbildung 2.2: Verlauf der Netzphasenspannungen und der verketteten Eingangsspannungen innerhalb einer Netzperiode und Unterteilung der Netzspannung in 12 Sektoren. Der grau schraffierte Bereich (Sektor 1) wird zur Analyse der Schaltzustände und für die Berechnung der Einschaltdauern herangezogen.

In Abbildung 2.2 sind die Phasenspannungen mit den entsprechenden  $\pi/6$ -breiten Sektoren dargestellt. Diese Unterteilung wird allen Berechnungen der Einschaltdauern und den in Kapitel 4 beschriebenen Modulationsmethoden zu Grunde gelegt.

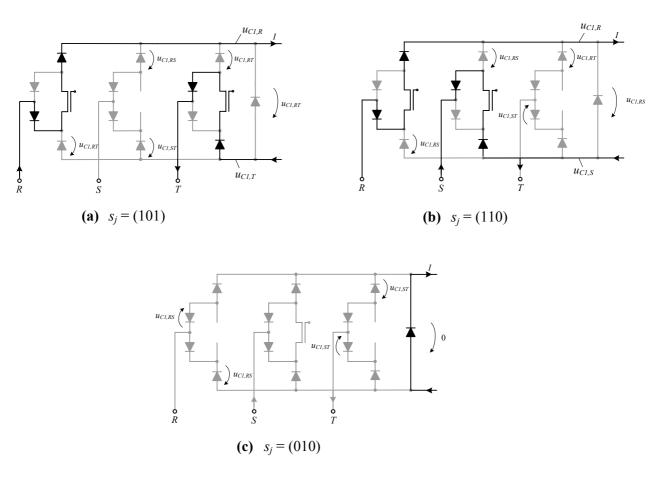

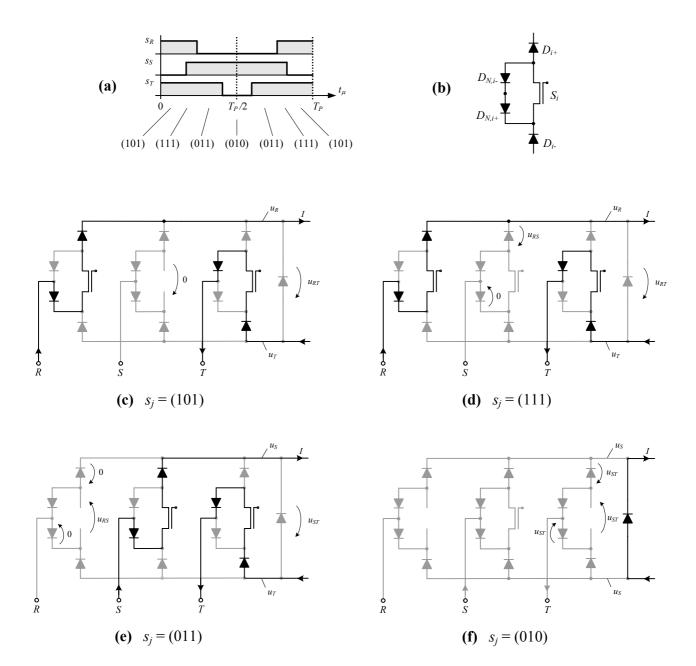

#### 2.1.2 Schaltzustände

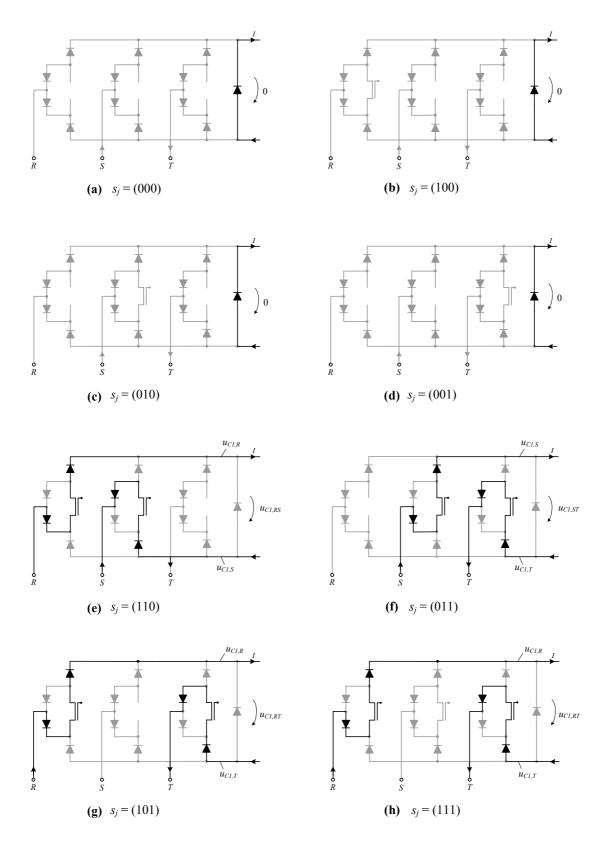

Im Folgenden wird ausgehend von den möglichen Schaltzuständen des Gleichrichters die Bildung des Sollraumzeigers des Eingangsstromes analysiert, woraus schliesslich die relativen Einschaltdauern abgeleitet werden. Zur Veranschaulichung werden die Zusammenhänge für eine Eingangsspannungs-Siuation  $u_{CI,R} > 0 > u_{CI,S} > u_{CI,T}$  (Sektor 1, siehe Abbildung 2.2) erläutert. Auf Grund der Symmetrie der Eingangsspannungen und der identen Struktur der drei Eingangsphasen des Konverters herrschen analoge Verhältnisse für die anderen Sektoren. Der Übersichtlichkeit halber wird also hier nur auf den Sektor 1 eingegangen und die Ergebnisse für die anderen Sektoren werden lediglich angegeben (siehe TABELLE 2.1).

Prinzipiell existieren aufgrund der drei Leistungsschalter  $2^3 = 8$  mögliche Schaltzustände, die eine unterschiedliche Aufteilung der Ströme auf die Eingangsphasen zur Folge haben. Zunächst sei nur der Sektor 1 betrachtet und angenommen, der DC-Strom I wäre von der Induktivität konstant eingeprägt.

Die Schalterstellung<sup>1</sup>  $s_j = (000)$ , d.h. alle Transistoren sind im ausgeschalteten Zustand, bewirkt, dass sich das System im Freilaufzustand befindet und sämtliche Eingangsströme null sind (siehe Abbildung 2.3(a)), womit für den Stromraumzeiger

$$\underline{i}_{rec,(000)} = 0$$

. (2.6)

gilt. Ohne die Diode  $D_F$  wäre dieser Zustand nicht zulässig, da dann der DC-Strom schlagartig zu null werden müsste, was eine entsprechend hohe Überspannung zur Folge hätte.

Die Schalterstellungen  $s_i$  der drei Leistungstransistoren  $S_i$  mit i = R, S, T werden in kompakter Form mit  $s_j = (s_R s_S s_T)$  indiziert, wobei  $s_i = 0$  bedeutet, dass der entsprechende Schalter ausgeschaltet ist; entsprechend befindet sich der Schalter  $S_i$  für  $S_i = 1$  in leitendem Zustand.

Funktionsweise Funktionsweise

Auch die Schalterstellungen  $s_j = (100) = (010) = (001)$  bewirken einen Freilauf über die Diode  $D_F$ , da der Pfad über die Freilaufdiode geringere Vorwärtsspannung als der entsprechende Pfad mit einem Transistor und zwei Moduldioden aufweist (siehe Abbildung 2.3(b)-(d))

$$\underline{i}_{rec,(100)} = \underline{i}_{rec,(010)} = \underline{i}_{rec,(001)} = 0.$$

(2.7)

Wenn nun die Schalter der Phasen R und S geschlossen werden  $s_j = (110)$ , wird sich aufgrund  $u_{CI,R} > u_{CI,S}$  wie in Abbildung 2.3(e) gezeigt ein Stromfluss von der Phase R über den Ausgangskreis zur Phase S einstellen. Mit der Definition des Raumzeigers

$$\underline{i}_{rec} = \frac{2}{3} (i_{rec,R} + e^{j2\pi/3} \cdot i_{rec,S} + e^{j4\pi/3} \cdot i_{rec,T})$$

(2.8)

erhält man für diesen Schalterzustand unter Berücksichtigung von  $i_{rec,R} = I$  und  $i_{rec,S} = -I$

$$\underline{i}_{rec,(110)} = I \cdot \frac{2}{\sqrt{3}} e^{-j\pi/6} \,. \tag{2.9}$$

Mit diesem Schaltzustand wird die verkettete Spannung  $u_{CI,RS}$  in den Zwischenkreis geschaltet.

Analog erhält man für  $s_j = (011)$ , d.h. für leitenden Zustand der Schalter der Phasen S und T (siehe Abbildung 2.3(f)) einen Stromraumzeiger

$$\underline{i}_{rec,(011)} = I \cdot \frac{2}{\sqrt{3}} j, \qquad (2.10)$$

und aufgrund von  $u_{CI,S} > u_{CI,T}$  entsteht einen Stromfluss von Phase S zur Phase T und eine Zwischenkreisspannung  $u = u_{CI,ST}$ .

Abbildung 2.3: Zusammenstellung sämtlicher möglicher Schalterstellungen und der daraus resultierenden Stromflüsse am Eingang bzw. der an den Ausgang geschalteten verketteten Eingangsspannungen.

Die grösste verkettete Spannung im Zwischenkreis, nämlich  $u_{CI,RT}$ , wird in diesem Sektor durch die Schaltzustände  $s_j = (101) = (111)$  erzeugt. Dass beide Zustände (siehe Abbildung 2.3(g)-(h)) in diesem Sektor äquivalent sind, lässt sich leicht zeigen. Aufgrund von  $u_{CI,R} > u_{CI,S}$  ist die Moduldiode  $D_{S,+}$  in Sperrrichtung gepolt und wegen  $u_{CI,S} > u_{CI,T}$  sperrt die Moduldiode  $D_{S,-}$ . Daher ist selbst bei geschlossenem Schalter  $S_S$  in der Phase S kein Stromfluss in positiver oder negativer Richtung möglich. Der Stromraumzeiger berechnet sich zu

$$\underline{i}_{rec,(101)} = \underline{i}_{rec,(111)} = I \cdot \frac{2}{\sqrt{3}} e^{j\pi/6}.$$

(2.11)

Damit sind alle acht möglichen Schaltzustände analysiert. Bei vier Schaltzuständen  $(s_j = (000), (100), (010), (001))$  ist der Eingang des Konverters vom Ausgang getrennt und das System befindet sich im Freilaufzustand. Für die restlichen vier Schaltzustände  $(s_j = (110), (011), (101), (111))$  stellt sich ein Stromfluss zwischen AC-Seite und DC-Seite ein, es wird Leistung an die DC-Seite geliefert. Daher werden diese vier Zustände im Folgenden als aktive Zustände bezeichnet.

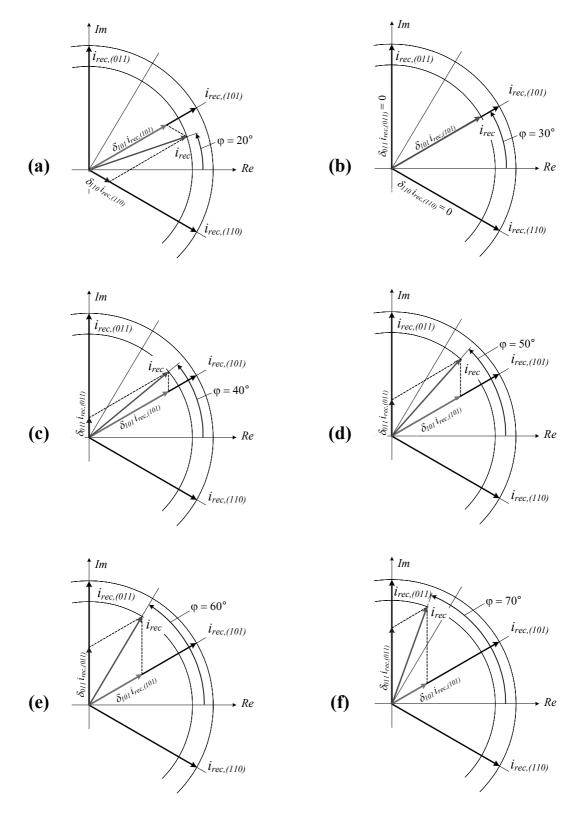

### 2.1.3 Bildung des Soll-Stromraumzeigers

Der momentane Raumzeiger der Filterkondensatorspannungen  $\underline{u}_{CI}$  wird, wie vorhin erwähnt, in erster Näherung dem Eingangsspannungsraumzeiger mit dem Phasenwinkel  $\varphi_N = \omega_N \cdot t$  und einer Amplitude gleich der Amplitude  $\hat{U}_N$  der Netzphasenspannungen gleichgesetzt  $\underline{u}_{CI} \approx \underline{u}_N$  (2.3). Nun soll der gewünschte Netzstromraumzeiger  $\underline{i}_N^*$  in Phase mit der Eingangsspannung erzeugt werden. Wenn, wie eingangs erwähnt, die Phasenverschiebung des Eingangsfilters vernachlässigt wird, so ist die Grundschwingungskomponente des Eingangsstromraumzeigers  $\underline{i}_{rec,(1)}^*$  genau gleich dem Netzstromraumzeiger  $\underline{i}_N^*$ . Der momentane Phasenwinkel  $\varphi_{CI}$  und der Betrag, d.h. die Amplitude der Gleichrichtereingangsphasenstromgrundschwingung  $I_{rec,(1)}^*$  bzw. der Netzphasenstrom-Grundschwingung  $I_{N,(I)}^*$  sind also direkt mittels der verfügbaren Raumzeiger einzustellen.

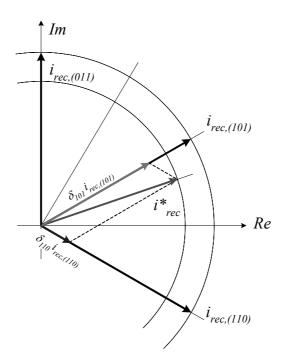

Abbildung 2.4: Darstellung der in Sektor 1 verfügbaren Stromraumzeiger und Bildung des Sollstromraumzeigers  $\underline{i}^*_{rec}$ .

In Abbildung 2.4 sind die in diesem Sektor verfügbaren Stromraumzeiger der aktiven Schaltzustände grafisch dargestellt. Man sieht, dass der gewünschte Soll-Stromraumzeiger durch die beiden benachbarten Raumzeiger  $\underline{i}_{rec,(110)}$  und  $\underline{i}_{rec,(101)} = \underline{i}_{rec,(111)}$  eingestellt werden kann. Prinzipiell könnte auch der dritte Raumzeiger  $\underline{i}_{rec,(011)}$  verwendet werden, allerdings wäre dann nicht mehr der volle Aussteuergrad des Konverters (M = 0...1) möglich. Für geringe Ausgangsspannungen könnte dieses Verfahren eventuell von Interesse sein, da die Schaltverluste reduziert werden können. Aufgrund der in Kapitel 1 festgelegten Spezifikationen ist aber der maximale Aussteuergrad notwendig und es werden in dieser Arbeit daher stets die beiden benachbarten Stromraumzeiger zur Bildung des Soll-Stromraumzeigers herangezogen.

Um den Sollstromraumzeiger nun wie gewünscht zu bilden, müssen die relativen Einschaltdauern  $\delta_{110}$  und  $\delta_{101} = \delta_{111}$  der Raumzeiger  $\underline{i}_{rec,(110)}$  und  $\underline{i}_{rec,(101)} = \underline{i}_{rec,(111)}$  eine entsprechende relative Einschaltdauer innerhalb einer Pulsperiode aufweisen. Wenn ein Modulationsindex M < 1 realisiert werden soll, ist auch eine entsprechende Freilaufdauer  $\delta_{FL}$  zu berücksichtigen.

### 2.1.4 Berechnung der Einschaltdauern

Der Berechnung des Soll-Stromraumzeigers werden folgende Annahmen zu Grunde gelegt:

• Der Buck-Konverter soll ohmsche Grundschwingungscharakteristik aufweisen, d.h. die Grundschwingungsanteile von Eingangsstrom und Eingangsspannung weisen keine Phasendifferenz auf:

$$\underline{i}_{rec,(1)} \sim \underline{u}_{C1,(1)}. \tag{2.12}$$

• Der lokale (auf eine Pulsperiode bezogene) Mittelwert der an den Ausgang des Buck-Gleichrichters geschalteten Spannung soll dem geforderten Wert  $u^*$  entsprechen<sup>2</sup>. Für den betrachteten Sektor 1 bedeutet das:

$$u^* = \delta_{101} \cdot u_{C1\,RT} + \delta_{110} \cdot u_{C1\,RS} \,. \tag{2.13}$$

• Die Summe der relativen Einschaltdauern (inklusive der Freilaufzeit) muss sich zu 1 ergänzen. Für den betrachteten Sektor folgt demnach:

$$\delta_{101} + \delta_{110} + \delta_{FL} = 1. \tag{2.14}$$

Damit können die relativen Einschaltdauern, die zur Realisierung des geforderten Stromraumzeigers notwendig sind, als Funktion der Eingangsspannungen und der gewünschten Ausgangsspannung berechnet werden.

In Phase R fliesst während der relativen Einschaltzeiten  $\delta_{101}$  und  $\delta_{110}$  der DC-Strom I in positiver Richtung, während in Phase S nur während  $\delta_{110}$  und in Phase T nur während  $\delta_{101}$  Strom in negative Richtung auftritt. Für die Gleichrichtereingangsströme gilt daher mit (2.12)

<sup>&</sup>lt;sup>2</sup> Hier sei vorläufig nur der Buck-Konverter betrachtet, d.h. die Zwischenkreisspannung ist gleich der geforderten Ausgangsspannung,  $u_0^* = u^*$ . Wenn die geforderte Ausgangsspannung die maximal mögliche Zwischenkreisspannung übersteigt, kommt der Boost-Konverter zum Einsatz, siehe Kapitel 2.2.

$$i_{rec,R,(1)} = I \cdot (\delta_{101} + \delta_{110})$$

$\sim u_{C1,R}$

$i_{rec,S,(1)} = -I \cdot \delta_{110}$   $\sim u_{C1,S}$  (2.15)

$i_{rec,T,(1)} = -I \cdot \delta_{101}$   $\sim u_{C1,T}$

Unter Verwendung von (2.15) erhält man

$$\delta_{110} = \frac{u_{C1,S}}{u_{C1,T}} \cdot \delta_{101}. \tag{2.16}$$

Durch Einsetzen von (2.16) in (2.13) ergibt sich die mittlere Zwischenkreisspannung

$$u^* = \delta_{101} \cdot \left( u_{C1,R} - u_{C1,T} + \frac{u_{C1,S}}{u_{C1,T}} (u_{C1,R} - u_{C1,S}) \right)$$

(2.17)

und daraus eine Beziehung für die relative Einschaltdauer  $\delta_{101}$

$$\delta_{101} = \frac{u^* \cdot u_{C1,T}}{u_{C1,R} \cdot u_{C1,T} - u_{C1,T}^2 + u_{C1,R} \cdot u_{C1,S} - u_{C1,S}^2}.$$

(2.18)

Mit

$$u_{C1,T} + u_{C1,S} = -u_{C1,R} (2.19)$$

erhält man schliesslich

$$\delta_{101} = -\frac{u^*}{u_{C1,R}^2 + u_{C1,S}^2 + u_{C1,T}^2} \cdot u_{C1,T}$$

$$= -\frac{2}{3} \frac{u^*}{|\underline{u_{C1}}|^2} \cdot u_{C1,T}$$

(2.20)

Analog folgt für die Einschaltdauer  $\delta_{110}$

$$\delta_{110} = -\frac{u^*}{u_{C1,R}^2 + u_{C1,S}^2 + u_{C1,T}^2} \cdot u_{C1,S}$$

$$= -\frac{2}{3} \frac{u^*}{|\underline{u}_{C1}|^2} \cdot u_{C1,S}$$

(2.21)

Mit (2.14), (2.20) und (2.21) ergibt sich die relative Dauer des Freilaufzustandes zu:

$$\delta_{FL} = 1 - \delta_{101} - \delta_{110} =$$

$$= 1 + \frac{2}{3} \frac{u^*}{|\underline{u}_{C1}|^2} \cdot (u_{C1,S} + u_{C1,T})$$

$$= 1 - \frac{2}{3} \frac{u^*}{|\underline{u}_{C1}|^2} \cdot u_{C1,R} .$$

(2.22)

Der Aussteuergrad oder Modulationsgrad M des Konverters ist in den Gleichungen (2.20) - (2.22) implizit enthalten. Mit

$$M = \frac{2}{3} \cdot \frac{u^*}{|\underline{u}_{C1}|} \tag{2.23}$$

lassen sich die Gleichungen (2.20) - (2.22) zu

$$\delta_{101} = -M \cdot \frac{u_{C1,T}}{|\underline{u}_{C1}|}, \tag{2.24}$$

$$\delta_{110} = -M \cdot \frac{u_{C1,S}}{|\underline{u}_{C1}|},\tag{2.25}$$

$$\delta_{FL} = 1 - M \cdot \frac{u_{C1,R}}{\left|\underline{u}_{C1}\right|} \tag{2.26}$$

umformen.

Für symmetrische, rein sinusförmige Netzverhältnisse ist der Betrag des Raumzeigers  $|u_{CI}|$  gleich der Amplitude der Eingangsspannungen  $\hat{U}_{CI}$ , daher lautet die Definition des Modulationsindex dann

$$M = \frac{2}{3} \cdot \frac{u^*}{\hat{U}_N} \tag{2.27}$$

Mit (2.24) - (2.27) lassen sich die relativen Einschaltdauern  $\delta_{101}$  und  $\delta_{110}$  mit (2.2) und (2.3) als

$$\delta_{101} = -M \cdot \cos(\omega_N t + 2\pi/3) \tag{2.28}$$

und

$$\delta_{110} = -M \cdot \cos(\omega_N t - 2\pi/3) \tag{2.29}$$

angeben, besitzen also einen rein sinusförmigen Verlauf.

Für die übrigen Sektoren sind die Einschaltdauern der Transistoren und die Freilaufzeiten analog zu berechnen. Die Ergebnisse sind in TABELLE 2.1 zusammengefasst.

Um aus den relativen Einschaltdauern schlussendlich die Einschaltdauern der einzelnen Transistoren zu berechnen, muss festgelegt werden, wie der redundante aktive Zustand mit der grössten verketteten Eingangsspannung realisiert wird (im ersten Sektor ist dies  $s_j = (101) = (111)$ ) und welcher der Schaltzustände  $s_j = (000) = (100) = (010) = (001)$  als Freilaufzustand eingesetzt wird. Zusätzlich gibt es für die Anordnung der Zustände innerhalb der Pulsperiode mehrere Möglichkeiten. Dies wird in Verbindung mit den Überlegungen zur Modulation in Kapitel 4 geklärt.

TABELLE 2.1

Relative Einschaltdauern der in den einzelnen Sektoren verfügbaren Raumzeiger

| Sektor  | $\delta_{101}$                                              | $\delta_{110}$                                              | $\delta_{011}$                                   | $\delta_{\mathrm{FL}}$                                                       |  |  |

|---------|-------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------|--|--|

| 1 + 12  | $-M \cdot \frac{u_{C1,T}}{\left \underline{u}_{C1}\right }$ | $-M \cdot \frac{u_{C1,S}}{ \underline{u}_{C1} }$            | -                                                | $\delta_{FL} = 1 - M \cdot \frac{u_{C1,R}}{ \underline{u}_{C1} }$            |  |  |

| 2+3     | $M \cdot \frac{u_{C1,R}}{\left \underline{u}_{C1}\right }$  | -                                                           | $M \cdot \frac{u_{C1,S}}{ \underline{u}_{C1} }$  | $\delta_{FL} = 1 + M \cdot \frac{u_{C1,T}}{\left \underline{u}_{C1}\right }$ |  |  |

| 4 + 5   | -                                                           | $-M \cdot \frac{u_{C1,R}}{\left \underline{u}_{C1}\right }$ | $-M \cdot \frac{u_{C1,T}}{ \underline{u}_{C1} }$ | $\delta_{FL} = 1 - M \cdot \frac{u_{C1,S}}{ \underline{u}_{C1} }$            |  |  |

| 6 + 7   | $M \cdot \frac{u_{C1,T}}{\left \underline{u}_{C1}\right }$  | $M \cdot \frac{u_{C1,S}}{ \underline{u}_{C1} }$             | -                                                | $\delta_{FL} = 1 + M \cdot \frac{u_{C1,R}}{ \underline{u}_{C1} }$            |  |  |

| 8 + 9   | $-M \cdot \frac{u_{C1,R}}{\left \underline{u}_{C1}\right }$ | -                                                           | $-M \cdot \frac{u_{C1,S}}{ \underline{u}_{C1} }$ | $\delta_{FL} = 1 - M \cdot \frac{u_{C1,T}}{ \underline{u}_{C1} }$            |  |  |

| 10 + 11 | -                                                           | $M \cdot \frac{u_{C1,R}}{\left \underline{u}_{C1}\right }$  | $M \cdot \frac{u_{C1,T}}{ \underline{u}_{C1} }$  | $\delta_{FL} = 1 + M \cdot \frac{u_{C1,S}}{\left \underline{u}_{C1}\right }$ |  |  |

In jedem Fall ist die effektive Leitdauer der drei Transistoren im Fall symmetrischer Verhältnisse für alle Sektoren durch

$$\delta_{leit,SR} = M \cdot \frac{\left| \underline{u}_{C1,R} \right|}{\hat{U}_{C1}} \tag{2.30}$$

$$\delta_{leit,SS} = M \cdot \frac{\left| \underline{u}_{C1,S} \right|}{\hat{U}_{C1}} \tag{2.31}$$

$$\delta_{leit,ST} = M \cdot \frac{\left| \underline{u}_{C1,T} \right|}{\hat{U}_{C1}} \tag{2.32}$$

gegeben, wie sich anhand der Einschaltdauern aus TABELLE 2.1 leicht nachprüfen lässt.

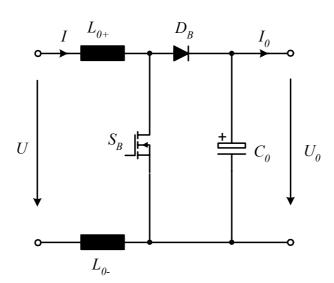

# 2.2 Hochsetzsteller-Ausgangsteil

Der ausgangsseitige Boost-Konverter befindet sich wie in Abbildung 2.5 gezeigt zwischen der Induktivität  $L_0$  und dem Kondensator  $C_0$ . Da diese beiden passiven Bauelemente bereits als Ausgangsfilter der Tiefsetzsteller-Eingangsstufe vorhanden sind, besteht der Aufwand daher lediglich im Einfügen eines Schalters und einer Diode (siehe Abbildung 2.5). Seine Aufgabe ist es für den Fall, dass die geforderte Ausgangsspannung  $u_0^*$  die seitens der Tiefsetzsteller-Eingangsstufe maximal mögliche Zwischenkreisspannung  $u_{max}$  übersteigt

$$u_0^* > u_{\text{max}},$$

(2.33)

die Spannung am Ausgang entsprechend hochzusetzen. Das hierfür erforderliche Tastverhältnis berechnet sich aus dem Spannungsübersetzungsverhältnis

$$\frac{u_0^*}{u_{\text{max}}} = \frac{1}{1 - \delta_B} \tag{2.34}$$

$$\delta_B = 1 - \frac{u_{\text{max}}}{u_0^*}. \tag{2.35}$$

Für deaktivierten Boost-Konverter

$$u_0^* \le u_{\text{max}} \tag{2.36}$$

bleibt der Boost-Schalter  $S_B$  ständig geöffnet und trägt nicht zur Spannungsübersetzung des Konverters bei. Die Soll-Ausgangsspannung ist dann wie in (2.13) berechnet durch die mittlere Zwischenkreisspannung gegeben:

$$u_0^* = u^*. (2.37)$$

Abbildung 2.5: Topologie des ausgangsseitigen Hochsetzstellers.

# 2.3 Betriebsbereich des Buck+Boost-Konverters

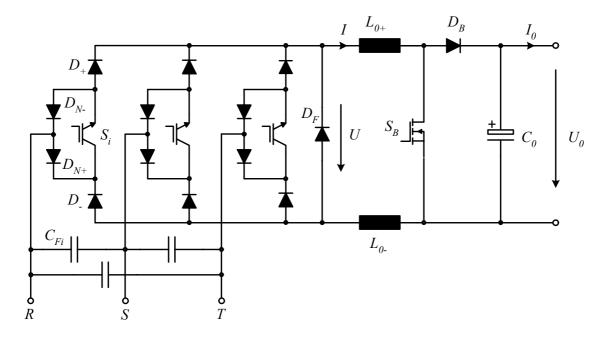

Der Tiefsetzsteller und der Hochsetzsteller lassen sich nun wie in Abbildung 2.6 zu einem Konverter zusammenfügen. Die Induktivität  $L_0$  (bzw.  $L_{0+}$  und  $L_{0-}$ ) wird vom Buck- und vom Boost-Teil geteilt und am Eingang und Ausgang des Systems befinden sich nun spannungseinprägende Kondensatoren. Das Gesamtsystem kann damit Eingangsspannungen in einem weiten Bereich auf eine konstante Ausgangsspannung umsetzen bzw. könnte auch bei fester Eingangsspannung die Ausgangsspannung in einem weiten Bereich eingestellt werden.

Abbildung 2.6: Gesamtschaltung des Buck+Boost-Konverters, der sich aus der Zusammenschaltung der Buck-Gleichrichterstufe und des ausgangsseitigen DC-DC Boost-Konverters ergibt.

Zum Abschluss dieses Kapitels werden nun die Aussteuerbereiche sämtlicher Betriebsgrössen berechnet, um eine Basis für die nachfolgende Auslegung des Systems zu erhalten.

Der Aussteuergrad M des Buck-Konverters ist über (2.23) definiert, für symmetrische Netzbedingungen entspricht das

$$M = \frac{2}{3} \cdot \frac{U}{\hat{U}_N} \,. \tag{2.38}$$

Unter Annahme eines verlustfreien Konverters lautet die Leistungsbilanz

$$P_0 = \frac{3}{2}\hat{U}_N\hat{I}_N = UI, \qquad (2.39)$$

somit ist das Verhältnis der ein- und ausgangsseitigen Ströme genau gleich dem Modulationsindex

$$M = \frac{\hat{I}_N}{I} \,. \tag{2.40}$$

Mit

$$\hat{I}_{N,\text{max}} = I \tag{2.41}$$

ist somit der Wertebereich des Modulationsindex bestimmt

$$M = 0...1$$

. (2.42)

Im praktischen Betrieb wird der Buck-Konverter nicht bis an die Grenzen seines Übersetzungsverhältnisses ausgesteuert werden, da für den geregelten Betrieb des Konverters eine aktive Dämpfung (siehe Kapitel 6) eingesetzt wird, für die ein Teil des Aussteuergrades reserviert wird. Um eine dynamische Reserve von 10% für die aktive Dämpfung des Systems sicherzustellen, wird der Modulationsgrad auf

$$M = 0...M_{\text{max}} = 0...0.9 \tag{2.43}$$

begrenzt. Wenn die Verluste im System vernachlässigt werden, lautet die Leistungsbilanz

$$P_N = \frac{3}{2}\hat{U}_N \hat{I}_N = UI = P, \qquad (2.44)$$

woraus sich mit (2.40) die Spannungsübersetzung zu

$$M = \frac{2}{3} \frac{U}{\hat{U}_N} = \frac{\sqrt{2}}{3} \frac{U}{U_{N \, rms}}.$$

(2.45)

ergibt. Die maximale Zwischenkreisspannung ist daher durch

$$U_{\text{max}} = \frac{3}{\sqrt{2}} M_{\text{max}} \cdot U_{N,rms} \tag{2.46}$$

gegeben.

Es sei nun gemäss den Spezifikationen in Kapitel 1 die Nennleistung  $P_0$  = 5kW, die gewünschte Ausgangsspannung  $U_0$  = 400V und der Eingangsspannungsbereich  $U_{N,rms}$  = 120V...280V betrachtet.

Für genügend hohe Eingangsspannungen kann die gewünschte Ausgangsspannung nur mit dem Buck-Eingangsteil hergestellt werden und der Boost-Konverter muss nicht aktiviert werden. Die Grenze ist mit (2.46) durch

$$U_{N,rms}\Big|_{U_0=U_{\text{max}}} = \frac{\sqrt{2}}{3} \frac{U_0}{M_{\text{max}}} = 210V$$

(2.47)

gegeben.

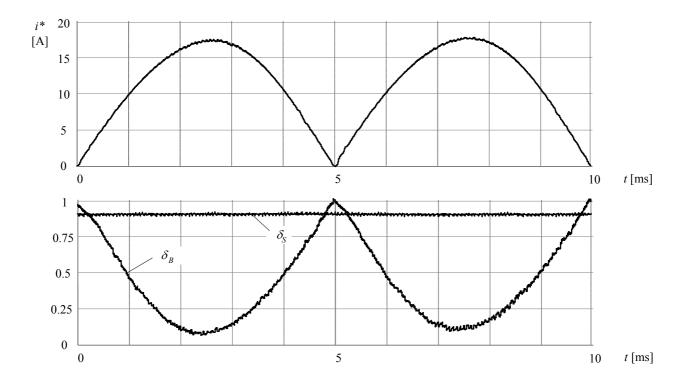

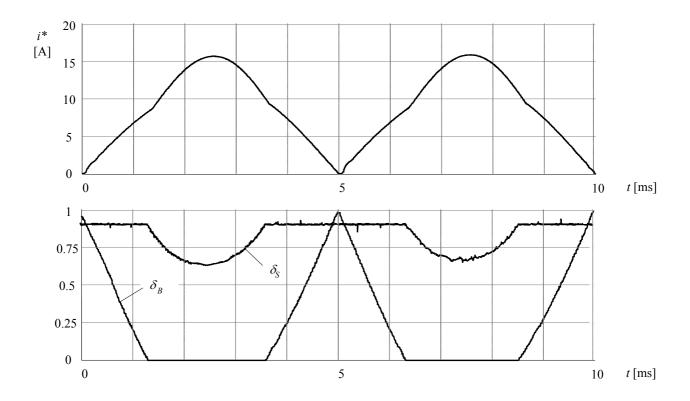

Im reinen Buck-Betrieb nimmt der Aussteuergrad M des Buck-Konverters mit (2.45) die Werte

$$M = \frac{\sqrt{2}}{3} \frac{U}{U_{N,rms}} = \frac{\sqrt{2}}{3} \frac{400 \text{V}}{210 \text{V}...280 \text{V}} = 0.67...0.9$$

(2.48)

an, während die Einschaltdauer des Boost Konverters stets gleich null ist:

$$\delta_B = 0. (2.49)$$

Die Zwischenkreisspannung U bleibt in diesem Bereich konstant auf

$$U = U_0 = 400 \,\mathrm{V} \,, \tag{2.50}$$

daher ist auch der DC-Strom I in der Induktivität konstant mit

$$I = \frac{P}{U} = \frac{5\text{kW}}{400\text{V}} = 12.5\text{A}$$

(2.51)

Die Eingangsstromamplitude  $\hat{I}_N$  wird auf Grund der konstanten Leistung mit grösserer Eingangsspannung kleiner,

$$\hat{I}_N = \frac{\sqrt{2}}{3} \frac{P_N}{U_{N,rms}} = \frac{\sqrt{2}}{3} \frac{5 \text{kW}}{210 \text{V}...280 \text{V}} = 8.4 \text{A}...11.2 \text{A},$$

(2.52)

Im Buck+Boost-Betrieb, d.h. für Eingangsspannungen

$$U_{N,rms} < 210 \mathrm{V} \,, \tag{2.53}$$

bleibt die Aussteuerung des Buck-Konverters auf seinem maximalen Wert

$$M = M_{\text{max}} = 0.9 \tag{2.54}$$

Die Zwischenkreisspannung U sinkt dabei für kleinere Eingangsspannungen auf

$$U = \frac{3}{\sqrt{2}} M_{\text{max}} \cdot U_{N,rms} = \frac{3}{\sqrt{2}} \cdot 0.9 \cdot (120 \text{V...}210 \text{V}) = 230 \text{V...}400 \text{V}, \qquad (2.55)$$

der Boost-Konverter muss daher mit (2.35) ein Tastverhältnis von

$$\delta_B = 1 - \frac{U}{U_0} = 1 - \frac{230 \text{V...}400 \text{V}}{400 \text{V}} = 0...0.43$$

(2.56)

aufweisen um weiterhin  $U_0 = 400$ V zu halten. Der Strom I in der DC-Induktivität steigt für sinkende Zwischenkreisspannungen gemäss

$$I = \frac{P}{U} = \frac{5\text{kW}}{230\text{V...}400\text{V}} = 12.5\text{A...}21.7\text{A};$$

(2.57)

auf Grund des konstanten Aussteuergrades des Buck-Eingangsteiles vergrössert sich damit auch der Eingangsstrom:

$$\hat{I}_N = M \cdot I = 0.9 \cdot (12.5 \text{A...} 21.7 \text{A}) = 11.3 \text{A...} 19.5 \text{A}.$$

(2.58)

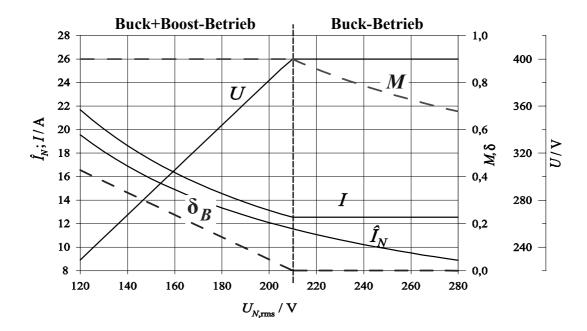

Die Abhängigkeiten der Betriebsparameter von der Eingangsspannung sind in Abbildung 2.7 nochmals dargestellt. Auf dieser Grundlage kann im Weiteren das Design des Systems durchgeführt werden.

Abbildung 2.7: Abhängigkeit der Betriebsparameter von der Eingangsspannung.

# Kapitel 3 Systemdesign

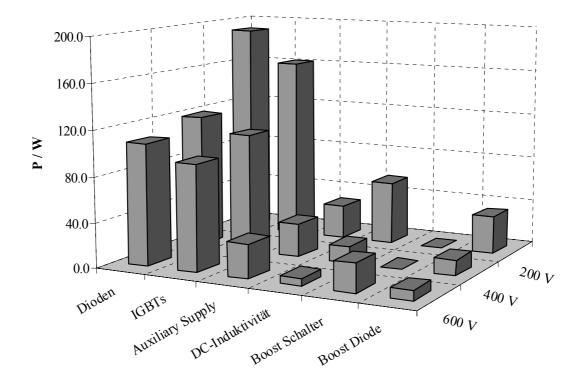

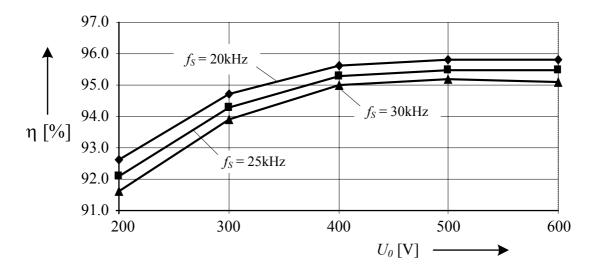

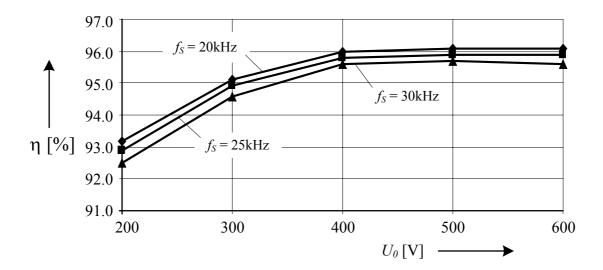

In diesem Kapitel werden sämtliche Betriebsgrössen für das System festgelegt. Dies sind im Wesentlichen der Typ und die Kennwerte der aktiven und passiven Bauteile des Systems sowie die Schaltfrequenz. Zunächst werden auf Basis der maximalen Beanspruchungen der Leistungshalbleiter des Systems die Komponenten ausgewählt. Das Schaltverhalten unter Verwendung der ausgewählten Halbleiter wird analysiert und die Schaltverluste in Abhängigkeit vom Arbeitspunkt des Konverters berechnet. Damit wird ein sinnvoller Bereich für die Schaltfrequenz ausgewählt und es werden die passiven Komponenten dimensioniert. Abschliessend kann der mit dieser Auslegung zu erwartende Gesamtwirkungsgrad des Konverters unter Berücksichtigung der Schalt- und Leitverluste, sowie der Verluste der passiven Komponenten berechnet werden.

# 3.1 Auswahl der Leistungshalbleiter

### 3.1.1 Strombelastung

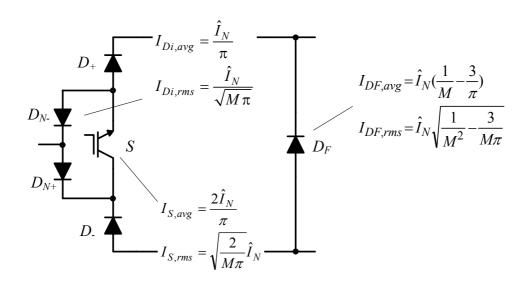

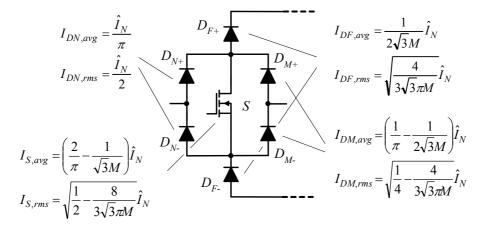

Zur Auswahl der Leistungshalbleiter und zur späteren Berechnung der Leitverluste müssen die Mittel- und Effektivwerte der Ströme in den Leistungstransistoren und - dioden ermittelt werden.

Aufgrund der Dreiphasen-Symmetrie der Eingangsspannungen und der identen Struktur der drei Eingangsphasen des Konverters können die Betrachtungen auf eine Phase beschränkt werden. Wie im vorhergehenden Kapitel gezeigt wurde, ist die Leitdauer des Transistors  $S_R$  für alle Sektoren gemäss (2.30)

$$\delta_{leit,SR}(\varphi_{C1}) = M \cdot \frac{\left| u_{C1,R} \right|}{\hat{U}_{C1}} = M \cdot \left| \cos \varphi_{C1} \right|. \tag{3.1}$$

Für konstanten Zwischenkreisstrom I ergibt sich daraus der lokale Mittelwert

$$i_{SR,avg}(\varphi_{C1}) = I \cdot \delta_{leit,SR}(\varphi_{C1}) = I \cdot M \cdot \left| \cos \varphi_{C1} \right|$$

(3.2)

und schliesslich der globale Mittelwert des Transistorstromes über eine Netzperiode

$$I_{SR,avg} = I \cdot M \cdot \frac{1}{2\pi} \int_{0}^{2\pi} |\cos \varphi_{C1}| d\varphi_{C1} = \frac{2\hat{I}_{N}}{\pi}.$$

(3.3)

Der lokale Effektivwert des Transistorstromes lässt sich mit

$$i_{SR,rms}^{2}(\varphi_{C1}) = I^{2} \cdot \delta_{leit,SR}(\varphi_{C1}) = I^{2} \cdot M \cdot |\cos \varphi_{C1}|$$

$$(3.4)$$

berechnen, also durch Multiplikation des lokalen Mittelwertes (3.2) mit dem konstanten Wert *I*. Ebenso erhält man den globalen Effektivwert über Multiplikation des globalen Mittelwertes mit *I*:

$$I_{SR,rms}^{2} = I^{2} \cdot M \cdot \frac{1}{2\pi} \int_{0}^{2\pi} \left| \cos \varphi_{C1} \right| d\varphi_{C1} = \frac{2\hat{I}_{N}^{2}}{M \cdot \pi}.$$

(3.5)

Die Moduldioden  $D_{R,N^+}$  und  $D_{R^+}$  haben aus Symmetriegründen in sechs der zwölf Sektoren dieselbe Leitdauer  $\delta_{leit,SR}$  wie der Transistor  $S_R$  und führen während der übrigen Sektoren keinen Strom. Für die beiden Moduldioden  $D_{R,N^-}$ ,  $D_{R^-}$  gilt dasselbe in umgekehrter Form. Daher sind die globalen Mittelwerte und die Quadrate der globalen Effektivwerte aller Moduldioden über eine Netzperiode

$$I_{DM,avg} = I \cdot M \cdot \frac{1}{2\pi} \int_{0}^{\pi} |\cos \varphi_{C1}| d\varphi_{C1} = \frac{\hat{I}_{N}}{\pi}.$$

(3.6)

$$I_{DM,rms}^{2} = I^{2} \cdot M \cdot \frac{1}{2\pi} \int_{0}^{\pi} |\cos \varphi_{C1}| d\varphi_{C1} = \frac{\hat{I}_{N}^{2}}{M \cdot \pi}.$$

(3.7)

Die Freilaufdiode wird im ersten Sektor dann leitend, wenn der Transistor  $S_R$  nicht leitet, d.h.

$$\delta_{leit,DF}(\varphi_{C1}) = 1 - M \cdot \frac{|u_{C1,R}|}{\hat{U}_{C1}} = 1 - M \cdot |\cos \varphi_{C1}|.$$

(3.8)

Der lokale Mittelwert des Freilaufdioden-Stromes im Sektor 1 ist also

$$i_{DF,avg}(\varphi_{C1}) = I \cdot \delta_{leit,DF}(\varphi_{C1}) = I \cdot \left(1 - M \cdot \left|\cos\varphi_{C1}\right|\right)$$

(3.9)

und das Quadrat des lokalen Effektivwertes

$$i_{DF,rms}^{2}(\varphi_{C1}) = I^{2} \cdot \delta_{leit,SR}(\varphi_{C1}) = I^{2} \cdot (1 - M \cdot |\cos \varphi_{C1}|).$$

(3.10)

Aufgrund der Symmetrie der drei Phasen wiederholt sich der Verlauf von  $i_{DF,avg}$  und  $i_{DF,rms}$  für alle folgenden Sektoren Der globale Mittelwert und das Quadrat des globalen Effektivwertes können daher durch Mittelung über den ersten Sektor gefunden werden:

$$I_{DF,avg} = I \cdot \frac{6}{\pi} \int_{0}^{\pi/6} \left( 1 - M \cdot \left| \cos \varphi_{C1} \right| \right) d\varphi_{C1} = I - \frac{3\hat{I}_{N}}{\pi} = \hat{I}_{N} \left( \frac{1}{M} - \frac{3}{\pi} \right), \tag{3.11}$$

$$I_{DF,rms}^{2} = I^{2} \cdot \frac{6}{\pi} \int_{0}^{\pi/6} \left( 1 - M \cdot \left| \cos \varphi_{C1} \right| \right) d\varphi_{C1} = \hat{I}_{N}^{2} \left( \frac{1}{M^{2}} - \frac{3}{M \cdot \pi} \right). \tag{3.12}$$

Die so gefundenen analytischen Beziehungen für die Mittel- und Effektivwerte der Ströme in den Halbleitern des Buck-Eingangsteils sind in Abbildung 3.1 zusammengefasst.

Abbildung 3.1: Mittelwerte und Effektivwerte der Ströme der Leistungshalbleiter des Eingangsteiles.

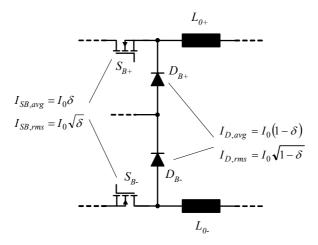

Für den Boost-Ausgangsteil lassen sich die Strombelastungen einfach berechnen. Der Mittelwert des Stromes im Boost-Schalter  $S_B$  ist direkt vom Tastverhältnis  $\delta_B$  abhängig

$$I_{SB,avg} = I \cdot \delta_B. \tag{3.13}$$

Mit dem Stromübersetzungsverhältnis des Boost-Konverters

$$\frac{I}{I_0} = \frac{U_0}{U} = \frac{1}{1 - \delta_B} \tag{3.14}$$

ergibt sich die Abhängigkeit des Mittelwerts des Stromes im Boost-Transistor vom Ausgangsstrom  $I_0$

$$I_{SB,avg} = I_0 \cdot \frac{\delta_B}{1 - \delta_B}. \tag{3.15}$$

Das Stromeffektivwertquadrat berechnet sich zu

$$I_{SB,rms}^2 = I^2 \cdot \delta_B = I_0^2 \cdot \frac{\delta_B}{(1 - \delta_B)^2}.$$

(3.16)

Analog dazu können schließlich auch der Mittelwert und das Quadrat des Effektivwertes des Stromes in der Boost-Diode  $D_B$  ermittelt werden

$$I_{DB,avg} = I \cdot (1 - \delta_B) = I_0 \tag{3.17}$$

$$I_{DB,rms}^2 = I^2 \cdot (1 - \delta_B) = I_0^2 \cdot \frac{1}{(1 - \delta_B)}.$$

(3.18)

Die analytischen Beziehungen für die Strombeanspruchung der Bauelemente des Boost-Konverters sind in Abbildung 3.2 grafisch zusammengefasst.

Abbildung 3.2 Mittelwerte und Effektivwerte der Strombelastungen der Leistungshalbleiter der Boost-Ausgangsstufe des Buck+Boost-Konverters.

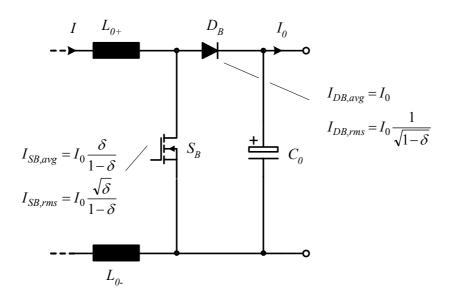

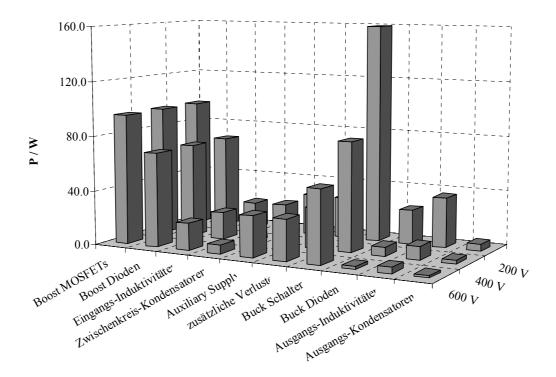

Die Abhängigkeit der Strommittel- und Stromeffektivwerte der Leistungshalbleiter von der Eingangsspannung  $U_{N,l-l,rms}$  ist in Abbildung 3.3 gezeigt. Die für die Dimensionierung relevanten Maximalwerte, die an einer der beiden Grenzen des Eingangsspannungsbereiches auftreten, sind in Tabelle 3.1 zusammengefasst.

Abbildung 3.3: Abhängigkeit der Mittel- und Effektivwerte der Strombelastungen in den Leistungshalbleitern von der Eingangsspannung.

TABELLE 3.1

Zusammenfassung der Minimal- und Maximalwerte der Strombelastungen der Halbleiter für minimale und maximale Eingangsspannung

| $U_{Nl	ext{-}l,rms}$ | M    | δ    | $\hat{I}_N$ | $I_{Si,avg}$ | $I_{Si,rms}$ | $I_{Di,avg}$ | $I_{Di,rms}$ | $I_{DF,avg}$ | $I_{DF,rms}$ | $I_{SB,avg}$ | $I_{SB,rms}$ | $I_{DB,avg}$ | $I_{DB,rms}$ |

|----------------------|------|------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| V                    | -    | -    | Α           | A            | A            | A            | A            | A            | A            | A            | A            | A            | A            |

| 208                  | 0.9  | 0.43 | 19.5        | 12.5         | 16.5         | 6.2          | 11.6         | 3            | 8.1          | 9.4          | 14.4         | 12.5         | 16.5         |

| 480                  | 0.67 | 0    | 8.4         | 5.3          | 8.2          | 2.7          | 5.8          | 4.5          | 7.5          | 0            | 0            | 12.5         | 12.5         |

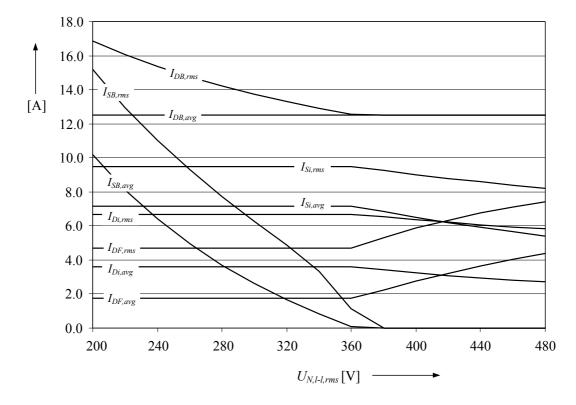

### 3.1.2 Sperrspannungsbeanspruchung

Es werden nun die maximalen Sperrspannungsbeanspruchungen der Leistungshalbleiter ermittelt um schliesslich eine Auswahl der Komponenten treffen zu können. Dafür ist es wieder ausreichend, lediglich den ersten Eingangsspannungssektor zu betrachten, da sich die Verhältnisse aufgrund der Phasensymmetrie für die folgenden Sektoren wiederholen. In Abbildung 3.4 sind die in Sektor 1 auftretenden Schaltzustände  $s_j = (101)$ , (110) und (010) des Buck-Eingangsteiles dargestellt<sup>3</sup>. Dabei sind die jeweils an den Halbleitern auftretenden Sperrspannungen eingezeichnet.

Die Maxima der verketteten Eingangsspannungen betragen im Sektor 1 ( $\varphi_{CI} = 0...\pi/6$ ) gemäss Abbildung 3.4

$$u_{C1,RT,\max,0...\pi/6} = u_{C1,RT}\Big|_{(\varphi_{C1} = \pi/6)} = \sqrt{3} \cdot \hat{U}_{C1} = 679 \text{V},$$

(3.19)

$$u_{C1,RS,\max,0...\pi/6} = u_{C1,RS}|_{(\varphi_{C1}=0)} = 1.5 \cdot \hat{U}_{C1} = 588V,$$

(3.20)

$$u_{C1,ST,\max,0...\pi/6} = u_{C1,ST}\Big|_{(\varphi_{C1}=\pi/6)} = \frac{\sqrt{3}}{2} \cdot \hat{U}_{C1} = 339 \text{V},$$

(3.21)

daraus ergeben sich die maximalen Sperrspannungen für die Halbleiter:

$$U_{\text{max.}Si} = u_{C1.RS.\text{max.}0...\pi/6} = 1.5 \cdot \hat{U}_{C1} = 588\text{V},$$

(3.22)

$$U_{\text{max},Di,N\pm} = u_{C1,RS,\text{max},0...\pi/6} = 1.5 \cdot \hat{U}_{C1} = 588\text{V},$$

(3.23)

$$U_{\text{max},Di\pm} = u_{C1,RT,\text{max},0...\pi/6} = \sqrt{3} \cdot \hat{U}_{C1} = 679 \text{V},$$

(3.24)

$$U_{\text{max},DF} = u_{C1,RT,\text{max},0...\pi/6} = \sqrt{3} \cdot \hat{U}_{C1} = 679 \text{V}.$$

(3.25)

Unter Berücksichtigung von Schaltüberspannungen, die in der Praxis bei hoher Schaltgeschwindigkeit Werte von etwa  $\Delta U = 150$ V annehmen können, sind daher Bauelemente mit einer Sperrspannungsfestigkeit von zumindest 900V auszuwählen.

<sup>&</sup>lt;sup>3</sup> Unter Vorgriff auf das schlussendlich verwendete schaltverlustoptimale Verfahren SLO (siehe Kapitel 4) werden hier nur diese drei Schalterkombinationen untersucht.

Der Transistor und die Diode des Boost-Teiles sind bei einer Ausgangsspannung von  $U_0 = 400$ V mit einer Nennsperrspannung von

$$U_{\text{max},SB} = U_{\text{max},DB} = U_0 = 400 \text{V}$$

(3.26)

belastet, daher kann bei der Auswahl der Komponenten unter Berücksichtigung von Schaltüberspannungen auf Halbleiter mit 600V Sperrspannungsfestigkeit zurückgegriffen werden.

Abbildung 3.4: Sperrspannungen an den Halbleitern für die drei im Sektor 1 auftretenden Schaltzustände. Wenn an einem Halbleiter keine Sperrspannung eingezeichnet ist, ist diese Null.

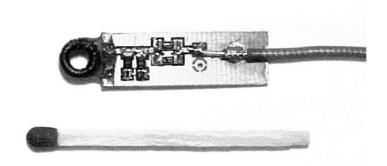

### 3.1.3 Auswahl der Leistungshalbleiter

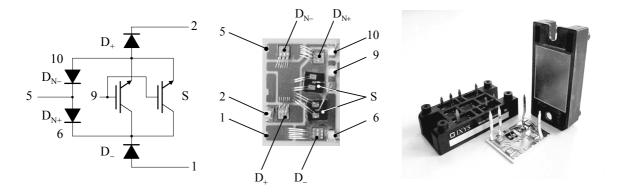

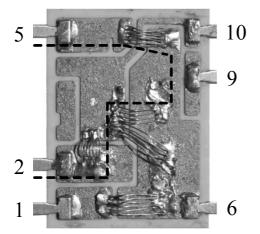

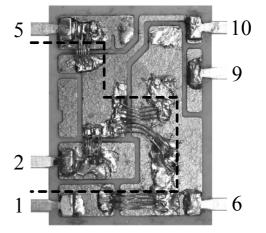

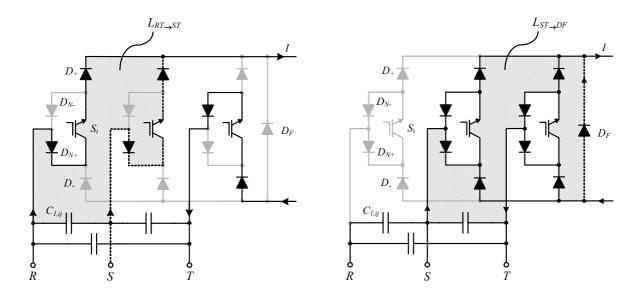

Mit den in den vorhergehenden Abschnitten ermittelten Strom- und Spannungsbelastungen können nun die Halbleiter ausgewählt werden. Für die Realisierung eines Brückenzweiges des Buck-Eingangsteiles wurden der Transistor und die vier Dioden in einem Leistungsmodul integriert [20]. Dies ermöglicht im Vergleich zu diskreter Realisierung eine weitaus kompaktere Bauweise. Das Leistungsmodul ist in Abbildung 3.5 gezeigt. Auf Grund der hohen Strombelastung bei kleiner Eingangsspannung wurden hier zur Aufteilung des Stromes zwei IGBTs parallel geschaltet. Die verwendeten Komponenten sind in zusammengefasst. Weitere Details sind in den Datenblättern ersichtlich [21],[22],[23]. Da am Boost-Schalter als maximale Sperrspannung die Ausgangsspannung auftritt, kann ein 600V-MOSFET-Schalter verwendet werden.

Die verwendeten Halbleiter-Komponenten sind in TABELLE 3.2 aufgelistet.

Abbildung 3.5: Schaltschema (links), internes Layout (Mitte) und Gehäuse des Leistungsmoduls zur Integration sämtlicher Leistungshalbleiter eines Brückenzweiges.

TABELLE 3.2

Für die Realisierung des Leistungsteiles verwendete Halbleiter-Komponenten

| Komponente               | Spezifikationen                                                                           |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| $Modul$ - $IGBT S_i$     | IGBT - MODUL VUI31-12N1, 1200V, 65A $U_{CE0}=1$ V, $r_{CE}=60$ m $\Omega$ ,               |  |  |  |  |

| $Modul$ - $Dioden D_i$ , | Diode - MODUL VUI31-12N1, 1200V, 25A $U_F = 1.65$ V, $r_D = 18$ mΩ,                       |  |  |  |  |

| $Diode D_F$              | RHRP30120 , 1200V, 30A $U_F = 0.97$ V, $r_D = 24$ m $\Omega$ $k_{l,rr} = 5$ µJ/A          |  |  |  |  |

| $Boost-MOSFET S_B$       | SPW47N60C3, 600V, 47A<br>$R_{DS,ON} = 70$ mΩ $k_{I,on} = 39$ μJ/A, $k_{I,off} = 8.3$ μJ/A |  |  |  |  |

| Boost-Diode $D_B$        | 30EPH06, 600V, 30A<br>$U_F = 0.67$ V, $r_D = 150$ mΩ $k_{I,rr} = 3.2$ μJ/A                |  |  |  |  |

# 3.2 Analyse des Schaltverhaltens

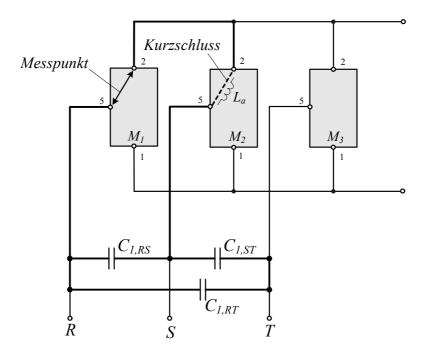

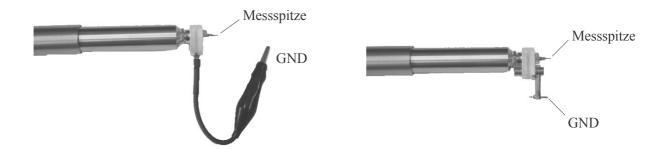

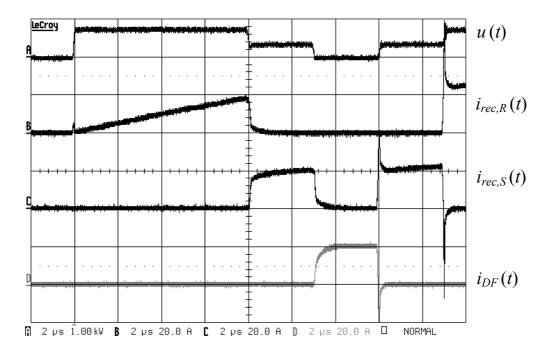

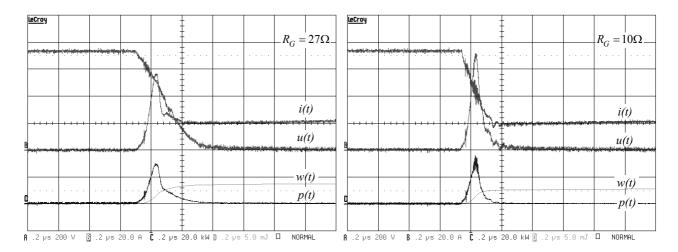

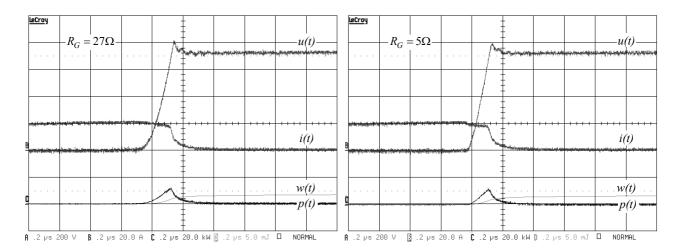

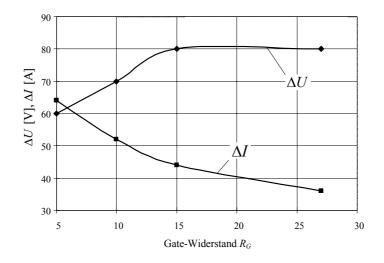

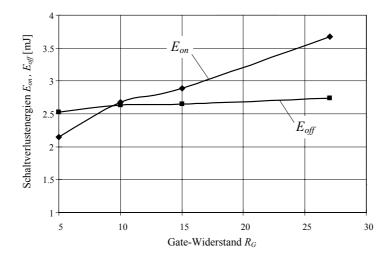

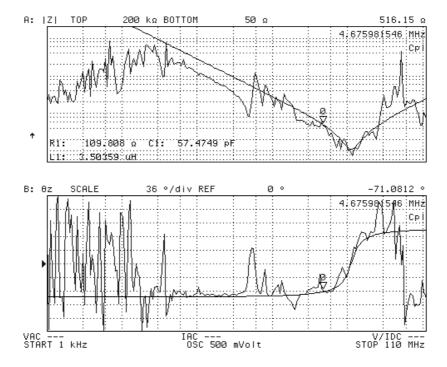

In diesem Abschnitt soll näher auf das Schaltverhalten der Leistungshalbleiter des Buck-Eingangsteiles eingegangen werden. In Verbindung damit ist die Analyse der Verdrahtungsinduktivitäten innerhalb des Moduls und zwischen den Phasen auf der Leiterplatte wichtig, da diese Induktivitäten bei den Kommutierungsvorgängen wesentlich die auftretenden Überspannungen bestimmen. Anschliessend werden die Gate-Vorwiderstände für Ein- und Ausschalten der Schalter so ausgewählt, dass geringe Schaltüberspannungen und –ströme sichergestellt werden. Das Ziel der dann folgenden Schaltverlustmessungen ist es, die auftretenden Schaltverluste in Abhängigkeit vom Arbeitspunkt, d.h. als Funktion der geschaltete Spannung und des geschalteter Stroms zu ermitteln. Das Wissen über die Schaltverluste dient schliesslich als Basis für die Wahl der Schaltfrequenz, wobei versucht wird einen Kompromiss zwischen hoher Leistungsdichte (bei hoher Schaltfrequenz auf Grund kleinerer passiver Komponenten) und hohem Wirkungsgrad (bei niedriger Schaltfrequenz auf Grund geringerer Schaltverluste) zu erreichen.

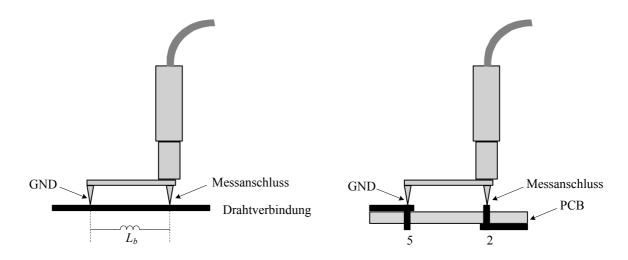

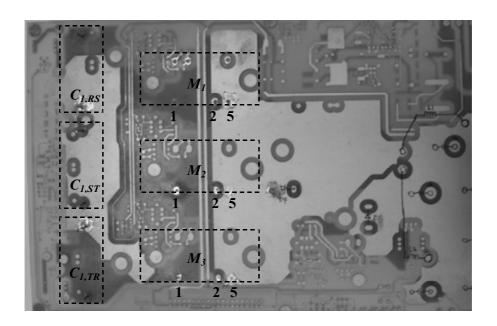

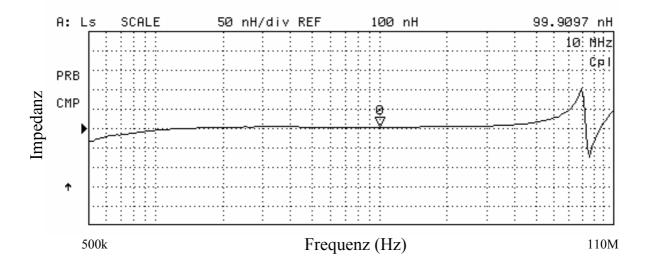

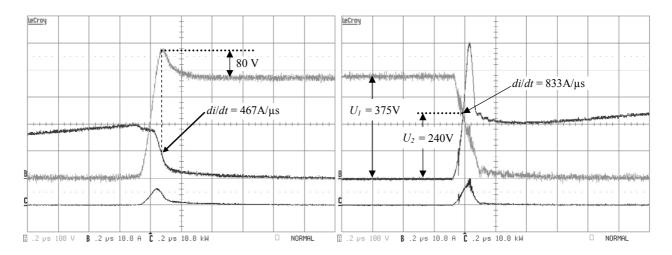

### 3.2.1 Analyse des Leistungsmoduls

Die Verwendung von Leistungsmodulen hat im Wesentlichen drei Vorteile gegenüber diskreter Realisierung:

- Kompaktere Bauform im vorliegenden Fall würden diskrete Elemente in TO247-Gehäusen fast den doppelten Platzbedarf aufweisen.

- Einfachere Bestückung (Einzelhalbleiter des Moduls sind gegenüber der Montagefläche isoliert) und damit geringere Kosten der gesamte Buck-Eingangsteil besteht nur mehr aus drei Modulen und einer Freilaufdiode.

- Geringere Verdrahtungsinduktivitäten und damit geringere Schaltüberspannungen

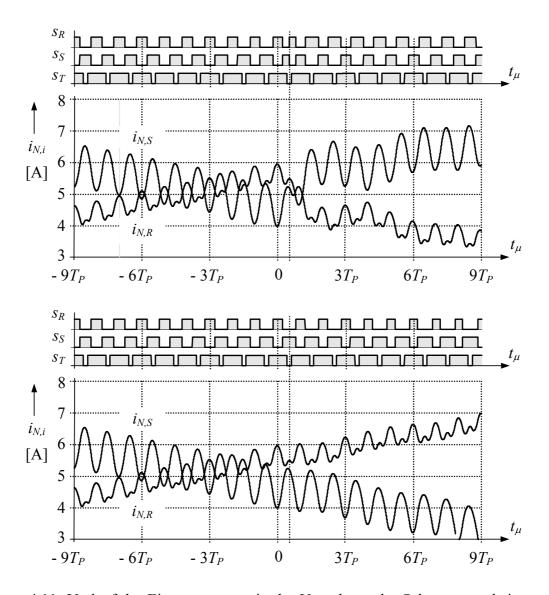

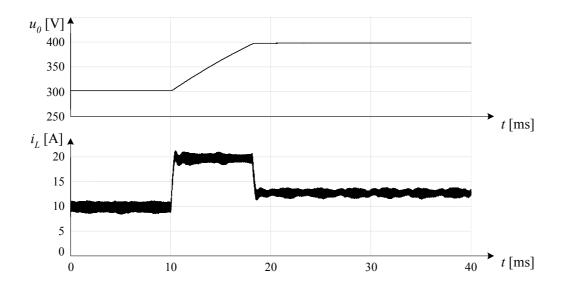

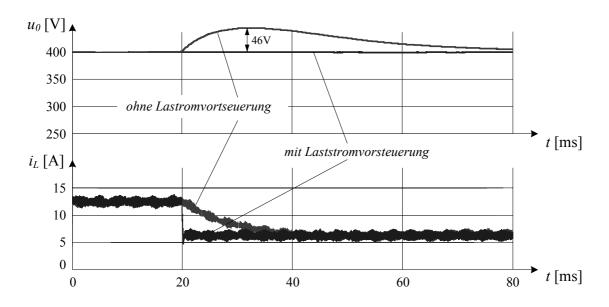

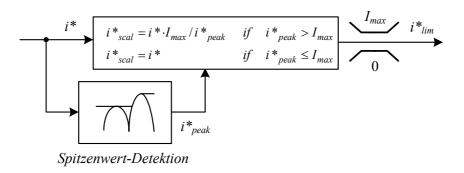

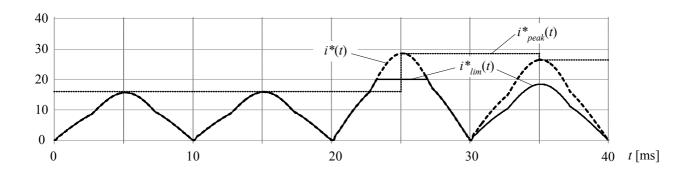

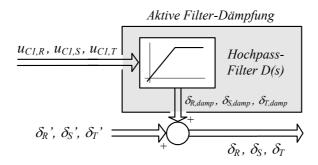

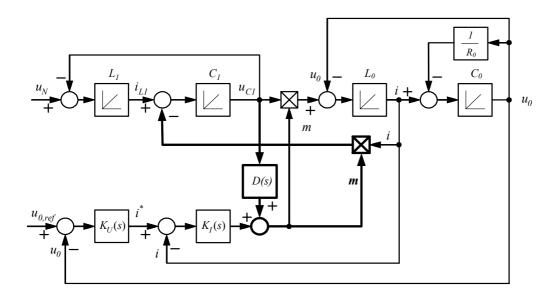

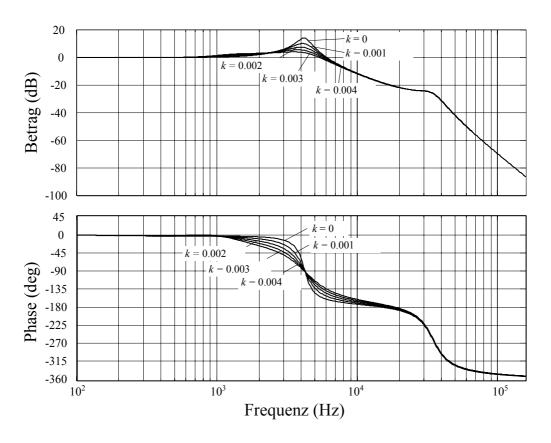

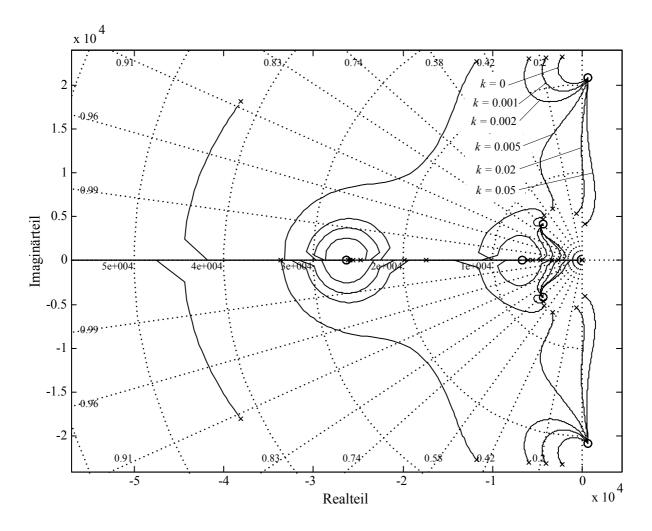

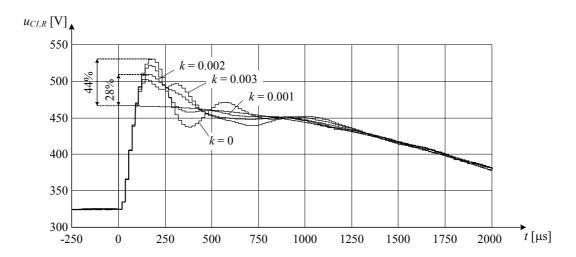

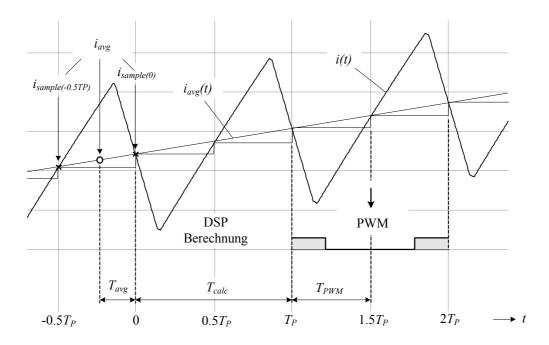

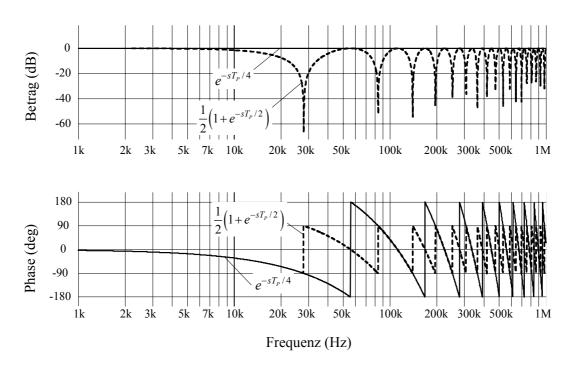

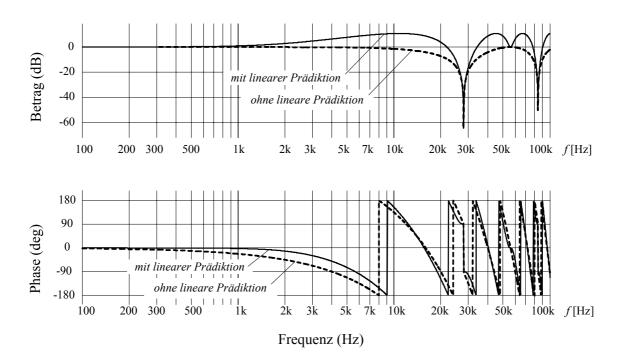

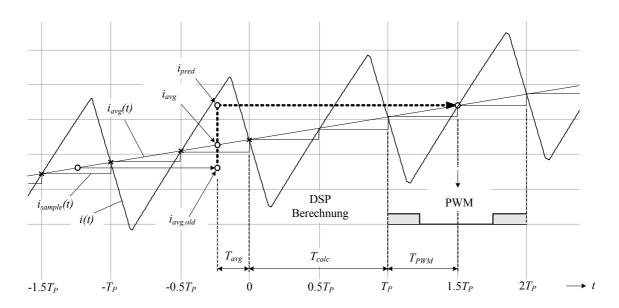

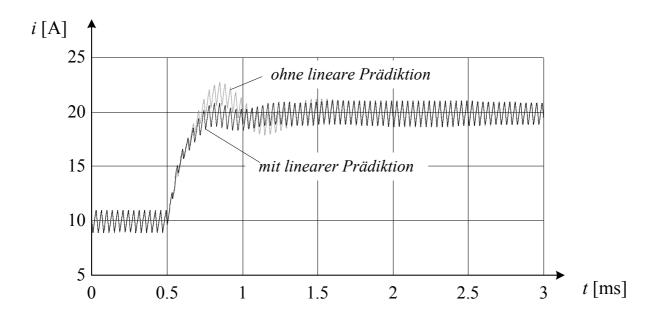

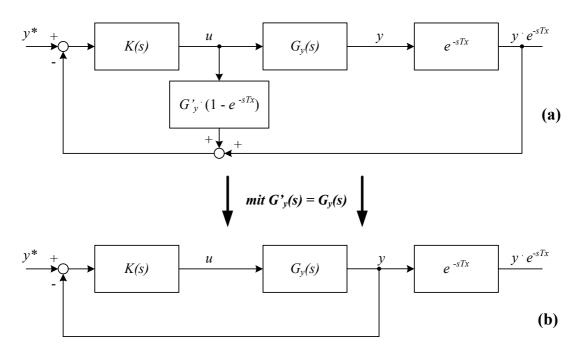

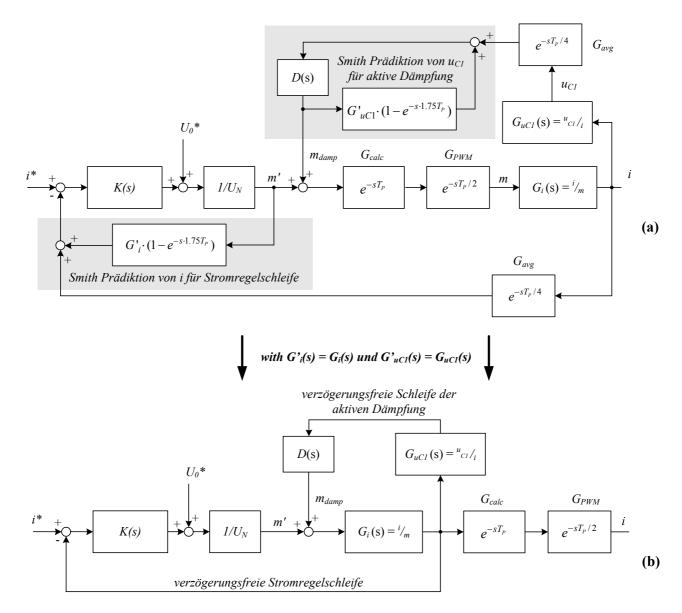

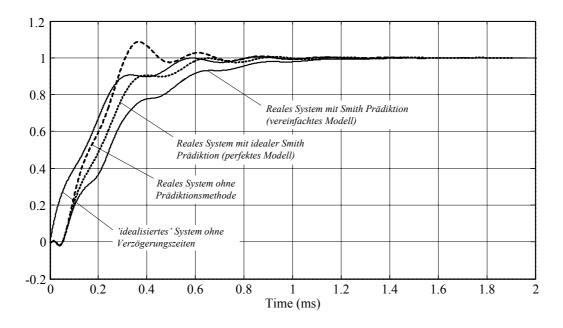

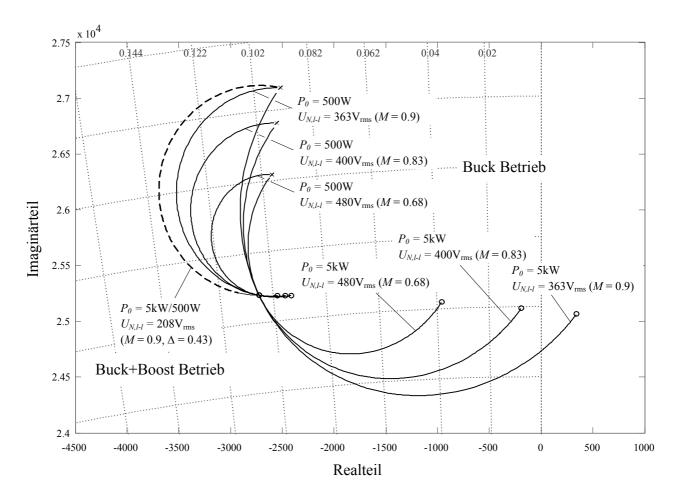

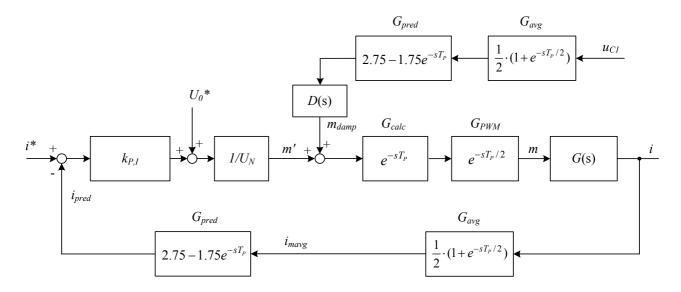

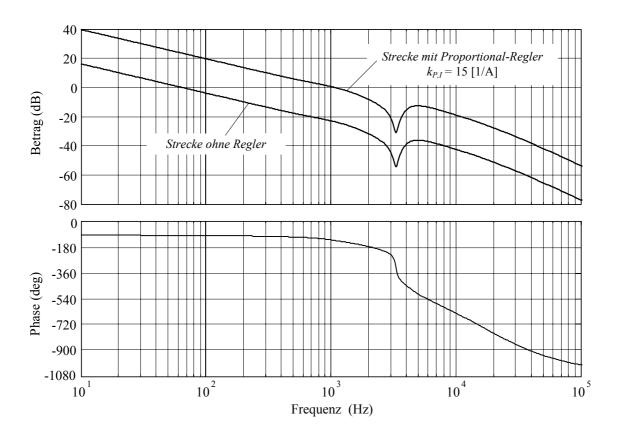

Demgegenüber stehen folgende Nachteile: