#### DISSERTATION

Theoretische und experimentelle Untersuchung eines Dreiphasen-Pulsgleichrichtersystems mit Dreischalter-Tiefsetzstellereingangsstufe und integrierter Hochsetzstellerausgangsstufe mit sinusförmiger Eingangsstromführung für den Einsatz in einem weiten Eingangsspannungsbereich

ausgeführt zum Zwecke der Erlangung des akademischen Grades eines Doktors der technischen Wissenschaften unter der Leitung von

> Prof. Dr. Johann Walter Kolar Power Electronics System Laboratory ETH-Zentrum/ETL H22, CH-8092 Zürich

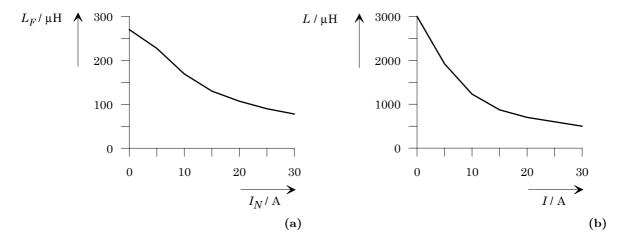

> > und

Prof. Dr. Manfred Schrödl Institut für Elektrische Antriebe und Maschinen Gusshausstraße 27/E372, A–1040 Wien

eingereicht an der Technischen Universität Wien Fakultät für Elektrotechnik und Informationstechnik

von

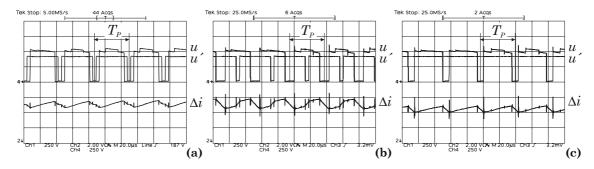

Dipl.-Ing. Martina Baumann Matr. Nr.: 9426619 Auhofstraße 84/41, A–1130 Wien

# Danksagung

### Kurzfassung

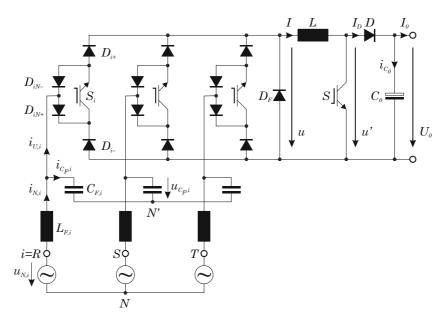

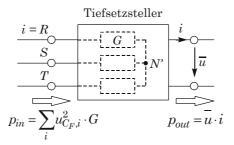

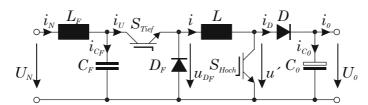

In der vorliegenden Arbeit wird ein neuartiges dreiphasiges Pulsgleichrichtersystem mit einer Dreischalter-Tiefsetzstellereingangsstufe und integrierter Hochsetzstellerausgangsstufe mit sinusförmigen Netzströmen und ohmschem Grundschwingungsverhalten für einen weltweiten Einsatz, d.h für den Betrieb in einem weiten Eingangsspannungsbereich von 208 V . . . 480 V Außenleiterspannung, mit einer Ausgangsspannung von 400 V und einer Nennleistung von 5 kW vorgestellt, das gegenüber den bekannten Schaltungsstrukturen wie dem Tiefsetzsteller oder dem Hochsetzsteller im genannten Einsatzbereich deutliche Vorteile bezüglich des Wirkungsgrades zeigt und gegenüber der Zusammenschaltung einphasiger Schaltungsstrukturen einen wesentlich geringeren Realisierungsaufwand aufweist.

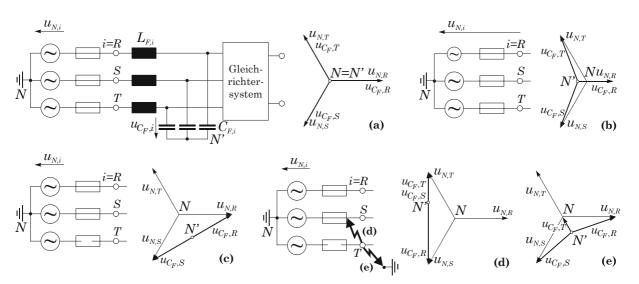

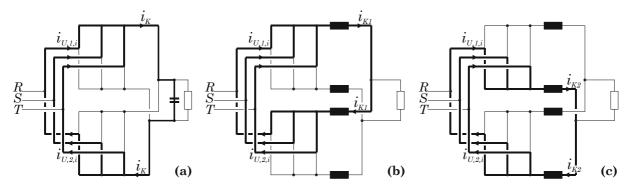

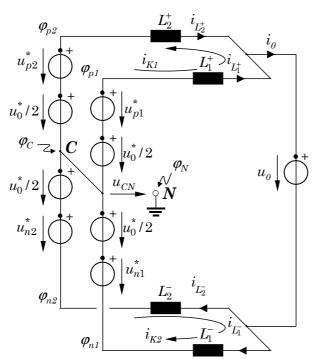

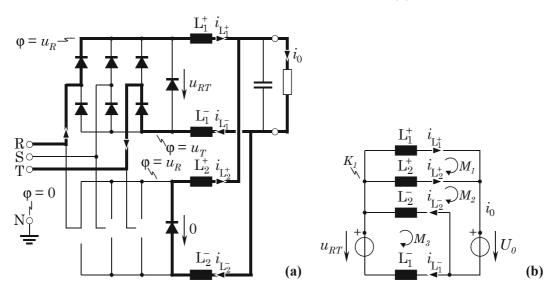

Die Entwicklung der Schaltung des Gleichrichtersystems wird in **Kapitel 1** gezeigt, wobei von der Kombination eines konventionellen Stromzwischenkreisumrichters mit einer integrierten Hochsetzstellerausgangsstufe ausgegangen wird.

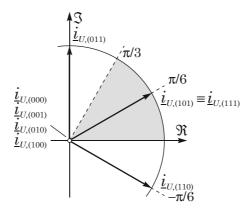

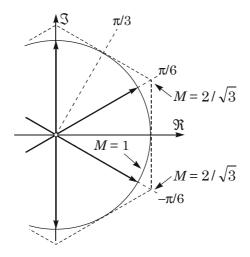

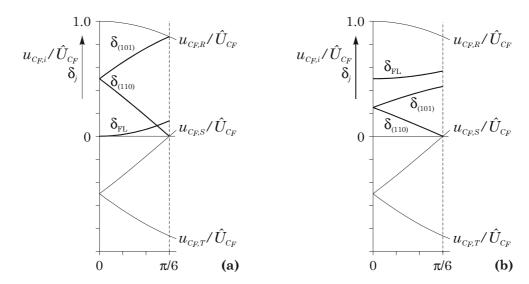

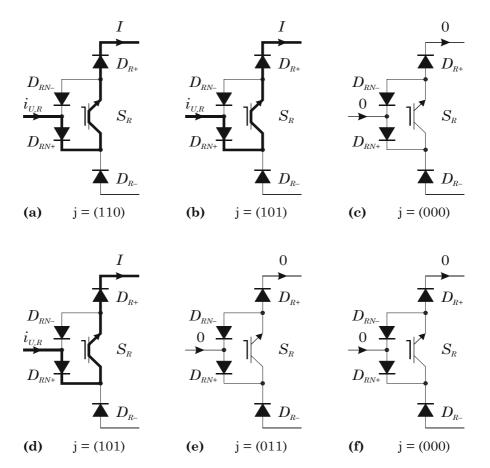

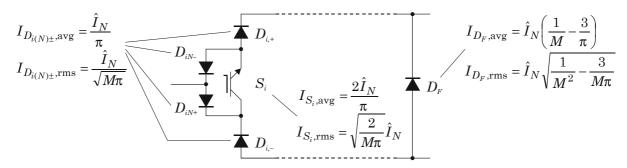

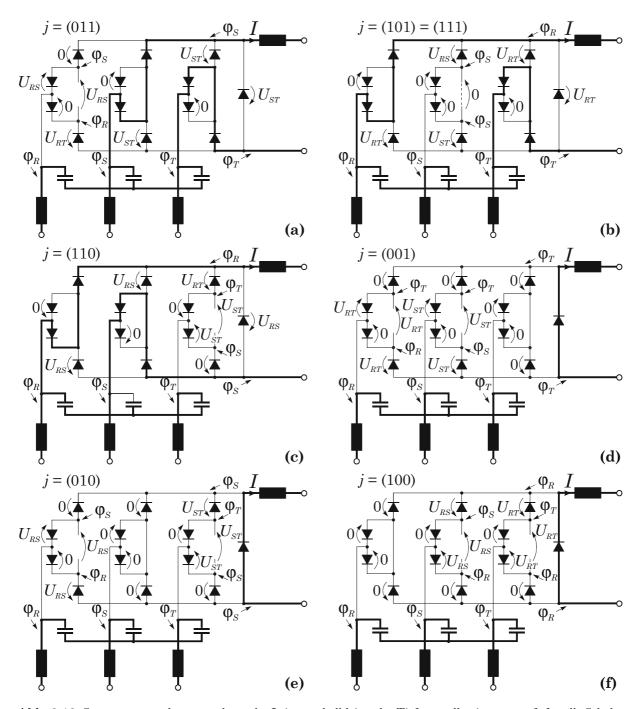

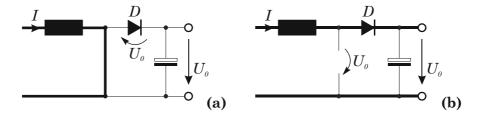

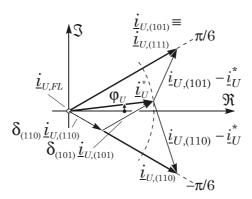

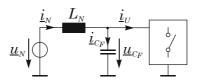

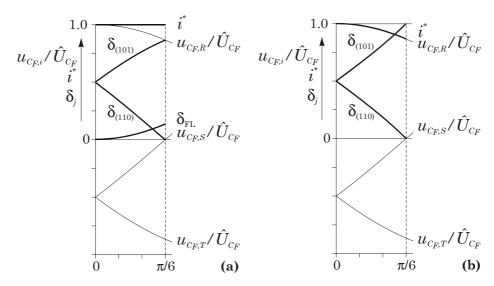

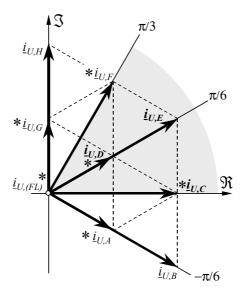

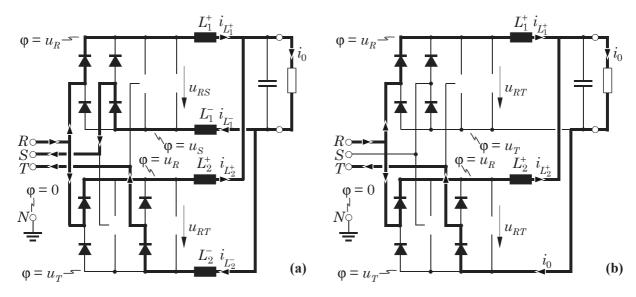

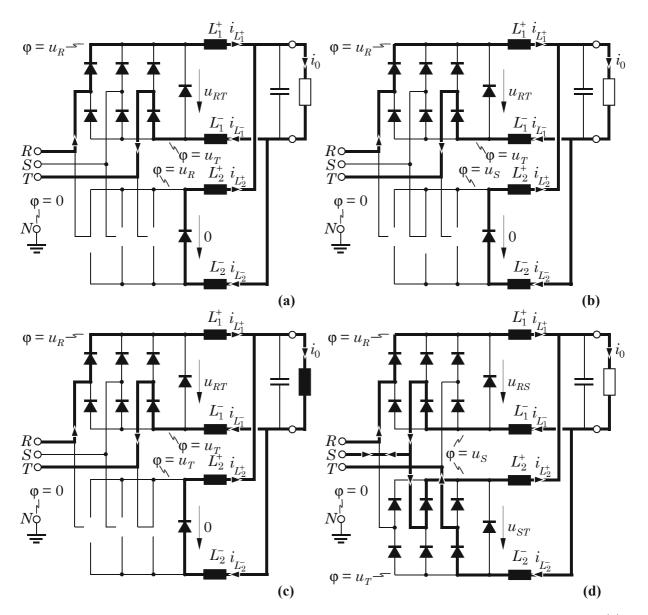

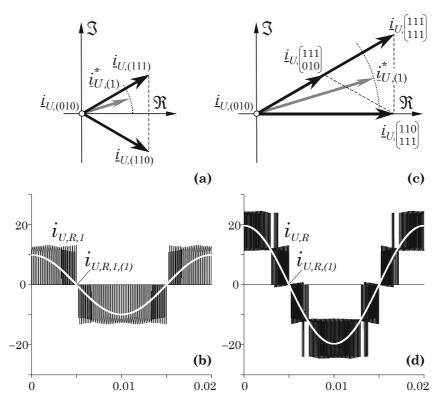

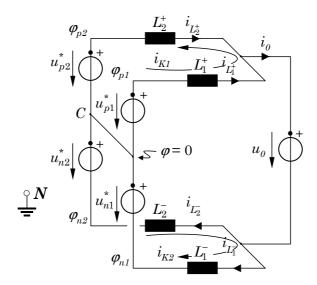

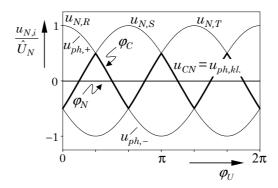

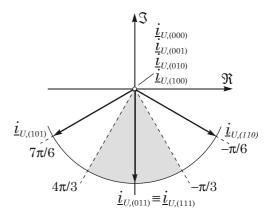

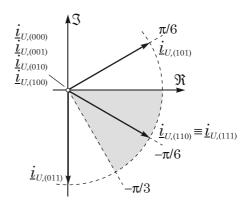

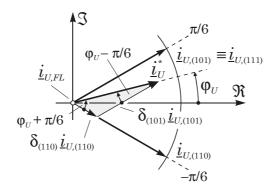

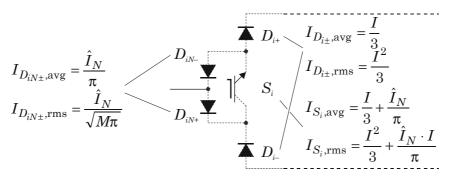

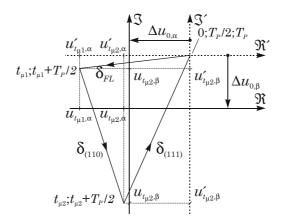

Die theoretische Analyse der Schaltung, die Bestimmung der Stromraumzeiger, die für die Bildung des Eingangsstromes zur Verfügung stehen, sowie die analytische Berechnung der Einschaltdauern und der Bauelementebeanspruchungen sind in **Kapitel 2** gezeigt.

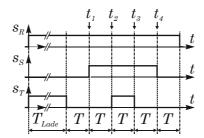

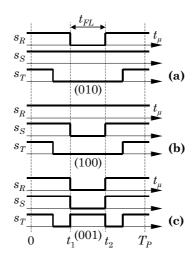

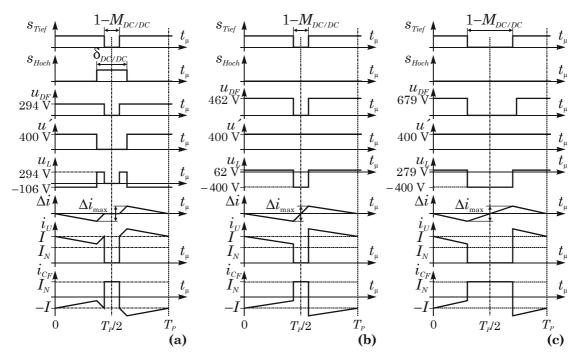

In Kapitel 3 werden verschiedene Modulationsverfahren, d. h. Möglichkeiten zur Anordnung der aktiven Schaltzustände und des Freilaufzustandes der Tiefsetzstellereingangsstufe innerhalb einer Pulshalbperiode, sowie die Wahlmöglichkeit, ob und welcher Leistungstransistor während eines  $\pi/3$ -breiten Netzintervalls im eingeschalteten Zustand verbleiben soll, untersucht und hinsichtlich ihrer Schaltverluste verglichen.

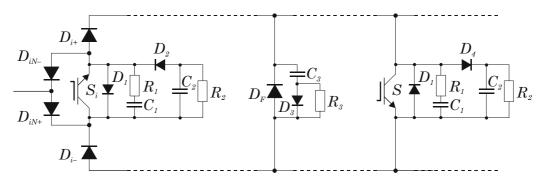

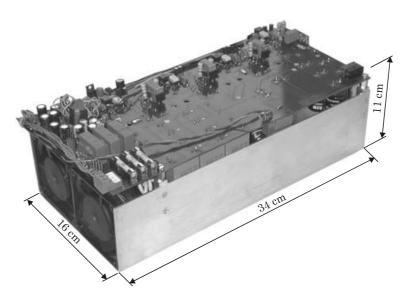

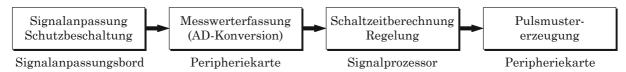

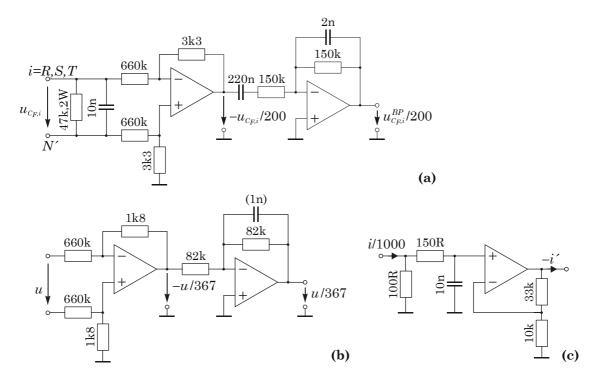

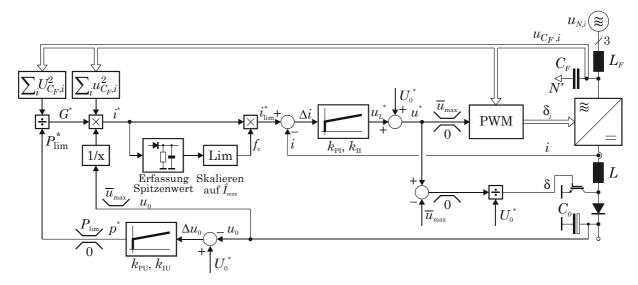

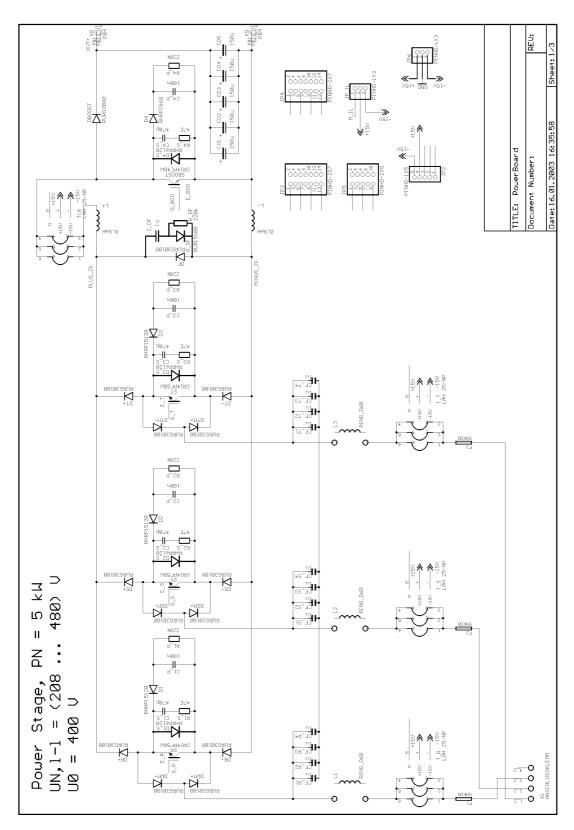

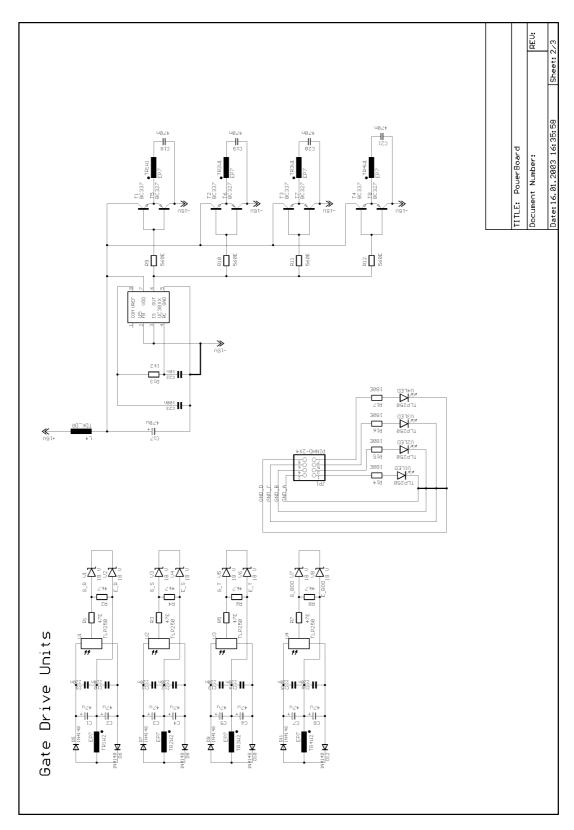

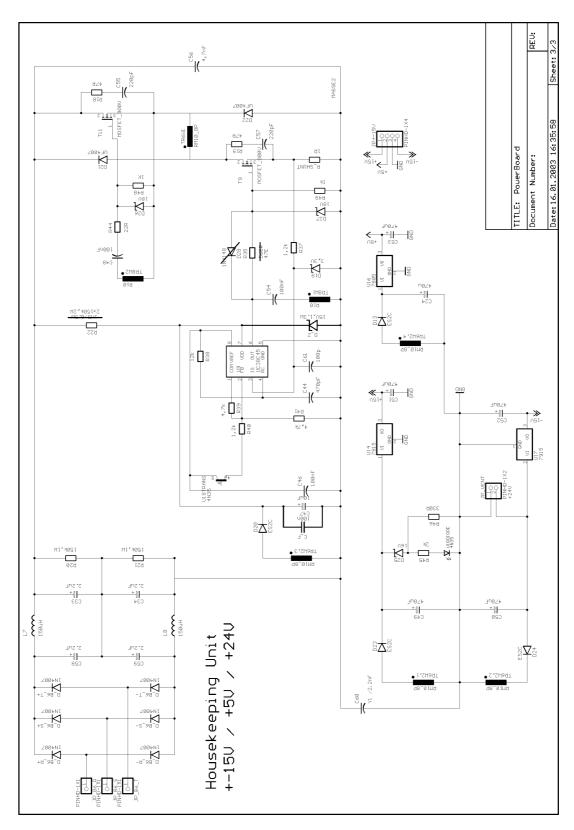

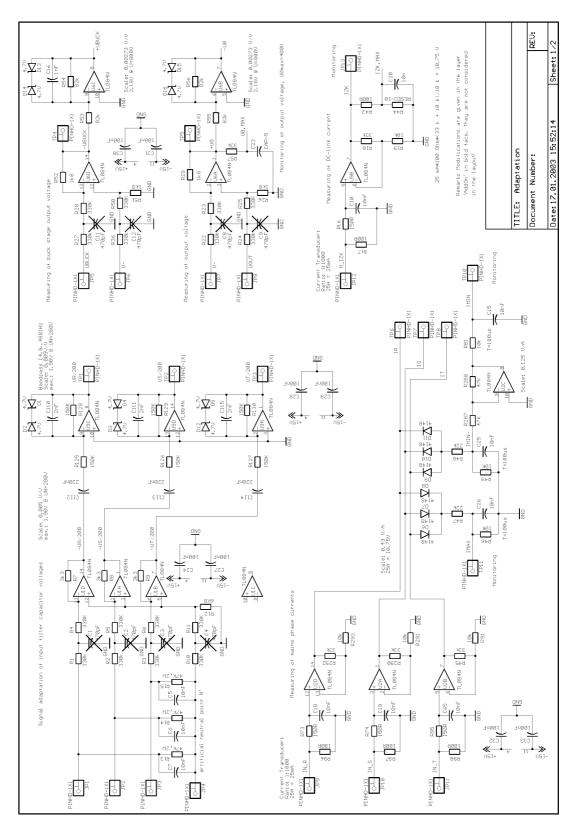

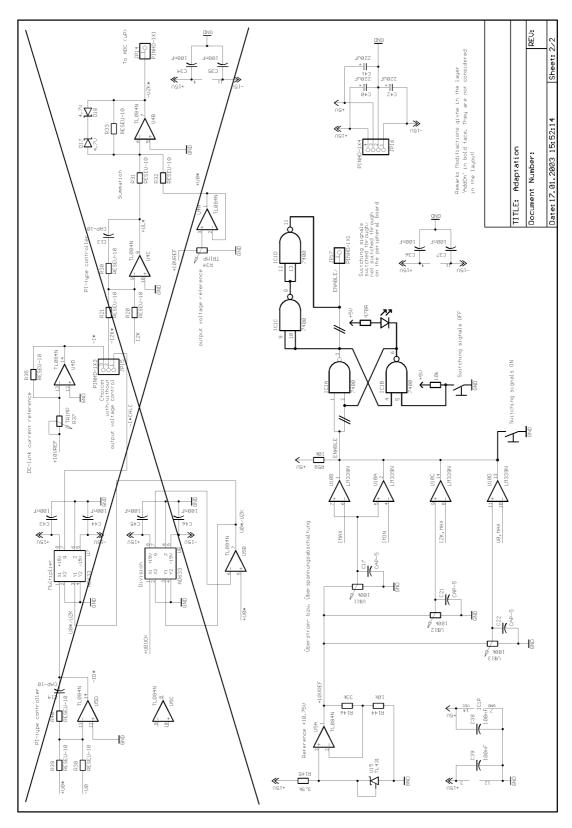

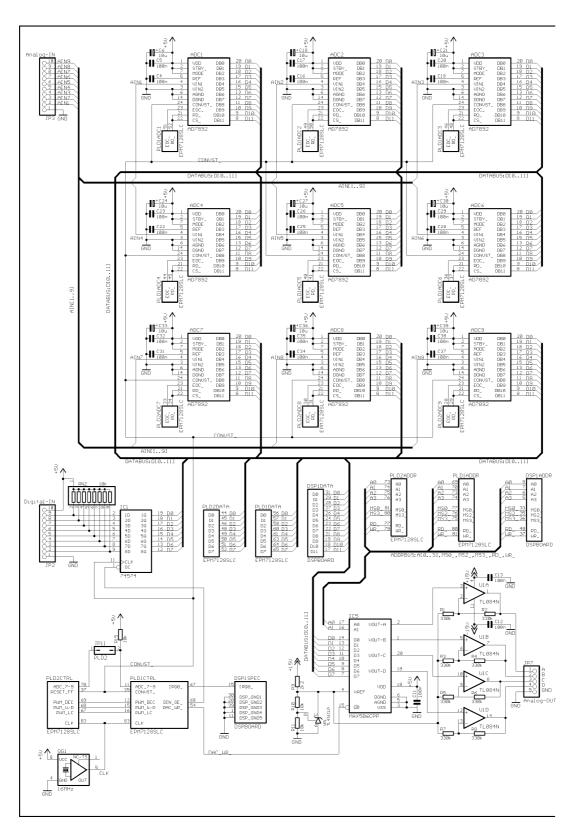

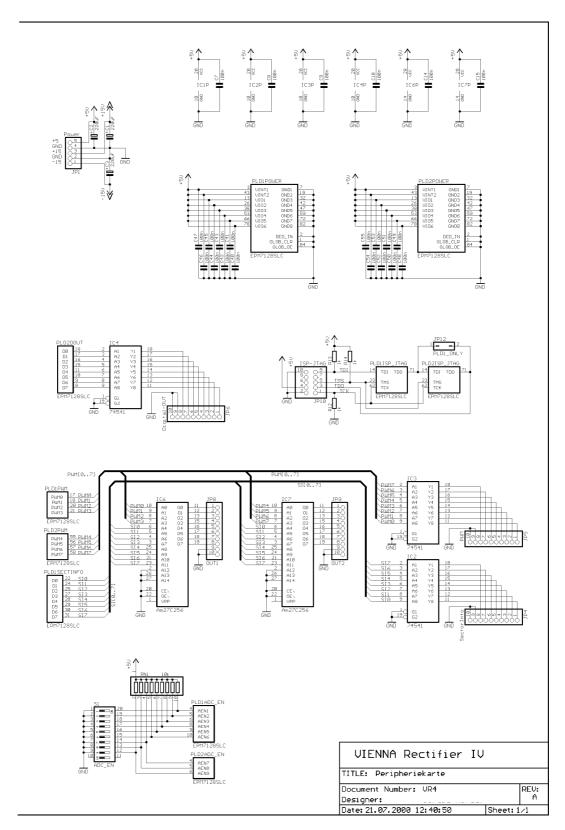

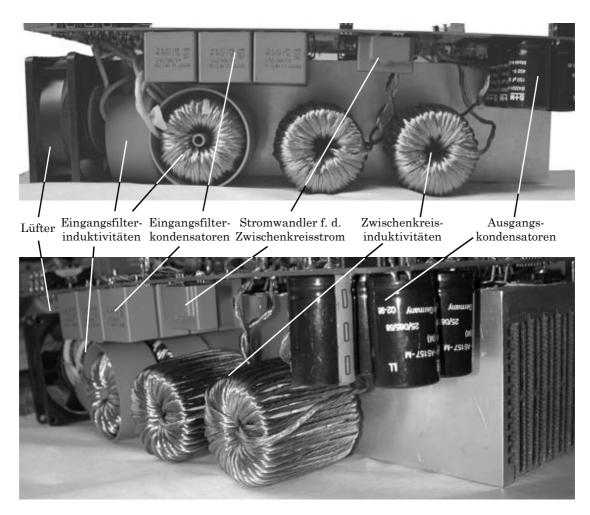

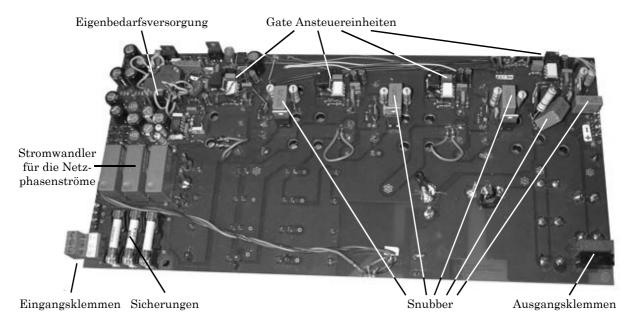

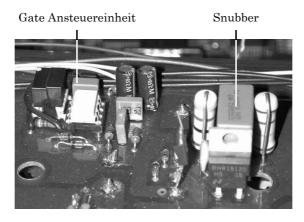

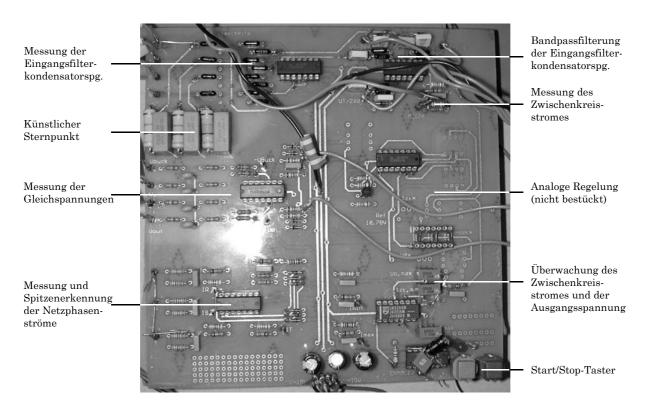

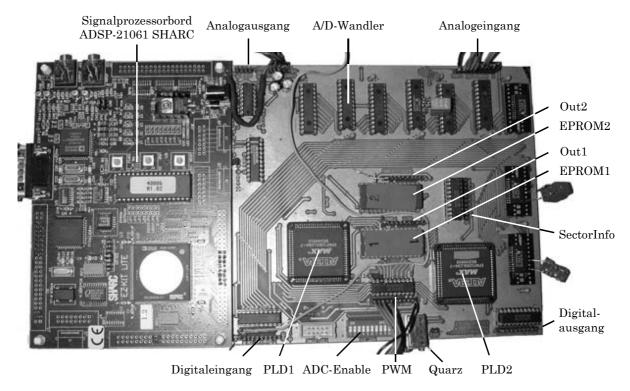

Für 5 kW Ausgangsleistung, einen weiten Eingangsspannungsbereich von 208 V . . . 480 V Außenleiterspannung und 400 V Ausgangsspannung wird in **Kapitel 4** die Dimensionierung eines Leistungsteils vorgenommen und es werden die passenden Leistungshalbleiter und deren Schutzbeschaltung sowie die passiven Bauelemente ausgewählt. Die gesamte Regelung des Gleichrichtersystems soll in einen digitalen Signalprozessor implementiert werden.

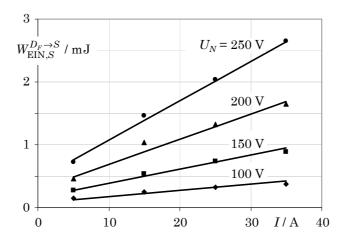

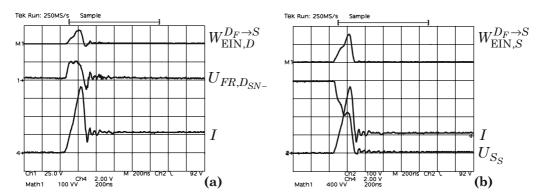

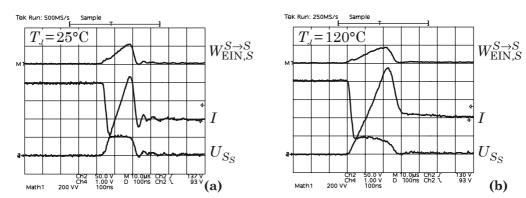

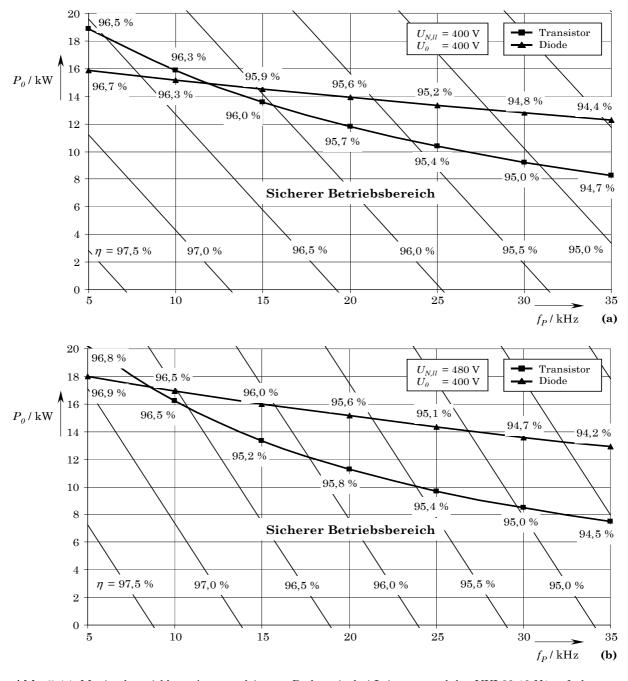

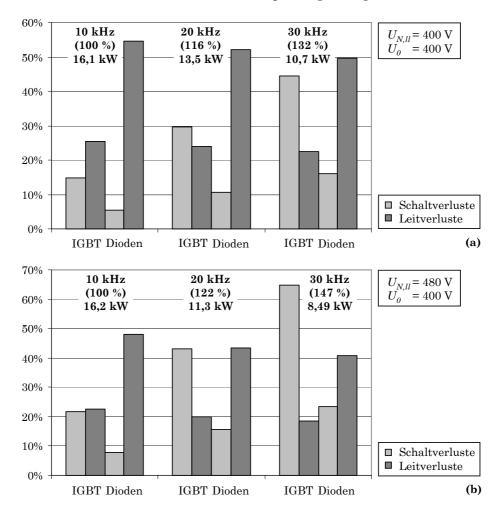

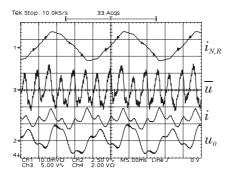

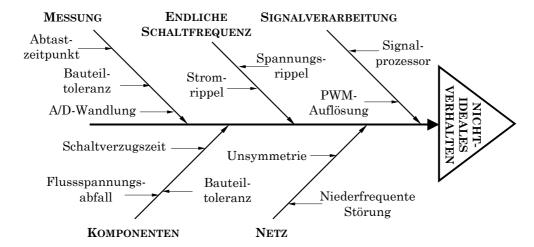

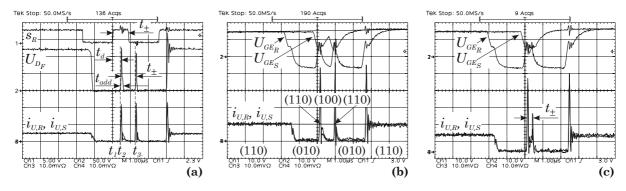

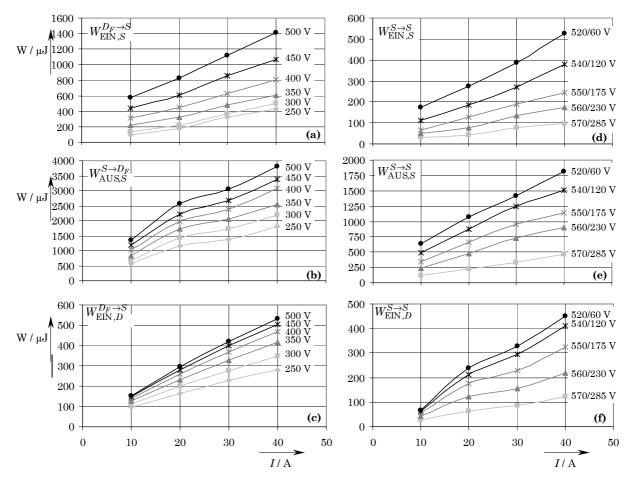

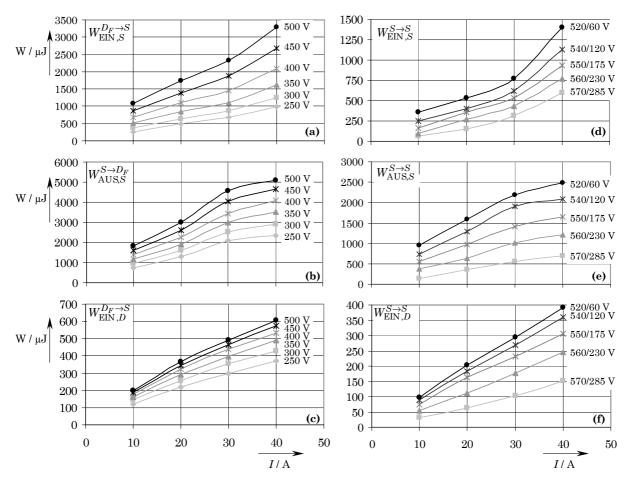

Um die Dimensionierung der Leistungshalbleiter zu kontrollieren, wird in Kapitel 5 eine detaillierte experimentelle Analyse des Schaltverhaltens der Leistungstransistoren und -dioden vorgenommen, womit die Schaltverluste bei allen vorkommenden Schalthandlungen ermittelt und daraus die Gesamtverluste sowie der Wirkungsgrad berechnet werden können. Damit können ein sicherer Betriebsbereich in Abhängigkeit von Schaltfrequenz und Ausgangsleistung und somit die zulässigen Betriebsparameter ermittelt werden. Die selbe experimentelle Analyse und die Ermittlung zulässiger Betriebsparameter wird auch für die Realisierung der Tiefsetzstellereingangsstufe mit von IYXS Semiconductor GmbH gefertigten Modulen VUI 30-12N1, die die Leistungshalbleiter eines Brückenzweiges enthalten, durchgeführt. Weiters sollen auch der Einfluss von Nichtidealitäten auf das Betriebsverhalten des Gleichrichtersystems untersucht und Abhilfemaßnahmen aufgezeigt werden.

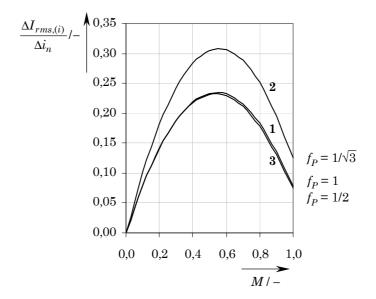

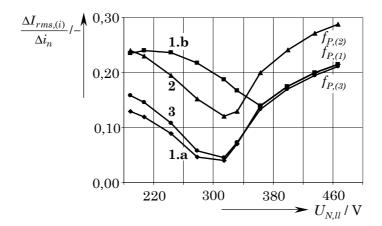

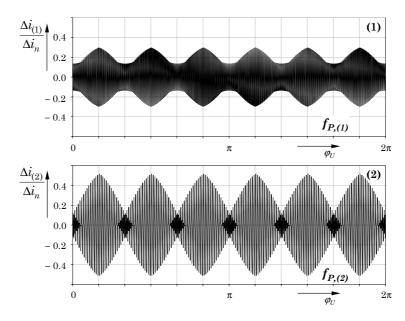

Um die Möglichkeiten zur Reduktion der Größe der Filterkomponenten zu untersuchen, werden die in Kapitel 3 vorgestellten Modulationsverfahren in **Kapitel 6** hinsichtlich der Spannungsbelastung an den eingangsseitigen Filterkondensatoren sowie hinsichtlich des Rippelstromes an der Zwischenkreisinduktivität verglichen.

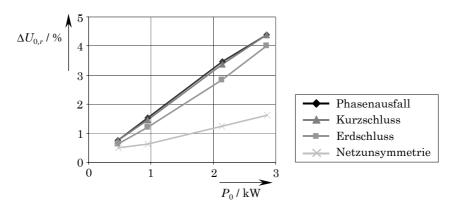

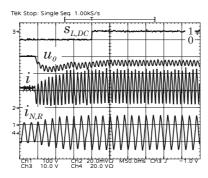

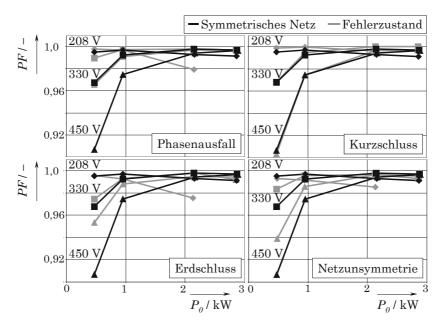

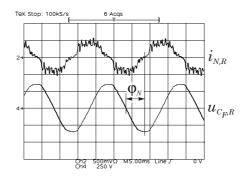

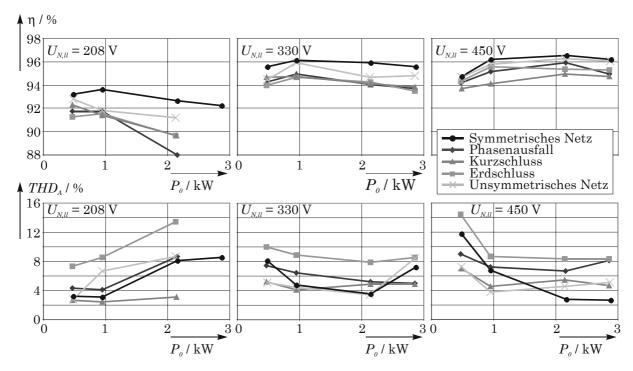

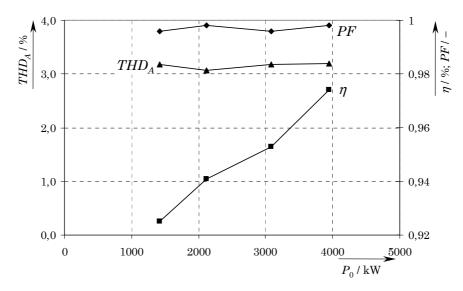

Aufgrund der industriellen Einsetzbarkeit wird an die Regelung des Gleichrichtersystems die Anforderung gestellt, dass ein Betrieb mit ohmschem Netzverhalten auch in unterschiedlichen Netzfehlerzuständen weiterhin möglich ist, wobei das unsymmetrische Netz, der Ausfall einer Phase sowie der Kurzschluss und der Erdschluss bei gleichzeitigem Phasenausfall als Fehlerzustände angenommen werden. Die Regelstruktur wird in Kapitel 7 vorgestellt, digitale Simulationen und experimentelle Analysen bestätigen deren Funktion, und die Messung der charakteristischen Kenngrößen des Gleichrichtersystems wie Leistungsfaktor, Total Harmonic Distortion der Netzphasenströme und Wirkungsgrad zeigen gute Eigenschaften für den Betrieb in einem Fehlerfall sowie im Normalbetrieb.

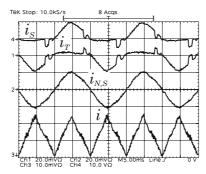

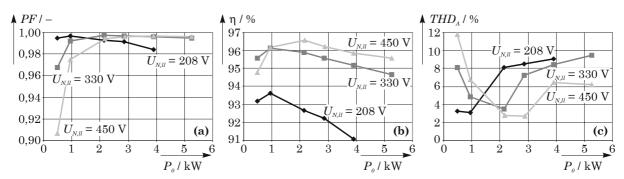

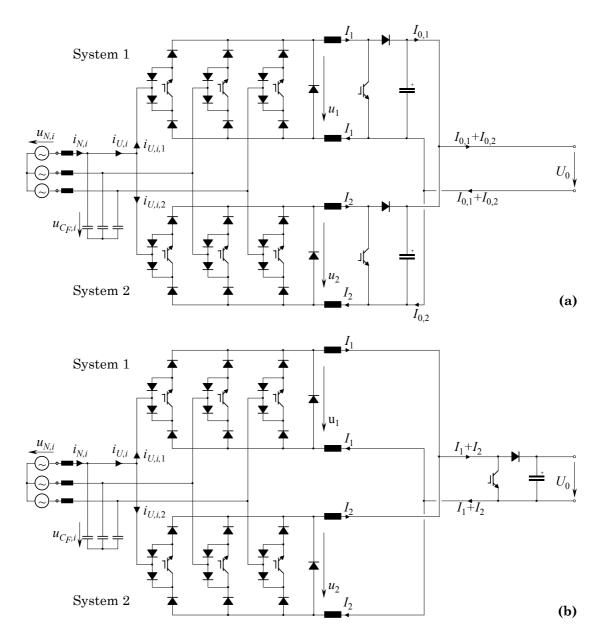

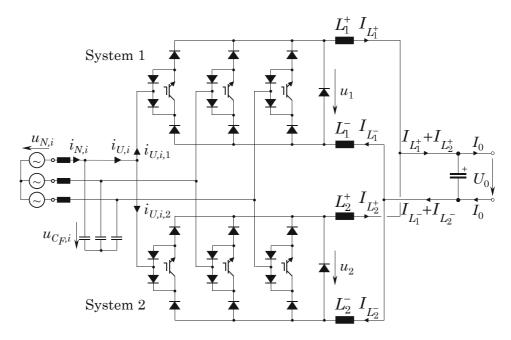

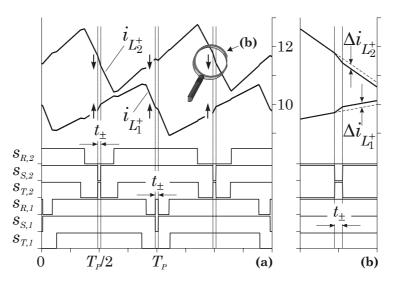

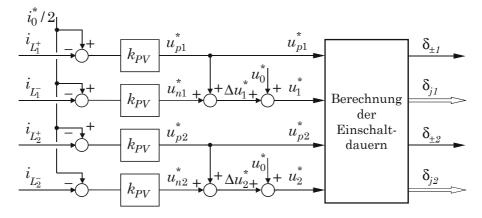

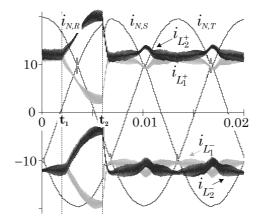

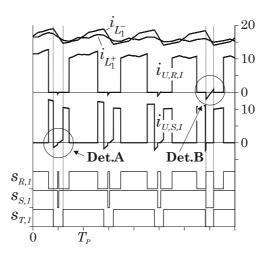

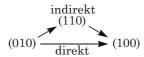

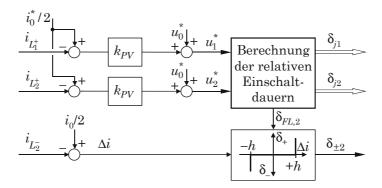

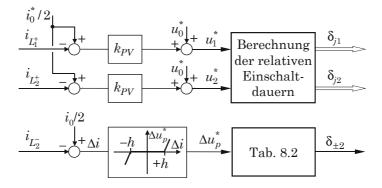

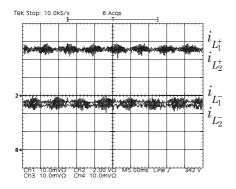

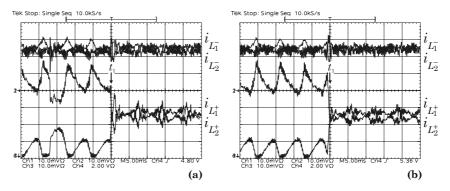

In Kapitel 8 wird die Parallelschaltung von zwei Eingangsstufen des Gleichrichtersystems untersucht, um eine höhere Ausgangsleistung als die mit 5 kW angenommene Nennleistung zu erhalten. Es wird ein Modulationsverfahren entwickelt, das hinsichtlich der Eigenstabilität der Stromaufteilung zwischen den Gleichrichtersystemen sowie hinsichtlich des Stromrippels an den Zwischenkreisinduktivitäten günstige Eigenschaften zeigt und es wird eine einfache Möglichkeit der Symmetrierung des Zwischenkreisstromes vorgestellt. Weiters werden unterschiedliche Regelstrukturen zur Zwischenkreisstromsymmetrierung

| ausgearbeitet und durch experimentelle Analyse eine vorteilhafte Struktur ausgewählt. Auch für den Parallelbetrieb werden die charakteristischen Kenngrößen ermittelt. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                        |

|                                                                                                                                                                        |

|                                                                                                                                                                        |

|                                                                                                                                                                        |

### Abstract

In this thesis a novel three-phase pulse-width-modulated rectifier system with a three-switch buck-type input stage and an integrated DC/DC boost converter output stage with sinusoidal mains phase currents and unity power factor is presented for world-wide applicability, i. e. for a mains voltage range of  $208~\rm V\ldots 480~\rm V$  line-to-line voltage, for an output voltage of  $400~\rm V$  and an output power of  $5~\rm kW$ . As compared to well known topologies like buck converter or boost converter, the novel rectifier system shows the advantage of a higher efficiency for the application in the wide input voltage range, and as compared to the combination of three single-phase buck+boost converters the proposed rectifier systems shows a significantly lower complexity .

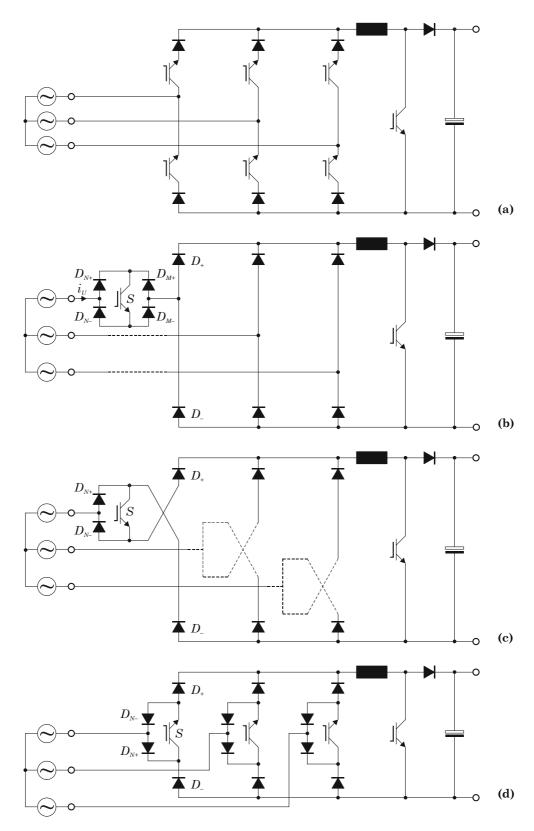

The development of the structure of the rectifier system is given in **Chapter 1**, where the base is the combination of a conventional current source converter with an integrated DC/DC boost converter output stage.

The theoretical analysis of the rectifier system, the determination of the current space vectors which are available for the formation of the input current, and the analytical calculation of the on-times of the power transistors as well as of the current and voltage stress of active and passive components are given in **Chapter 2**.

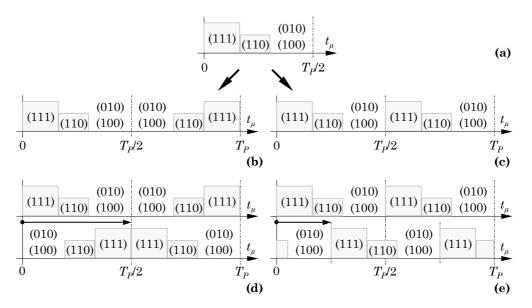

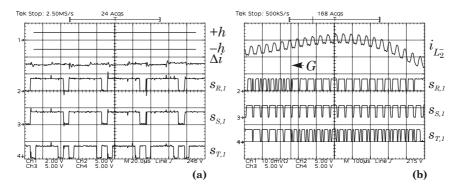

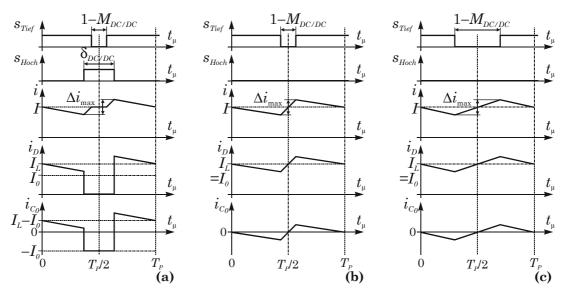

In Chapter 3 different modulation methods, i. e. possibilities for arranging active switching states and the free-wheeling state of the buck input stage within a pulse period, and the possibility, if a power transistor should be kept in the on-state during a  $\pi/3$ -wide interval of the mains period, are investigated and compared concerning their switching losses.

For 5 kW output power, a wide input voltage range of 208 V ... 480 V line-to-line voltage and 400 V output voltage the dimensioning of the power stage is given in **Chapter 4** and power semiconductors, snubber circuits and passive components are chosen. The control of the rectifier system is implemented in a digital signal processor.

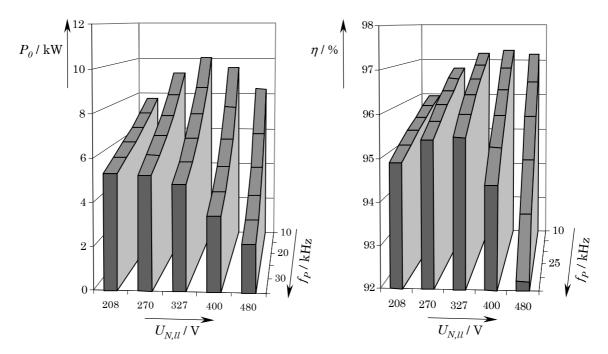

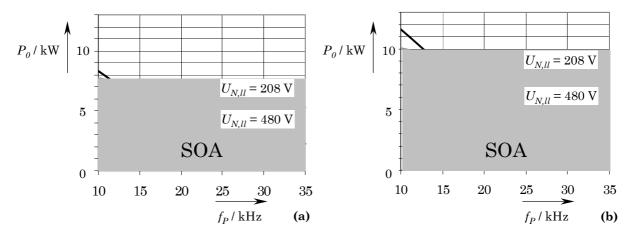

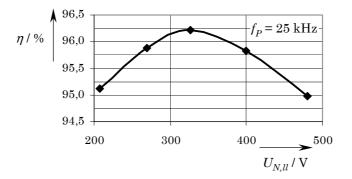

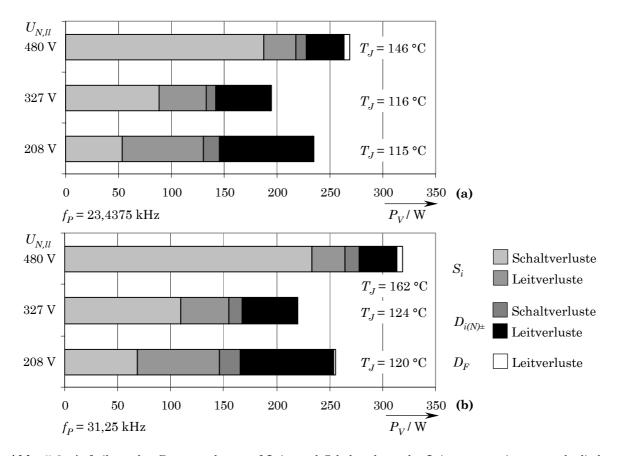

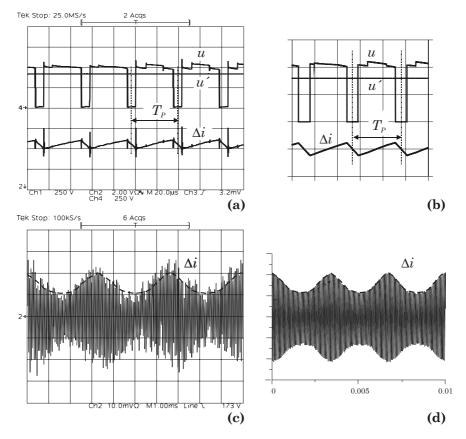

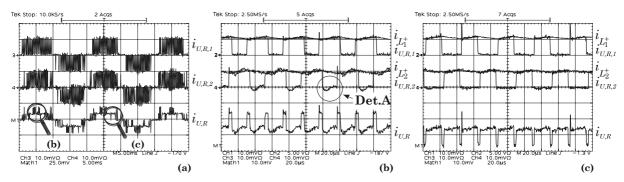

In order to check the dimensioning of the power semiconductors, a detailed experimental analysis of the switching behavior of the power semiconductors is carried out in **Chapter 5**. There, the switching losses of all occurring switching actions are determined and the total power loss as well as the efficiency are calculated. With this the safe operating area in dependency on the switching frequency and the output power and the allowable operating parameters can be given. The same analysis is carried out for the realization of the buck input stage with power modules VUI 30-12N1 from IYXS Semiconductor GmbH which contain the power semiconductors of one bridge leg. Furthermore, the influence of non-idealities on the operating behavior of the rectifier system is investigated and proper pre-control methods or hardware adaptations for minimizing the influences are discussed.

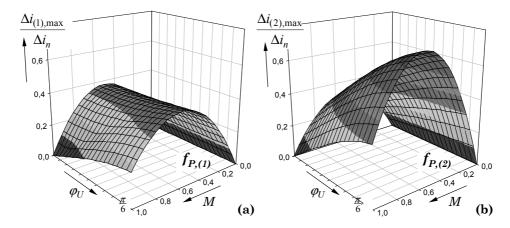

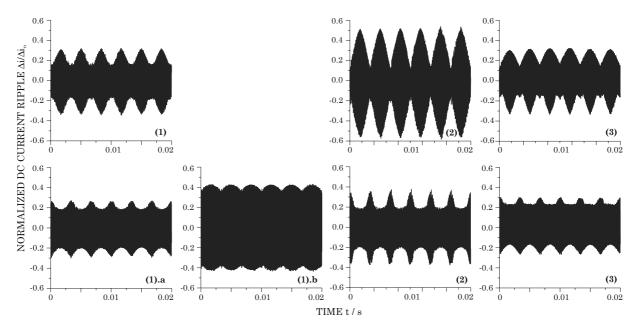

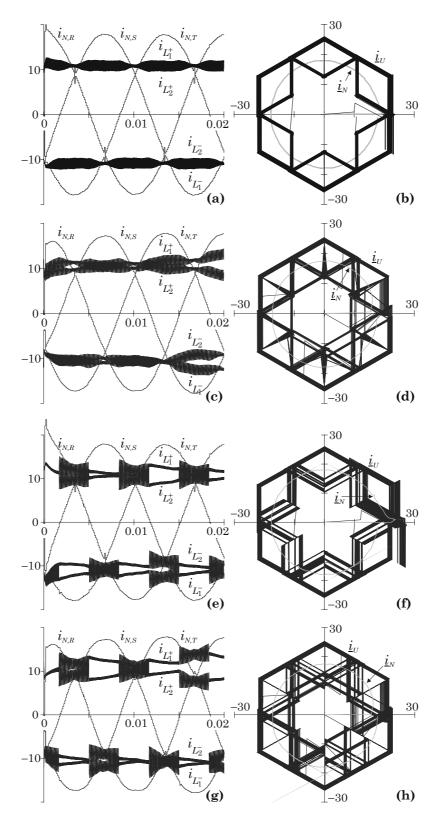

In order to reduce the size of the input filter components, the modulation methods presented in Chapter 3 are compared in **Chapter 6** concerning the input filter capacitor voltage ripple and the buck+boost inductor current ripple.

Due to the industrial application of the rectifier, the system should continue in operation with sinusoidal mains phase currents and unity power factor also in case of a mains failure. The investigated failure conditions are unbalanced mains, the loss of one phase, a short circuit between two phases and an earth fault during the loss of one phase. A proper control structure is presented in **Chapter 7**, digital simulations and experimental results confirm the function of the control, the system characteristics like power factor, total harmonic distortion of the mains phase currents and efficiency show reasonable behavior during normal conditions and during a mains failure.

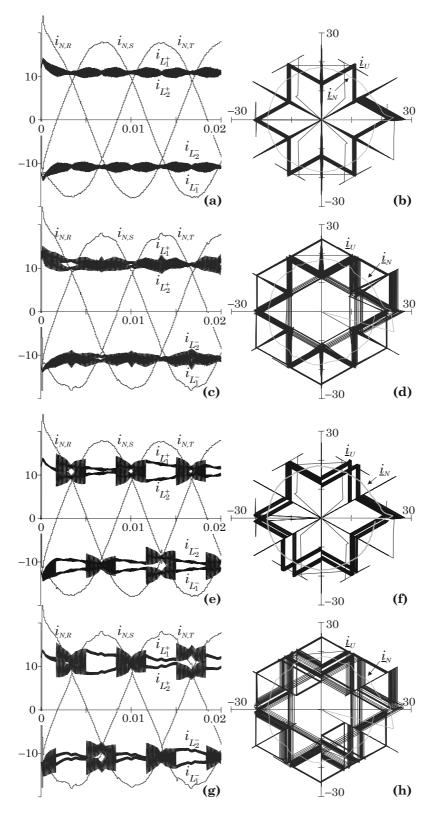

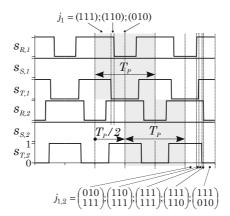

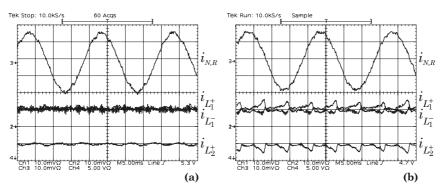

In Chapter 8 the parallel connection of two buck input stages is investigated in order to achieve a higher output power. A modulation method is chosen, which is advantageous concerning the self-stability of the DC-link current partitioning between the rectifier systems and concerning the DC-link current ripple. Furthermore, a simple possibility for the symmetrization of the DC-link currents is given and different control structures for DC-side current balancing are presented and compared by experimental investigations. The systems characteristics are determined for parallel operation, too.

# Inhaltsverzeichnis

| Fo | Formelzeichen und Abkürzungen vi |                                                                          |                 |  |  |  |

|----|----------------------------------|--------------------------------------------------------------------------|-----------------|--|--|--|

| 1  | Ein                              | leitung                                                                  | 1               |  |  |  |

|    | 1.1                              | Schaltungsstrukturen                                                     | 1               |  |  |  |

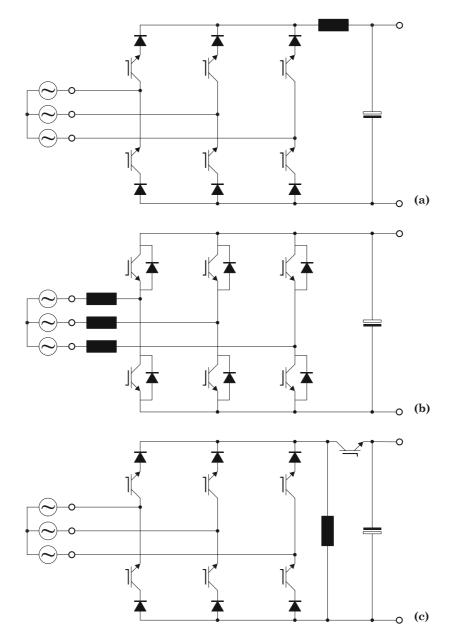

|    |                                  | 1.1.1 Dreiphasiger Tiefsetzsteller                                       | 1               |  |  |  |

|    |                                  | 1.1.2 Dreiphasiger Hochsetzsteller                                       | 2               |  |  |  |

|    |                                  | 1.1.3 Dreiphasiger Tief-Hochsetzsteller                                  | 2               |  |  |  |

|    |                                  |                                                                          | 2               |  |  |  |

|    | 1.0                              |                                                                          | 2               |  |  |  |

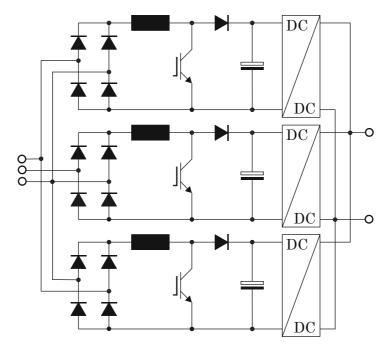

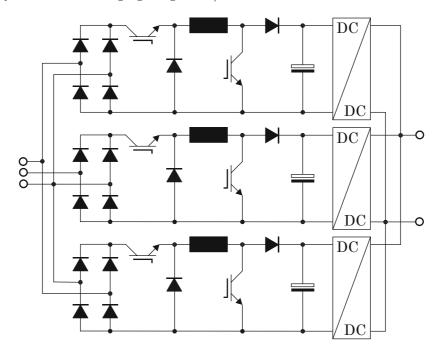

|    | 1.2                              | Entwicklung der Schaltungsstruktur des Dreiphasen/Dreischalter-          | _               |  |  |  |

|    |                                  | Tiefsetzstellers mit integrierter Hochsetzstellerausgangsstufe           | 3               |  |  |  |

| 2  | Gru                              | undlegende theoretische Betrachtungen                                    | 7               |  |  |  |

|    | 2.1                              | Schaltungsstruktur                                                       | 7               |  |  |  |

|    | 2.2                              | Annahmen und Voraussetzungen                                             | 7               |  |  |  |

|    | 2.3                              | Allgemeine Anforderungen                                                 | 9               |  |  |  |

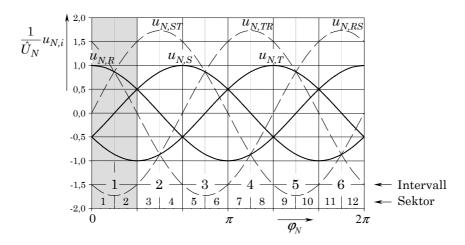

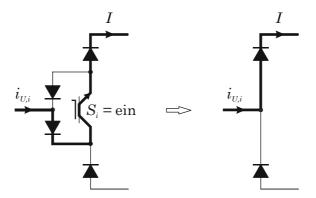

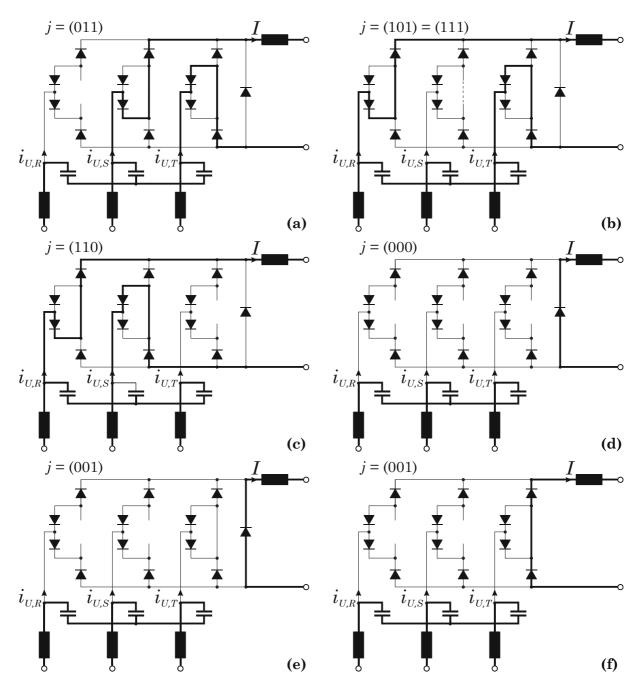

|    | 2.4                              | Leitzustände und Stromraumzeiger der Eingangsstufe                       | 9               |  |  |  |

|    | 2.5                              | Bildung des Eingangsstromes                                              | 11              |  |  |  |

|    | 2.6                              |                                                                          | 14              |  |  |  |

|    |                                  | • •                                                                      | 15              |  |  |  |

|    |                                  | 5 5                                                                      | 17              |  |  |  |

|    |                                  | 9 0                                                                      | 18              |  |  |  |

|    |                                  |                                                                          | 18              |  |  |  |

|    |                                  |                                                                          | 18              |  |  |  |

|    |                                  |                                                                          | _               |  |  |  |

|    |                                  | 1 0 1 0                                                                  | 18              |  |  |  |

|    |                                  | 9 9                                                                      | 18              |  |  |  |

|    |                                  | 2.6.4.B Hochsetzstellerausgangsstufe                                     | 19              |  |  |  |

| 3  | Aus                              |                                                                          | 21              |  |  |  |

|    | 3.1                              | Mögliche Schaltzustandssequenzen                                         | 21              |  |  |  |

|    | 3.2                              | Analyse der Schaltverluste der unterschiedlichen Schaltzustandssequenzen | 22              |  |  |  |

| 4  | Pra                              | ktische Realisierung                                                     | 24              |  |  |  |

| _  | 4.1                              |                                                                          | $\frac{1}{24}$  |  |  |  |

|    | 7.1                              |                                                                          | $\frac{24}{24}$ |  |  |  |

|    |                                  |                                                                          | $\frac{24}{25}$ |  |  |  |

|    |                                  |                                                                          | $\frac{25}{26}$ |  |  |  |

|    |                                  |                                                                          | _               |  |  |  |

|    |                                  |                                                                          | 27              |  |  |  |

|    |                                  |                                                                          | 27              |  |  |  |

|    |                                  |                                                                          | 29              |  |  |  |

|    |                                  | 8 8                                                                      | 29              |  |  |  |

|    | 4.2                              |                                                                          | 30              |  |  |  |

|    | 4.3                              | <u> </u>                                                                 | 30              |  |  |  |

|    |                                  |                                                                          | 31              |  |  |  |

|    |                                  | 4 3 2 Realisierung der Peripheriekarte                                   | 21              |  |  |  |

*INHALTSVERZEICHNIS* ii

|   |     | 4.3.3         | Steuerungsablauf                                                                 | 32 |

|---|-----|---------------|----------------------------------------------------------------------------------|----|

| 5 | Exp | erime         | ntelle Analyse des Leistungsteils                                                | 35 |

|   | 5.1 | Schalt        | verlustmessung für diskreten Aufbau                                              | 35 |

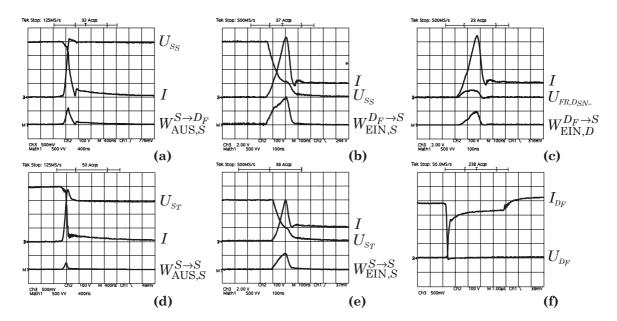

|   |     | 5.1.1         | Experimentelle Ermittlung der Schaltverluste                                     | 35 |

|   |     | 5.1.2         | Auswertung der experimentellen Ergebnisse                                        | 36 |

|   |     | 5.1.3         | Berechnung der Gesamtverluste                                                    | 38 |

|   |     | 0.1.0         | 5.1.3.A Berechnung der Leitverluste                                              | 38 |

|   |     |               | 5.1.3.B Detaillierte Betrachtung der Schalthandlungen und Berechnung der Schalt- | 00 |

|   |     |               | verluste                                                                         | 39 |

|   |     |               | 5.1.3.C Berechnung der gesamten mittleren Verlustleistung                        | 41 |

|   |     | 5.1.4         | Ermittlung der zulässigen Betriebsparameter                                      | 41 |

|   |     | 5.1.4 $5.1.5$ | Aufteilung der Gesamtverluste auf Leit- und Schaltverluste                       | 43 |

|   | F 0 |               |                                                                                  |    |

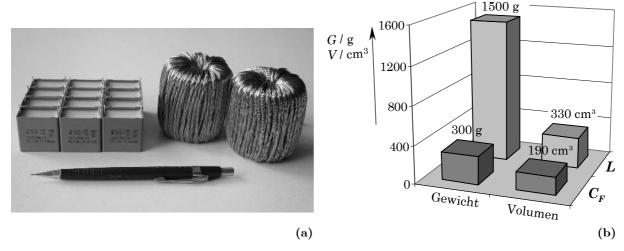

|   | 5.2 |               | cklung eines Leistungsmoduls                                                     | 44 |

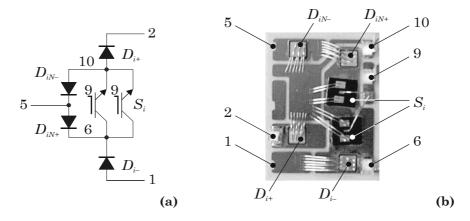

|   |     | 5.2.1         | Interne Struktur des Leistungsmoduls                                             | 45 |

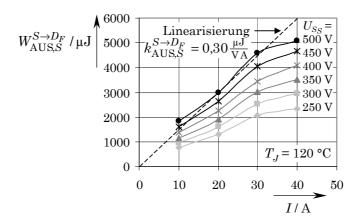

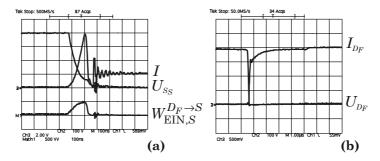

|   |     | 5.2.2         | Experimentelle Ermittlung der Schaltverluste                                     | 45 |

|   |     | 5.2.3         | Ermittlung der zulässigen Betriebsparameter                                      | 48 |

|   |     | 5.2.4         | Wirkungsgrad und Verlustaufteilung                                               | 49 |

|   |     | 5.2.5         | Beurteilung des Leistungsmoduls VUI 30-12 N1 und Verbesserungsvorschläge $\ .$   | 51 |

|   | 5.3 |               | ss von Nichtidealitäten auf das Betriebsverhalten                                | 52 |

|   |     | 5.3.1         | Analyse der Ursachen für nichtideales Betriebsverhalten                          | 53 |

|   |     |               | 5.3.1.A Flussspannungsabfälle der Leistungshalbleiter                            | 53 |

|   |     |               | 5.3.1.B Gestörte Netzspannung                                                    | 54 |

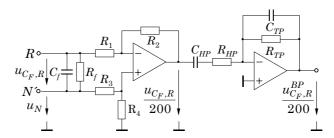

|   |     |               | 5.3.1.C Eingangsspannungsmessung                                                 | 56 |

|   |     |               | 5.3.1.D Signalverarbeitung                                                       | 56 |

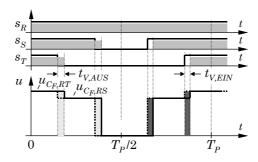

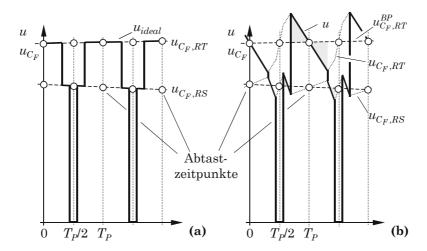

|   |     |               | 5.3.1.E Schaltverzug                                                             | 57 |

|   |     |               | 5.3.1.F Signalabtastung                                                          | 58 |

|   |     |               | 5.3.1.G Endliche Schaltfrequenz                                                  | 58 |

|   |     |               | 5.3.1.H Kommutierung des Zwischenkreisstromes                                    | 59 |

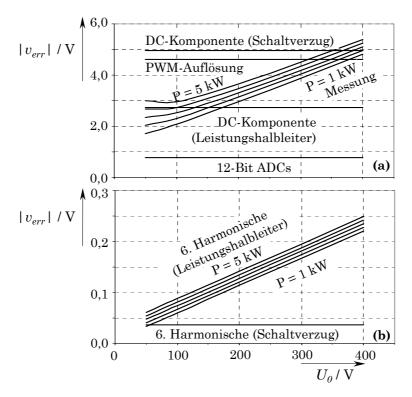

|   |     | 5.3.2         | Größe der Störung in der Tiefsetzstellerausgangsspannung                         | 59 |

|   |     | 5.3.3         | Bewertung der unterschiedlichen Nichtidealitäten und Abhilfemaßnahmen            | 59 |

|   |     |               | 5.3.3.A Vernachlässigbare Einflüsse                                              | 61 |

|   |     |               | 5.3.3.B Flussspannungsabfälle                                                    | 61 |

|   |     |               | 5.3.3.C Zeitauflösung der PWM-Ausgangssignale                                    | 61 |

|   |     |               | 5.3.3.D Schaltverzug                                                             | 61 |

|   |     | 5.3.4         | Schlussbemerkung                                                                 | 61 |

|   |     | 0.0.4         | Demassbehierkung                                                                 | ΟI |

| 6 | Ver | gleich        | und Bewertung der Modulationsverfahren                                           | 62 |

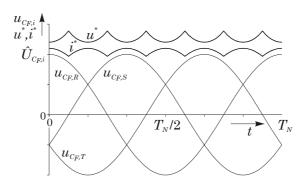

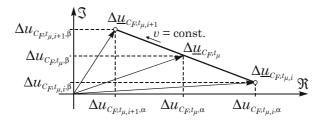

| _ | 6.1 |               | ungsrippel an den eingangsseitigen Filterkondensatoren                           | 62 |

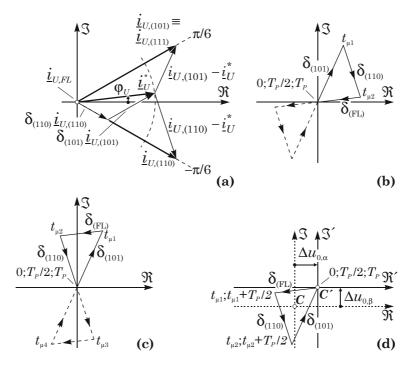

|   | 0.1 | 6.1.1         | Analytisch geschlossene Berechnung                                               | 63 |

|   |     | 6.1.2         | Trajektorien des Spannungsraumzeigers                                            | 64 |

|   |     | 0.1.2         | 6.1.2.A Trajektorie für Modulationsverfahren 1                                   | 65 |

|   |     |               | 6.1.2.B Trajektorie für Modulationsverfahren 2                                   | 65 |

|   |     |               | ·                                                                                | 66 |

|   |     | 619           | y .                                                                              |    |

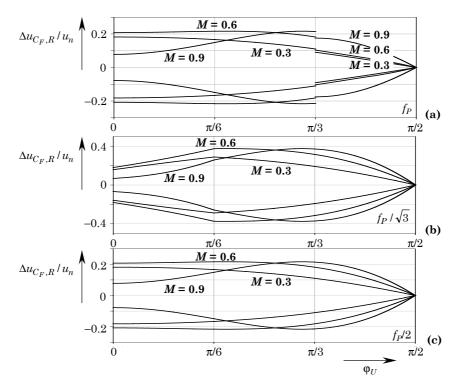

|   |     | 6.1.3         | Effektivwert des Spannungsrippels                                                | 67 |

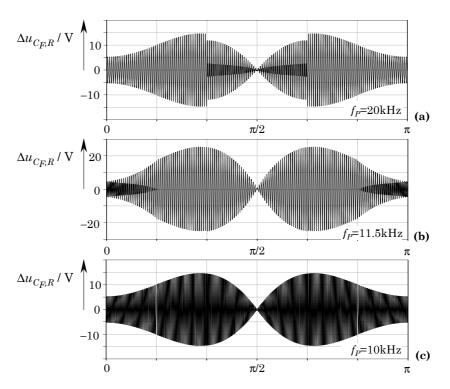

|   |     | 6.1.4         | Zeitverlauf und Einhüllende des Spannungsrippels                                 | 68 |

|   | 0.2 | 6.1.5         | Vergleich der unterschiedlichen Modulationsverfahren                             | 68 |

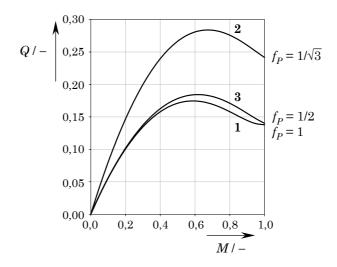

|   | 6.2 |               | rippel an der Zwischenkreisinduktivität                                          | 70 |

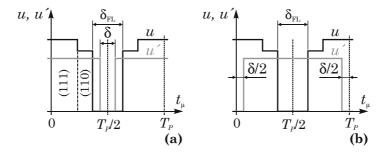

|   |     | 6.2.1         | Modulation der Hochsetzstellerausgangsstufe                                      | 70 |

|   |     | 6.2.2         | Analytische Berechnung des Zwischenkreisstromrippels                             | 71 |

|   |     | 6.2.3         | Zeitverlauf und Einhüllende des Zwischenkreisstromrippels                        | 73 |

|   | 6.3 | Vergle        | eich der unterschiedlichen Modulationsverfahren                                  | 76 |

*INHALTSVERZEICHNIS* iii

| 7                             | Regelung des Gleichrichtersystems |                                                                                                                                                                                                                                                                                                 |                                                      |  |  |  |

|-------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|

| 7.1 Theoretische Überlegungen |                                   |                                                                                                                                                                                                                                                                                                 |                                                      |  |  |  |

|                               |                                   | 7.1.1 Grundlegendes                                                                                                                                                                                                                                                                             | 78                                                   |  |  |  |

|                               |                                   | 7.1.2 Berechnung der Einschaltdauern und des Zwischenkreisstromsollwerts                                                                                                                                                                                                                        | 80                                                   |  |  |  |

|                               |                                   | 7.1.3 Berechnung der Sollwerte                                                                                                                                                                                                                                                                  | 81                                                   |  |  |  |

|                               |                                   | 7.1.3.A Deaktivierte Hochsetzstellerausgangsstufe                                                                                                                                                                                                                                               | 81                                                   |  |  |  |

|                               |                                   | 7.1.3.B Aktive Hochsetzstellerausgangsstufe                                                                                                                                                                                                                                                     | 82                                                   |  |  |  |

|                               | 7.2                               | Entwurf einer Regelstruktur für die Beherrschung von Fehlerfällen                                                                                                                                                                                                                               | 83                                                   |  |  |  |

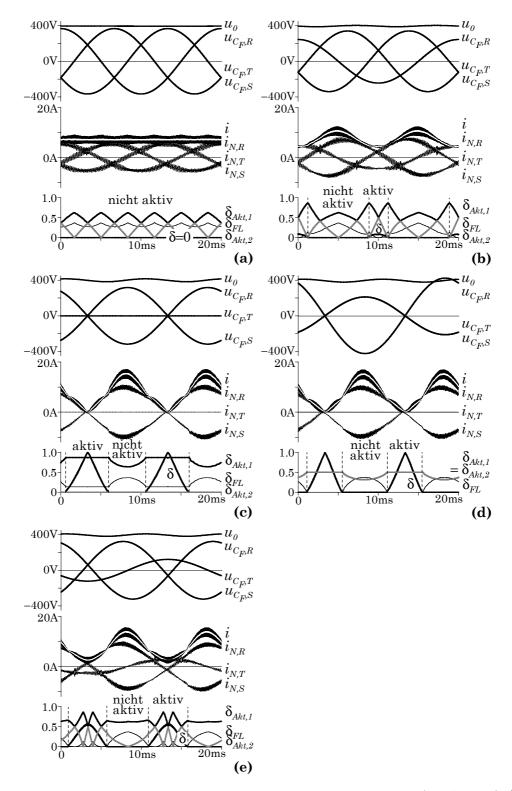

|                               | 7.3                               | Simulationsergebnisse                                                                                                                                                                                                                                                                           | 86                                                   |  |  |  |

|                               |                                   | 7.3.1 Symmetrische Netzspannungen                                                                                                                                                                                                                                                               | 86                                                   |  |  |  |

|                               |                                   | 7.3.2 Unsymmetrische Netzspannungen                                                                                                                                                                                                                                                             | 87                                                   |  |  |  |

|                               |                                   | 7.3.3 Phasenausfall                                                                                                                                                                                                                                                                             | 87                                                   |  |  |  |

|                               |                                   | 7.3.4 Kurzschluss bei Phasenausfall                                                                                                                                                                                                                                                             | 87                                                   |  |  |  |

|                               |                                   | 7.3.5 Erdschluss bei Phasenausfall                                                                                                                                                                                                                                                              | 87                                                   |  |  |  |

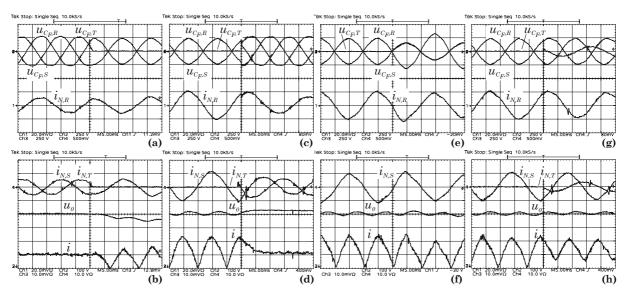

|                               | 7.4                               | Experimentelle Analyse der Regelung                                                                                                                                                                                                                                                             | 89                                                   |  |  |  |

|                               |                                   | 7.4.1 Verhalten im unsymmetrischen Netz                                                                                                                                                                                                                                                         | 89                                                   |  |  |  |

|                               |                                   | 7.4.1.A Übergang zwischen unterschiedlichen Netzzuständen                                                                                                                                                                                                                                       | 89                                                   |  |  |  |

|                               |                                   | 7.4.1.B Verhalten der Ausgangsspannung                                                                                                                                                                                                                                                          | 90                                                   |  |  |  |

|                               |                                   | 7.4.1.C Limitierung des Zwischenkreisstromes                                                                                                                                                                                                                                                    | 91                                                   |  |  |  |

|                               |                                   | 7.4.1.D Aufteilung der Gleichrichtereingangsströme bei Kurzschluss zweier Pha-                                                                                                                                                                                                                  | 91                                                   |  |  |  |

|                               |                                   | sen und gleichzeitigem Phasenausfall                                                                                                                                                                                                                                                            | 92                                                   |  |  |  |

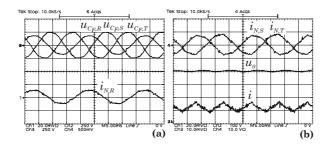

|                               |                                   | 7.4.2 Charakteristische Kenngrößen                                                                                                                                                                                                                                                              | 92                                                   |  |  |  |

|                               |                                   | 7.4.2.A Leistungsfaktor                                                                                                                                                                                                                                                                         | 93                                                   |  |  |  |

|                               |                                   | 7.4.2.B Wirkungsgrad                                                                                                                                                                                                                                                                            | 93<br>93                                             |  |  |  |

|                               |                                   | 7.4.2.C Total Harmonic Distortion der Netzphasenströme                                                                                                                                                                                                                                          | 93<br>94                                             |  |  |  |

|                               |                                   | 7.4.2.D Kenngrößen im Normalbetrieb                                                                                                                                                                                                                                                             | 94<br>95                                             |  |  |  |

|                               | 75                                | Bewertung des Regelkonzepts und mögliche Verbesserungen                                                                                                                                                                                                                                         | 95<br>95                                             |  |  |  |

|                               | 7.5                               | Dewertung des Regelkonzepts und mognene verbesserungen                                                                                                                                                                                                                                          | 90                                                   |  |  |  |

| 8                             | Par                               | rallelschaltung von zwei Gleichrichtersystemen                                                                                                                                                                                                                                                  | 97                                                   |  |  |  |

| _                             | 8.1                               | Theoretische Überlegungen                                                                                                                                                                                                                                                                       |                                                      |  |  |  |

|                               | 0.1                               | 8.1.1 Raumzeigermodulation                                                                                                                                                                                                                                                                      |                                                      |  |  |  |

|                               |                                   | 8.1.2 Einfluss der Schaltzustände auf die Stromänderung                                                                                                                                                                                                                                         |                                                      |  |  |  |

|                               |                                   | 8.1.3 Entwicklung eines Modulationsverfahrens                                                                                                                                                                                                                                                   |                                                      |  |  |  |

|                               |                                   | 8.1.4 Symmetrierung des Zwischenkreisstromes                                                                                                                                                                                                                                                    |                                                      |  |  |  |

|                               |                                   | 8.1.4.A Kreisströme und Strom-Nullsystem                                                                                                                                                                                                                                                        |                                                      |  |  |  |

|                               |                                   | 8.1.4.B Symmetrierung durch unterschiedliche Freilaufzustände                                                                                                                                                                                                                                   |                                                      |  |  |  |

|                               | 8.2                               | Regelung zur Zwischenkreisstrom-Symmetrierung                                                                                                                                                                                                                                                   |                                                      |  |  |  |

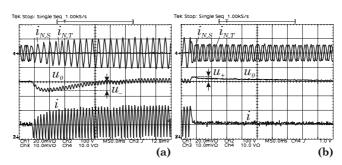

|                               | 0.2                               | 8.2.1 Simulationsergebnisse                                                                                                                                                                                                                                                                     |                                                      |  |  |  |

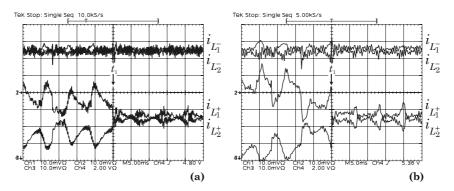

|                               |                                   |                                                                                                                                                                                                                                                                                                 | 114                                                  |  |  |  |

|                               |                                   | •                                                                                                                                                                                                                                                                                               | 116                                                  |  |  |  |

|                               |                                   | <u> </u>                                                                                                                                                                                                                                                                                        | $110 \\ 117$                                         |  |  |  |

|                               |                                   |                                                                                                                                                                                                                                                                                                 | $\frac{117}{117}$                                    |  |  |  |

|                               |                                   |                                                                                                                                                                                                                                                                                                 | 117                                                  |  |  |  |

|                               | 0.9                               |                                                                                                                                                                                                                                                                                                 | 119                                                  |  |  |  |

|                               | 8.3                               | 0                                                                                                                                                                                                                                                                                               | 119                                                  |  |  |  |

|                               |                                   | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                           |                                                      |  |  |  |

|                               |                                   |                                                                                                                                                                                                                                                                                                 | 100                                                  |  |  |  |

|                               | 0.4                               | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                           | 120                                                  |  |  |  |

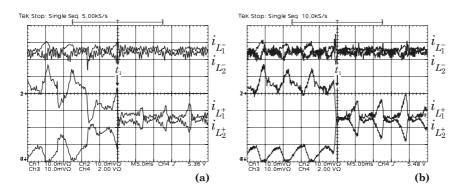

|                               | 8.4                               | Experimentelle Analyse der Regelstrukturen                                                                                                                                                                                                                                                      | 121                                                  |  |  |  |

|                               | 8.4                               | Experimentelle Analyse der Regelstrukturen                                                                                                                                                                                                                                                      | 121<br>121                                           |  |  |  |

|                               | 8.4                               | Experimentelle Analyse der Regelstrukturen                                                                                                                                                                                                                                                      | 121<br>121<br>121                                    |  |  |  |

|                               | 8.4                               | Experimentelle Analyse der Regelstrukturen                                                                                                                                                                                                                                                      | 121<br>121<br>121<br>123                             |  |  |  |

|                               | 8.4                               | Experimentelle Analyse der Regelstrukturen                                                                                                                                                                                                                                                      | 121<br>121<br>121<br>123<br>123                      |  |  |  |

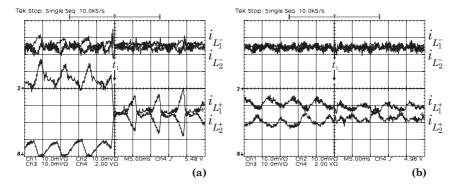

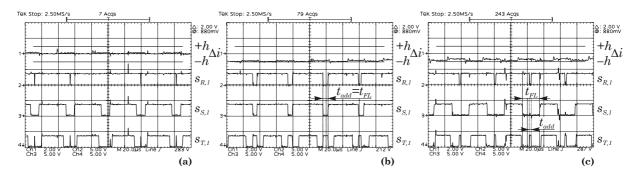

|                               | 8.4                               | Experimentelle Analyse der Regelstrukturen  8.4.1 Verhalten ohne symmetrierende Regelung  8.4.2 Vergleich der beiden Regelstrukturen  8.4.3 Einfluss der Position des Störwiderstandes  8.4.4 Details des Systemverhaltens  8.4.4.A Schaltzustandsfunktionen                                    | 121<br>121<br>121<br>123<br>123<br>123               |  |  |  |

|                               | 8.4                               | Experimentelle Analyse der Regelstrukturen  8.4.1 Verhalten ohne symmetrierende Regelung  8.4.2 Vergleich der beiden Regelstrukturen  8.4.3 Einfluss der Position des Störwiderstandes  8.4.4 Details des Systemverhaltens  8.4.4.A Schaltzustandsfunktionen  8.4.4.B Grenzen des Regelkonzepts | 121<br>121<br>121<br>123<br>123<br>123<br>124        |  |  |  |

|                               | 8.4                               | Experimentelle Analyse der Regelstrukturen  8.4.1 Verhalten ohne symmetrierende Regelung  8.4.2 Vergleich der beiden Regelstrukturen  8.4.3 Einfluss der Position des Störwiderstandes  8.4.4 Details des Systemverhaltens  8.4.4.A Schaltzustandsfunktionen  8.4.4.B Grenzen des Regelkonzepts | 121<br>121<br>121<br>123<br>123<br>123<br>124<br>124 |  |  |  |

INHALTSVERZEICHNIS iv

|              | 8.4.5.A Einfluss der symmetrierenden Regelung auf das Netzverhalten                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|              | B.5 Bewertung der Parallelschaltung und mögliche Verbesserungen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| 9            | Zusammenfassung und Ausblick 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 28          |

| $\mathbf{A}$ | Stromraumzeiger und Berechnung der Einschaltdauern 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36          |

|              | A.1 Leitzustände und Stromraumzeiger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

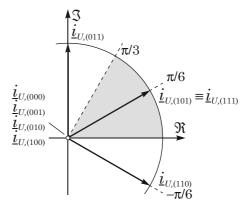

|              | A.1.1 Intervall $1, \varphi_N \in (0; \frac{\pi}{3})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

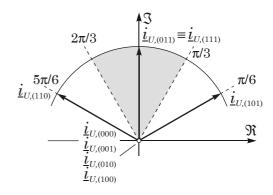

|              | A.1.2 Intervall $2, \varphi_N \in (\frac{\pi}{3}; \frac{2\pi}{3}) \dots 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

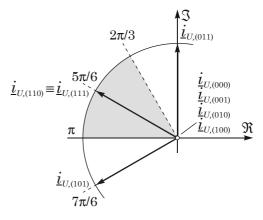

|              | A.1.3 Intervall 3, $\varphi_N \in (\frac{2\pi}{3}; \pi)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

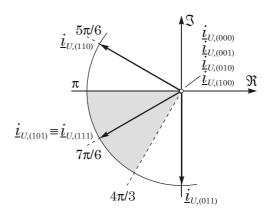

|              | A.1.4 Intervall 4, $\varphi_N \in (\pi; \frac{4\pi}{3})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 138         |

|              | A.1.5 Intervall 5, $\varphi_N \in (\frac{4\pi}{3}; -\frac{\pi}{3})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 138         |

|              | A.1.6 Intervall $6, \varphi_N \in (-\frac{\pi}{3}; 0)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

|              | A.2 Analytisch geschlossene Berechnung der relativen Einschaltdauern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

|              | A.3 Ersetzen von Zeitgrößen durch Raumzeigergrößen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |