DISS. ETH NO. 20354

## ULTRA-HIGH PERFORMANCE TELECOM DC-DC CONVERTER

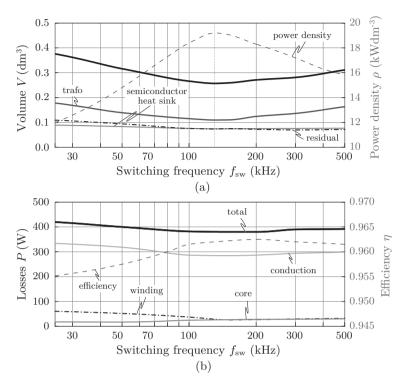

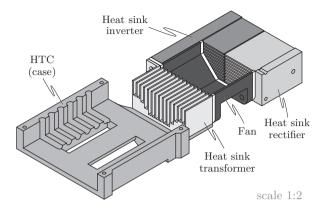

A dissertation submitted to ETH ZURICH

for the degree of Doctor of Sciences

presented by UWE BADSTÜBNER Dipl.–Ing., TU Berlin born 20. July 1979 citizen of Stuttgart, Germany

accepted on the recommendation of Prof. Dr. J. W. Kolar, examiner Prof. Dr. W. G. Hurley, co-examiner

For my parents Sieglinde and Jürgen

## Abstract

Telecommunication and data provision are cornerstones of our modern society. The evolution of the multimedia network around the world started more than one century ago and, as a consequence, the power supplies for the telecom facilities and the parallel-emerging data centres passed through the entire evolution of power electronic systems. Telecom facilities and data centres have started to merge with the digitalisation of the telecom networks. Ever since the following internet boom in the nineties of the last century, the demand on a high-performance data storage, transmission, and computation is rapidly increased. Concurrently, the demanded performance of the modules in the power supply chain and the Information and Communication Technology (ICT) equipment has severely increased. The development of highly compact converter systems counteract the increased demand on space for the ICT-equipment and additionally enables a more-efficient cooling in the data centres. The continuous expansion of digital networks and data centres, as well as the increasing energy prices and the advanced environmental awareness result in shifting drivers for the power-supply development towards an efficient energy transmission and distribution, whereas the power density of the system should remain on a high level.

In this thesis, the limits for the power density and efficiency for DC-DC converters as part of the power supply chain in data centres or telecommunication facilities is investigated. Based on comprehensive analytical thermal, electrical, and magnetic models, the system performance is calculated with the selected free design parameters. Furthermore, these analytical models provide the basis for an automated determination of the optimal design parameters with respect to the maximum power density and/or the maximum efficiency.

Based on the examples of a series-parallel-resonant converter and a phase-shift pulse-width-modulated DC-DC converter with current doubler rectifier, the analytical determination of the maximum power density based on an optimisation algorithm is explained in detail in chapter 2. With the resulting optimised design parameters, the corresponding prototype systems are realised with which the applied analytical models are validated. Moreover, an almost loss-less snubber circuit for the hard-switched rectifier elements of general phase-shift converters is presented, which detracts the ringing energy from the core of the magnetic components and provides this energy for further utilisation.

In addition, a phase-shift pulse-width-modulated DC-DC converter

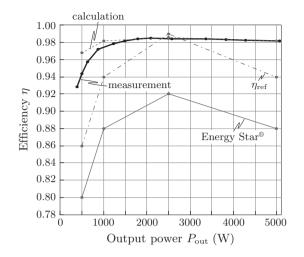

with centre-tapped transformer and second-order output filter is optimised with respect to energy efficiency. The optimisation objective is a load-dependent efficiency profile with a maximum efficiency of 99%. The analytical models, the realised prototype, and the model-validation measurements are detailed in chapter 3. Moreover, the sensitivities of the component parameters on the resulting system performance are investigated. Finally, the influence of the model accuracy on the optimal design parameters is evaluated in chapter 4, and an outlook on further steps in research is given.

# Kurzfassung

Telekommunikation und die Bereitstellung von Daten jeglicher Art sind Grundsteine unserer modernen Gesellschaft. Die Evolution der multimedialen Vernetzung der Erde begann vor mehr als einem Jahrhundert und somit durchliefen die Spannungsversorgungen für die Telekommunikationseinrichtungen und die zunächst parallel aufkommenden Rechenzentren die vollständige Evolution leistungselektronischer Systeme. Mit der Digitalisierung der Telekommunikationsnetze begannen die Telekommunikationseinrichtungen und Rechenzentren zu verschmelzen. Seit dem darauffolgenden Internet-Boom in den neunziger Jahren des letzten Jahrhunderts stieg der Bedarf an einer hoch-leistungsfähigen Datenübertragung, Datenspeicherung und Datenverarbeitung rasant an. Gleichzeitig stieg die Performanceanforderung an die Module der Spannungsversorgungskette und des Datenverarbeitungsequipments massiv an. Die Entwicklung hoch-kompakter und hoch-efficienter Umrichter wirkt dem gestiegenen Platzbedarf des Datenverarbeitungsequipments entgegen und ermöglicht darüber hinaus eine effizientere Kühlung der Rechenzentren. Der anhaltende Ausbau der digitalen Netze und Rechenzentren sowie die steigenden Energiepreise und das erhöhte Umweltbewusstsein verlagern die Zielsetzung bei der Entwicklung moderner Spannungsversorgungen hin zu einer effizienten Energieübertragung und -verteilung, während die Leistungsdichte auf einem hohen Niveau gehalten werden soll.

In der vorliegenden Arbeit sind die Grenzen der Leistungsdichte und Energieeffizienz für Gleichspannungswandler als Teil der Energieübertragungskette in einem Rechenzentrum oder in einer Telekommunikationseinrichtung untersucht. Basierend auf umfangreichen analytischen thermischen, elektrischen und magnetischen Modellen wird die Systemperformance mit der Vorgabe der freien Designparameter berechnet. Diese Modelle bilden des Weiteren die Grundlage für eine automatisierte Berechnung der optimalen Designparameter in Hinblick auf die maximale Leistungsdichte und maximale Effizienz.

Am Beispiel eines Serien-Parallel-Resonanzwandlers und eines pulsweitenmodulierten Gleichspannungswandlers mit Stromverdoppler-Gleichrichterschaltung ist die analytische Berechnung der maximalen Leistungsdichte in Kapitel 2 mithilfe eines Optimierungsalgorithmus im Detail erklärt. Auf Basis der berechneten optimalen Designparameter werden entsprechende Prototypen realisiert und die angewendeten analytischen Modelle experimentell validiert. Darüber hinaus wird eine quasi-verlustfreie Entlastungsschaltung für die hartgeschalteten Gleichrichterelemente von pulsweitenmodulierten Gleichspannungswandlern präsentiert, welche die Schwingungsenergie aus dem Kern der magnetischen Komponente entzieht und zur weiteren Verwendung zur Verfügung stellt.

Des Weiteren ist ein pulsweitenmodulierter Gleichspannungswandler mit Zwei-Wicklungstransformator und einem Ausgangsfilter zweiter Ordnung in Hinsicht auf Energieeffizienz optimiert. Das Optimierungsziel ist eine maximale Effizienz von 99% unter weiterer Berücksichtigung der Teillast-Effizienz. Die analytischen Modelle, der realisierte Prototyp sowie die Validierungsmessungen sind im Detail in Kapitel 3 präsentiert. Darüber hinaus werden die Sensitivitäten der resultierenden Performance bezüglich der Komponentenparameter untersucht. Der Einfluss der Modellgenauigkeit auf die optimalen Designparameter wird in Kapitel 4 evaluiert und ein Ausblick auf weitere Forschungen gegeben.

## Acknowledgement

This thesis results from my employment as scientific assistant at the Power Electronic Systems Laboratory at the ETH Zurich. I would like to thank Prof. Johann W. Kolar for giving me the opportunity to work in this research facility and for the extremely inspiring, intense, and instructive time.

I sincerely thank Prof. William Gerard Hurley from the Power Electronics Research Centre at the National University of Ireland in Galway for his interest in my work and for accepting the invitation to be the co-examiner at my PhD defence – it was an honour.

My special thanks go to Prof. Jürgen Biela for the advices during the first years of my PhD studies and many productive and interesting discussions.

My sincere thanks belong to all my colleagues for making such a great working environment, especially to my office-mates Dr. Simon D. Round, for your friendly welcome, great help, and interesting discussions, and to Christoph B. Marxgut, for your cheering skills, the introduction in classical music, and great technical chats. I thank the co-workers in the lab I18 for the good atmosphere: Dominik Bortis, Daniel Christen, Florian Krismer, Yanick Lobsiger, and Stefan Waffler. Special thanks go as well to all the other colleagues including David O. Bolliat, Thomas Friedli, Jonas Mühlethaler, Andreas Müsing, Gabriel I. Ortiz, Thomas Reichert, Mario Schweizer, Thiago B. Soeiro. It was great to work with you and to have the good time besides the work, interesting lunch breaks, sports and after-work activities. I take this opportunity to thank my semester and master students for your motivated work and contributions.

My warm thanks go to Ivana F. Kovačević, Philipp Karutz, Daniel Aggeler ("oelfi easse"), and Michael Hartmann for your friendship and the great time we have.

For making such a great friendly environment and your help, I extend heartfelt thanks to the PES-administration, namely Peter H. Albrecht, Markus Berger, David Bowler, Roswitha Coccia, Damaris Egger, Isabelle von Niederhäusern, Prisca Maurantonio, Monica Kohn-Müller, Beat Seiler, Peter Seitz, and Claudia Stucki – you are all doing a great job!

And finally I give my sincere thanks to all my friends and my family for their great support, without whom the success of this thesis would not have been possible.

# Contents

| 1        | Hig  | h-Perf                                               | ormance-Design-Challenge                       | 1   |  |  |

|----------|------|------------------------------------------------------|------------------------------------------------|-----|--|--|

|          | 1.1  | Performance Indices of Power Electronic Systems      |                                                |     |  |  |

|          | 1.2  | Design                                               | n for Highest Performances                     | 10  |  |  |

|          | 1.3  | Telecom Facilities and Data Centre Supply Chain      |                                                |     |  |  |

|          |      | 1.3.1                                                | Telecom Facility Power Supply Chain            | 14  |  |  |

|          |      | 1.3.2                                                | Data Centre Power Supply Chain                 | 21  |  |  |

|          |      | 1.3.3                                                | Uninterruptible Power Supply (UPS) Systems     | 23  |  |  |

|          |      | 1.3.4                                                | Typical Loss Distribution of Data Centres      | 25  |  |  |

|          |      | 1.3.5                                                | "Go Green" - Challenges and Possibilities      | 27  |  |  |

|          | 1.4  | Teleco                                               | om DC-DC Converter Topologies                  | 37  |  |  |

|          | 1.5  | Contri                                               | ibution and Outline of this Thesis             | 54  |  |  |

| <b>2</b> | Pow  | Power-Density-Optimised Systems                      |                                                |     |  |  |

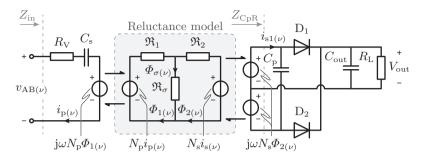

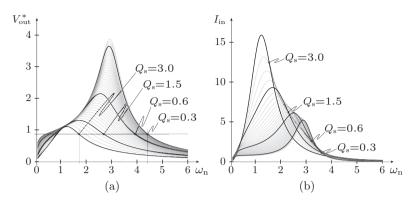

|          | 2.1  | Series-                                              | -Parallel-Resonant Converter (LCC)             | 60  |  |  |

|          |      | 2.1.1                                                | Design Process of the LCC-Resonant Converter . | 77  |  |  |

|          |      | 2.1.2                                                | Analytical Converter Models                    | 81  |  |  |

|          |      | 2.1.3                                                | Optimisation Results                           | 110 |  |  |

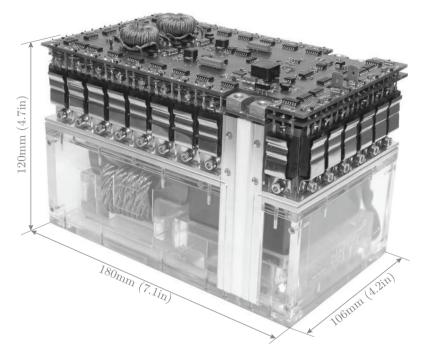

|          |      | 2.1.4                                                | Realised Ultra-Compact LCC Prototype           | 114 |  |  |

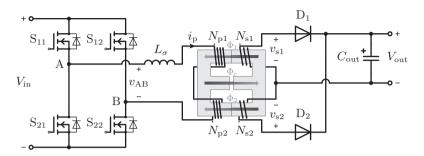

|          | 2.2  | Phase-Shift PWM Converter with Current Doubler (CDR) |                                                |     |  |  |

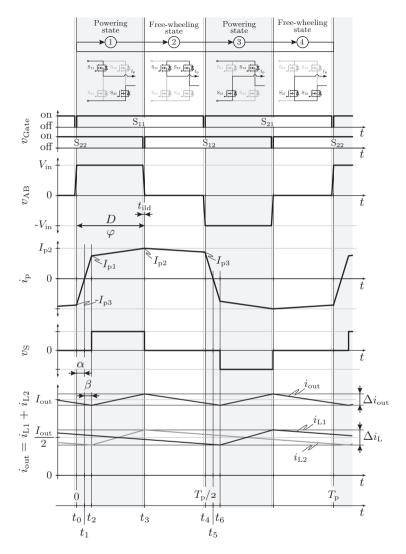

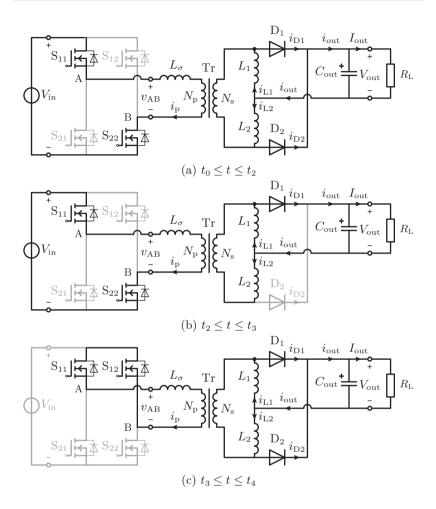

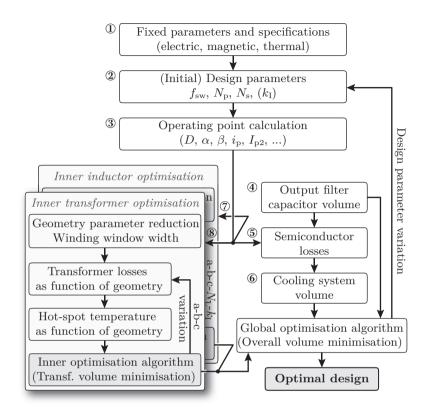

|          |      | 2.2.1                                                | Design Process of the PWM CDR Converter        | 130 |  |  |

|          |      | 2.2.2                                                | Analytical Converter Models                    | 133 |  |  |

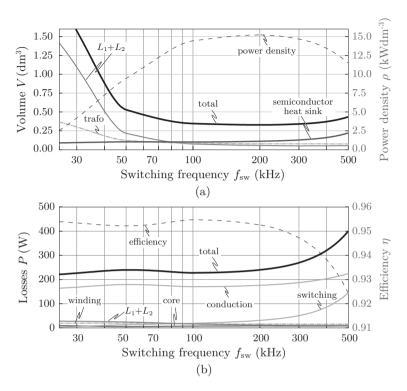

|          |      | 2.2.3                                                | Optimisation Results                           | 145 |  |  |

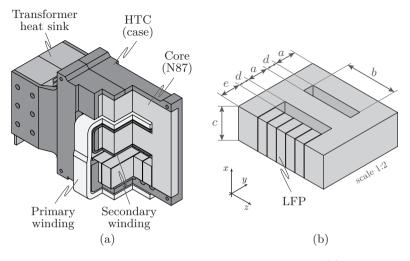

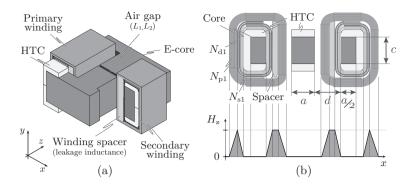

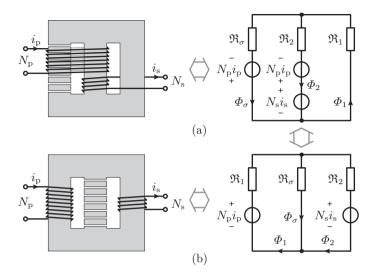

|          |      | 2.2.4                                                | Magnetic Integration of the CDR                | 151 |  |  |

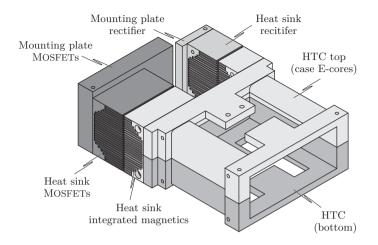

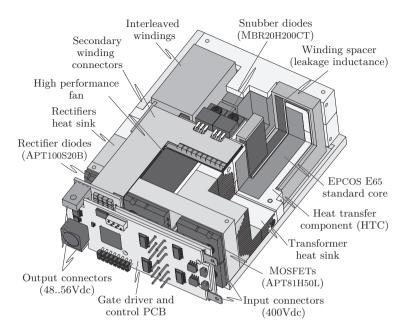

|          |      | 2.2.5                                                | Realised Ultra-Compact CDR Prototype           | 156 |  |  |

|          | 2.3  | Loss-I                                               | Less Snubber Circuits                          | 161 |  |  |

| 3        | Effi | ciency                                               | -Optimised Systems                             | 169 |  |  |

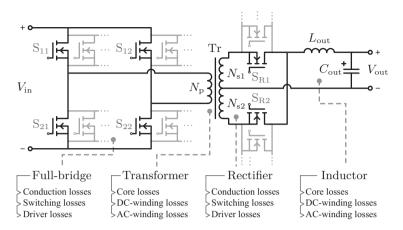

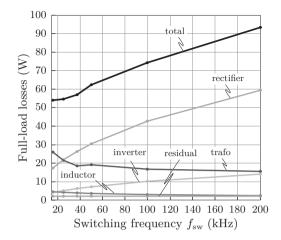

|          | 3.1  | Phase                                                | -Shift PWM Converter                           | 170 |  |  |

|          | 3.2  | Design                                               | n Process of the PWM CTR Converter             | 172 |  |  |

|          | 3.3  |                                                      |                                                | 179 |  |  |

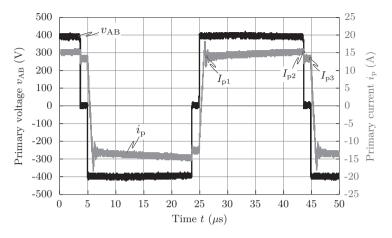

|          |      | 3.3.1                                                | Operating Point                                | 180 |  |  |

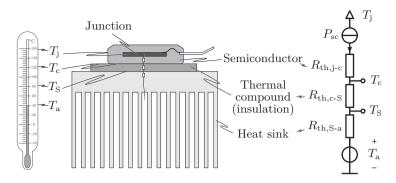

|          |      | 3.3.2                                                | Semiconductor Losses                           | 184 |  |  |

|          |      | 3.3.3                                                | Losses in the Magnetic Components              | 193 |  |  |

|          |      | 3.3.4                                                | Dielectric Losses in the Output Capacitors     | 197 |  |  |

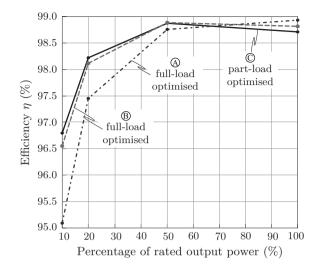

|          | 3.4  | Optim                                                | nisation Results                               | 198 |  |  |

|          |      | 3.4.1                                                | Performance-Influence of Semiconductors        | 198 |  |  |

|          |      | 3.4.2                                                | Performance-Influence of Magnetic Devices      | 201 |  |  |

|    |                                    | 3.4.3 Efficiency-Optimal Converter System      | 203               |  |  |  |

|----|------------------------------------|------------------------------------------------|-------------------|--|--|--|

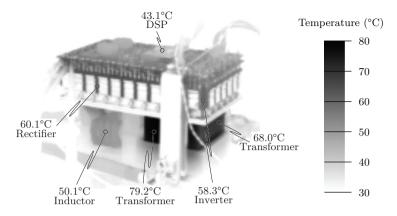

|    | 3.5                                | Realised High-Efficiency CTR Prototype         | 208               |  |  |  |

|    | 3.6                                | Design Parameter Influence                     | 221               |  |  |  |

|    |                                    | -                                              | 227               |  |  |  |

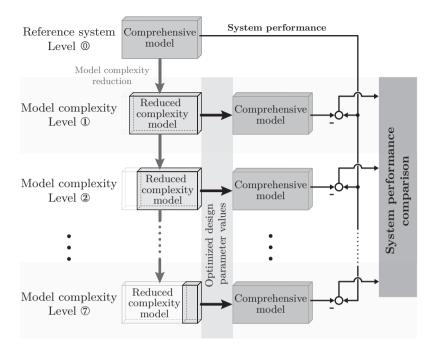

| 4  |                                    |                                                |                   |  |  |  |

|    | 4.1                                | A Compact Efficiency-Optimised System          | 228               |  |  |  |

|    | 4.2                                | Influence of the Optimisation Goal             | 232               |  |  |  |

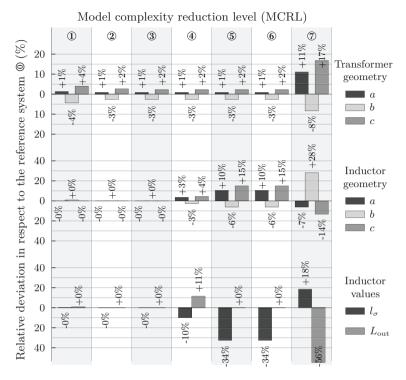

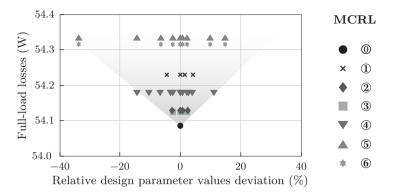

|    | 4.3                                | Reduction of the Model Complexity              | 236               |  |  |  |

| 5  | Conclusion - Optimal Design Spaces |                                                |                   |  |  |  |

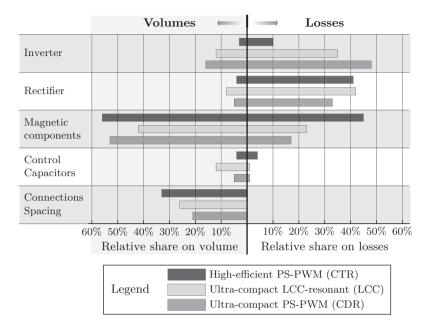

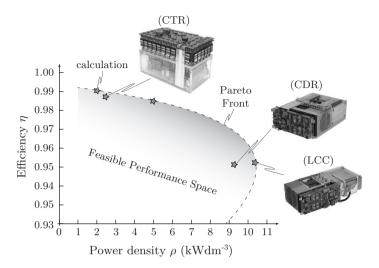

| 0  | 5.1                                | Discussion - Optimised Performance Spaces      | <b>245</b><br>246 |  |  |  |

|    | 5.2                                | Multi-Objective Pareto-Optimal Designs         | 250               |  |  |  |

|    | 5.3                                | Improvements for Future Data Centres           | 252               |  |  |  |

|    |                                    |                                                |                   |  |  |  |

| Α  | Fun                                | ndamental Frequency Analysis (LCC) 25          |                   |  |  |  |

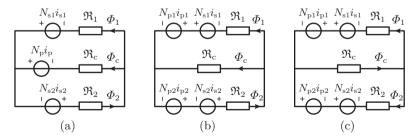

| в  | Mo                                 | del Deviation: Equivalent Reluctance Circuit   | 267               |  |  |  |

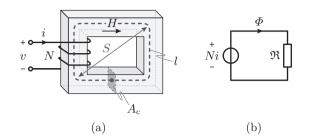

|    | B.1                                | Basic Electromagnetic Laws                     | 267               |  |  |  |

|    | B.2                                | Equivalent Reluctance Circuit Model            | 269               |  |  |  |

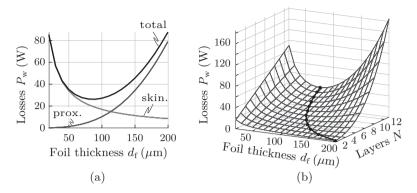

| С  | Wir                                | nding Losses in Magnetic Devices               | 273               |  |  |  |

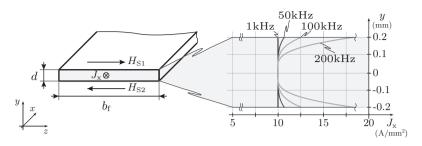

| Ũ  | C.1                                | 8                                              |                   |  |  |  |

|    | C.2                                | Proximity Effect in Foil Conductors            | $276 \\ 278$      |  |  |  |

|    | C.3                                | HF-Losses in Winding Arrangements              | 280               |  |  |  |

|    | C.4                                | Orthogonality of Skin and Proximity Losses     | 283               |  |  |  |

|    | C.5                                | Optimal Foil Thickness                         | 285               |  |  |  |

|    |                                    | -                                              |                   |  |  |  |

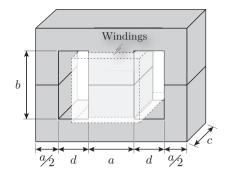

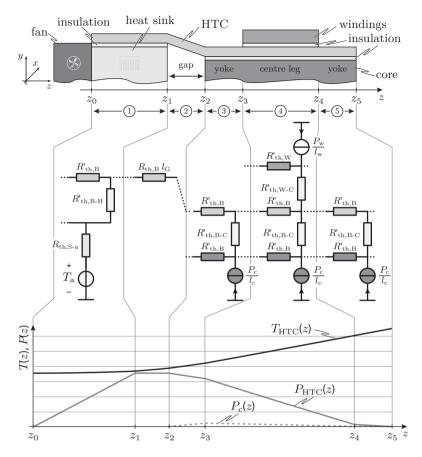

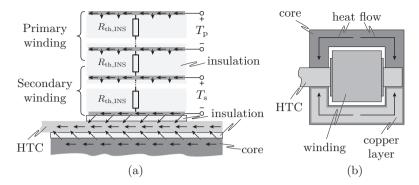

| D  |                                    | rmal Transformer Model                         | <b>291</b>        |  |  |  |

|    | D.1                                | Physical Heat Transmission Mechanisms          | 291               |  |  |  |

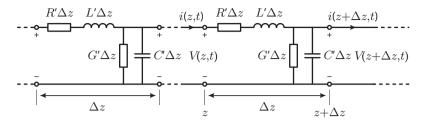

|    | D.2                                | Transmission Line Equations                    | 294               |  |  |  |

|    | D.3                                | Derivation of the Temperature Distribution     | 297               |  |  |  |

|    |                                    | D.3.1 Temperature Distribution in the Windings | 303               |  |  |  |

|    |                                    | D.3.2 Temperature Distribution in the Core     | 304               |  |  |  |

|    |                                    | D.3.3 Induced Eddy Currents in the HTC         | 305               |  |  |  |

| Bi | Bibliography                       |                                                |                   |  |  |  |

# The Challenge of a High-Performance Design An Introduction

The evolution of power electronic systems has now been going on for a century and the exact start, in accordance with the definition of power electronics<sup>1</sup> might be in 1911, when E. F. W. Alexanderson of the General Electric Company (GE) filed a patent application for modulating the current from a high frequency alternator [1, 2]. Alexanderson described a 72 kW magnetic amplifier circuit for radio telephony [3], in today's literature commonly named saturable reactors and transducers, which enabled the transatlantic communication between the United States of America and Europe soon afterwards.

In the 1920's there was a rapid development of vacuum tubes, followed shortly afterwards by gas and vapour filled tubes (thyratrons and ignitrons) [1]. In 1930 the New York Subway installed 3 MW gridcontrolled mercury-arc rectifiers for Dc-motor traction and mercury-arc cycloconverters for universal motor traction were introduced on German railways one year later [4]. Gas and vapour filled tubes were widely used until the mid-1960s.

The principle operation of semiconductor switching devices was described and patented by J.E. Lilienfeld for a Field Effect Transistors (FET) in 1925 in Canada and one year later in the U.S.A. [5]. In 1948, J. Bardeen, W. Brattain and W. Shockley of the Bell Laboratories in-

<sup>&</sup>lt;sup>1</sup>"Power electronics is the technology associated with the efficient conversion, control and conditioning of electric power by static means from its available input form into the desired electrical output form." [1]

vented the point-contact transistor, shortly followed by the junction transistor in 1951 [1, 4]. The revolution of silicon power electronic devices started with the introduction of GE's Silicon Controlled Rectifier (SCR), known since the 1960's as a thyristor, which initialised the step from the gas and vapour filled tubes S-curve [6] to the power semiconductors S-curve. A major step in the development process occurred in the 1970's with the introduction of a giant transistor for DC-motor drives around 1975, a power Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) in 1978, the high power Gate Turn-Off thyristor (GTO) in 1980 and finally the Insulated Gate Bipolar Transistor (IGBT) in 1983 [1, 4]. The era of modern power electronics had begun.

Since the 1970's power semiconductor devices have greatly improved. Besides higher voltage and current ratings, new device materials have been introduced, e.g. silicon carbide (SiC) and gallium nitride (GaN), allowing e.g. higher junction temperatures and smaller on-resistances or faster switching, respectively. The weight of power electronics modules was reduced by factor of more than eight from 1975 to 1998; the footprint size has been reduced by 40 % and the number of solder layers has been reduced from five to one thereby increasing reliability drastically [7]. In the same time the on-resistance of power MOSFETS (e.g. 50 V, Infineon) has been halved [7]. Major advances in power electronics have been mostly based on the improvement steps of power semiconductor devices.

The advances in semiconductor devices will retain its major influence in power electronics in future, however, in consequence of the interdisciplinarity of power electronic systems, environmental, economic and social changes will largely determine the performance drivers of power electronic systems in future. In the next section, an introduction of the most important performance indices and trends of power electronic systems will be given, followed by an abstract perspective on the modulation of the mapping function connecting the available design space with the obtainable performance space in section 1.2. In the ever growing number of telecommunication facilities and data centres the performance of power electronic systems has a major influence on their economic and ecological characteristics. The construction and design challenges as well as the improvement prospects of the facilities subsystems are introduced and discussed in section 1.3. In the power supply chain for the actual load in data centres and telecom facilities - the Information and Communication Technology (ICT) equipment – the

performance of the power supply unit has a major impact on the total facility performance. Independent on the facility DC-DC converters are necessarily applied in this supply chain. Suitable topologies for telecommunication DC-DC converters are discussed in section 1.4 at the end of this chapter.

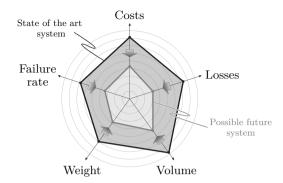

### 1.1 Performance Indices of Power Electronic Systems

With the beginning of modern power electronics after the power semiconductor revolution new dimensions have been enabled and added to the research fields. Power electronics research has shifted from enabling the technology itself to orientating on the system performance, which is quantified by performance indices. The manufacturers of power supplies are usually the suppliers of Original Equipment Manufacturers (OEM) which are influenced themselves by their customers - the actual endusers – and their demands are passed back to the power supplies manufacturers. For that reason, the research and development departments (R&D) are barley technology driven - rather technology-responsive [8]. The resulting most important R&D drivers and performance indices, respectively, are the system cost, losses, volume, weight and failure rate as illustrated in **Fig. 1.1**. The *ideal* power supply for the consumer can be found in the centre of the performance diagram, there the equipment is of zero costs, operates without losses, is infinitesimal small/light and is operating without maintenance effort forever. Even though this utopian wish can't be fulfilled, innovations and improvements in power electronics are clearly enabling big steps towards the centre of the performance diagram in Fig. 1.1.

The performance indices are commonly normalized in order to allow the characterization of a system independent of nominal values, i.e. integral properties of the converter are evaluated with relative quantities [9], e.g. the volume referred to the output power. The most commonly used normalized performance indices resulting from the performance drivers in **Fig. 1.1** - power density, efficiency, output power per unit weight, relative costs and mean time between failures - are introduced in the following.

**Figure 1.1:** Graphical representation of the performance indices for state of the art and future systems.

**Power Density** The commonly used relative representation of the system volume or compactness is the power density  $\rho$ , the ratio of rated output power  $P_{\text{out}}$  to the system volume  $V_{\text{sys}}$ ,

$$\rho = \frac{P_{\text{out}}}{V_{\text{sys}}} \left(\frac{\text{kW}}{\text{dm}^3}, \frac{\text{kVA}}{\text{dm}^3}\right); \qquad (1.1)$$

$1 \,\mathrm{kW/dm^3} = 1 \,\mathrm{kW/\ell} = 1 \,\mathrm{W/cm^3} \cong 16.4 \,\mathrm{W/in^3}$  and  $100 \,\mathrm{W/in^3} \cong 6.1 \,\mathrm{kW/dm^3}$ . Alternatively, a power density could be declared with respect to partial volumes, for instance magnetic devices, heat sinks or an auxiliary supply, and the nominal output power could be the replaced by the maximum output power, if different, and the partial-volume respective power.

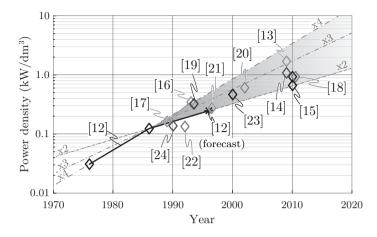

The power density has been one of the most important drivers for power electronics for the last decades and in the course of miniaturisation still has a high significance. As an example the pursuit on highpower-density telecom Power Supply Units (PSU) can be observed in consequence of the continuously increasing demand on data centres and telecommunication facilities. In fact, until some years ago the Capital Expenditure (CapEx) for data centres have been measured on the occupied cross-section area [10] and power density has been figured out as most important performance index for power electronics roadmaps [11].

The system size and consequently the power density are mainly determined by the heat sinks and the passive circuit components, such as

**Figure 1.2:** Power density  $\rho$  of realised telecom Power Supply Units (PSU). (Rectified output voltage  $V_{\text{out}} = 46..56 \text{ Vdc}$ ; output power  $\approx 1..10 \text{ kW}$ )

capacitors and inductors. The innovations and improvements of power semiconductors, allowing higher switching frequency and lower conduction and switching losses, have mainly enabled a considerable system volume reduction. An increase of the switching frequency by a factor of 10 can result in an increase of the power density by factor of 1.5 to 2 [12, 25]. Some power density milestones are presented in Fig. 1.2 for telecom PSUs which are utilised to rectify the single- or three-phase supply voltage of the mains into a DC-output voltage  $V_{out}$  typically between 46 and 56 V.<sup>2</sup> Considering the mid-eighties power density of  $\rho$  $\approx 0.12 \,\mathrm{kW/dm^3}$  as origin [12], three straight lines are plotted in the diagram for the following investigations, identifying the doubling, tripling and quadrupling of the power density within a decade (marked with x2, x3 and x4, respectively, in Fig. 1.2). As presented in [12], the power density has been quadrupled from 1976 to 1986 and the forecast, which showed a further doubling until 1996 (marked with a "\*") has been later proved by [21]. An even higher increase as the predicted doubling of the system power-density in that decade has been shown by [17] (approx. tripling) and even the continuation of the quadrupling-trend in the previous decade has been featured by the rectifier systems presented

$<sup>^{2}</sup>$ More detailed specifications can be found in section 1.3.

in [16, 19].

Right after the millennium-turn, the power densities of realised PSUs have been approximately on the tripling-trend line considering the origin in the eighties (e.g. [20, 23]). At the end of the first decade of the 21<sup>st</sup> century, the power density of applied telecom PSUs can be found between the doubling and the tripling trend line (e.g. [13–15, 18]). A continuation of the quadrupling-trend appears to be difficult, on one hand because a power-density-increase is besides the improvements and innovations of the power semiconductor industry also depending on the advancements of the passive components, which could be observed only to a minor degree in the last decades [8]. On the other hand, the focus of the development and research of power electronic systems is not merely on a single performance index as the power density, but rather on multiple performance indices at the same time, allowing for instance smaller costs while accepting a smaller power density conversely. The identification of the theoretical power-density barrier, i.e. the limit of power density when only focusing on this single performance index, is one of the major parts of this thesis presented for telecom DC-DC converter systems in chapter 2.

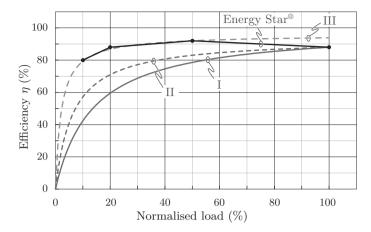

Efficiency The market for switching power supplies has grown with the raising market for desktop computers and the global network; and still, the annual investment growth forecast e.g. for telecom and datacom power supplies over a power range of some watts to several kilowatts is higher than 15% [26]. At the same time, the demand on electric energy has grown as well and power electronics is becoming the key technology for a more sustainable generation, distribution and use of electric energy. Besides the ecological aspects, power electronics development and research is strongly driven by economic considerations. This progression is shown clearly for instance for telecom and data centre PSUs: until some years ago, it took 20 to 30 years until the costs for powering and cooling have been equal to the purchasing cost of the PSU [10]. However, because of the falling prices for power electronic equipment and the contrary increasing energy prices, the operating costs exceed the hardware costs nowadays in less than two years [10]. This leads to a move towards the development of more efficient power supplies. Consequently, besides power density, the system efficiency  $\eta$  is one of the most important physical performance indices to characterise a power

Figure 1.3: System efficiency in dependency of the relative rated output power  $P_{\rm out}/P_{\rm out,N}$  as proposed in the Energy Star<sup>®</sup> requirements for computer servers [27]. I: efficiency graph of a system with constant losses over the entire load range; II+III system with constant and load-dependent losses.

electronic system,

$$\eta = \frac{P_{\text{out}}}{P_{\text{in}}} = \left(1 + \frac{P_{\text{loss}}}{P_{\text{out}}}\right)^{-1} \approx 1 - \frac{P_{\text{loss}}}{P_{\text{out}}},\tag{1.2}$$

with the system input power  $P_{\rm in}$ , the output power  $P_{\rm out}$ , and the total system losses  $P_{\rm loss}$ .

The system efficiency is usually specified for the rated output power  $(P_{\text{out}} = P_{\text{out},N})$ . However, in several fields of application converter systems are frequently not only operated at full load and in consequence the corresponding efficiency specifications and regulations are specified together with part-load efficiencies, e.g.  $\eta_{10\%}$ ,  $\eta_{20\%}$ ,  $\eta_{50\%}$  and  $\eta_{100\%}$  as proposed in the Energy Star<sup>®</sup> requirements for computer servers [27]. In **Fig. 1.3** the suggested required part-load efficiency values for computer server power supplies (single output, AC-DC & DC-DC) are illustrated for a rated output power higher than 1 kW regarding Energy Star<sup>®</sup> [27].

A power supply system with constant losses over the entire load range and with a full-load efficiency similar to Energy Start<sup>®</sup>, i.e.  $\eta_{100\%} = 88\%$ , cannot accomplish the required part-load-efficiency as

illustrated in **Fig. 1.3** (marked with I). Neither the system II can fulfil the requirements whose total losses are the sum of constant and load-dependent losses linearly decreasing with the output power<sup>3</sup>, although the part-load efficiency could be improved and is more realistic regarding to a physical system. In order to meet the part-load efficiency requirements, the constant system losses can only have a minor share of the total losses, as e.g. shown for the efficiency graph of system III<sup>4</sup> in **Fig. 1.3**. That implicates that low-power consumers, e.g. the digital control and the auxiliary supply, have to be thoroughly considered during the design process of high-efficiency power supplies. Moreover, these and further subsystems consuming an almost fixed amount of power even though the converter systems is not transmitting energy to the output if no load is applied. As a result of these fixed losses – also called shunt, no-load, tare or parallel losses – an efficiency curve starts at zero at no-load as illustrated in **Fig. 1.3**.

Alternatively to the specification of discrete efficiency points, the mean efficiency over the output power range could be applied as, for instance, for photovoltaic inverters [28] or, with the knowledge of the mission/load profile, the more precisely specifying Mean Mission Efficiency [9, 29]. In order to enable a direct calculation of the required cooling effort and heat emissions, respectively, the relative losses are calculated to characterise the power electronic system [9],

$$\frac{P_{\rm loss}}{P_{\rm out}} = \frac{1-\eta}{\eta}.$$

(1.3)

For big systems like data centres, which consist of several subsystems ensuring the system energy balance, the Power Usage Effectiveness (PUE) as suggested e.g. in [30] could appropriately be applied to describe the system efficiency,

$$PUE = \frac{P_{\text{fac}}}{P_{\text{ICT}}},$$

(1.4)

with the total power delivered to the facility  $P_{\text{fac}}$  and the power supplied to the intrinsic load  $P_{\text{ICT}}$  which is in this case the ICT-equipment.

<sup>&</sup>lt;sup>3</sup>The constant losses of system II equal the load-dependent losses at 100 % output power and the total losses are  $\eta_{100\%} = 88$  %, similar to Energy Star<sup>®</sup>.

<sup>&</sup>lt;sup>4</sup>System III shows constant and load-dependent losses which are equal at 50 % load and the sum of both is equal to  $\eta_{50\%}=92\%$ , similar to Energy Star<sup>®</sup> at this point.

As indicated before, the efficiency is more and more in the focus for power electronics development and research which leads to higher efficiency converter systems on the market. As the power density, the efficiency is strongly coupled to other performance indices and higher system efficiency can besides components and topology advances only be achieved with e.g. more volume and weight as well as higher cost. Because of the major importance, chapter 3 is dedicated to the identification of the interdependency and limits of the system efficiency of telecom DC-DC converter systems, the second major aspect of this thesis.

Output Power per Unit Weight The system weight  $W_{\rm sys}$  is barley investigated in literature at the moment, however, in the course of evolution towards Electric Vehicles (EV), More Electric Aircraft (MEA) and for several other fields of applications - especially in the area of mobility - the weight of the required power electronic system is important, because of the direct coupling between system weight and energy consumption. As the result of this coupling and the increasing awareness concerning energy consumption a weight-regarding normalised performance index, i.e. the output power per unit weight,  $\gamma$  [9],

$$\gamma = \frac{P_{\text{out}}}{W_{\text{sys}}} \left(\frac{\text{kW}}{\text{kg}}, \frac{\text{kVA}}{\text{kg}}\right), \qquad (1.5)$$

has to be considered in future system designs.

**Relative Costs** The market for power electronic systems is mainly driven by the requirements of the end user. The literature agrees on identifying the system costs as the most powerful driver for the market, e.g. [8, 26, 31–33]. More than 77% of OEMs in the field of power supplies named costs as the most important non-product power supply vendor selection criteria [8]. As a result, the manufacturing costs have been reduced for instance by 30% per electronic function and year in the power semiconductor industry [32]. The power that can be installed for a given system price  $C_{\rm sys}$ ,

$$\sigma = \frac{P_{\text{out}}}{C_{\text{sys}}} \text{ e.g.}\left(\frac{\text{kW}}{\notin}\right), \qquad (1.6)$$

can be used as normalized performance index to specify the system [9].

Mean Time Between Failures (MTBF) Nearly 41% of OEMs identify reliability as an important product selection criteria for power supplies [26]. The reliability requirements are usually specified in the form of a Mean Time Between Failure (MTBF) [34], the inverse of the random failure rate  $\lambda$ ,

MTBF =

$$\frac{\int_0^T R_{\rm T}(t) dt}{1 - R_{\rm T}(t)} = \frac{1}{\lambda},$$

(1.7)

with the reliability function  $R_{\rm T}(t)$  and the point in time T. The reliability model for the applied system components, e.g. for power modules [35, 36], are commonly complex and challenging to establish. Moreover, a power electronic system often contains several hundred models aggravating the computation of the integral. An approximation as e.g. proposed in [34] could be applied in this case.

Power density, efficiency, output power per unit weight, relative costs, and mean time between failures - all five performance indices which influence the design of power electronic systems are approaching the costumer's demands and specifications. The resulting system performance is consequently a trade-off between different target whereas in special applications certainly the highest possible value of a specific performance index might be claimed. Moreover, for roadmaps and future research and development orientations of OEMs, the examination and knowledge of the limit of a single performance index is the corner stone. In this thesis the two, for telecom power supplies most important non-product performance indices – power density and efficiency – are investigated in order to identify the highest possible performances for this type of power electronics system. The principle approach to obtain these limits is explained in the following section.

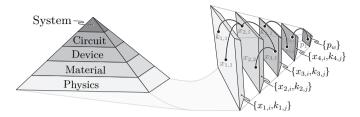

#### 1.2 Design for Highest Performances

The performance of a power electronic system depends on the system design, i.e. the determination of possible design parameter which results in the required system performance. The key for investigating the performance is consequently the exploration of the subordinate levels of a power electronic system and the therein contained elements. In order to obtain the highest performance, the system elements have to be

Figure 1.4: Levels of a power electronic system.

defined in the way that the optimum performance related to a specified optimisation criterion is accomplished.

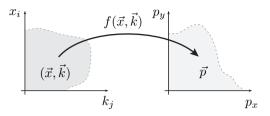

From a hierarchical perspective a power electronic system can be divided into five technology levels [32]: fundamental physics - material - device - circuit - system. Each level provides the basis for the next level above and the respective lower level forms the design space of the respective next higher level(s). The free design parameters  $\vec{x}$  and constants  $\vec{k}$ , which configure the design space, enable a specific performance  $\vec{p}$  in the next level above as illustrated in **Fig. 1.4**.

For instance, with Ohm's law, e.g.  $x_{1,1}$ , and the resistivity of the material copper, e.g.  $k_{1,1}$ , of the fundamental physics level, the electrical DC-resistance, e.g.  $x_{2,1}$ , is defined as function of the cross-section area, e.g.  $k_{2,1}$ , and length, e.g.  $k_{2,2}$ . The material can be used as bus bars, e.g.  $x_{3,1}$  in the device level, for interconnecting two circuit elements, e.g.  $x_{4,1}$  and  $x_{4,1}$ , and thus has an influence on the system performance, e.g.  $p_2$ , which could be assigned to the converter efficiency  $\eta$ .

The elements of the single level have theoretical and practical limits which are partly almost fix; for instance the laws of physics are changing very rarely. On the other side, limits might change very rapidly – for instance because of new technological inventions and economical rethinking, respectively. Either way, the limits of each level-element have to be considered in the performance analysis for authentic results.

If the performance exploration is concentrated on the entire power electronic system rather than single devices or materials, the four lower levels (fundamental, material, device, circuit) can be summarized to the design space - the basis for enabling the power electronic system<sup>5</sup>. The resulting summarized free design parameters  $\vec{x} = (x_1, x_2, \dots x_n)$  have to be determined during the system design process and a specific system

<sup>&</sup>lt;sup>5</sup>The following variable names refer to the designators proposed in [9, 37, 38].

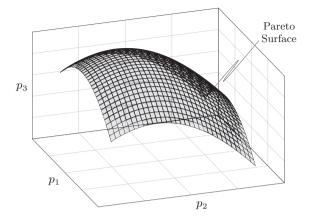

**Figure 1.5:** Mathematical perspective of mapping the design space to the performance space of a power electronic system.

performance  $\vec{p} = (p_1, p_2 \dots p_m)$  results.

During the conventional design process, the design parameters  $\vec{x}$  are determined based on the performance requirements  $\vec{r} = (r_1, r_2 \dots r_s)$  and design constants  $\vec{k} = (k_1, k_2 \dots k_l)$ . The design parameters  $\vec{x}$ , performance requirements  $\vec{r}$ , and constants  $\vec{k}$  are related together with the design constraints  $g_i(\vec{x}, \vec{k}, \vec{r}) = 0$ . Because of the complexity of the power electronic system, the number of design variables  $\vec{x}$  exceeds the number of design constraints  $g_i$  resulting in an extremely large number of sets of possible solutions for the design variables  $\vec{x}$  satisfying the requirements  $\vec{r}$  and constraints  $g_i$ . However, an optimum performance regarding one or more performance indexes  $p_{w,\text{opt}}$  ( $w = 1, 2 \dots m$ ) is generally not obtained with that design approach.

For a performance-specific exploration of the power electronics system design a mathematical description  $f(\vec{x}, \vec{k})$  is necessary to map the design space consisting of the free and constant design parameters  $(\vec{x}$ and  $\vec{k})$  to the performance space  $\vec{p}$ , as illustrated in **Fig. 1.5** [9, 38]. The feasible design space is constituted by the physical and theoretical limits of the containing elements and the constraint functions  $g_i$  and  $h_j$ ,

$$g_i(\vec{x}, \vec{k}, \vec{r}) = 0,$$

$i = 1, 2, \dots p,$  (1.8)

$$h_j(\vec{x}, \vec{k}, \vec{r}) \ge 0,$$

$j = 1, 2, \dots, q,$  (1.9)

which describe e.g. performance requirements and specifications, inner system states and limits. The resulting performance space is consequently limited as well and the optimum design related to a performance index  $p_w$  (w = 1, 2...m) is obtained if the mapping function  $f(\vec{x}, \vec{k})$ , defined as optimum design criterion, is maximal,

$$f\left(\vec{x},\vec{k}\right) \to \max$$

. (1.10)

If for instance the power density  $\rho$  of a power electronic system at the nominal output power  $P_{\text{out}}$  is defined as performance index  $p_1$ , and the highest possible value for  $p_1 = p_{1,\text{max}}$  is the aim of the system design considering the side conditions  $(g_i \text{ and } h_j)$ , the mapping function  $f\left(\vec{x}, \vec{k}\right)$  describes the sum of the n volume-contributing elements  $V_i$   $(i = 1 \dots n)$  of the examined system,

$$f\left(\vec{x}, \vec{k}\right) = \frac{\sum_{i=1}^{n} V_i}{P_{\text{out}}} .$$

(1.11)

The optimal design parameters  $\vec{x}_{opt}$  can be obtained by applying an automatic optimisation procedure varying the free design parameters  $x_u$  until the highest feasible performance for  $p_1$ ,

$$p_1 = p_{1,\max} = f\left(\vec{x}_{\text{opt}}, \vec{k}\right),$$

results. This system design approach has been successfully applied for ultra-compact and high efficiency telecom DC-DC power supplies as described in chapter 2 and chapter 3, respectively.

### 1.3 Telecom Facilities and Data Centre Supply Chain

Telecommunication facilities and data centres are an important cornerstone of our modern society. These "silent companions" enable almost every security and economically relevant interactions, e.g. control and guidance of the air/land/water transport, financial transactions or ecological calamities warnings. Malfunctions of the involved facilities may result in chaos, breakdown of the public life or even represent hazards to live and health. In addition to the security relevant services, data centres provide an almost infinite appearing reservoir of data bases utilised for scientific research and computation, as well as social networks, news and all the entertainment provided by the World Wide Web. The architectures for powering the different types of the facilities and the associated challenges are the focus of this section. The evolution of the today's global communication and data transfer network and the involved date centres started with the development and the continuous extension of the telephony network and the thereby necessary telecommunication (telecom) facilities, i.e. access, service and switching nodes. In parallel started latish the installation of data storage and processing centres, mainly constituted in big research facilities and companies. These arrangements are different regarding maintenance, structure and powering. Telecom facilities are historically Dcpowered and availability has been the highest priority, whereas data communication centres are AC-powered and rather service orientated.

In the course of the worldwide digitalisation of the telephony networks and the internet boom in the early nineties, five separate networks for telephony, mobile telephony, data communication, router/internet communication and broadband communications started to merge [39]. The broadband technology, starting with the Integrated Services Digital Network (ISDN), later e.g. Asynchronous Digital Subscriber Line (ADSL) and Very High Bit rate Digital Subscriber Line (VDSL), is providing the possibility of fast data processing, exchange and recall to a large share of the population. The demand on information and entertainment is rapidly increasing and as a result, already in the late nineties, 60% of the total access network and IT energy consumption has been used for the costumers personal computers, 30% for the application servers, 5% for the switching nodes and another 5% for the access nodes [39]. Since then, numerous data centres – also called "server farms" or "internet hotels" - have been founded; and still, the annual growth rate of shipped server equipment has been 17% in 2004 [40] and the global market for data communication annually exceeds USD 100 Billion [41].

#### 1.3.1 Telecom Facility Power Supply Chain

After the invention of the telephone by Philipp Reis in 1861 and the improvements made by Alexander G. Bell and David E. Hughes in 1876, one of the first public telephone networks has been set in operation in 1881 in Berlin, Germany, supplied by a local battery system [42]. The principle of the DC-powered telecom facilities was left unchanged, even though the rectifier connected to the local power grid, charging the battery and supplying the DC-bus, went through the whole history of power electronics - from the mercury-arc rectifiers in the nineteen-twenties,

Figure 1.6: Structure of telecom facilities with a 48 V Dc-bus.

selenium rectifiers, magnetically controlled rectifiers, to the point of introduction of silicon semiconductors, such as thyristors, GTOs and MOSFETS.

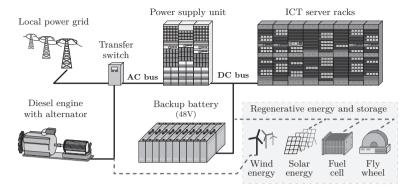

The typical structure of a telecom facility is illustrated in **Fig. 1.6**. The facilities are commonly connected to the local single- or threephase grid during normal operation. In series with a transfer switch, the mains voltage is rectified in the Power Supply Unit (PSU) and converted down to the voltage level of the Dc-bus. The universal standard Dc-bus voltage<sup>6</sup> is 48 V, defined by the European Telecommunications Standards Institute (ETSI) and the American National Standards Institute (ANSI) [39], limited by the maximum allowed voltage for electronic devices without additional protection, as defined in the international standard for protection and safety of low-voltage installations [44], with consideration of a battery voltage tolerance. This low bus voltage allows the work on the operating system with a minimum risk of personal injury without special safety precautions. The safety voltage has been increased to 60 V [44] and therefore ICT-equipment with a nominal input voltage of  $52 \,\mathrm{V}$  to  $54 \,\mathrm{V}$  is available on the market, counteracting the higher power demand of the ICT-equipment and the accruing ohmic losses in the bus cables.

In the case of a local power grid breakdown, backup batteries supply the facilities immediately with the required energy. The batteries are directly connected via circuit breakers or fuses with the DC-bus and

$<sup>^{6}</sup>$ The bus voltage is rather -48 V relating to Earth potential, e.g. [43], mainly because of the corrosion reduction of the copper wires installed in the ground.

thus mainly determining the bus voltage. By the end of the sixties, 23 plus three additional flooded lead acid battery cells ("23/26 el") have been deployed with a resulting bus voltage range of 45 to 53 V [45]. The additional three battery cells supplied with a separate rectifier could be switched to the bus in order to compensate variable loads. From the mid-seventies until the mid-eighties 24 battery cells ("24 el") have been installed with an voltage range of 41 to 55 V [45]. Since the mid-eighties switched mode rectifiers are deployed (52.8 V [45]), today commonly with low maintenance Value-Regulated Lead-Acid batteries (VRLA). The required input voltage range of the telecom equipment connected to the bus is determined by the battery voltage range and the conversion efficiency might decrease at lower battery voltage, e.g. in case of a prolonged breakdown. The battery hold-up time is approximately three hours for an autonomous operation [46], depending on the requirements, and therefore the volume occupied by the batteries might result in high space requirement in the facilities.

The availability of telecom facilities has a very high priority and the three hours back-up time of the batteries is commonly not sufficient as prolonged breakdowns of several hours or days, for instance caused by human mistakes, or accidents, or severe weather, are important to master besides the rather seldom occurring short and medium interrupts, mostly caused by failures of the PSU. For this reason, generally diesel engines coupled with alternators are installed which provide energy for 150 to 300 hours autonomous operation [46]. In case of a prolonged mains breakdown the generator is switched to the rectifier stage via the transfer switch recharging the battery and supplying the facilities. The diesel generators can be replaced by fuel cells, e.g. proposed in [45, 47], and the battery can be replaced or be supported by High Speed Flywheels (HSF), e.g. in [39, 47, 48].

In some inaccessible regions a local power grid is not available and other power sources must be used. Already in the mid-seventies, solar photovoltaic cells have been applied for powering telecom facilities in isolated areas of Australia [49]. The back-up batteries there are exposed to high stress because of the daily sun-cycle and the superimposed annual cycle and must offer a huge back-up time up to 10 or 15 days [49]. Moreover, the battery charge should not be lower than 50 % during poor weather in order to enlarge the battery lifetime. The lead-acid batteries are as a result the most-expensive part of the powering system, followed by the solar panels, as presented for instance in [49] for a 11 kW-system

Figure 1.7: Schematic of a DC-powered telecom facility.

installed in 1978. The life-time requirements are nevertheless around 15 years.

Besides the autonomous powering of the telecom facilities, renewable energy sources could be deployed in addition to the local power grid, e.g. [46, 47, 50, 51]. Wind turbines and solar photovoltaic cells as illustrated in **Fig. 1.6** are feasible as supportive energy sources.

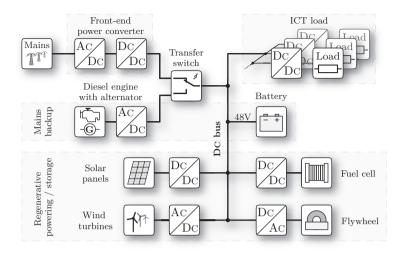

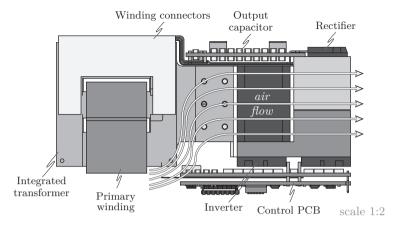

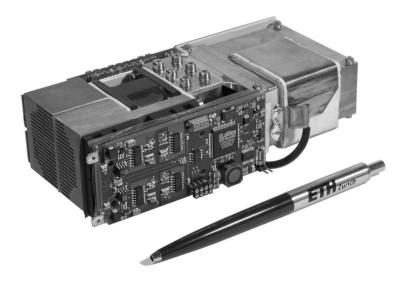

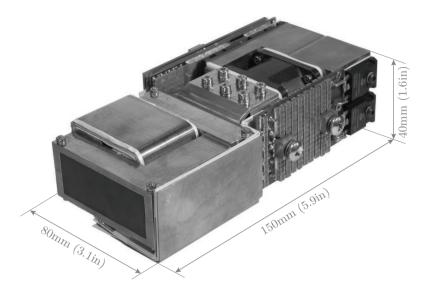

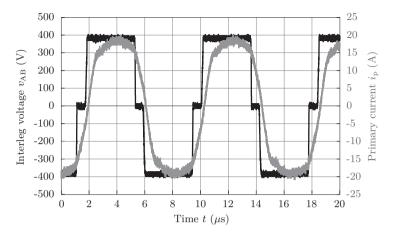

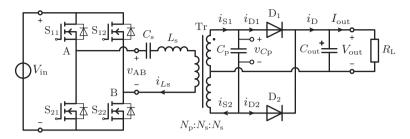

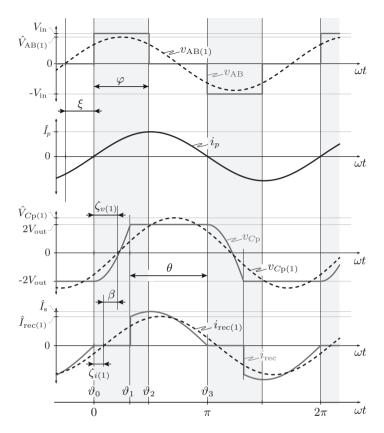

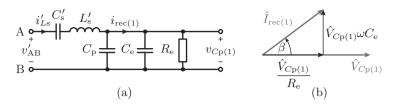

A summary of the telecom facility power supply is schematically shown in **Fig. 1.7**. The Power Supply Unit (PSU) which rectifies the mains voltage and provides the 48 V DC-bus voltage is divided into two conversion stages: the front-end AC-DC rectifier, today commonly with Power Factor Correction (PFC), and the DC-DC converter connected in series to step the intermediate circuit voltage galvanically isolated down (400 V to 48 V). Historically, the PSU has been composed of a transformer for the galvanically isolated voltage step-down followed by a rectifier.

The complexity of the complete powering system and the number of power conversions in case of the DC-bussed facilities are much less than e.g. for an AC-bussed data centre as shown below in this section. Telecom facilities offer therefore an inherently higher reliability.

The different demanded on-board voltage levels of the telecom equipment are generated with Voltage Regulation Modules (VRMs),

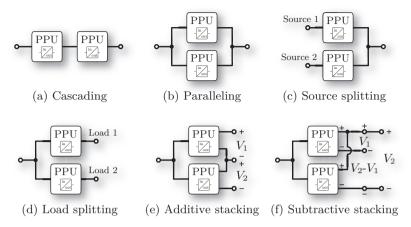

**Figure 1.8:** Basic structures for power distribution [52, 53]: (a) Cascading, (b) Paralleling, (c) Source splitting (d) Load splitting (e) Additive stacking, (f) Subtractive stacking. (PPU = Power Processing Unit).

i.e. DC-DC converters which step the DC-bus voltage (48 V) down to 12 V, 5 V, 3.3 V, etc.

**Distributed Power Systems (DPS)** The initial power supply unit in telecom facilities has been *centralised*, i.e. the only conversion stage has been the galvanically isolated rectifier which provided the required voltage of the telecom equipment. The advantage of centralised powering is that the thermal management is concentrated in a single box; however, the power system with a single conversion stage is not flexible and usually fails to provide the required regulation performance at the point of load [52] due to the bus impedance. Moreover, the availability of a centralised power supply is inherently small.

In consequence of the today's required performance in data centres and telecom facilities, the trend is away from *centralised* system to Distributed Power Systems (DPS) which are able to provide the required dynamic and accuracy, e.g. for the low voltage and high-frequency clocked processors. The complexity of the powering system thereby increases and multiple power conversion stages are in different locations, as for instance shown in **Fig. 1.7** for modern telecom facilities. The basic structures of distributed power systems are shown in **Fig. 1.8**  [52, 53]:

- (a) Cascading

- (b) Paralleling

- (c) Source splitting

- (d) Load splitting

- (e) Additive stacking

- (f) Subtractive stacking.

Because the discussion of the below presented more complex data centres is partly based on distributed power systems the basic DPS structures are shortly described in the following.

**Cascading** of power supplies is applied for efficiently providing high conversion ratios and adequate dynamic load regulation. In **Fig. 1.7**, for instance, the PSU is divided into rectifier commonly with PFC for rectifying the mains voltage to an intermediate Dc-voltage (approx. 400 V for the single-phase European 230 V Ac-grid), followed by a Dc-Dc converter which steps down the intermediate circuit voltage to the demanded Dc-bus voltage (e.g. 48 V). The current carried in the Dc-bus should be small in order to avoid expensive and heavy copper wiring. For that reason the bus voltage is usually higher than the load voltage and thus a further cascading is deployed for the VRMs located close to the load which step down the Dc-bus voltage to the demanded load voltage with fast control loops for regulating highly dynamic load variations. In addition to the fast responses, variation of the bus voltage can be compensated, e.g. in case of an autonomous battery supply and the associated bus-voltage decrease.

**Paralleling** power converters is the basic method behind modularisation and widely used in data centres and telecom facilities. The need of modular architectures originates from the costumers demand for flexible, reliable, standardised, higher power supplies. Off-the-shelf available standardised modules, e.g. paralleled in the PSUs to obtain the specified power range, lower the engineering costs and time, resulting in an increased competitiveness. Modularisation also enables redundancy for higher reliability of the power supply: m + r modules are installed, with the *m* demanded modules and the additional *r* redundant modules, which allow *r* units, e.g. usually r=1 [52] or for high-available systems even r=m), to fail for an uninterrupted system operation and maintenance, and furthermore reduce the thermal and electric stresses of the components. Besides the application to obtain a higher availability, redundant PSU-modules are for instance further used for faster charging the back-up batteries after a line break-down. An additional advantage of paralleling modules in single power supplies is the possibility of interleaved switching operation which enables the reduction of magnetic components and a higher effective switching frequency, resulting in higher control bandwidth and faster dynamic response, the prevention of abnormal or even damaging system conditions [52], and moreover, the reduction of harmonics and Electromagnetic Interference (EMI) due to the current ripple reduction, resulting in smaller filter components.

Source splitting is used to increase the reliability and power range of a power supply, similarly to paralleling. By applying separated converters for supplying a common load the uninterrupted supply of the telecom equipment is ensured (amongst others), as for instance shown in **Fig. 1.7**, where the DC-bus can be powered either by the local network via the PSU or the backup battery. A further typical application is the separation of the mains-phases, where each phase is connected to an own PSU, resulting in a higher availability of power in case a module fails.

Load splitting is commonly referred to a distributed power system and is applied, e.g. in large scale facilities and in case various voltage levels are required. Splitting of the load DC-DC converters in Fig. 1.7, for instance, and the close connection to the load enables an adequate voltage regulation, the minimisation of noise interference effects between the loads [52] and the isolation of the noise generation from the rest of the system. In addition to the system level, further onboard VRMs for multiple voltage levels are deployed in the equipment modules itself.

Stacking of power supplies is commonly applied for realising nonstandard or very precise voltages with standard modules. Higher or mirrored voltages can be implemented with additive stacking as illustrated in Fig. 1.8(e), whereas the low voltages for processors are partly realised with subtractive stacking as shown in Fig. 1.8(f).

These basic structures are applied in complex systems like data centres in order to fulfil the high-performance requirements of the computer equipment.

#### 1.3.2 Data Centre Power Supply Chain

Data centres, installed for computation and data storage in the first place, look back to a steeply growing system performance during the last century. The computation speed and capacity of the storing devices are continuously increasing and the performance (size, computation speed, storage capacity, price, etc.) of available computer equipment is wideranged – from small home servers to megawatt server farms. Different to telecom facilities, where the uninterrupted availability has the highest priority, data processing and storage centres are more batch-orientated, i.e. the equipment must be able to be fast upgraded, extended and swapped, respectively. Because of the demanded flexibility and the wide-range application area, the merger of classical telecom facilities with data processing and storage centres are commonly AC-bussed with the local standard grid voltage.

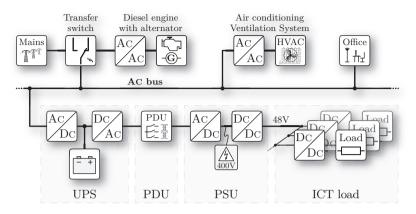

A possible structure of a medium-scale data centre is schematically illustrated in **Fig. 1.9**. The main branch, supplying the data processing and communication equipment (ICT-load), is connected via circuit breakers to the local power grid. The first unit in the power supply chain is the Uninterruptible Power Supply (UPS) guaranteeing the continuously powering for the equipment in case of a line breakdown. The energy backup is provided by batteries similar to telecom facilities, however, the battery voltage is commonly higher than 48 V and may reach 400 V and more [41]. For an uninterrupted 3 hours supply, e.g. 54 cells are required for a 10-kVA system and 206 cells for a 300-kVA system [41]. In case of a prolonged line breakdown of several hours or days, commonly an alternator operated by a diesel engine is installed in the facility in order to limit the size and costs for the UPS system.

The UPS is followed by the Power Distribution Unit (PDU), which commonly provides besides circuit breakers, a galvanic isolation, load balancing and reactive power compensation. Besides rack-based centralised UPS systems, in some data centres, more costly decentralised UPS are applied for single important racks in order to reduce the complexity of the PDU because of the inherent power factor correction of the UPS systems.

The power distribution units are followed by the Power Supply Units (PSUs), which are adapted to the required voltage level of the Information and Communication Technology (ICT)-equipment. The communication equipment, for instance, is traditionally 48 V-DC-powered [54] and the PSU thus rectifies the AC-bus voltage, e.g. 230 V in Europe,

**Figure 1.9:** Schematic of an AC-powered data centre (UPS = Uninterruptible Power Supply, PDU = Power Distribution Unit, PSU = Power Supply Unit). For the UPS system the double-conversion type, most-applied above 5 kVA, is shown.

and galvanically isolates and steps down the voltage in a second conversion stage. Especially in large-scale data centres, there are several racks completely equipped with PSUs, whereas for small business servers the PSU can be found directly in the rack units.

Additional on-board DC-DC converters (point of load converters) are installed in the rack units, ranging from 10 W to more than 200 W, for powering the low-voltage processors. The required voltage has decreased from the 5.0 V TTL logic in the mid-sixties, to 3.3 V for 5<sup>th</sup> generation processors in the mid-nineties, and down to 1.0 V in 2001 [54]. The current demand meanwhile has increased by a factor of 10 from 13 A for the 2.0-2.5 V 6<sup>th</sup> generation processors in 1996-98 to 100 A in 2001 [54]. Because of the highly dynamic loads requiring current slew rates of 100 A/µs and more, the load converters must be well-decoupled from the system, by providing fast regulators and high band-width control loops.

In a strict sense, almost all the energy provided by the local network is converted into heat in a data centre. The facility must be consequently cooled down to a reasonably low temperature allowing the devices to operate in the respective Safe Operating Area (SOA) and therefore, a system for Heating, Ventilation, and Air-Conditioning  $(HVAC)^7$  is necessary, which itself is a high-power consumer in the data centre. Besides the ICT-equipment, the HVAC system, as well as building establishment, like office spaces and lighting, are supplied by the alternator in case of a line breakdown.

Compared to the telecom facilities as depicted in **Fig. 1.7** the number of conversion stages between the local grid and the ICT-equipment is higher in the AC-bussed data centre cf. **Fig. 1.9**: three stages in the telecom facility and minimum of five stages in the AC-bussed data centre. The presented UPS system in **Fig. 1.9**, for instance, includes minimum of two conversion stages: the rectification of the AC-bus voltage to the battery intermediate circuit voltage and the inversion of the DC-voltage to the AC-bus. Both, rectifier and inverter carry there the entire load current during normal operation and consequently, this UPS system has a high share on the occurring losses. The different structures of UPS systems and their application areas are shortly discussed in the following section.

#### 1.3.3 Uninterruptible Power Supply (UPS) Systems

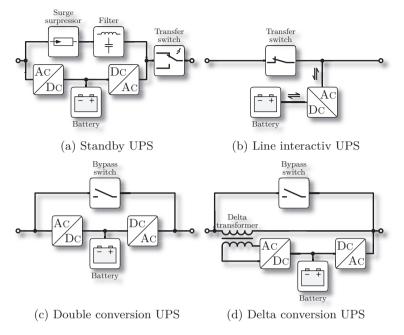

Mostly depended on the power level and required response time there are four main types of UPS systems as shown in **Fig. 1.10** [55, 56]:

- (a) Standby UPS

- (b) Line interactive UPS

- (c) Double conversion UPS

- (d) Delta conversion UPS.

In the following paragraphs the main UPS architectures are briefly introduced.

Standby UPS, cf. Fig. 1.10 (a), are commonly used for low power systems like for desktop computers. The inverter operates only in case of a line breakdown and the UPS provides therefore a high system efficiency. Additional filter structures enable an adequate noise reduction. A special form of the standby UPS is the **standby-ferro UPS**, where the transfer switch in Fig. 1.10 (a) is replaced by a transformer. This kind of UPS has been once dominant in the 3 to 15 kVA range [56], however, is not commonly used anymore because of the low efficiency

<sup>&</sup>lt;sup>7</sup>Common definitions are additionally Computer Room Air-Conditioning unit (CRAC) and/or Computer Room Air Handler (CRAH).

Figure 1.10: Schematics of the four main architectures of UPS systems.

and a fundamental instability when operating with modern computer  $\rm loads^8.$

Line interactive UPS, cf. Fig. 1.10 (b), is the most common design for web and department servers in the power range of 0.5 to 5 kVA and have a small share (approximately 19%) in the 20.1 to 50 kVA power range [55]. A bidirectional inverter is used for charging the battery and providing the uninterrupted power delivery to the ICT-equipment. This type of UPS provides a high efficiency (97 to 98%) over the entire load range [55] as the inverter only operates while charging the battery or during a line breakdown like the standard standby UPS.

**Double conversion UPS**, cf. **Fig. 1.10 (c)**, is the most common type in the power range above 10 kVA. Because the battery charger and

$<sup>^{8}</sup>$ The reason of the instability is the capacitive behaviour of the PFC-loads and the inductive behaviour of the PDU transformer which form a ringing circuit resulting in high currents [56]

the inverter both carry the entire power flow to the load, the resulting reliability and conversion efficiency of this UPS system is lower compared to e.g. standard standby UPS. However, the efficiency range of available double-conversion UPS systems is quite large because many manufacturers incorporate higher efficiency systems in their product range: 85% to 94% at 50% load and up to 95% at full load [56].

**Delta-conversion UPS**, cf. **Fig. 1.10** (d), is a relatively new system introduced by American Power Conversion Corp.  $(APC)^9$  in order to reduce the drawbacks of the double-conversion on-line design. The UPS systems are available in the power range of 5 kVA to 1.6 MVA with dual purposes: control of the input power characteristics, i.e. sinusoidal current and voltage waveforms, as well as harmonics reduction, and control of the input current, i.e. regulation of the battery charge [56]. The most important advantage of the delta conversion UPS are the significant reduction of the power losses: 96 % to 97 % at 50 % load and 97 % at full load.

For a 1-MVA data centre the efficiency gain of the delta-conversion UPS already results in 20 kW lower losses compared to the highestefficiency double-conversion UPS and thereby inherently an even higher facility efficiency because of the cooling effort reduction. That emphasises the high influence of the UPS system on the data centre efficiency and operation costs. A summary of the loss distribution in a typical data centre is given in the following in order to identify the important potentials for improvements.

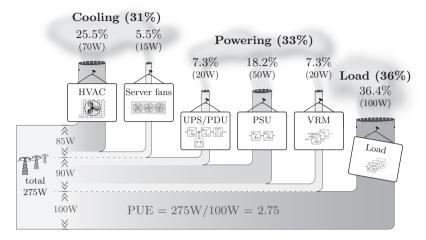

## 1.3.4 Typical Loss Distribution of Data Centres

The losses in the data centre, emerging because of non-ideal power conversion and the related cooling effort, are getting more and more a big concern of the operators as the energy bill for powering, cooling and lighting is up to one half of the total data centre costs (sum of energy bill, hardware and software costs) [40, 48, 57–59]. The typical loss distribution of a data centre with a PUE = 2.75 (according to equation (1.4)) is illustrated in **Fig. 1.11** referring to data presented in [47]<sup>10</sup>.

Almost a third of the supplied energy is used for the cooling system, cf. Fig. 1.11 [47]; for the system with a higher PUE = 2.13 as presented

<sup>&</sup>lt;sup>9</sup>Now part of Schneider Electric SA.

<sup>&</sup>lt;sup>10</sup>Approximately similar distributions can be found in [30, 48, 57].

**Figure 1.11:** Typical distribution of losses in today's data centres. (Data extracted from [47] for a data centre with a Power Usage Effectiveness, cf. (1.4), of PUE = 2.75.)

in  $[30]^{11}$  the loss-share of the cooling system is even higher: 23% for the chiller, 3% for the humidifier outside the facility and 15% for the CRAC/CRAH systems inside, which results in 41% of the total energy supplied to the data centre.

Further 7.3% of the supplied energy are used for the power conversion in the uninterruptible power supply and power distribution unit (approximately two third thereof in the UPS and one third in the PDU [57]). The power supply unit and load converters additionally consume one third of the total energy for the voltage conversion. Only approximately one third of the assimilated energy in **Fig. 1.11** is consequently available for the actual load: the ICT-equipment. A similar result is presented in the investigation of [48]: a 1U 300 W server rack unit requires a total power of  $P_{\text{tot}} = 973 \text{ W}$  to be operated.

Powering and cooling of servers accounted for 1.2% of the entire United States (U.S.) electricity consumption in 2005 [58]; the complete information and communication technology consumed 8% of the electricity – both in the European Union (2009 [51]) and in the U.S. (already in 1998 [47]). In consequence of the current data centre losses and the

$<sup>^{11}{\</sup>rm The}$  basis of this investigation has been a typical high-availability data centre operating at 30 % of the design capacity.

continuously increasing demand on ICT, there is an urgent need for action, making the power conversion with all the belonging contributors more efficient and thereby contributing in environment protection and additionally saving a high amount of money for the energy bill. In the following section, the challenges and possibilities for more efficient data centres are highlighted.

#### 1.3.5 "Go Green" - Challenges and Possibilities

Investigations in more efficient facilities have been especially expedited since the introduction and expansion of ISDN in the mid-eighties. Since then, the aspiration of the power supply manufactures has been the exaltation of the power density (e.g. [50]) in order to increase the cooling efficiency and counteract the rising space required for the digital equipment. The continuous demand on ICT, rising energy prices and increased ecological awareness, force the manufactures to provide further solutions for more efficient data centres. The challenges and possibilities for more "green" facilities are discussed in the following paragraphs.

**Power Density** Besides the improvements regarding competitiveness, marketing and room utilisation, developing and providing highpower-density equipment generally offers the technical advantage that compact systems can be cooled down more efficiently: the occupied area in the facility is smaller and thereby the cooling volume is decreased. Additionally, compact systems are providing shorter airflow paths, less air mixing, and higher heat rejection temperatures [57]. Today's applied rack units provide a power supply ranging from 2 to 6 kW [47, 48]; new High Density (HD) racks are available with 12 to 20 kW [48, 57], and the industry prediction is that the density will grow up to  $40 \,\mathrm{kW}$ per rack or cabinet in the next few years [48] resulting in an improved chiller efficiency and increased air conditioning capacity [57]. The efficiency exaltation by increasing the power density is coupled to physical limitations of the applied components. The efficiency border can be exceeded by increasing the efficiency of the installed IT and non-IT components and the advancements in power distribution as discussed below.

Cooling System (HVAC/CRAC/CRAH) The cooling system has major impact on the loss distribution as shown in Fig. 1.11. Besides the above mentioned reduction of the cooling volume, the energy required for facility air conditioning can be further decreased by reducing the heat generated in the computer room, i.e. by increasing the efficiency of the power conversion, and by developing and installing highly efficient HVAC systems. Furthermore, the cooling systems are usually over-dimensioned because of the complicate prediction of losses and to facilitate the possibility for extending the server room. New row-based cooling systems may be a good solution as investigated in [57]: for a data-centre-typical operation at 30 % of the rated load capability, the cooling effectiveness for the room cooling is approximately 66%, whereas the cooling effectiveness for the row-based cooling could be increased to 90 % [57]. Another reason for installing oversized HVAC systems is the necessity to cool down occurring hot-spots in the computer room to the specified maximum allowed temperature. An intelligent load distribution and load-depended variable speed drives for the fans are an arising solution for that challenge.

In many regions of the earth the promising opportunity exists of cooling the facility partly or even completely with outside air, as presented e.g. in [58]: if the outside air temperature is about 4 to  $6 \,^{\circ}$ C the chillers are shut down entirely and the resulting energy savings are 300 kW an hour (!); in [57] the estimated efficiency gain is 5 to 10 %.

The potential loss-reduction by an improved cooling system is up to 30% as shown in [30].

The fundamental power distribution method has a substantial influence on the data centre efficiency. As presented above, different approaches are pursued powering telecom facilities and data centres resulting in different structures, complexities and performances. The opportunities and challenges applying different bus structures (DC, AC, and High-Frequency (HF) AC), the respective waveforms and voltage levels are discussed in the following.

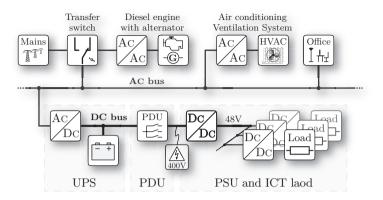

**DC-Powered Data Centres** Besides in telecom facilities, DC-power systems are deployed for instance in mainframe computers, space vehicles, the international space station, aircraft, ships, and radar stations [60]. In literature, e.g. [40, 47, 48, 57], very promising developments can be found suggesting data centres with a DC-bus as the better option for more efficiently powering the classical data centres

Figure 1.12: Schematic of a DC-powered data centre.

than with an AC-bus. The main advantages of DC-distributed facilities are based on the lower complexity of the supply chain as shown in **Fig. 1.12** which directly results in a decreased energy demand for the power conversion stages. Furthermore, the power density increases by 30% [40] and due to the resulting reduction of the cooling volume, the PUE is indirectly further improved.

The presented power savings in [40, 47, 48, 57], when shifting from AC- to DC-powered data centres, are between 13 and 35%, depending on the applied equipment and the utilisation of load capability. In addition to the cost-reduction for purchasing, installing, and maintaining the hardware, the energy bill can be drastically decreased<sup>12</sup>.

Approximately 10% of the service interrupts are caused by power supplies [41]. In consequence of a lower devices count the reliability of a system increases; therefore the MTBF of a typical AC-data centre is approximately 100'000 hours whereas DC-powered data centres achieve a seventy times higher MTBF of 7'000'000 hours [40].

In [47] a DC-powered data centre is introduced where the DC-bus voltage has been increased from the telecom-typical 48 V to approximately 400 V in order to counteract the continuously growing demand on power of the ICT equipment, cf. **Fig. 1.12**. Because of the decreased current in the bus bars, the conduction losses can be reduced and the

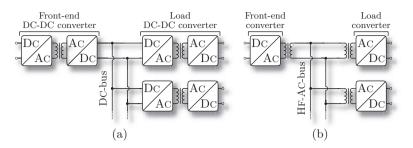

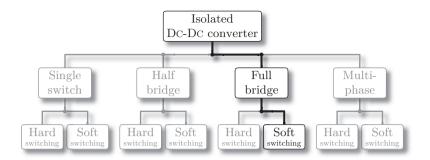

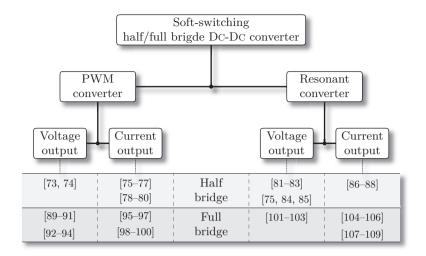

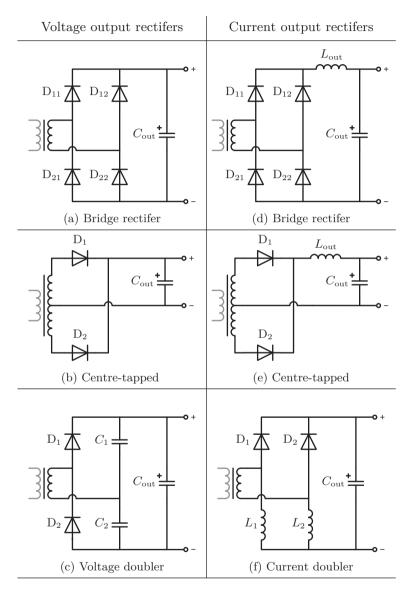

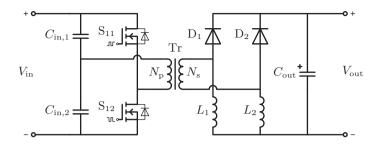

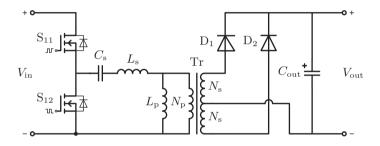

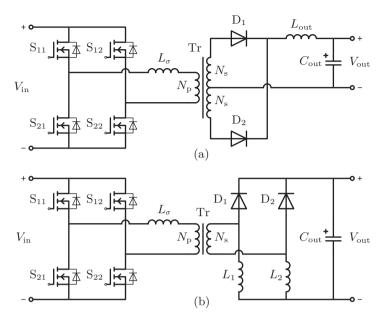

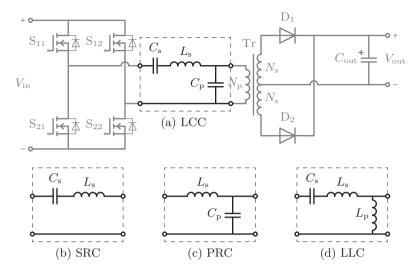

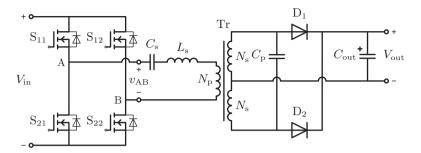

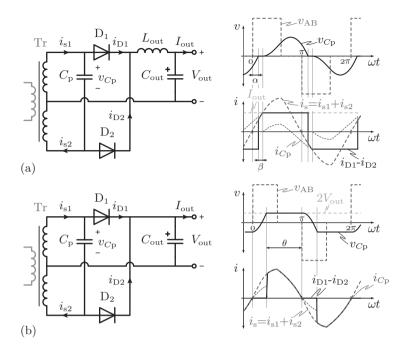

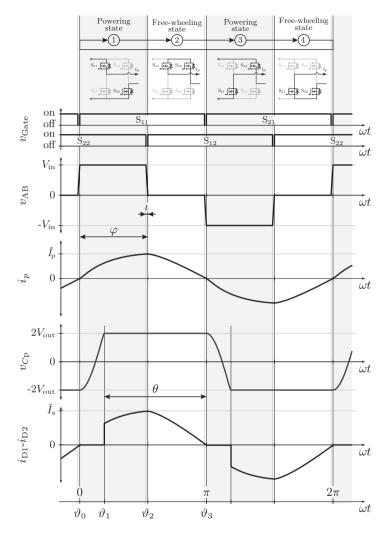

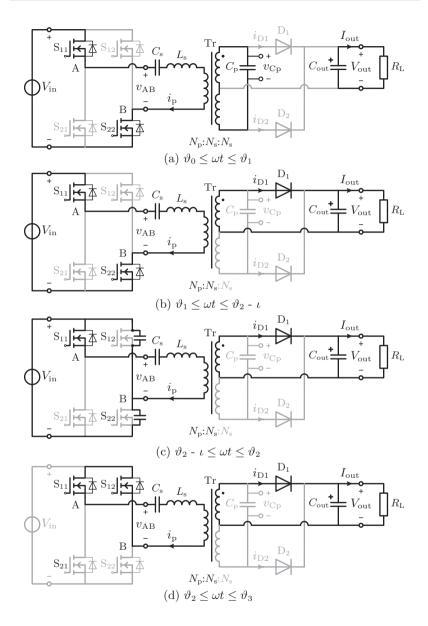

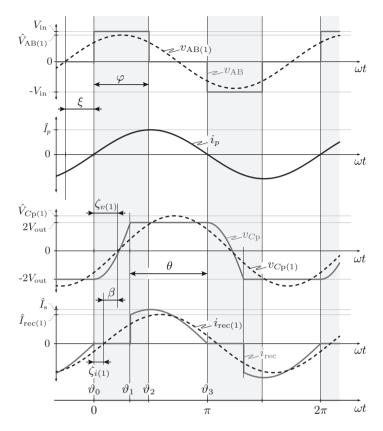

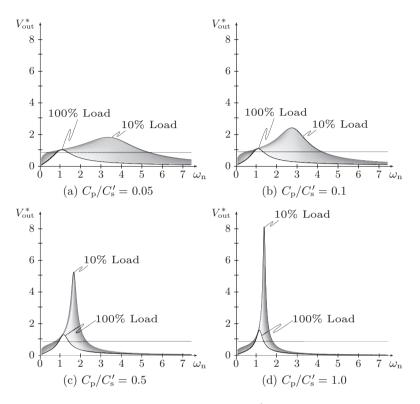

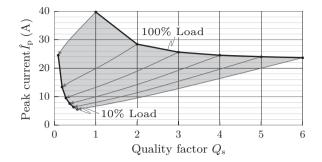

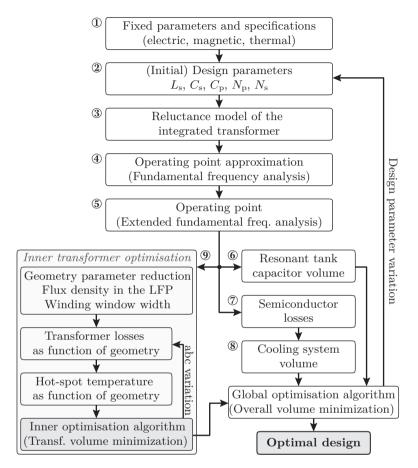

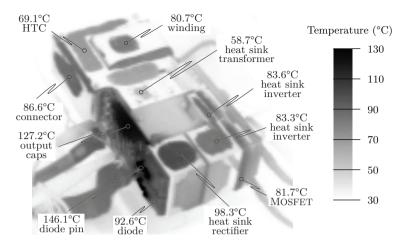

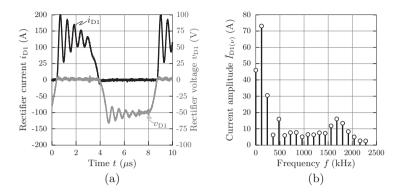

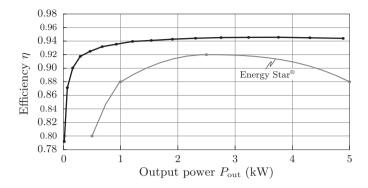

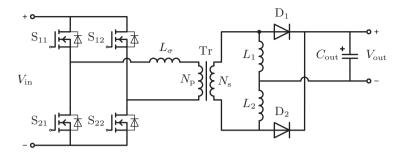

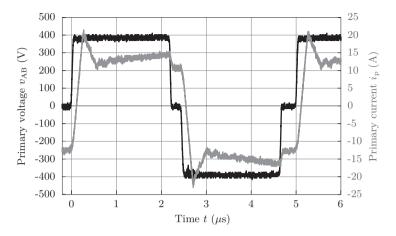

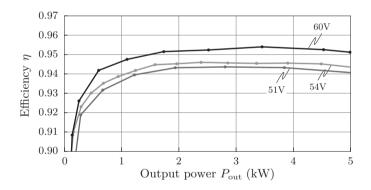

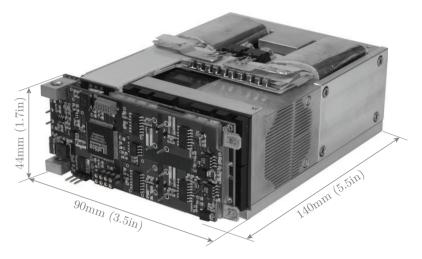

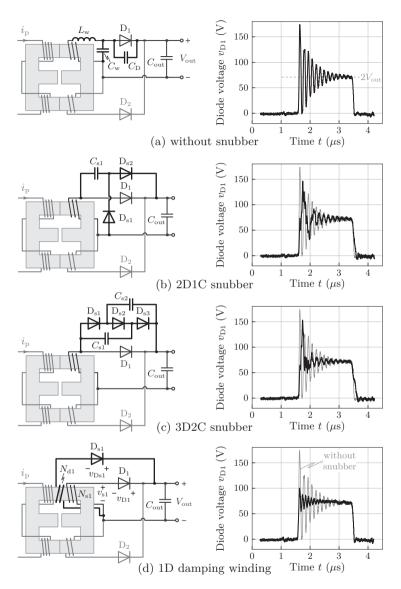

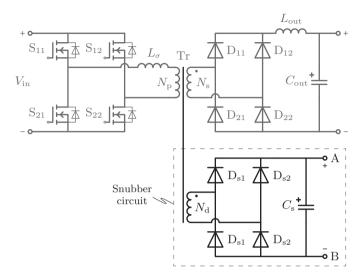

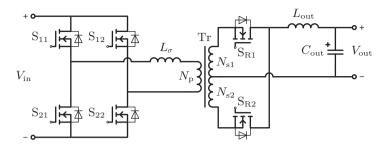

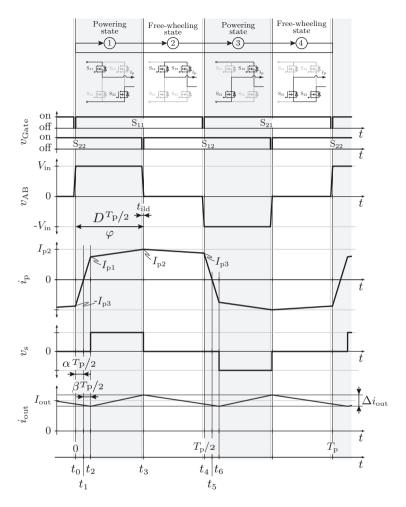

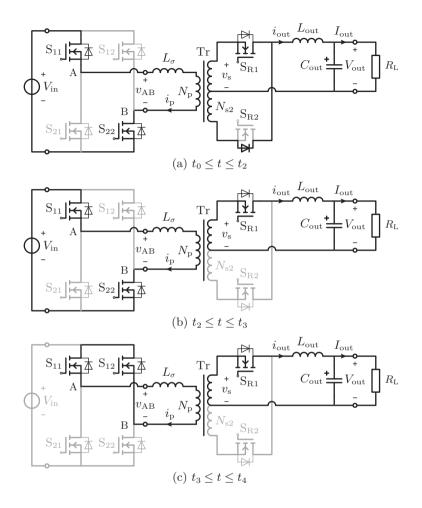

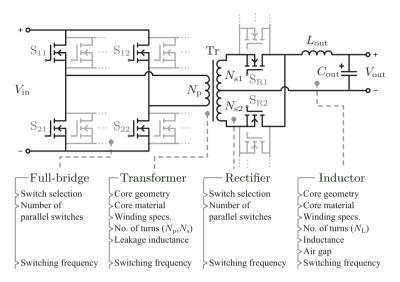

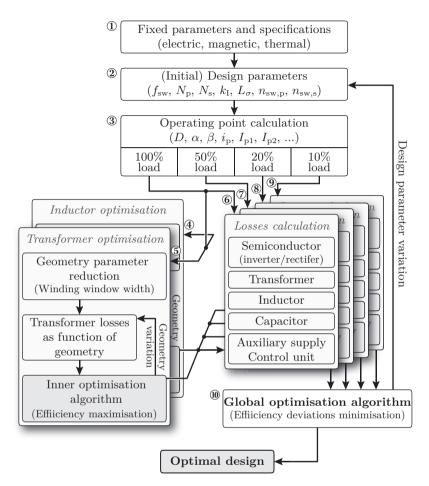

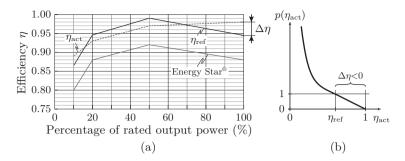

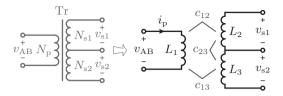

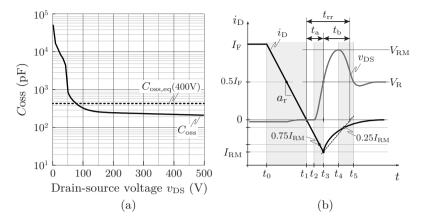

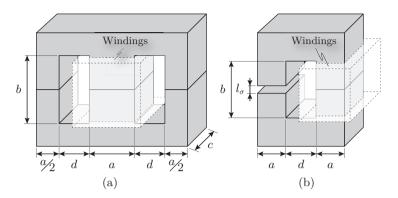

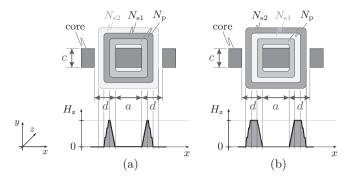

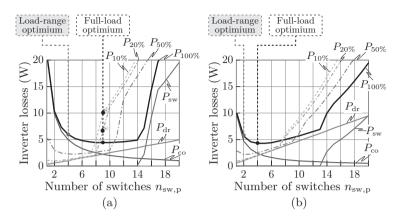

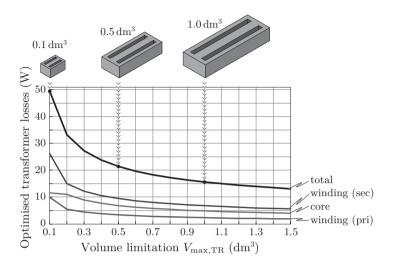

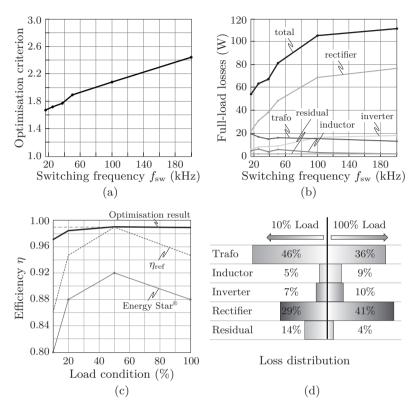

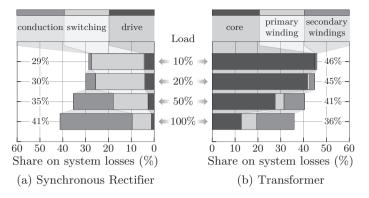

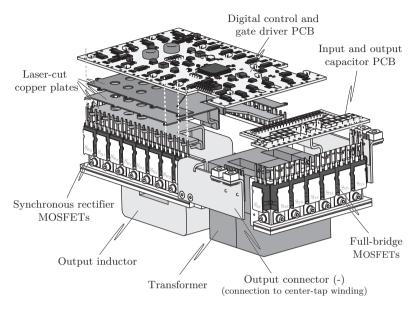

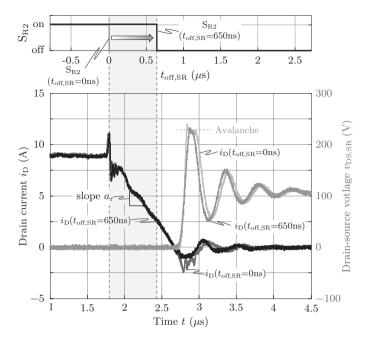

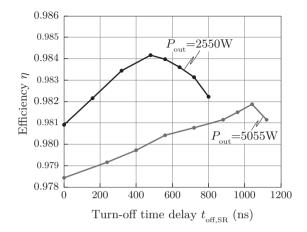

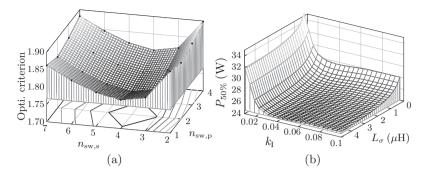

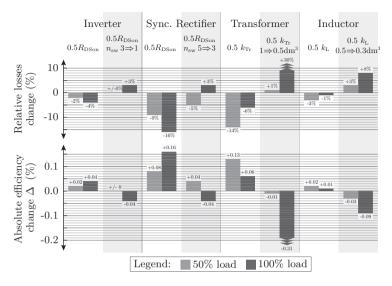

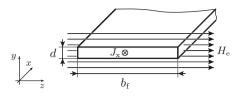

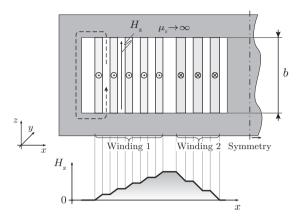

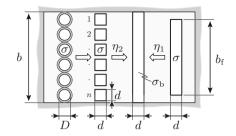

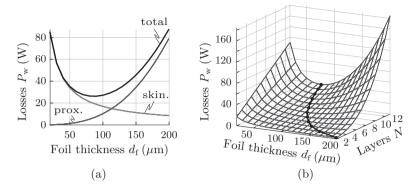

$<sup>^{12}</sup>$  Taking a 1-MW data centre operated at 50 % load capability and a key account price of CHF 0.15 per kW/h exclusive VAT as basis, the annual energy bill savings are around a quarter million CHFs!