# Comparison of Prediction Techniques to Compensate Time Delays Caused by Digital Control of a Three-Phase Buck-Type PWM Rectifier System

Thomas Nussbaumer, *Member, IEEE*, Marcelo Lobo Heldwein, *Student Member, IEEE*, Guanghai Gong, *Student Member, IEEE*, Simon D. Round, *Senior Member, IEEE*, and Johann W. Kolar, *Senior Member, IEEE*

*Abstract*—The digital control of a three-phase three-switch buck-type rectifier system is analyzed in this paper. Three main sources of time delays in the control loop can be identified for the implementation on a digital signal processor (DSP): 1) the delay time due to the sampling of the control quantities; 2) the one due to the calculation time of the DSP; and 3) the one due to the sample-and-hold function of the pulsewidth modulator. Using the buck-type system as an example, the influence of the time delay on the stability of the inner current control loop is discussed, and two prediction methods for time-delay compensation, i.e., a linear prediction and the Smith prediction, are comparatively evaluated. The control performance and the effect of the delay times and the prediction methods are shown by simulation results and through measurements on a 5-kW prototype.

*Index Terms*—Digital control, prediction techniques, pulsewidth modulation (PWM) rectifier, time-delay compensation.

# I. INTRODUCTION

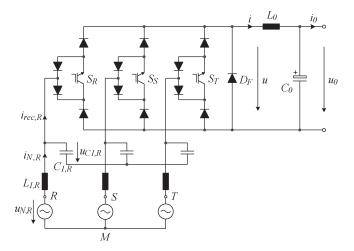

T HREE-PHASE buck-type pulsewidth modulation (PWM) rectifiers (cf. Fig. 1), which are frequently referred to as current source rectifiers, feature constant output voltage, sinusoidal input currents, unity power factor, direct start-up, and overcurrent protection in case of an output short circuit. Therefore, this topology is of high interest for the realization of front-end converters for telecommunications power supply modules, for applications in future More Electric Aircrafts, or as power supplies for process technology. By integration of the buck-type rectifier with a boost-type output stage [1], a wide input and/or output voltage range can be achieved, and sinusoidal input currents in phase with the input voltages can also be maintained in case of heavily unbalanced mains and/or in case of a mains phase loss.

Manuscript received September 1, 2005; revised September 12, 2007.

M. L. Heldwein, G. Gong, S. D. Round, and J. W. Kolar are with the Power Electronic Systems Laboratory, Swiss Federal Institute of Technology (ETH), CH-8092 Zurich, Switzerland.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2007.909061

Fig. 1. Topology of the three-phase buck-type PWM rectifier.

The control of this system has already been treated in the literature [1]–[4]; however, the influence of a digital realization has not been considered until now. The implementation of the control on a digital signal processor (DSP) is the current state of the art since it facilitates the integration of more functionality, the implementation of more complex control schemes, and high flexibility for changes of the program. On the other hand, digital signal processing always results in time delays, mainly due to three reasons:

- sampling of the continuous current and voltage quantities [5];

- 2) calculation time of the DSP [6];

- 3) PWM generation [7], [8].

Each of these time delays introduces a phase shift in the control loop, which reduces, in total, the achievable control bandwidth or diminishes the closed-loop system stability. To compensate for these time delays, two prediction methods are discussed and compared in this paper using the three-phase buck-type PWM rectifier as the design example.

In this paper, the prediction is only applied to the dc side current; however, in the physical rectifier implementation, the time-delay compensation method using prediction is also applied to the measured three-phase ac capacitor voltages.

791

T. Nussbaumer was with the Power Electronic Systems Laboratory, Swiss Federal Institute of Technology (ETH), CH-8092 Zurich, Switzerland. He is now with Levitronix GmbH, CH-8005 Zurich, Switzerland (e-mail: nussbaumer@lem.ee.ethz.ch).

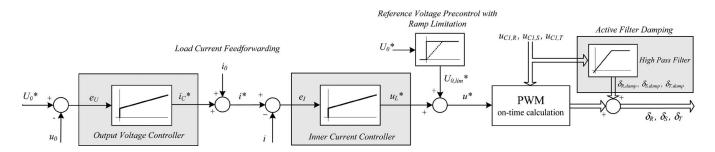

Fig. 2. Cascaded two-loop control structure for the buck-type PWM rectifier including load current feedforward, reference voltage precontrol, and an active damping of the input filter resonance.

The term "predictive control" covers a very wide field, and in the literature, many different control techniques including prediction methods have been presented [9], [10]. A classification of several predictive control techniques for inverter applications can be found in [11], a survey of linear and nonlinear control techniques for three-phase PWM converters can be found in [12], and current prediction methods for active power filters can be found in [13] and [14].

In the area of motor control, recent publications combine the well-known direct torque control [15], [16] with predictive control techniques by using the dynamic equations of the machine in order to predict and optimize the trajectory of the motor torque. This method leads to faster dynamic responses of the torque, as compared to the classical field-oriented control, and has been applied to permanent-magnet synchronous machines [17], SyncRel machines [18], and induction motors [19].

In power electronic applications, prediction techniques generally try to determine the path of the current vector (or the current error vector) at the beginning of the pulse period and to generate an appropriate voltage vector by PWM so as to minimize the predicted error. When the voltage vector is selected in order to null the error at the end of the pulse period, the predictive controller is usually called a deadbeat controller [10], [20], [21]. These prediction methods are based on a complete or simplified model of the plant in order to predict the future current. Well-known concepts are model predictive control [22] and generalized predictive control [23]. However, all of these methods require large computational resources, particularly, for more complex systems (high system order and/or nonlinear system behavior) and for high switching frequencies and/or short available calculation times. Hence, these techniques often cannot be employed in industrial applications, such as drive systems or switch-mode power converters.

For an industrial implementation, it is desirable to maintain a simple control concept that is straightforward to implement. This is also true in a digital implementation, where it is desired to compensate for time delays with techniques that also have low computational effort. Bibian and Hua [24] presented two predictive schemes, based on linear extrapolation, with low computational requirements to compensate for time delays of only one pulse period. They show that both methods result in an increase in the controller bandwidth. However, there has been no comparison of the performance and implementation effort of a model-based technique (Smith prediction [25]) with a simple linear extrapolation prediction method to compensate for time delays that are greater than one pulse period. In this paper, the time delays due to the DSP control are identified, and their effect on the stability is analyzed for a threeswitch buck-type PWM rectifier in Section II; a basic control structure of the rectifier is also presented and explained briefly. The delay times that occur due to the digital computation are analyzed in Section III. In Section IV, two prediction methods for compensating the time delays, i.e., a linear extrapolation prediction technique and the Smith prediction method, are presented, and their performance is shown by simulation results in the time domain. At the end of Section IV, a comparative evaluation regarding effectiveness, robustness, and implementation effort of the two prediction methods is given. Finally, in Section V, measurement results on a 5-kW hardware prototype show the effect of the time delays and the performance improvement by using the proposed linear prediction technique.

# **II. CONTROL STRUCTURE**

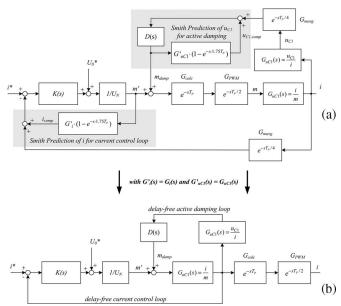

In Fig. 2, a basic control structure of the buck-type rectifier is depicted. An outer control loop regulates output voltage  $u_0$ to a constant reference value  $U_0^*$  and sets reference value  $i^*$ for the inner dc current loop. The use of the feedforward of load current  $i_0$  decreases the variation of the output voltage in the case of load changes. The output  $u_L^*$  of the inner current controller has a precontrol of the rate-limited reference output voltage  $U_{0,\lim}^*$  in order to improve the large-signal behavior of the controller in case of a start-up. The relative on-times  $\delta_i$  (where index *i* denotes the three phases i = R, S, T) of the three power transistors  $S_i$  are calculated by the DSP according to the required output voltage  $u^*$  and the actual input voltages  $u_{C1,i}$ . To achieve sinusoidal input currents, several modulation methods that can be optimized to achieve minimum switching losses, minimum current ripple, or minimum distortion of the mains currents [26] have been developed [1]. Independent of the utilized modulation method, the conduction times of the three buck transistors are

$$\alpha_i = \frac{2}{3} \cdot \frac{u^*}{\hat{U}_{C1}^2} \cdot |u_{C1,i}| \tag{1}$$

in order to adjust the fundamental component [denoted by the index (1)] of the input currents  $i_{\text{rec},i,(1)}$  of the three phases that are proportional to the input voltages  $u_{C1,i}$ , which are given by

An active damping scheme, which is explained in detail in [4], is additionally employed in order to damp the resonance of the input filter. Therefore, for this control scheme, output voltage  $u_0$ , dc current *i*, and at least two of the input filter capacitor voltages  $u_{C1,i}$  have to be measured. The output voltage loop usually is very slow; therefore, the measurement of the output voltage is not time critical, whereas, for the fast inner loop, eventual delays in the detection and calculation of the current and the voltages can decrease the control performance, as will be shown in the next section.

## **III. ANALYSIS OF SYSTEM DELAYS**

The following considerations are based only on the analysis of the time delays that are associated with inductor current *i*. However, for the dynamics of the inner current control loop considering active damping (Section II), the derivation of the delay times of the filter capacitor voltages  $u_{C1,i}$  needs to be considered. The analysis is similar, and the same conclusions can be drawn; therefore, only the inductor current time delays are considered for the sake of brevity.

The selection of the switching frequency is always a crucial part of the converter design. On one hand, it significantly influences the efficiency and the power density of the system; on the other hand, the time delays introduced by the digital control are minimized for lower switching frequencies.

In [27], it was found that, for the buck-type rectifier topology (cf. Fig. 1), a switching frequency in the range of  $f_P =$ 20-30 kHz leads to a good compromise between efficiency (switching losses) and power density (volume). For the rectifier considered in this paper, a switching frequency of  $f_P =$  $1/T_P = 28$  kHz is selected.

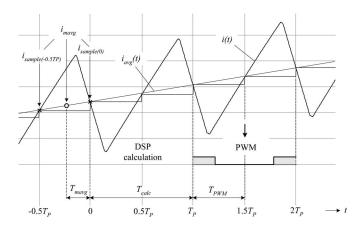

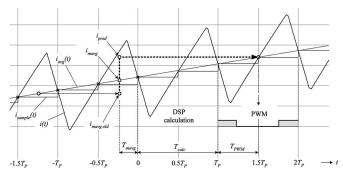

The measurement of the dc current is performed by a magnetoresistive Sensitec CMS 2025 dc current sensor [28]. The DSP [29] has a 20-Msample/s 14-bit analog-to-digital converter, and therefore, the conversion delay can be neglected. Furthermore, the effect of the time delay of the switches [30] is not considered due to the comparatively low switching frequency. As shown in Fig. 3, the samples are taken every half pulse period exactly at the middle and at the end/beginning of each pulse interval (in Fig. 3, this is explicitly shown for  $t = -0.5T_P$  and t = 0). If a symmetric triangular carrier is used for the PWM generation, the samples at these time instants ideally do not contain any switching frequency components and therefore should be identical to the local average values of the current  $i_{avg}(t)$  (cf. Fig. 3 at  $t = -0.5T_P$  and t = 0).

However, in order to improve the robustness of the measurement result against inaccuracies in the current acquisition, an additional moving average function of second order is employed. The transfer function of this filter is given by

$$G_{\text{mavg}} = \frac{1}{2} (1 + e^{-sT_P/2}).$$

(3)

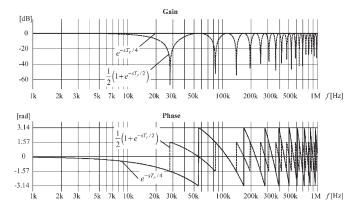

The effect of this filter is depicted in Fig. 4. It can be seen that the switching frequency and its higher harmonics are perfectly suppressed, whereas the magnitude of lower frequencies (< 5 kHz) is not essentially affected by this operation.

Fig. 3. Delays occurring due to current acquisition (two-times oversampling and moving averaging of inductor current i), DSP calculation, and PWM generation. The current is sampled two times within one pulse period (at the middle and at the beginning and/or end of each period), and the moving average function introduces a delay of  $0.25 T_P$ . Due to the calculations of the control commands, and on-times, a delay of one full pulse period occurs. Additionally, the sample-and-hold function of the PWM causes a half-pulse-period delay, therefore resulting in total delay of  $1.75 T_P$ .

Fig. 4. Bode diagram of the transfer function of a moving averaging operation of second order (3) in comparison with the approximated transfer function of a delay of  $0.25 T_P$  (4).

For lower frequencies, the moving averaging function can be approximated with good accuracy as a delay of a quarter pulse period

$$G_{\rm mavg} \approx e^{-sT_P/4}$$

(4)

which is proven in Fig. 3, where the moving average value  $i_{\text{mavg}}$  occurs at  $-0.25T_P$ . Fig. 4 also shows the good agreement of the magnitudes of (3) and (4) up to 10 kHz and of the phase until switching frequency  $f_S = 28$  kHz.

For the calculation of the actual input voltage sector and/or relation of the input phase voltages, which determines the switching states employed for forming the input current, the control commands, and the calculation of the relative on-times of the PWM outputs, one pulse period is reserved (cf. Fig. 3), therefore generating an additional delay of

$$G_{\text{calc}} \approx e^{-sT_P}.$$

(5)

In the subsequent pulse period, the PWM pulse pattern, which was generated by the relative on-times  $\delta_i$  that have been previously calculated, is applied to the system. In [8], it is

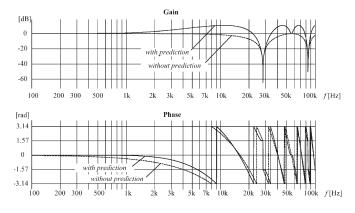

Fig. 5. Influence of the linear prediction (8) on the magnitude and phase of the delay transfer function (7).

shown that a modulator with instantaneous sampling, e.g., for analog control, has zero phase lag. Compared to this, the system at hand performs a sample-and-hold function, thus keeping the values of  $\delta_R$ ,  $\delta_S$ , and  $\delta_T$  constant for one whole pulse period.

As can be proven by simulations and/or analytical calculations, this introduces an additional delay time of a half pulse period,

$$G_{\rm PWM} = e^{-sTp/2} \tag{6}$$

which is valid if the PWM is updated only once per pulse period. For a double update mode, the delay time introduced by the PWM operation is reduced to a quarter pulse period [5].

The resolution of the PWM output of the DSP (12.5 ns) and the delay time of the utilized gate driver (200 ns) are small and can therefore be neglected. Accordingly, the total transfer function of the digital processing of the DSP is

$$G_{del} = G_{mavg} \cdot G_{calc} \cdot G_{PWM}$$

=  $\frac{1}{2} (1 + e^{-sT_P/2}) \cdot e^{-s \cdot 1.5T_P}$

$\approx e^{-s \cdot 1.75T_P}.$  (7)

## **IV. PREDICTION METHOD**

### A. Linear Prediction

The sampling, digital processing, and pulsewidth modulation introduce a large phase shift, e.g.,  $\varphi = \pi/2$  at f = 4 kHz (cf. Fig. 5). For a purely integral plant and a proportional controller, this would already represent the maximum bandwidth on the border of instability. For a conservative controller design, the maximum loop bandwidth would be limited to f = 1 kHz.

A possible way to compensate the delay-time effect is a linear prediction of the forthcoming current values. This method works without knowledge of the system that is being controlled and simply predicts the future value by a linear function based on the past values. As a first step, the total average delay time has to be calculated. From (7) and as shown in Fig. 6, an average delay time of 1.75  $T_P$  occurs between point  $t = -T_{mavg} = -0.25T_P$  where the value  $i_{mavg}$  would occur without ripple (which provides the basis for the calculation of the relative

Fig. 6. Linear prediction of the forthcoming current value in order to compensate the delays due to the digital signal processing.

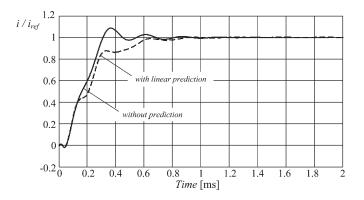

Fig. 7. Effect of the linear prediction of the dc current, shown for the step responses of the inner current control loop.

on-times for the PWM) and the point when the PWM pattern becomes effective for the rectifier  $T_{calc} + T_{PWM} = 1.5T_P$ .

The discrete transfer function that has to be calculated in the DSP can be derived as

$$G_{\rm pred}(z) = \frac{i_{\rm pred}}{i_{\rm mavg}} = 2.75 - 1.75z^{-1}$$

(8)

and therefore expressed in difference equation format

$$i_{\text{pred},k} = 2.75 \cdot i_{\text{mavg},k} - 1.75 \cdot i_{\text{mavg},k-1}$$

(9)

which has a derivative behavior. The effect of the prediction in combination with the total transfer function of the digital processing, as previously described [cf. (7)], can be viewed in Fig. 5. The phase is increased by nearly  $\Delta \varphi = \pi/4$  between 1 and 10 kHz, resulting in higher control bandwidth and/or stability of the inner control loop. The magnitude in this frequency band is increased by up to 6.5 dB; therefore, the current controller gain can be lowered accordingly in the design step, compared to a system without prediction.

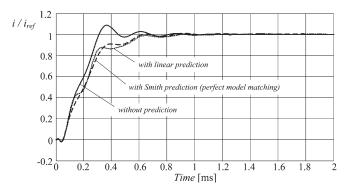

The effect of the prediction on the current can be seen in the step response of the inner current control loop, as depicted in Fig. 7. As previously described, the system stability is improved, and/or the current overshoot is reduced; the inner control bandwidth is kept the same.

Since a sudden step of the load condition directly changes the current reference value, the prediction also improves the load disturbance behavior. In the same way, this method can be utilized for the prediction of the input filter capacitor

Fig. 8. Principle of the Smith prediction: (a) general structure of the prediction method and (b) equivalent circuit showing that the delay is removed from the control loop.

voltages  $u_{C1,i}$ . With this, the disturbance rejection of the inner loop can also be improved for disturbances coming from the mains side.

#### B. Smith Prediction

A more advanced prediction method that includes a model of the plant has been first presented in [25]. This so-called Smith prediction is briefly described and applied to the bucktype rectifier system.

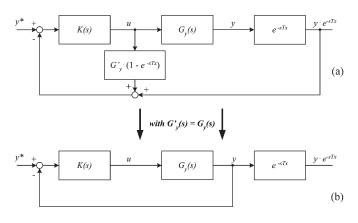

Generally, as depicted in Fig. 8(a), the feedback of a control variable y including a total delay time  $T_x$  is changed according to

$$y' = y \cdot e^{-sT_x} + (1 - e^{-sT_x}) \cdot u \cdot G'_y(s)$$

(10)

where  $y \cdot e^{-sTx}$  is the control variable containing delay  $T_x$ , u is the controller output, and  $G'_y(s)$  is the model of the plant. As shown in Fig. 8(b), for the ideal case wherein  $G'_y(s) = G_y(s)$ , the delay is moved outside of the plant that is seen by the controller; therefore, the controller can be designed for considerably higher bandwidth and stability.

For the buck-type rectifier system, a prediction of both the dc current in the control feedback path and the capacitor voltages in the active damping path has to be considered. In Fig. 9(a), the block diagram of the inner control loop including the Smith prediction feedback terms is depicted. Analogous to Fig. 8(b), the delay-free loops are shown in Fig. 9(b).

As shown in Fig. 9(a), it is necessary to evaluate the signals

$$i_{\rm comp} = G'_i \cdot (1 - e^{-s \cdot 1.75T_P}) \cdot m'$$

(11)

and

$$u_{C1,\text{comp}} = G'_{uC1} \cdot (1 - e^{-s \cdot 1.75T_P}) \cdot m_{\text{damp}}$$

(12)

inside the DSP at every calculation step in order to compensate for the total delay time of 1.75  $T_P$ . Therefore, the transfer functions  $G'_i$  and  $G'_{uC1}$  have to be identified, which can be performed by ac analysis of the linearized single-phase model of the system [31] for an operating point. With this,  $G'_i$  and

Fig. 9. (a) Block diagram of the inner current loop including the Smith prediction feedback for the dc current and the input capacitor voltage. (b) Equivalent circuit for a perfect model of the plant utilized in the feedback functions.

$G'_{uC1}$  are obtained as transfer functions in the *s*-domain. By using, for example, the Tustin transformation

$$s = \frac{2}{T_P} \cdot \frac{1 - z^{-1}}{1 + z^{-1}}.$$

(13)

$G'_i(s)$  and  $G'_{uC1}(s)$  are transformed into the time-discrete z-domain functions  $G'_i(z)$  and  $G'_{uC1}(z)$ , respectively. Using the system parameters and the operating point (nominal input voltage and rated output power) given in the Appendix,  $G'_i(z)$  is given by

$$G'_{i}(z) = \frac{i}{m'} = 3.56 \cdot \frac{1 - 0.35z^{-1} - 0.33z^{-2} + 1.02z^{-3}}{1 - 2.15z^{-1} + 2.02z^{-2} - 0.86z^{-3}}.$$

(14)

Therefore, based on the model  $G'_i(z)$ , the calculated current value  $i_k$  of calculation step k can be given in a difference equation form by

$$i_{k} = 3.56 \left( m'_{k} - 0.35m'_{k-1} - 0.33m'_{k-2} + 1.02m'_{k-3} \right) + 2.15i_{k-1} - 2.02i_{k-2} + 0.86i_{k-3}.$$

(15)

Accordingly, the current value delayed by 1.75  $T_P$  is derived by

$$i_{k-1.75} = 3.56 \left( m'_{k-1.75} - 0.35m'_{k-2.75} - 0.33m'_{k-3.75} + 1.02m'_{k-4.75} \right) + 2.15i_{k-2.75} - 2.02i_{k-3.75} + 0.86i_{k-4.75}.$$

(16)

With (14)–(16), (11) can be evaluated at each calculation step k by

$$i_{\text{comp},k} = i_k - i_{k-1.75}.$$

(17)

However, despite this technique seeming to be promising, three problems are associated with the practical implementation.

First, the computational effort is quite high since, in addition to (15)–(17), the appropriate compensation signals for the filter capacitor voltages for two of the three phases, e.g., *R* and *S*, i.e.,

$$u_{C1,R,\text{comp},k} = u_{C1,R,k} - u_{C1,R,k-1.75}$$

(18)

$$u_{C1,S,\text{comp},k} = u_{C1,S,k} - u_{C1,S,k-1.75}$$

(19)

have to be derived in every calculation step in the DSP. The third compensation signal is then given by the relation

$$u_{C1,T,\text{comp},k} = -u_{C1,R,\text{comp},k} - u_{C1,S,\text{comp},k}.$$

(20)

2) Second, the current, voltage, and modulation index values are not available at noninteger time instants, e.g.,  $i_{k-2.75}$ . Therefore, either these values have to be approximated by linear interpolation of the nearby sampled values or the sampling method has to be adapted. For example, the sampling instants at  $t = 0.25T_P$  and  $t = 0.75T_P$  would have to be selected, resulting in a total delay of  $T_x = 2T_P$ . With this, the equation

$$i_{k-2} = 3.56 \left( m'_{k-2} - 0.35m'_{k-3} - 0.33m'_{k-4} + 1.02m'_{k-5} \right) + 2.15i_{k-3} - 2.02i_{k-4} + 0.86i_{k-5} \quad (21)$$

could be calculated. However, the current ripple suppression would then be reduced for this sampling method.

3) The parameters in (15) and (16), given for a specific operating point, are strongly dependent on the operating variables, such as input voltage and output power. Additionally, the inductor values are dependent on the actual inductor current, and the capacitors values are usually only given within a tolerance range. Since the effect of the prediction is strongly dependent on the accuracy of the model, the inaccuracies in the model that always occur have a large influence on the control performance. This problem can only be solved by adapting the model of the plant, according to (14), to the actual operating point, which would further increase the computational effort of this method, unless operating-point-dependent lookup tables are utilized.

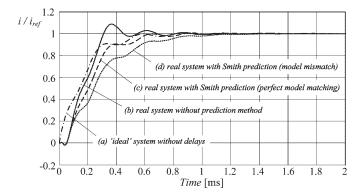

In Fig. 10, the effect of the Smith prediction on the inner current loop step response is illustrated. For the ideal case of a perfect match of the model and the plant  $G'_i = G_i$  and  $G'_{uC1} = G_{uC1}$ , the step response [Fig. 10(c)] is only delayed by 1.75 pulse periods, compared to a system containing no delays [Fig. 10(a)]. As compared to the step response of the controlled system without prediction [Fig. 10(b)], the reference tracking performance is obviously improved. However, if the model that has been calculated for the nominal operating point, e.g., (14), is utilized for another operating point (in the case at hand,  $P_{\text{out}} = 1 \text{ kW}$ , and  $U_{N,l-l,\text{rms}} = 440 \text{ V}$ ) due to the mismatch of the model, the performance of the real system is significantly decreased, and the step response is much slower [Fig. 10(d)].

Fig. 10. Influence of the Smith prediction for perfect and simplified modeling of the plant, shown for the step responses of the inner current control loop.

Fig. 11. Comparison of the linear prediction and the Smith prediction, shown for the step responses of the inner current control loop.

Fig. 12. Five-kilowatt prototype of the buck-type rectifier including a DSP control board and electromagnetic compatibility input filter. Overall dimensions:  $240 \text{ mm} \times 160 \text{ mm} \times 120 \text{ mm}$ .

## C. Comparison of the Prediction Methods

For the compensation of the time delays, the effort involved for the implementation of the Smith prediction method is much higher compared to the linear prediction method and cannot be justified by better performance. The Smith prediction method was originally developed for simple plants of loworder systems; however, buck rectifier systems with the input and output filters apparently do not fulfill this requirement. Therefore, the calculations for predicting the currents and

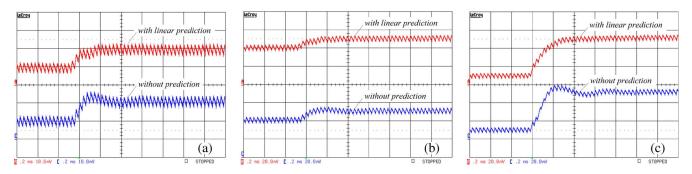

Fig. 13. Current waveforms of the closed-loop system for steps in the current reference (performed by load steps): (a) 2-4 A (current scale: 2 A/div, time scale: 200  $\mu$ s/div), (b) 8-10 A (current scale: 4 A/div, time scale: 200  $\mu$ s/div), and (c) 2-10 A (current scale: 4 A/div, time scale: 200  $\mu$ s/div).

voltages become complex and time consuming. Furthermore, uncertainties in the model and deviations from the operating point significantly decrease the performance of the prediction.

In contrast, the linear prediction is an easy and robust method, which forecasts a future state variable based on two sampled values. The knowledge of the model of the system to be controlled is not required; hence, this technique is suitable for any operating point and is very robust against parameter variations. The only information that is required is the total delay time introduced by the digital control. The system dynamics are implicitly included in the linear prediction by the sampled state variables; however, the trajectories are simplified by linear approximations. Therefore, it is clear that this method is only valid if the characteristic system dynamics are significantly slower than the delay time that has to be compensated. This condition is usually fulfilled for switch-mode power supplies due to the fact that the cutoff frequencies of the input and output filters usually lie well below the switching frequency in order to sufficiently smooth the switching frequency ripple values. For the buck-type rectifier considered, the cutoff frequency of the input filter (parameters given in the Appendix) lies at  $f_{c,in} = 3.9$  kHz, and the cutoff frequency of the output filter at  $f_{c,out} = 130$  Hz and is therefore sufficiently below  $1/(1.75T_P) = 16$  kHz. As long as this condition is fulfilled, the linear prediction can be applied in the same manner to other topologies, such as voltage source inverters or single-phase power factor corrections.

In Fig. 11, the small-signal step responses of the inner current control loop are shown for the two prediction methods. Even assuming perfect matching of the model that is used in the Smith prediction method with the system to be controlled, the performance is not improved compared to the linear prediction. Therefore, to compensate for the time delays of the system, the implementation of the linear prediction of the dc current and the input capacitor voltages without explicit knowledge of the system to be controlled is sufficient and reasonable in terms of performance and implementation effort. Therefore, only the linear prediction method has been implemented and experimentally tested in a hardware prototype of the system. The experimental results that prove the effectiveness of the linear prediction technique are presented in the next section.

# V. EXPERIMENTAL VERIFICATION

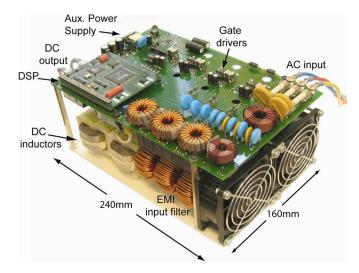

The proposed control structure is implemented in software on a custom Analog Devices ADSP-21991 160-MIPS DSP board

and tested on a 5-kW hardware prototype of the system (cf. Fig. 12). The two-times oversampling, averaging, DSP control, and PWM generation, as presented in Section III, are implemented with the C software language. The rectifier switching frequency is 28 kHz, and therefore, the maximum time allowed for the processing of the control code is 35.7  $\mu$ s. The total processing time for the oversampling, rectifier control, and active damping, excluding the prediction methods, is 29.7  $\mu$ s. The 32-bit precision implementation of the time-delay compensation calculations by linear prediction requires only 0.4  $\mu$ s of computation time, compared to the 9.3  $\mu$ s for the Smith prediction implementation, which is a processing time increase of 23 times. The additional computation time required to perform the Smith prediction is not justified, as there is no performance enhancement, as shown by simulation, and the inclusion of the Smith prediction calculation causes the total interrupt processing time to exceed the switching frequency period, thus resulting in a nonreal-time implementation. Therefore, only the experimental results for the linear prediction method are presented.

From Fig. 13, it can be seen for step load changes that the linear prediction method, as proposed in Section IV, increases the stability of the system, due to the compensation of the phase shift introduced by the delay times occurring in the digital system, compared to the case without prediction. Fig. 13(a) shows the response of the dc current for a small step of the current reference in the lower power range (2-4 A), whereas Fig. 13(b) shows the current waveforms for a small step in the upper power range (8-10 A); in Fig. 13(c), a large current load step has been performed from 2 to 10 A. These three current load steps show that the proposed linear prediction method works well over the whole modulation range and is not sensitive to parameter variations. To achieve the same overshoot-free step response of the system without the prediction method, the gain of the inner current controller would have to be reduced, thus causing a decrease in the bandwidth of the current control. Therefore, it could be shown that the stability of a system including delay times is improved by the linear prediction of the control quantities while the system control bandwidth is maintained.

#### VI. CONCLUSION

The digital control of a three-phase rectifier system is analyzed in this paper. First, the origins of relevant time delays in the control loop are found to be caused by the sampling of the control quantities, the calculation time of the control program in the DSP, and the sample-and-hold function of the PWM modulator. For the three-phase buck-type rectifier, these time delays introduce a large phase shift of nearly  $\varphi = \pi/2$  at one decade below the switching frequency, and this reduces the phase margin and stability and, therefore, the achievable bandwidth of a controller. In order to reduce this phase shift, two prediction methods, i.e., a linear prediction and the Smith prediction, are analyzed and compared.

The Smith prediction ideally completely compensates the delay times but requires a precise model of the system to be controlled and therefore results in a high implementation effort. The performance of this prediction technique is highly sensitive to the accuracy of the modeling; in contrast, the linear prediction method cannot completely compensate the introduced phase shift, but it does not require any information about the model and is therefore characterized by a significantly lower implementation effort. Furthermore, the linear prediction is not sensitive to parameter variations and deviations from the nominal operating point. Taking this into account, it is concluded that, for a system with high system order (due to the complex model)—as it is usually the case for converter systems with input and output filters-the effort of a Smith prediction is not worthwhile compared to the use of the linear prediction method. Measurements on a hardware prototype verify that the linear prediction method clearly increases the stability of the system by counteracting the delay times introduced by the digital control.

# APPENDIX System Operating Parameters

$$P_{\text{out}} = 1 - 5 \text{ kW}$$

$P_{\text{out,nom}} = 5 \text{ kW} \text{ (rated output power)}$

$U_{N,l-l,\text{rms}} = 320 - 440 \text{V}$

$U_{N,l-l,\mathrm{rms,nom}} = 400 \mathrm{V} \text{ (nominal input voltage)}$

$$U_{out} = 400 \text{ Vdc}$$

$f_P = 28 \text{ kHz}$

$L_{1,i} = 240 \mu \text{H}$

$C_{1,i} = 6.8 \mu \text{F}$

$L_0 = 2 \text{ mH}$

$C_0 = 750 \mu \text{F}.$

#### REFERENCES

- M. Baumann, U. Drofenik, and J. W. Kolar, "New wide input voltage range three-phase unity power factor rectifier formed by integration of a three-switch buck-derived front-end and a DC/DC boost converter output stage," in *Proc. IEEE-INTELEC*, 2000, pp. 461–470.

- [2] G. D. Marques, "A PWM rectifier control system with DC current control based on the space vector modulation and AC stabilisation," in *Proc. IEEE-ISIE*, 1997, pp. 318–322.

- [3] D. J. Tooth, "The behavior and analysis of a three-phase AC-DC stepdown unity power factor converter," Ph.D. dissertation, Dept. Comput. and Elect. Eng., Heriot-Watt Univ., Edinburg, U.K., 1999.

- [4] T. Nussbaumer and J. W. Kolar, "Comparative evaluation of control techniques for a three-phase three-switch buck-type AC-to-DC PWM con-

verter system," in *Proc. 3rd IEEE Nordic Workshop Power Ind. Electron.*, Stockholm, Sweden, Aug. 12–14, 2002, CD-ROM.

- [5] V. Blasko, V. Kaura, and W. Niewiadomski, "Sampling of discontinuous voltage and current signals in electrical drives: A system approach," *IEEE Trans. Ind. Appl.*, vol. 34, no. 5, pp. 1123–1130, Sep./Oct. 1998.

- [6] S. Zheng and D. Czarkowski, "Modeling and digital control of a phasecontrolled series-parallel resonant converter," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 707–715, Apr. 2007.

- [7] D. M. Mitchell, "Pulsewidth modulator phase shift," *IEEE Trans. Aerosp. Electron. Syst.*, vol. AES-16, no. 3, pp. 272–278, May 1980.

- [8] R. D. Middlebrook, "Predicting modulator phase lag in PWM converter feedback loops," in *Proc. Powercon 8*, Dallas, TX, 1981, pp. H-4.1–H-4.6.

- [9] J. Holtz and S. Stadtfeld, "A predictive controller for the stator current vector of ac machines fed from a switched voltage source," in *Proc. IPEC Conf. Rec.*, Tokyo, Japan, 1983, pp. 1665–1675.

- [10] D. G. Holmes and D. A. Martin, "Implementation of a direct digital predictive current controller for single and three phase voltage source inverters," in *Conf. Rec. IEEE IAS Annu. Meeting*, 1996, vol. 2, pp. 906–913.

- [11] R. Kennel and A. Linder, "Predictive control of inverter supplied electrical drives," in *Proc. IEEE Power Electron. Spec. Conf.*, 2000, vol. 2, pp. 761–766.

- [12] M. P. Kazmierkowski and L. Malesani, "Current control techniques for three-phase voltage-source PWM converters: A survey," *IEEE Trans. Ind. Electron.*, vol. 45, no. 5, pp. 691–703, Oct. 1998.

- [13] S. Buso, L. Malesani, and P. Mattavelli, "Comparison of current control techniques for active filter applications," *IEEE Trans. Ind. Electron.*, vol. 45, no. 5, pp. 722–729, Oct. 1998.

- [14] A. Dell'Aquila, A. Lecci, and M. Liserre, "A comparison between two predictive controllers for single-phase active filter," in *Proc. IEEE IECON*, 2003, vol. 3, pp. 2294–2299.

- [15] G. S. Buja and M. P. Kazmierkowski, "Direct torque control of PWM inverter-fed AC motors—A survey," *IEEE Trans. Ind. Electron.*, vol. 51, no. 4, pp. 744–757, Aug. 2004.

- [16] M. Bertoluzzo, G. Buja, and R. Menis, "Direct torque control of an induction motor using a single current sensor," *IEEE Trans. Ind. Electron.*, vol. 53, no. 3, pp. 778–784, Jun. 2006.

- [17] M. Pacas and J. Weber, "Predictive direct torque control for the PM synchronous machine," *IEEE Trans. Ind. Electron.*, vol. 52, no. 5, pp. 1350–1356, Oct. 2005.

- [18] R. Morales-Caporal and M. Pacas, "A predictive torque control for the synchronous reluctance machine taking into account the magnetic cross saturation," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 1161–1167, Apr. 2007.

- [19] P. Correa, M. Pacas, and J. Rodriguez, "Predictive torque control for inverter-fed induction machines," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 1073–1079, Apr. 2007.

- [20] Y. A.-R. I. Mohamed and E. F. El-Saadany, "An improved deadbeat current control scheme with a novel adaptive self-tuning load model for a three-phase PWM voltage-source inverter," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 747–759, Apr. 2007.

- [21] L. Springob and J. Holtz, "High-bandwidth current control for torqueripple compensation in PM synchronous machines," *IEEE Trans. Ind. Electron.*, vol. 45, no. 5, pp. 713–721, Oct. 1998.

- [22] E. F. Camacho and C. Bordons, *Model Predictive Control*. London, U.K.: Springer-Verlag, 1999.

- [23] D. W. Clarke, C. Mohtadi, and P. S. Tuffs, "Generalized predictive control—Part I: The basic algorithm," *Automatica*, vol. 23, no. 2, pp. 137– 148, Mar. 1987.

- [24] S. Bibian and J. Hua, "Time delay compensation of digital control for dc switchmode power supplies using prediction techniques," *IEEE Trans. Power Electron.*, vol. 15, no. 5, pp. 835–842, Sep. 2000.

- [25] O. J. M. Smith, "A controller to overcome dead time," *ISA J.*, vol. 6, no. 2, pp. 28–33, 1959.

- [26] T. Nussbaumer and J. W. Kolar, "Improving mains current quality for three-phase three-switch buck-type PWM rectifiers," *IEEE Trans. Power Electron.*, vol. 21, no. 4, pp. 967–973, Jul. 2006.

- [27] T. Nussbaumer, K. Mino, and J. W. Kolar, "Design and comparative evaluation of three-phase buck boost and boost buck unity power factor PWM rectifier systems for supplying variable DC voltage link converters," in *Proc. 10th Eur. Power Quality Conf. (PCIM)*, Nuremberg, Germany, May 23–27, 2004, pp. 126–135.

- [28] Sensitec Current Sensor CMS2025-SP3. [Online]. Available: www. sensitec.com

- [29] Analog Devices ADSP219x, DSP Hardware Reference, Aug. 2003. rev. 1.1. [Online]. Available: www.analog.com/Processors

- [30] B. Bryant and M. K. Kazimierczuk, "Voltage-loop power-stage transfer functions with MOSFET delay for boost PWM converter operating in CCM," *IEEE Trans. Ind. Electron.*, vol. 54, no. 1, pp. 347–353, Feb. 2007.

- [31] T. Nussbaumer, G. Gong, M. L. Heldwein, and J. W. Kolar, "Controloriented modeling and robust control of a three-phase buck+boost PWM rectifier (VRX-4)," in *Conf. Rec. IEEE IAS Annu. Meeting*, Hong Kong, Oct. 2–6, 2005, pp. 169–176. CD-ROM.

**Thomas Nussbaumer** (M'05) was born in Vienna, Austria, in 1975. He received M.Sc. degree in electrical engineering (with honors) from the Vienna University of Technology, Vienna, in 2001, and the Ph.D. degree from the Power Electronic Systems Laboratory, Swiss Federal Institute of Technology (ETH), Zurich, Switzerland, where he performed research on the design, control, and modulation of three-phase rectifiers with low effects on the mains, in 2004.

After receiving the Ph.D. degree, he continued research on power factor correction techniques, modeling and dynamic control of three-phase rectifiers, and electromagnetic compatibility. Since February 2006, he has been with Levitronix GmbH, Zurich, where he is currently working on magnetically levitated motors and pumps for the semiconductor process industry.

Dr. Nussbaumer is a member of the Austrian Society of Electrical Engineering (OVE).

**Marcelo Lobo Heldwein** (S'99) received the B.S. and M.S. degrees in electrical engineering from the Federal University of Santa Catarina, Florianópolis, Brazil, in 1997 and 1999, respectively. He is currently working toward the Ph.D. degree in the Power Electronic Systems Laboratory, Swiss Federal Institute of Technology (ETH), Zurich, Switzerland.

From 1999 to 2001, he was a Research Assistant with the Power Electronics Institute (INEP), Federal University of Santa Catarina. From 2001 to 2003, he

was an Electrical Design Engineer with Emerson Energy Systems in São José dos Campos, Brazil, and Stockholm, Sweden. His research interests include power factor correction techniques, static power converters, and electromagnetic compatibility.

Mr. Heldwein is a member of the Brazilian Power Electronic Society.

**Guanghai Gong** (S'03) was born in Zhejiang, China, on March 23, 1977. He received the B.Sc. and M.Sc. degrees in electrical engineering from Zhejiang University, Zhejiang, China, in 1999 and 2002, respectively. He is currently working toward the Ph.D. degree at the Power Electronic Systems Laboratory, Swiss Federal Institute of Technology (ETH) Zurich, Switzerland.

His research interests include hybrid power amplifiers combined by switched-mode converters and linear power amplifiers, soft-switched dc-dc con-

verters, and ac-dc converters for aircraft applications.

**Simon D. Round** (SM'99) received the B.E. (Hons.) and Ph.D. degrees from the University of Canterbury, Christchurch, New Zealand, in 1989 and 1993, respectively.

From 1992 to 1995, he was a Research Associate with the Department of Electrical Engineering, University of Minnesota, and a Research Fellow with the Norwegian Institute of Technology, Trondheim, Norway. From 1995 to 2003, he was a Lecturer/ Senior Lecturer with the Department of Electrical and Electronic Engineering, University of

Canterbury, where he performed research on power quality compensators, electric vehicle electronics, and cryogenic power electronics. He was also a Power Electronic Consultant for Vectek Electronics, where he developed a "state-of-the-art" digital controller for high-power inverter systems. In September 2004, he joined the Power Electronic Systems Laboratory, Swiss Federal Institute of Technology (ETH), Zurich, Switzerland, as a Senior Research Associate. His current research interests are silicon carbide power electronics, control of three-phase unity-power-factor rectifiers, and the application of sparse matrix converters.

Dr. Round has been actively involved in the IEEE New Zealand South Section, where he was the Vice-Chair and Chairman from 2001 to 2004. He was the recipient of the University of Canterbury Teaching Award in 2001.

Johann W. Kolar (M'89–SM'04) received the Ph.D. degree (summa cum laude/promotio sub auspiciis praesidentis rei publicae) from the Vienna University of Technology, Vienna, Austria.

Since 1984, he has been an Independent International Consultant in close collaboration with the Vienna University of Technology, in the fields of power electronics, industrial electronics, and highperformance drives. On February 1, 2001, he was appointed Professor and Head of the Power Electronic Systems Laboratory, Swiss Federal Institute

of Technology (ETH), Zurich, Switzerland. He has proposed numerous novel PWM converter topologies, and modulation and control concepts, e.g., the VIENNA rectifier and the Three-Phase AC-AC Sparse Matrix Converter. He has published more than 250 scientific papers in international journals and conference proceedings. He is the holder of more than 70 patents. His current research interest is ac-ac and ac-dc converter topologies with low effects on the mains, e.g., for a power supply of telecommunication systems, More-Electric-Aircraft, and distributed power systems in connection with fuel cells. Other main areas of his research are the realization of ultracompact intelligent converter modules employing latest power semiconductor technology (SiC), novel concepts for cooling and EMI filtering, multidomain/multiscale modeling and simulation, pulsed power, bearingless motors, and power MEMS. Since 2002, he has also been an Associate Editor for the Journal of Power Electronics of the Korean Institute of Power Electronics and a member of the Editorial Advisory Board of the Institute of Electrical Engineers of Japan Transactions on Electrical and Electronic Engineering.

Dr. Kolar is a member of the Institute of Electrical Engineers of Japan (IEEJ) and of the technical program committees of numerous international conferences in the field (e.g., Director of the Power Quality Branch of the International Conference on Power Conversion and Intelligent Motion). From 1997 to 2000, he served as an Associate Editor for the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS and since 2001 as an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS. He was the recipient of the Best Transactions Paper Award of the IEEE Industrial Electronics Society in 2005 and an Erskine Fellowship from the University of Canterbury, Christchurch, New Zealand, in 2003. In 2006, the European Power Supplies Manufacturers Association awarded the Power Electronics Systems Laboratory of ETH Zurich as the leading academic research institution in Europe.