## Advanced Bidirectional Three-Phase Current/Voltage DC-Link Buck-Boost/Boost-Buck PFC AC/DC Converter Systems

A thesis submitted to attain the degree of

DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

presented by DAIFEI ZHANG

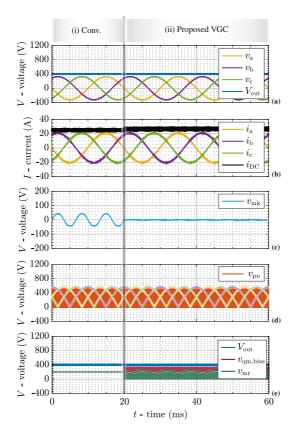

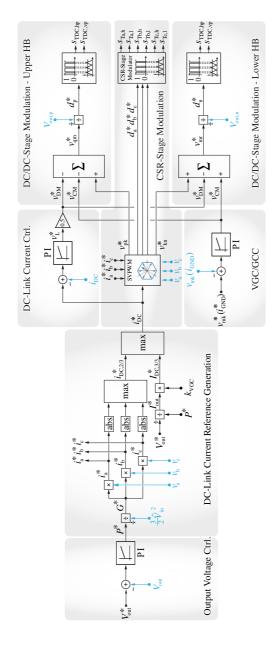

MSc ETH born on 24.08.1994 citizen of Taiyuan, Shanxi, China

accepted on the recommendation of Prof. Dr. Johann W. Kolar, examiner Prof. Dr. Ryan (Yunwei) Li, co-examiner

ETH Zurich Power Electronic Systems Laboratory Physikstrasse 3 | ETL I12 8092 Zurich | Switzerland

http://www.pes.ee.ethz.ch

© 2019-2023, Daifei Zhang

致金晶。 致我的父母,艳岩和虎平。

To Jinjing. To Yanyan and Huping, my parents.

# Acknowledgments

I finally started to write this acknowledgment on a rainy Swiss national day and memory is journeying back and forth...

First and foremost, I want to express my earnest gratitude to my advisor and supervisor, Prof. Dr. Johann W. Kolar, for his unwavering support and guidance. He embodies the qualities of a visionary researcher, an engineer dedicated to perfection, and a mentor tirelessly committed to teaching. He is the person who resolved my long-standing confusion and guided me to a deeper understanding of the power electronics world.

I also wish to express my deep appreciation to Prof. Dr. Ryan (Yunwei) Li for serving as a co-examiner and providing crucial support to this thesis through his affirmation and encouragement.

My journey in power electronics began at RWTH Aachen in 2016, marking my first stop in Europe and my initial exposure to advanced power electronics technologies. I would like to express my sincere gratitude to Prof. De Doncker for sharing his valuable knowledge and providing encouragement. I am also thankful to all the power electronics folks in Aachen: Zhiqing (Prof. Yang), Zheng (Dr. An) and Shenghui (Prof. Cui), and most importantly, my bachelor thesis supervisor, Jingxin (Prof. Hu), who has been supporting me from the moment I stepped foot in Europe up to the present day. Of course, it was in Aachen that I had the privilege of meeting the most important person in my life, Jinjing.

I relocated to Zurich in 2017 to pursue my master's degree. I would like to once again express my gratitude to Prof. Kolar for his kindness and for delivering top-level power electronics lectures that not only captivated my interest but also influenced my decision to dedicate my career to this field. My sincere thanks also extend to Dr. Tobias Geyer and Dr. Florina Krismer for their incredible lectures and affirmations, which further solidified my passion for power electronics. I would also like to extend my appreciation to the lecture TAs with whom I engaged in valuable discussions and who later became my PES colleagues: Dr. Dominik Neumayr, Dr. Michael M. Antivachis, and Dr. Pantelis Papamanolis. Additionally, I am grateful to my project and master thesis supervisors, Dr. Thomas Guillod and Dr. Piotr Czyż, for being the first people to integrate me into the world of PES. Furthermore, I am immensely grateful for all the time I spent with my D-ITET mates; thank you, Dan, Mingkun, Anliang, Baiwei, Yunni (Dr. Li), Jiawei, Ying, and Tanuj.

I started my Ph.D. journey at PES in 2019, and I am truly grateful to Prof. Kolar for offering me the opportunity to be part of this world-class PES team. The discussions we had during the Ph.D. position discussion in I-lab and your office are still clear and vivid in my mind, e.g., that the graduation should includes the comprehensive experimental verification of a new concept besides detailed theoretical studies. Upon joining PES, I received immediate hospitality and support from Monica Kohn-Müller and Prisca Maurantonio, who helped me immensely with third-country difficulties and various administrative affairs. Furthermore, I want to express my sincere gratitude to all the senior fellows of the PES team, from whom I received invaluable guidance and learned from their vast experience and insights: Dr. Mattia Guacci, Dr. Jon Azurza, and especially Dr. Jonas Huber, who shares the office with me and sets a great example for me not only in technical excellence but also in social skills. Moreover, the expertise and dedication of Jonas have played a pivotal role in shaping the excellence of our research. For instance, his invaluable guidance in the planning, structuring, and polishing of our papers has significantly enriched the exceptional quality of our work.

I also had the great pleasure of working with other fantastic colleagues in the lab and outside of work: Dr. Gustavo C. Knabben - our conversations during my MV transformer design were always enjoyable; Rosario Giuffrida thank you for introduction of Zyng and other FPGA knowledge in G-lab; Reto Bonetti - you are necessary for safe EMI measurements; Prof. Spasoje Miric - the conclusion of dinner talk in the kitchen is always "Serbia and China are good friends forever"; Emanuel Hubmann - it was wonderful to have you around every early Monday morning and to correct funny exam sheets together; Dr. Pascal Niklaus - a true team player, always ready to integrate everyone. Besides them, the whole PES team is responsible for the great research atmosphere and I would like thank: Dr. Jordi Everts, Dr. Matthias Kasper, Dr. Dominik Bortis, Dr. Marcel Alexander-Schuck, Dr. Morris J. Heller, Dr. Pedro Bezerra, Dr. Lukas F. Hornscheidt-Schrittwieser, Dr. Mario Mauerer, Dr. Daniel Rothmund, Dr. Julian Böhler, Dr. Michael Haider, Dr. David Menzi, Dr. Jannik Schäfer, Dr. Pascal Püntener, Dr. Marc Röthlisberger, Dr. Davide Cittanti, Dr. Junzhong Xu, Ivana Bagarić, Neha Nain, Gwendolin Rohner. Also, PES would not work that smoothly without Yvonne Schnyder-Lieberherr, Nadine Wacha, Roswitha Coccia, and Peter Seitz. Furthermore, I really appreciated the support and help from the students who worked on their semester projects or master theses with me: Stephan Leuch, Danqing Cao, Pengpeng Sun, Christos Leontaris, Andrin Schneider, Jérôme Kaufmann, and Mücahid Akbas.

Furthermore, I would like to highlight Baiwei, Dan, Anliang, Yunni (Dr. Li), Sisi (Dr. Zhao), Min (Dr. Luo), Yi (Dr. Dou) and recently Gunaghai (Dr. Gong) for all Chinese festival dinner parties. Even though this sounds like a Chinese power electronics "gang" in Zurich, we actually never talk about power electronics but only enjoy food and drinks.

Last but most importantly, I would not have reached this point without my parents, Yanyan and Huping, who have provided their unwavering support, love, and confidence throughout this journey. Very special gratitude to Jinjing, who left the U.S. to join me in Zurich with all the love, who made my Ph.D. life much more balanced with the work, and who will continue the journey alongside me.

Daifei Zhang Zurich, August 2023

世上本没有路,走的人多了,也便成了路。 - 鲁迅

Paths are not made in this world, but as more people walk, they become roads. – Lu Xun

## **Abstract**

M ORE efficient and compact electric vehicle (EV) chargers promote sustained transportation electrification towards a low-carbon economy. Advanced three-phase (3-Φ) bidirectional AC/DC converter systems with buck-boost functionality, e.g., with an extended output voltage range of 200 V to 1000 V, could be employed as standard building blocks in various galvanically isolated EV chargers, but could promisingly also serve as future RCD-based *non-isolated* EV chargers characterized by significantly increased efficiency and power density compared to state-of-the-art isolated EV charger solutions, and are accordingly reviewed and analyzed in this thesis comprehensively considering both the current DC-link (current source) and the voltage DC-link (voltage source) topologies.

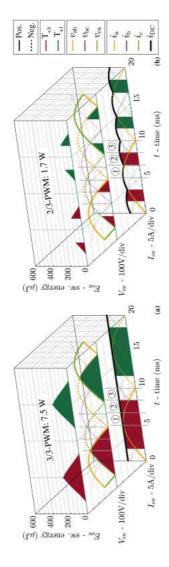

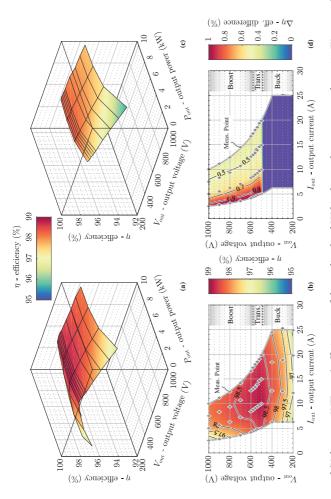

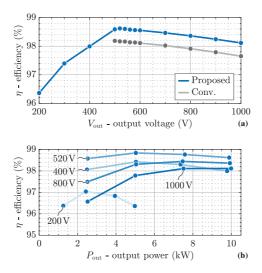

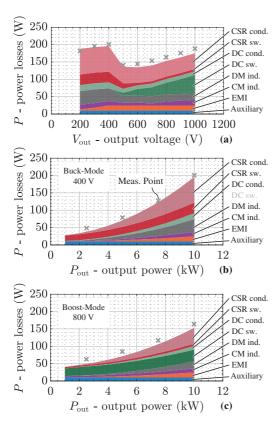

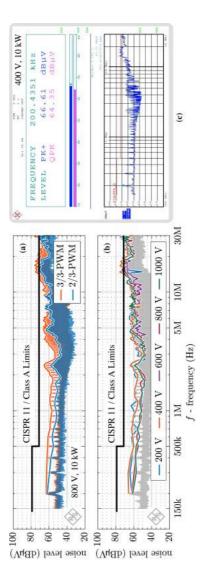

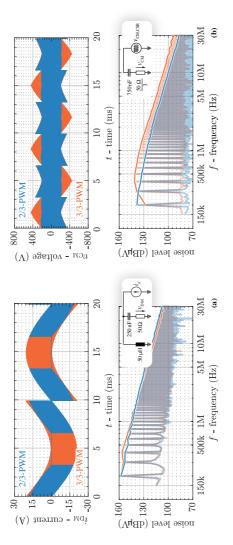

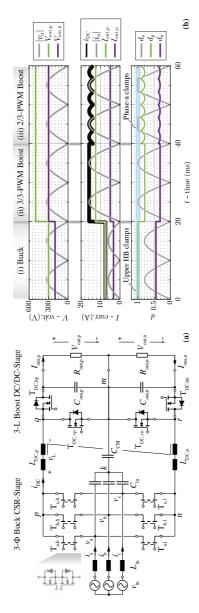

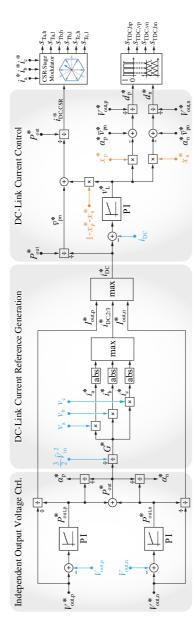

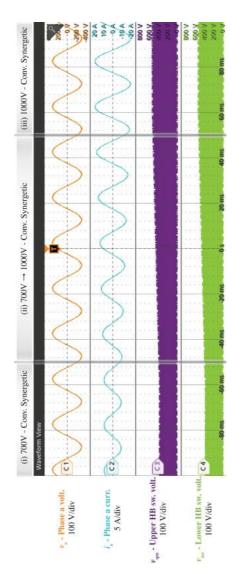

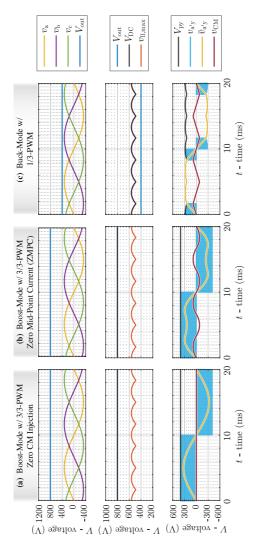

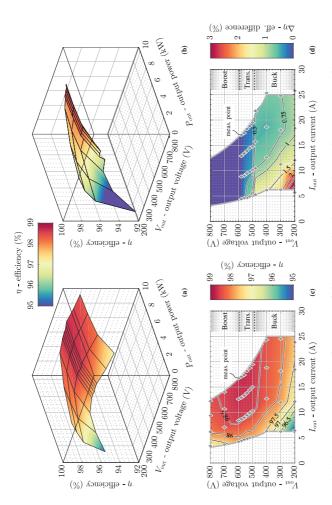

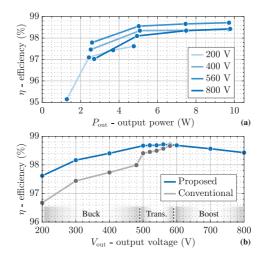

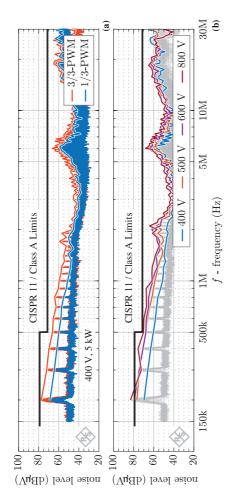

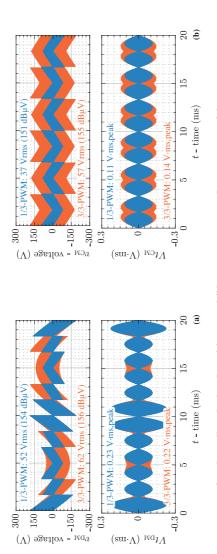

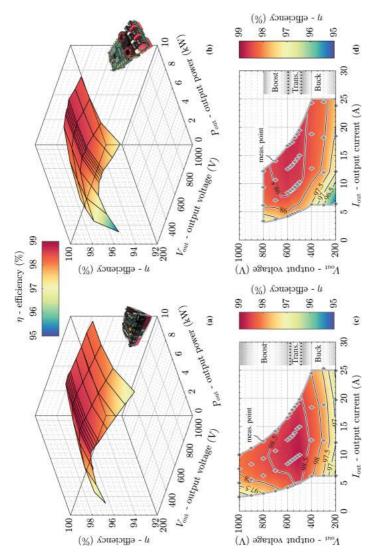

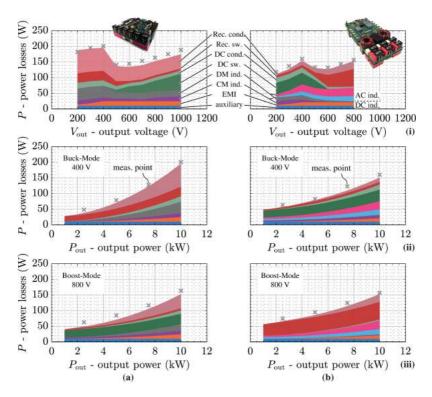

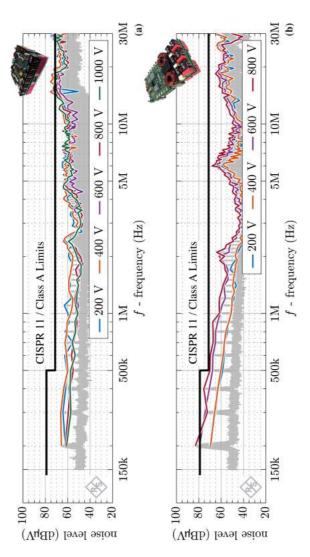

A 3-Φ current DC-link buck-boost (bB) PFC AC/DC converter system, where a 3- $\Phi$  buck-type current source rectifier (CSR)-stage and a subsequent 3-L boost-type DC/DC-stage are combined through one advantageous shared DC-link inductor, is first selected from the category of current source converter systems. The buck functionality is achieved by operating the CSR-stage solely in 3/3-PWM without switching the DC/DC-stage such that the DC/DCstage only creates the inevitable conduction losses but zero switching losses. In the boost-mode, the DC/DC-stage steps up the rectified voltage of the 3- $\Phi$ mains to a required large output value and, beneficially, shapes the DC-link current to follow the upper envelope of the absolute value of the 3- $\Phi$  currents to eliminate the zero switching state (shoot-through state) of the CSR-stage, i.e., the CSR-stage operates with 2/3-PWM. These loss-optimum operations, i.e., reduced number of switching instants due to clamping of one phase of the CSR-stage or the DC/DC-stage, and minimum possible DC-link current for any operating point, are guaranteed by a proposed synergetic control strategy. These favorable features are experimentally verified, including conducted EMI measurements, using a 10 kW hardware demonstrator with a power density of 6.4 kW/dm<sup>3</sup> (107.5 W/in<sup>3</sup>) and a peak efficiency of 98.8%. The measured ultra-flat efficiency surface proves the expected highly efficient operation over wide output voltage and power ranges.

Furthermore, the synergetic control concept of the 3-Φ current DC-link bB PFC AC/DC converter system is extended to regulate two independent DC outputs for heavy-duty EVs. The loss-optimal operations are still retained, i.e., the reduced number of switching instants due to clamping of one phase of the CSR-stage (switching only two out of the three phases, i.e., 2/3-PWM) or individual clamping of the DC/DC-stage's two half-bridges, and minimum possible DC-link current for any operating point. Experimental confirmation

of the proposed control scheme using the built 10 kW demonstrator system is provided, and a significant measured efficiency improvement, e.g., from 97.9 % to 98.4 % (0.5 %) at 10 kW, is demonstrated, which is largely independent of output voltage asymmetries and load asymmetries.

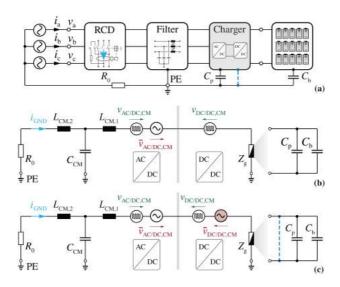

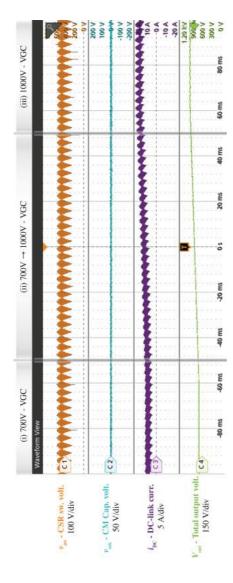

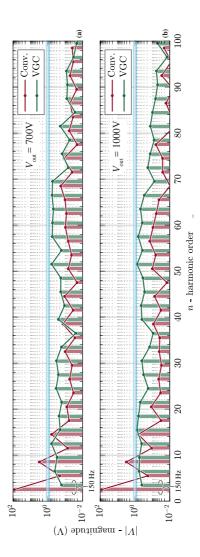

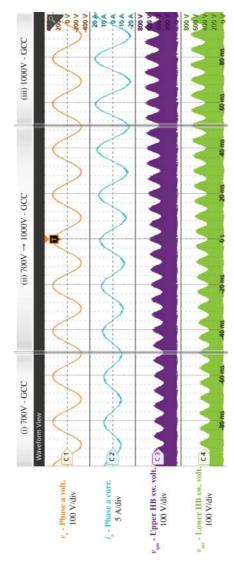

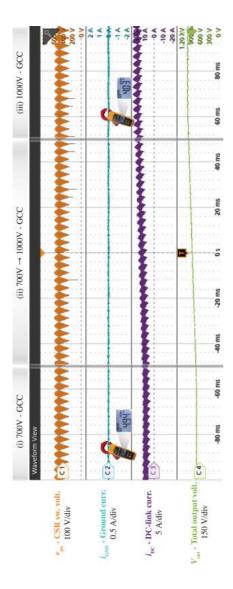

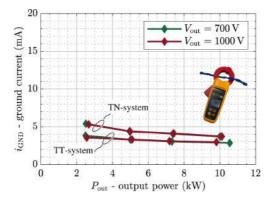

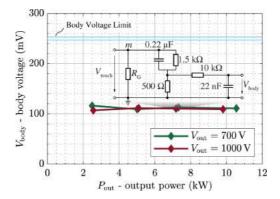

Targeting non-isolated EV chargers based on the analyzed 3-Φ current DC-link bB PFC AC/DC converter system, a virtual grounding control (VGC) is proposed to operate the DC/DC-stage to compensate the low-frequency (LF) common-mode (CM) voltage resulting from the CSR-stage modulation and thus controls the LF CM voltage between the DC output and protective earth (PE) to zero. This enables further a direct connection of the DC output midpoint to PE, where an additionally proposed ground current control (GCC) prevents nuisance tripping of mandatory RCDs by regulating the measured LF CM ground current. The proposed concepts are verified on the realized 10 kW hardware demonstrator considering Terra-Terra (TT) and Terra-Neutral (TN) grounding systems. The proposed GCC successfully limits the LF CM leakage current to < 6 mA RMS, i.e., significantly below typical RCD trip levels, and, using the human-body impedance model according to UL 2202, achieves a test voltage of 110 mV that is clearly below the most stringent limit (250 mV) of the standard, which provides a viable solution for future non-isolated EV chargers.

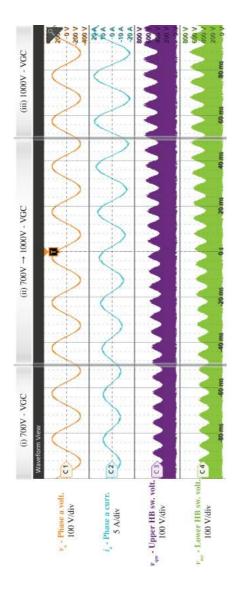

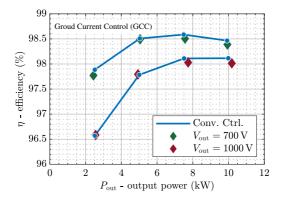

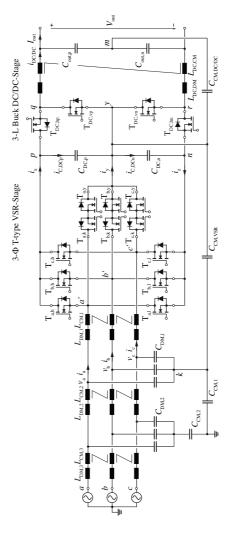

Besides the aforementioned current DC-link topologies, such bidirectional AC/DC buck-boost converter systems can also be realized in the form of widely-analyzed voltage DC-link topologies. A three-level (3-L) realization of the 3-Φ voltage DC-link rectifier stage facilitates small EMI filters and hence compact converter realization so that a T-type (Vienna) voltage source rectifier (VSR)-stage is selected as front-end. To achieve buck-boost functionality, the boost-type VSR-stage must be combined with a buck-type DC/DC stage, which again advantageously is realized as a 3-L structure to reduce the magnetics volume and to enable controllability of the voltage DC-link midpoint potential. Thus, a 3-Φ voltage DC-link boost-buck (Bb) PFC AC/DC converter system is selected and studied from the category of voltage source topologies. For high output voltages, the VSR-stage continuously modulates all three phases to regulate the output voltage (3/3-PWM) while the DC/DC-stage remains clamped to avoid switching losses. For low output voltages, the DC/DC-stage advantageously controls the DC-link voltage to enable 1/3-PWM (only one of the three bridge-legs operates with PWM at any given time) of the VSR-stage with reduced switching losses. Furthermore, a novel 2/3-PWM scheme for the output voltage transition region, where output voltages are in between the buck-mode and the boost-mode operation limits, xii

guarantees operation with minimal losses, i.e., the minimum number of the VSR-stage bridge-legs operating with PWM, and with the minimum possible DC-link voltage, for any output voltage. These advantageous operations are ensured by a proposed synergetic control concept which achieves a seamless transition between the loss-optimum operating modes. A comprehensive experimental verification, including pre-compliance EMI measurements, using a 10 kW hardware demonstrator with a power density of  $5.4 \, \mathrm{kW/dm^3}$  (91 W/in³) and a peak efficiency of 98.8% confirms the theoretical analyses.

Finally, based on two realized hardware demonstrators, a comprehensive comparison of current and voltage DC-link buck-boost AC/DC converter systems is provided regarding hardware realization, synergetic control implementation, efficiency characteristics, and conducted EMI noise emissions. The thesis concludes with a summary of the main results and a discussion of future research areas.

# Kurzfassung

E FFIZIENTERE und kompaktere Ladegeräte für Elektrofahrzeuge unterstützen die Elektrifizierung des Transportsektors und die Transformation hin zu einer klimafreundlichen Wirtschaft. Fortschrittliche dreiphasige (3-Φ) bidirektionale AC/DC-Konverter mit Leistungsfaktorkorrektur (Power Factor Correction, PFC, d.h. Sinuseingangsstrom) und Hoch- und Tiefsetzstellerfunktion, d.h. einem weiten Ausgangsspannungsbereich von beispielsweise 200 V bis 1000 V bei Speisung aus einem 3-Φ-400 V-Netz, können einerseits in galvanisch getrennten, vielfach modular aufgebauten Fahrzeugladegeräten eingesetzt werden, bieten andererseits aber auch eine interessante Lösung für zukünftige mittels FI-Schutzschaltern überwachte nicht isolierte Ladegeräte, welche sich durch höhere Effizienz und Leistungsdichte (verglichen mit isolierten Ladegeräten) auszeichnen, und werden demgemäss in dieser Arbeit umfassend analysiert, wobei sowohl Topologien mit (Konstant)stromzwischenkreis als auch (Konstant)spannungszwischenkreis betrachtet werden.

Im ersten Schritt wird ein 3-Φ-AC/DC-Konverter mit PFC und Tief-Hochsetzfunktion und Stromzwischenkeis analysiert (3-Φ-bB-AC/DC-Konverter), d.h. die Kopplung eines 3-Φ-AC/DC-Tiefsetzstellersystems mit Stromausgang und eines Dreilevel-DC/DC-Hochsetzstellers mit Stromeingang über eine gemeinsame Zwischenkreisinduktivität betrachtet. Für Tiefsetzstellerbetrieb der Gesamtanordnung werden sämtliche Phasen der Gleichrichtereingangsstufe getaktet (3/3-PWM) und die DC/DC-Hochsetzausgangsstufe geklemmt, wodurch Schaltverluste der DC/DC-Stufe vermieden werden bzw. diese Stufe nur Leitverluste aufweist. Für Hochsetzstellerbetrieb wird die gleichgerichtete Spannung des 3-Φ-Netzes mittels der DC/DC-Stufe auf den gewünschten Spannungswert angehoben und weiters der Zwischenkreisstrom derart geformt, dass dieser der Einhüllenden der Absolutwerte der 3- $\Phi$ -Eingangsphasenstromsollwerte folgt, womit kein Freilaufbzw. Nullschaltzustand der Eingangsstufe erforderlich ist und die Taktung unter deutlicher Einsparung an Schaltverlusten auf zwei von drei Phasen beschränkt werden kann (2/3-PWM). Diese synergetische verlustoptimierte Regelung von Gleichrichterstufe und DC/DC-Ausgangsstufe, welche die Zahl an Schalthandlungen dadurch reduziert, dass entweder der Schaltzustand von einer Phase der Gleichrichterstufe oder der Schaltzustand des Hochsetzstellers festgehalten/geklemmt und der Zwischenkreisstrom stets auf dem minimal erforderlichen Wert gehalten wird, wird durch die vorgeschlagene Regelstruktur auch für den Übergangsbereich zwischen reinem Tiefsetzstellerund reinem Hochsetzstellerbetrieb des Gesamtsystems garantiert. Die vorteilhaften Eigenschaften des neuen Konzeptes werden experimentell, inklusive

EMV-Messungen, anhand eines Demonstratorsystems mit 10 kW Nennleistung verifiziert, welches eine Leistungsdichte von  $6.4\,\mathrm{kW/dm^3}$  (107.5 W/in³) und eine Effizienz von bis zu 98.8% aufweist. Die gemessene, extrem flache Effizienzcharakteristik belegt die erwartete hocheffiziente Funktion über einen weiten Ausgangsspannungs- und Ausgangsleistungsbereich.

Darüber hinaus wird das synergetische Regelungskonzept des  $3\text{-}\Phi\text{-}bB\text{-}AC/DC\text{-}Konverters}$  derart erweitert, dass zwei unabhängige Gleichspannungsausgänge für elektrische Nutzfahrzeuge zur Verfügung stehen. Der verlustoptimale Betrieb wird dabei weiterhin aufrechterhalten, d.h., es wird weiterhin die Anzahl an Schaltvorgängen entweder durch das Klemmen einer Phase der Gleichrichterstufe oder durch das Klemmen einer der beiden Halbbrücken des DC/DC-Hochsetzstellers reduziert und der Zwischenkreisstrom für jeden Arbeitspunkt minimiert. Das vorgeschlagene Regelkonzept wird mithilfe des 10 kW-Demonstratorsystems experimentell verifiziert und eine signifikante Steigerung der gemessenen Effizienz von 97.9 % auf 98.4 % (0.5 %) bei 10 kW, weitgehend unabhängig von Ausgangsspannungs- und Ausgangsleistungsasymmetrien nachgewiesen.

Mit Blick auf zukünftige nicht isolierte Fahrzeugladegeräte wird für das 3-Φ-bB-AC/DC-Konvertersystem weiters eine Pseudoerdungsregelung vorgeschlagen, welcher die DC/DC-Hochsetzstellestufe derart regelt, dass die seitens der Gleichrichterstufe generierte niederfrequente Gleichtaktspannung kompensiert und dadurch die niederfrequente Gleichtaktspannung zwischen dem Gleichspannungsausgangsmittelpunkt und Schutzerde zu Null wird. Dadurch kann der Mittelpunkt des Gleichspannungsausgangs direkt mit Schutzerde verbunden werden, wobei in diesem Fall eine Erdstromregelung mit Sollwert Null verhindert, dass die vorgeschriebenen FI-Schutzschalter unnötigerweise auslösen. Das vorgeschlagene Konzept wird mithilfe des 10 kW-Demonstratorsystems sowohl für Terra-Terra-(TT)- als auch für Terra-Neutral-(TN)-Erdungssysteme verifiziert. Die Erdstromregelung limitiert den niederfrequenten Gleichtaktleckstrom auf < 6 mA RMS, d.h. auf deutlich unter typischen Auslöseschwellen von FI-Schutzschaltern liegende Werte, zudem wird, unter Verwendung des Körper-Ersatznetzwerkes nach UL 2202, eine verbleibende Erdspannung von 110 mV verifiziert, welche deutlich unter dem strikten Limit von 250 mV der Norm liegt, und somit eine für zukünftige nicht isolierte Fahrzeugladegeräte einsetzbare Lösung präsentiert.

Nebst der vorstehend beschriebenen Topologie mit Stromzwischenkreis, können auf-/abwärts wandelnde 3-Φ-PFC-Gleichrichtersysteme auch mittels einer industriell weit verbreiteten Spannungszwischenkreisschaltungstopologie realisiert werden. Eine Dreilevelrealisierung der Gleichrichterstufe xvi

hat hierbei den Vorteil, dass EMV Filter geringeren Bauvolumens Einsatz finden können, bzw. der Konverter eine höhere Leistungsdichte aufweist, weshalb ein T-typ-(Vienna)-Hochsetzgleichrichter als Eingangsstufe gewählt wird. Um zudem die Tiefsetzfunktion zu etablieren wird diese Konverterstufe mit einem nachgeschalteten DC/DC-Tiefsetzsteller kombiniert, und dieser ebenfalls in Dreilevelstruktur realisiert, um das Volumen der magnetischen Komponenten zu verkleinern und eine Regelung der Spannung des Mittelpunktes des beiden Konvertersystemen gemeinsamen Spannungszwischenkreises zu ermöglichen. Für hohe Ausgangsspannungen werden, um die Ausgangsspannung zu regeln alle drei Phasen der Gleichrichtereingangsstufe getaktet (3/3-PWM), wobei der DC/DC-Tiefsetzsteller geklemmt verbleibt um Schaltverluste zu vermeiden. Bei tiefen Ausgangsspannungen wird die Zwischenkreisspannung vorteilhafterweise durch den DC/DC-Tiefsetzsteller mit Rücksicht auf einen sechspulsigen, durch die Einhüllende der Absolutwerte der Netzsphasenspannungen definierten Verlauf geregelt, bzw. findet 1/3-PWM Einsatz, d.h. es wird jeweils nur eine der drei Phasen der Eingangsstufe getaktet und der Strom in den beiden verbleibenden Phasen indirekt durch den DC/DC-Tiefsetzsteller bzw. die vorstehend erwähnte Formung der Zwischenkreisspannung geregelt und so gegenüber 3/3-PMW eine massive Reduktion der Schaltverluste erreicht. Des Weiteren wird durch ein neuartiges 2/3-PWM-Modulationsschema für jene Fälle, in denen eine Ausgangsspannung des Gesamtsystems zwischen den durch reinen Hochsetzoder reinen Tiefsetzbetrieb abgedeckten Spannungsbändern eingestellt werden muss garantiert, dass ein Betrieb mit minimalen Verlusten vorliegt, d.h. in jedem Moment nur die minimale Anzahl an Halbbrücken getaktet und die Zwischenkreisspannung auf dem tiefst möglichen Wert gehalten wird. Hervorzuheben ist, dass das vorgeschlagene synergetischen Regelkonzept einen nahtlosen Übergang zwischen den verschiedenen verlustoptimalen Betriebsarten sicherstellt. Eine umfassende experimentelle Verifikation, inklusive EMV Messungen, durchgeführt mithilfe eines Demonstratorsystems mit 10 kW Nennleistung und einer Leistungsdichte von 5.4 kW/dm³ (91 W/in³) und einer Effizienz von bis zu 98.8%, bestätigt die theoretische Analyse.

Abschliessend wird bezugnehmend auf die beiden realisierten Demonstratorsysteme ein umfassender Vergleich der Hardwarerealisierungen, der synergetischen Regelungen, der Hardwareimplementierungen, der Effizienzcharakteristiken und der leitungsgebundenen EMV Störaussendungen dreiphasiger Tief-Hochsetz-Stromzwischenkreis- und Hoch-Tiefsetz-Spannungszwischenkreis-PFC-AC/DC-Konvertersysteme gegeben. Die Arbeit

schliesst mit einer Zusammenfassung der wichtigsten Forschungsergebnisse und einer Diskussion zukünftiger Forschungsbereiche.

## **Abbreviations**

1/3-PWM One-Third Pulse-Width Modulation 2/3-PWM Two-Third Pulse-Width Modulation

2-L Two-Level

3/3-PWM Three-Third Pulse-Width Modulation

3-L Three-Level 3-Φ Three-Phase

AC Alternating Current

bB buck-Boost Bb Boost-buck

BEV Battery Electric Vehicle CC Constant Current

CCS Combined Charging System

CM Common-Mode

CSR Current Source Rectifier

CV Constant Voltage

DAB Dual Active Bridge

DAB Dual Active Bridge DC Direct Current DM Differential-Mode

EMI Electromagnetic Interference

EV Electric Vehicle

FET Field-Effect Transistor

GaN Gallium Nitride

GCC Ground Current Control

GFCI Ground Fault Circuit Interrupter

GND Ground HB Half-Bridge HF High-Frequency

HTS High-Temperature Superconducting

HV High-Voltage

IEA International Energy Agency

IEC International Electrotechnical Commission

IEEE Institute of Electrical and Electronics Engineers

LF Low-Frequency

M-BDS Monolithic Bidirectional Switch

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NPC Neutral Point Clamped OBC On-Board Charger

PCB Printed Circuit Board

PE Protective Earth

PFC Power Factor Correction

PHEV Plug-In Hybrid Electric Vehicle

PI Proportional-Integral

PV Photovoltaic

PWM Pulse-Width Modulation RCD Residual Current Device

RMS Root Mean Square

Si Silicon

SiC Silicon Carbide SoC State of Charge

STEPS Stated Policies Scenario

SVPWM Space Vector Pulse-Width Modulation

TN Terra-Neutral TT Terra-Terra

UL Underwriters Laboratories

VGC Virtual Grounding Control

VSR Voltage Source Rectifier

# Contents

| Ac | knov  | vledgm  | nents                                                                  | v   |

|----|-------|---------|------------------------------------------------------------------------|-----|

| Ab | strac | et      |                                                                        | хi  |

| Κι | ırzfa | ssung   |                                                                        | xv  |

| Ab | brev  | iations |                                                                        | xix |

| 1  | Intr  | oductio | on                                                                     | 1   |

|    | 1.1   | Electri | ic Vehicle (EV) Charger Development                                    | 5   |

|    | 1.2   | 3-Ф Вι  | ack-Boost AC/DC Converter Systems                                      | 7   |

|    |       | 1.2.1   | $_3$ -Ф Buck-Boost (bB) Current DC-Link System                         | 9   |

|    |       | 1.2.2   | $_3\text{-}\Phi$ Boost-Buck (Вb) Voltage DC-Link System $\ .\ .\ .\ .$ | 9   |

|    | 1.3   | Main (  | Contributions                                                          | 11  |

|    |       | 1.3.1   | Scientific Contributions                                               | 11  |

|    |       | 1.3.2   | Demonstrator Systems and Performance Benchmark                         | 14  |

|    | 1.4   | List of | Publications                                                           | 14  |

|    |       | 1.4.1   | Patents                                                                | 14  |

|    |       | 1.4.2   | Journal Papers                                                         | 16  |

|    |       | 1.4.3   | Conference Papers                                                      | 17  |

|    |       | 1.4.4   | Keynotes and Tutorials                                                 | 18  |

|    |       | 1.4.5   | Supervised Projects and Theses                                         | 18  |

|    | 1.5   | Thesis  | Outline                                                                | 19  |

| 2  | A TI  | ree-Pl  | nase Synergetically Controlled Buck-Boost Curren                       | t   |

|    | DC-   | Link E  | V Charger                                                              | 21  |

|    | 2.1   | Introd  | uction                                                                 | 22  |

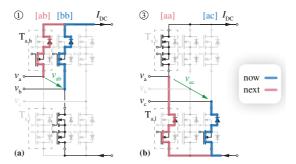

|    | 2.2   | Curre   | nt DC-Link Converter Modulation                                        | 28  |

|    |       | 2.2.1   | Conventional 3/3-PWM                                                   | 29  |

|    |       | 2.2.2   | Advanced 2/3-PWM                                                       | 32  |

|    |       | 2.2.3   | Switching Loss Comparison                                              | 32  |

|    | 2.3   | Loss-C  | Optimal Operation                                                      | 35  |

|    |       | 2.3.1   | Buck-Mode                                                              | 36  |

|    |       | 2.3.2   | Boost-Mode                                                             | 36  |

|    |       | 2.3.3   | Transition-Mode                                                        | 38  |

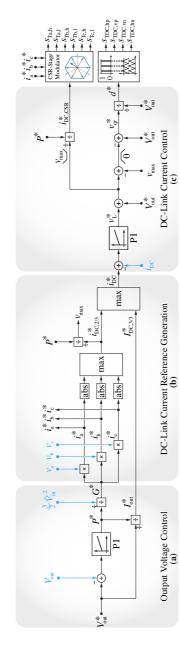

|    | 2.4   | Syner   | getic Control Strategy                                                 | 38  |

|    | -     | 2.4.1   | Output Voltage Control                                                 | 38  |

|    |       | 2.4.2   | DC-Link Current Reference Generation                                   | 40  |

|    |       | -       |                                                                        | xxi |

|                                                                                                                   |      | 2.4.3  | DC-Link Current Control                            | 40              |

|-------------------------------------------------------------------------------------------------------------------|------|--------|----------------------------------------------------|-----------------|

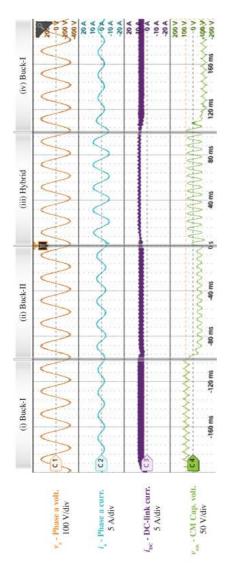

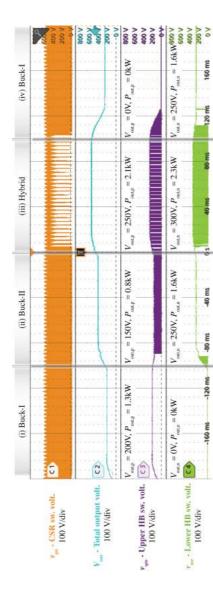

|                                                                                                                   | 2.5  | Experi | mental Verification                                | 42              |

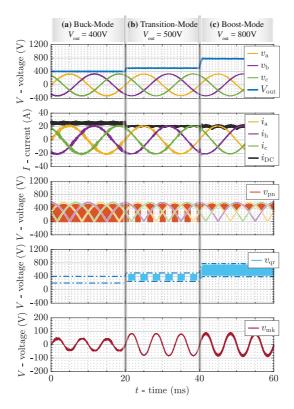

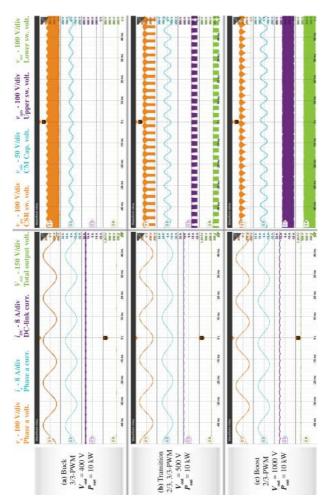

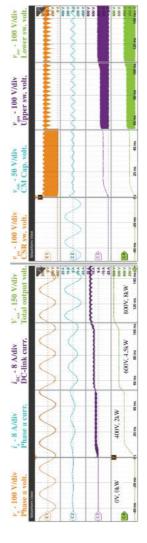

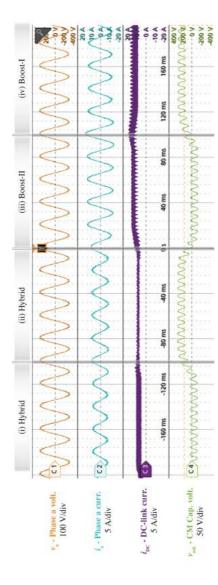

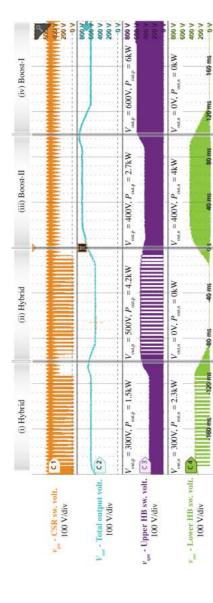

|                                                                                                                   |      | 2.5.1  | Experimental Waveforms                             | 42              |

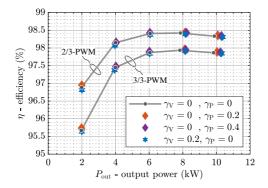

|                                                                                                                   |      | 2.5.2  | Efficiency Measurements                            | 46              |

|                                                                                                                   |      | 2.5.3  | EMI Measurements                                   | 50              |

|                                                                                                                   | 2.6  | Summ   | ary                                                | 51              |

| 3                                                                                                                 | 3-Ф  | Synerg | etically Controlled Current DC-Link AC/DC Buck-    | -               |

| -                                                                                                                 |      |        | verter with Two Independently Regulated DC Out-    |                 |

|                                                                                                                   | puts |        |                                                    | 57              |

|                                                                                                                   | 3.1  | Introd | uction                                             | 58              |

|                                                                                                                   | 3.2  |        | ting Modes with Independent Outputs                | 61              |

|                                                                                                                   |      | 3.2.1  | Buck-Mode                                          | 62              |

|                                                                                                                   |      | 3.2.2  | Buck-Mode                                          | 63              |

|                                                                                                                   |      | 3.2.3  | Hybrid-Mode                                        | 64              |

|                                                                                                                   | 3.3  | Syner  | getic Control Strategy                             | 64              |

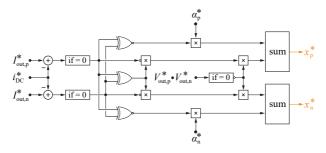

|                                                                                                                   |      | 3.3.1  | Independent Output Voltage Control                 | 64              |

|                                                                                                                   |      | 3.3.2  | DC-Link Current Reference Generation               | 66              |

|                                                                                                                   |      | 3.3.3  | DC-Link Current Control                            | 67              |

|                                                                                                                   | 3.4  | Measu  | red Efficiency Improvement                         | 69              |

|                                                                                                                   | 3.5  | Summ   | ary                                                | 75              |

| _                                                                                                                 | Mass | Taalat | ad a A Comment DC Link Book Decet EV Chausen       |                 |

| 4 Non-Isolated 3-Ф Current DC-Link Buck-Boost EV Charg<br>with Virtual Output Midpoint Grounding and Ground Curre |      |        |                                                    |                 |

|                                                                                                                   | Con  |        | around Current                                     |                 |

|                                                                                                                   |      |        | uction                                             | <b>77</b><br>78 |

|                                                                                                                   | 4.1  |        | ting Principle                                     | 85              |

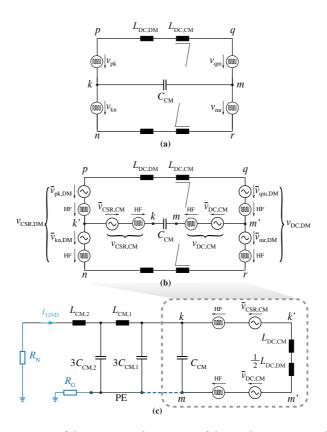

|                                                                                                                   | 4.2  | 4.2.1  | CM Equivalent Circuit                              | 86              |

|                                                                                                                   |      | 4.2.1  | Virtual Grounding Control (VGC)                    | 88              |

|                                                                                                                   |      | 4.2.3  | Ground Current Control (GCC)                       | 96              |

|                                                                                                                   | 4.3  |        | ol Strategy                                        | 96              |

|                                                                                                                   | 4.3  | 4.3.1  | Output Voltage and DC-Link Current Control         | 96              |

|                                                                                                                   |      | 4.3.2  | Virtual Grounding Control & Ground Current Control | 98              |

|                                                                                                                   |      | 4.3.3  | CSR-Stage and DC/DC-Stage Modulation               | 99              |

|                                                                                                                   | 4.4  |        | mental Results                                     | 99              |

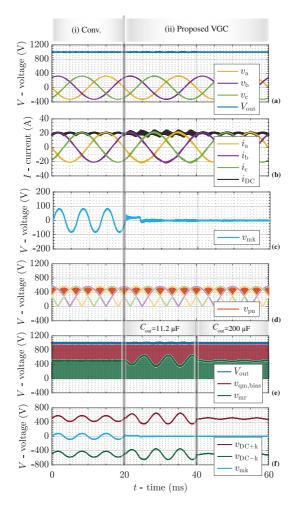

|                                                                                                                   | 4.4  | 4.4.1  | Operation with VGC                                 | 100             |

|                                                                                                                   |      | 4.4.2  | Operation with GCC                                 | 101             |

|                                                                                                                   |      | 4.4.3  | TT and TN Grounding Systems                        | 101             |

|                                                                                                                   |      | 4.4.4  | Ground Current Measurements                        | 109             |

|                                                                                                                   |      | 4.4.5  | Touch Current Test                                 | 110             |

|                                                                                                                   |      | 4.4.7  | 100011 00110111 1001                               | 110             |

|    |        | 4.4.6 Efficiency                                                                                                | 111 |

|----|--------|-----------------------------------------------------------------------------------------------------------------|-----|

|    | 4.5    | Summary                                                                                                         | 112 |

| 5  | -      | imal Synergetic Control of High-Efficiency 3-Ф 3-L Boost<br>k Voltage DC-Link Very Wide Output Voltage Range EV |     |

|    | Cha    | rger                                                                                                            | 115 |

|    | 5.1    | Introduction                                                                                                    | 116 |

|    | 5.2    | Operating Principle                                                                                             | 121 |

|    |        | 5.2.1 Boost-Mode                                                                                                | 122 |

|    |        | 5.2.2 Buck-Mode                                                                                                 | 126 |

|    |        | 5.2.3 Transition-Mode                                                                                           | 126 |

|    | 5.3    | Synergetic Control Strategy                                                                                     | 132 |

|    |        | 5.3.1 Output Voltage Control & Mains Current Control                                                            | 132 |

|    |        | 5.3.2 DC-Link Voltage Reference Generation                                                                      | 134 |

|    |        | 5.3.3 DC-Link Voltage Control                                                                                   | 135 |

|    |        | 5.3.4 DC/DC-Stage Current Control                                                                               | 135 |

|    | 5.4    | Hardware and Experimental Verification                                                                          | 137 |

|    |        | 5.4.1 Hardware Demonstrator                                                                                     | 137 |

|    |        | 5.4.2 Experimental Waveforms                                                                                    | 138 |

|    |        | 5.4.3 Efficiency Measurements                                                                                   | 140 |

|    |        | 5.4.4 EMI Measurements                                                                                          | 144 |

|    | 5.5    | Summary                                                                                                         | 147 |

| 6  | Con    | clusion and Outlook                                                                                             | 149 |

|    | 6.1    | Comparison of Current and Voltage DC-Link AC/DC Con-                                                            |     |

|    |        | verter Systems                                                                                                  | 151 |

|    | 6.2    | Summary                                                                                                         | 156 |

|    | 6.3    | Outlook and Future Research Areas                                                                               | 158 |

| Bi | bliog  | raphy                                                                                                           | 161 |

| Cı | ırricı | ılum Vitae                                                                                                      | 179 |

# 1

## Introduction

$\mathbf{T}^{\text{RANSPORTATION}}$  of passengers and freight currently accounts for approximately 25% of world energy use [1] and generates 25% of all CO<sub>2</sub> emissions [2]. Given a more efficient conversion technology and, at the same time, enabling the use of renewable energy, electrified transportation is believed as one of the most promising measures to reduce fossil fuel consumption significantly and support the net-zero CO<sub>2</sub> emission target set forth in the Paris Agreement before 2050 [3]. Furthermore, electric vehicles (EVs) are the single most important technology for decarbonizing the transport sector since EVs are more and more powered by renewable energy and much more efficient at converting energy into propulsion than gasoline and diesel vehicles.

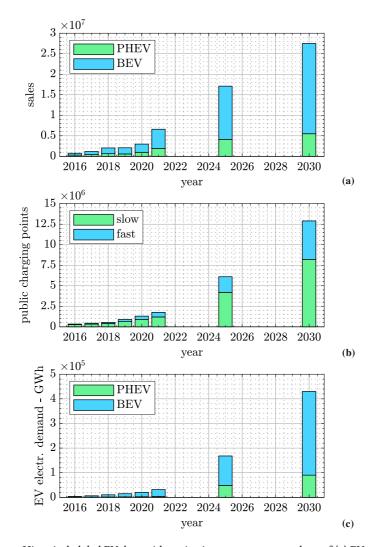

According to International Energy Agency (IEA), **Fig. 1.1** shows historical global EV data with projections to 2030 on numbers of EV sales, public charging points, and electricity demand consumed by the EV fleet. Obvious prosperities have been already observed before 2021 and exponential increases are expected until 2030, e.g., more than 270 million EVs will be sold, 13 million public EV charging points will be installed, and electricity consumption is supposed to be 430 000 GWh/year in 2030 by EVs.

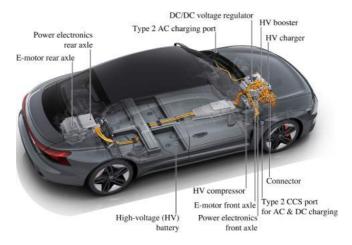

EVs have been popular on the street since the 1900s. **Fig. 1.2** depicts an old-fashioned electric brougham, which was driven by two four-pole electric motors (rated at two horsepower) allowing reverse rotating capability. The battery pack, consisting of 48 cells of chloride accumulators, was placed beneath the driver's seat [6]. Interestingly, a similar drivetrain structure is being implemented on modern EVs even though more than a hundred years have passed. **Fig. 1.3** shows a drivetrain system of the Audi RS e-tron GT with a battery voltage of 800 V and an on-board charger (OBC) allowing 11 kW AC charging. If using fast DC charging, a charging power of up to 270 kW can charge the battery from 5% to 80% SoC (state of charge) within 25 minutes [7].

Fig. 1.1: Historical global EV data with projections to 2030 on numbers of (a) EV sales, (b) public charging points, and (c) electricity demand consumed by the EV fleet [4]. Note that EVs include battery electric vehicles (BEVs) and plug-in hybrid electric vehicles (PHEVs). Also, note that the Stated Policies Scenario (STEPS) projection model, proving a more conservative benchmark for the future, is applied in this analysis [5].

Fig. 1.2: Electric brougham, i.e., also called *horseless vehicle*, was extensively used around the 1900s [6].

Fig. 1.3: 800 V drivetrain system of Audi RS e-tron GT [7].

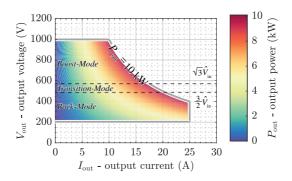

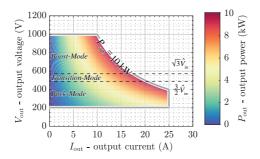

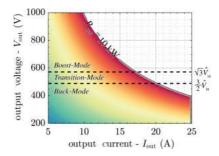

To facilitate the transition from fossil-fuel-based to carbon-free road transportation by EVs, more efficient and compact EV battery chargers are key enablers to overcome range anxiety and further reduce the costs of EVs. The EV chargers are typically realized as multi-stage solutions where PFC AC/DC converter systems are always needed to convert the AC mains voltage into a DC output charging the EV batteries [8]. Furthermore, a wide charging voltage range (typically from 200 V up to 1000 V, as shown in Fig. 1.4) requires buck-boost functionality, which is provided by such converter systems. State-of-the-art isolated EV chargers are additionally employing a series resonant

Fig. 1.4: Typical operating range of a 10 kW EV charger module [12]; note the output current limit of  $I_{\rm out}=25$  A.

converter with limited voltage controllability but high efficiency for isolating the output voltage; in the future, the isolation stage could be omitted, i.e., the buck-boost AC/DC converter systems directly used as non-isolated EV charging systems [9]. In this regard, a synergetically-controlled 3- $\Phi$  current DC-link buck-boost (bB) PFC AC/DC converter system featuring ultra-flat efficiency characteristics over a wide operating range is first studied and analyzed in this thesis. Furthermore, the proposed synergetic control strategy is extended to regulate two independent DC outputs for future high-voltage batteries of heavy-duty electric vehicles [10], which could advantageously be split into upper and lower halves [11]. Then, new virtual grounding control (VGC) and ground current control (GCC) schemes are proposed to avoid nuisance tripping of residual current devices (RCDs) and to ensure the resilient operation of future non-isolated EV chargers. Finally, a synergetically-controlled  $\operatorname{3-\Phi}$  voltage DC-link boost-buck (Bb) PFC AC/DC converter system, from the category of widely-analyzed voltage DC-link topologies, is investigated and comprehensively compared with the 3-Φ current DC-link bB PFC AC/DC converter system.

**Section 1.1** provides a brief overview of EV charger developments, where several main structures of EV battery chargers are summarized, including isolated and non-isolated EV charging structures. **Section 1.2** introduces several buck-boost AC/DC converter topologies with voltage or current DC-links and the two most promising 3-Φ buck-boost AC/DC converter systems are selected regarding simplicity and high performance as subjects of this thesis. **Section 1.3** presents the main contributions of this thesis and all

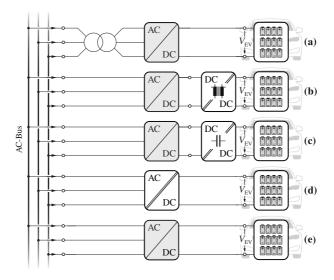

**Fig. 1.5:** Structures of typical isolated or future non-isolated EV battery chargers. The multi-stage structure is the dominant solution where the galvanic isolation functionality can be provided by a dedicated transformer or converter stage, i.e., **(a)** a low-frequency (LF) transformer, **(b)** a high-frequency (HF) DC/DC converter featuring inductive isolation, **(c)** an HF DC/DC converter featuring capacitive isolation. **(d)** The isolation functionality can also be integrated into the PFC rectifier stage to achieve a single-stage isolated AC/DC converter. **(e)** Non-isolated charger concepts facilitating more compact and more efficient realizations of future EV chargers are analyzed in this thesis.

related publications are listed in **Section 1.4**. **Section 1.5** outlines the content of each chapter.

## 1.1 Electric Vehicle (EV) Charger Development

Typical structures of isolated or future non-isolated EV chargers (see Fig. 1.5) are summarized in this section. The galvanically isolated solutions are presently dominant since a high common-mode (CM) impedance provided by either inductive or capacitive isolation is realized between the grid and the vehicle to ensure electrical safety passively [9, 13, 14].

The galvanic isolation can be achieved by a low-frequency (LF), i.e., mains frequency transformer (see **Fig. 1.5a**), but LF transformers are intrinsically

penalized by large volumes [15]. Thus, advantageously operating the transformer at an increased frequency can achieve high efficiency and reduce system volume, as shown in Fig. 1.5b, where an additional high-frequency (HF) transformer-based isolated DC/DC converter is applied. Such an isolated converter stage can be implemented as a dual active bridge (DAB) converter [16–19], an LLC resonant converter [20–22], or a series resonant DC/DC converter, i.e., DC transformer (DCX, [23, 24]). Even though, in this case, the required ultra-wide output voltage regulation capability can be provided by both the DC/DC converters and the 3-Φ PFC rectifier front-ends, loss-optimal operating modes of the whole system are very hard to be specified since collaborative operations of the two converters (DC/DC and PFC rectifier stages) with varying voltage gains are fairly complex. Thus, optimal EV charger designs of the cascaded system have to take the front-end and the isolation-stage into account at the same time instead of optimizing them separately. To avoid such complicated design and control issues, DCXs are preferably selected as standard isolated building blocks with a near-unity voltage conversion ratio [25]. Thus, the 3- $\Phi$  AC/DC converter system must cover a correspondingly wide output voltage range and/or the PFC rectifier front-end must incorporate buck-boost capability.

Even though HF transformers can successfully reduce losses and required volume compared to conventional LF transformers, such main magnetic components are still typical obstacles to future EV chargers with even higher efficiencies and power densities. Thus, research on capacitive coupling (see **Fig. 1.5c**), as a dual coupling type of inductive transformers, has been carried out where power is transferred between two isolated metal barriers [26–30]. Either series resonant [29] or switched capacitor [27] topologies can be implemented to realize the capacitive galvanic isolation with fairly small magnetic components resulting in compact isolation realizations. However, only very limited voltage regulation capabilities can be obtained by the capacitive galvanic isolation stage, therefore, the 3- $\Phi$  AC/DC converter needs, again, to provide the full buck-boost capability.

Furthermore, the buck-boost functionality and the galvanic isolation capability can also be realized by one single converter stage as shown in **Fig. 1.5d**, e.g.,  $3-\Phi$  matrix-type DAB converter [31] or  $3-\Phi$  isolated phase-modular converter [32]. However, single-stage isolated PFC rectifiers need very complicated control/modulation strategies to cover the required ultrawide output voltage range and high-efficiency operation over such a wide range can hardly be guaranteed.

Providing galvanic isolation always means placing an additional element, i.e., an LF transformer or an isolated DC/DC converter, in the power flow path and consequently leads to more bulky and more complex systems with increased power losses and costs. To roughly quantify these drawbacks, consider photovoltaic (PV) inverter systems: compared to traditional solutions that include galvanic isolation, their transformerless counterparts feature an efficiency improvement of 1% to 2% and about twice the power density [33,34]. Thus, non-isolated converter structures become attractive solutions for future EV chargers allowing compact, highly efficient, and low-cost realizations as shown in **Fig. 1.5e**. Without galvanic isolation, reliable protection against electrical hazards can only be provided by residual current devices (RCDs)¹ installed at the grid interface, which is mandatory according to standards (e.g., IEC 61851, UL 2202) [9]. Furthermore, to achieve compatibility with the wide range of EV battery voltages, non-isolated EV chargers, i.e., 3-Φ AC/DC converter systems, must provide buck-boost functionality.

All in all, except for the single-stage isolated EV charger solution (see **Fig. 1.5d**), 3-Φ AC/DC converter systems covering an ultra-wide output voltage range, e.g., from 200 V up to 1000 V, serve as a standard building block for various kinds of EV charging structures. Most importantly, they can be adapted as future non-isolated EV chargers and used to build chargers of even higher power levels with reduced costs and improved efficiencies.

### 1.2 3-Ф Buck-Boost AC/DC Converter Systems

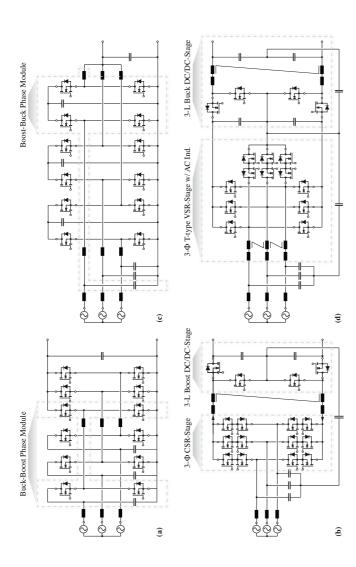

3- $\Phi$  buck-boost AC/DC converter systems are introduced in this section. Generally speaking, 3- $\Phi$  AC/DC converter systems, either with or without the buck-boost functionality, can be categorized into two main types, widely-used voltage DC-link (voltage source) systems, and less-frequently employed current DC-link (current source) systems. Thus, two promising topologies, i.e., 3- $\Phi$  buck-boost (bB) current DC-link PFC AC/DC converter system (see **Fig. 1.6b**) and 3- $\Phi$  boost-buck (Bb) voltage DC-link PFC AC/DC converter system (see **Fig. 1.6d**), are selected from the two categories as main subjects for a detailed analysis and performance comparison between two topologies over an ultra-wide output voltage range is conducted in this thesis.

<sup>&</sup>lt;sup>1</sup>Another common name is "ground fault circuit interrupter" (GFCI).

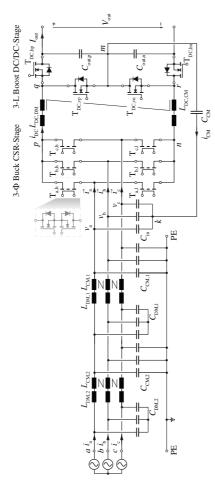

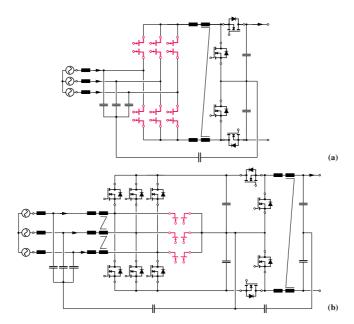

Fig. 1.6: Typical topologies of buck-boost and/or boost-buck 3- $\Phi$  PFC AC/DC converter systems, which are commonly grouped into two categories, i.e., (a) and (b) current DC-link (current source) systems, and (c) and (d) voltage DC-link (voltage source) systems. The (b) 3-Φ bB current DC-link PFC AC/DC converter system and (d) 3-Φ Bb voltage DC-link PFC AC/DC converter system are the main subjects of this thesis with integrated CM filters for full functionality, i.e., partial EMI filtering. Two benchmark topologies, i.e., (a) 3- $\Phi$  bB phase-modular PFC Y-rectifier and (c) 3- $\Phi$  Bb phase-modular PFC rectifier, are also shown.

#### 1.2.1 3-Ф Buck-Boost (bB) Current DC-Link System

Fig. 1.6a shows a 3- $\Phi$  bB phase-modular PFC Y-rectifier composed of three identical bB DC/DC-stages [35, 36]. The converter belongs to the current DC-link category as the 3- $\Phi$  mains currents are generated by pulse-width modulation based on the currents of the phase inductors (for buck-type operation). The phase-modular structure allows an easy rearrangement of the converter structure for single-phase operation to deliver full output power. However, the 3- $\Phi$  bB phase-modular Y-rectifier is penalized by an increased number of main inductors, i.e., three inductors instead of only one inductor in a conventional 3- $\Phi$  current DC-link PFC rectifier. Furthermore, the transistors of the DC-side half-bridges (HBs) have to block and switch the full output voltage so that operating at a very high output voltage is problematic in terms of significant hard-switching losses and larger HF voltage-time areas across the three phase inductors requiring relatively large inductance values for limiting the current ripples.

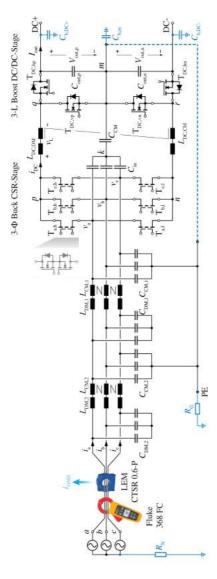

Therefore, instead of the phase-modular structure, a 3- $\Phi$  bB current DC-link PFC AC/DC converter system (see **Fig. 1.6b**), formed by a 3- $\Phi$  buck-type current source rectifier (CSR)-stage and a subsequent 3-L boost-type DC/DC-stage, is selected. The 3- $\Phi$  bB current DC-link PFC AC/DC converter system shows an increased complexity in the CSR front-end since each HB of the CSR-stage requires two inverse-series connected power semiconductors to provide the bidirectional blocking capability. However, its output DC/DC boost-stage is simpler and more straightforward compared to the 3- $\Phi$  bB phase-modular Y-rectifier. Only four transistors are needed in the 3- $\Phi$  bB current DC-link PFC AC/DC converter system output stage but twelve transistors would be needed for the Y-rectifier to achieve a 3-L characteristic of the bridge-legs connected to the DC output.

#### 1.2.2 3-Φ Boost-Buck (Bb) Voltage DC-Link System

**Fig. 1.6c** presents a 3-Φ Bb phase-modular PFC rectifier employing three independently regulated boost-buck converter stages (modules) [36, 37]. Each converter module generates an AC input voltage for controlling the current in the input inductor and/or related grid phase current by pulse-width modulating the corresponding phase DC-link voltage (for boost-type operation), and thus, this system is of voltage source type. Similar to the aforementioned dual current DC-link system, the phase modular topology allows a convenient converter rearrangement for single-phase supply. However, the 3-Φ Bb phase-modular PFC rectifier is impaired by an increased number of DC-side buck

inductors, i.e., three inductors instead of only one inductor in a conventional  $3-\Phi$  voltage DC-link PFC AC/DC converter system. Moreover, each transistor needs to block and switch the full related DC-link voltage, leading to increased semiconductor costs and reduced power conversion efficiency. Furthermore, extending the 2-L structure shown in **Fig. 1.6c** into a 3-L realization (input and output stage) would result in 24 required power transistors.

A 3-L realization of a 3- $\Phi$  PFC rectifier stage facilitates small EMI filters and hence compact converter realizations [38, 39]. In particular, the T-type (Vienna) voltage source PFC rectifier (VSR)-stage [40, 41] is a widely used industry-standard solution [42–44]. Thus, a 3- $\Phi$  Bb voltage DC-link PFC AC/DC converter system (see **Fig. 1.6d**) is considered to achieve boost-buck functionality, where the boost-type VSR-stage is combined with a buck-type DC/DC-stage (e.g., [45,46]), which again advantageously is realized as a 3-L structure to reduce the magnetics volume and to enable controllability of the VSR-stage DC-link midpoint potential. Therefore, this system (see **Fig. 1.6d**) is selected in the voltage DC-link category and analyzed in detail in this thesis.

Compared to conventional Bb voltage DC-link systems (e.g., **Fig. 1.6d**), bB current DC-link systems (e.g., **Fig. 1.6b**) offer several advantages:

- ▶ Only one shared main DC-link inductor connecting the CSR-stage and the DC/DC-stage is needed in bB current DC-link systems instead of three boost AC-side inductors and, at least, one DC-side inductor, which leads to a compact converter realization with reduced manufacturing costs.

- ▶ Furthermore, since only one main DC-link inductor current has to be regulated in bB current DC-link systems, synergetic control implementation is more straightforward, and the 3-Φ mains currents and the DC output current can be generated in an open-loop manner [47]. In contrast, the 3-Φ mains currents and the DC output current in Bb voltage DC-link systems have to be measured and regulated to ensure a sufficient control bandwidth. Accordingly, a significantly more complex synergetic control structure and/or an increased number of current sensors is required.

- ▶ EMI noise emissions of current source PFC rectifiers are dependent on the DC-link current (proportional to the output power) instead of the DC-link voltage (equal to the output voltage in boost-mode) as in voltage source PFC rectifiers. Thus, less additional EMI noise filtering efforts are required when operating current source rectifiers at high DC

output voltages (in contrast to voltage source rectifiers), i.e., especially for charging of future heavy-duty EVs with the battery voltage up to  $1500\,\mathrm{V}$  [10].

Furthermore, upcoming monolithic bidirectional switches (M-BDSs), which can overcome the factor-of-four penalty in chip area usage of a conventional discrete realization, will significantly decrease the implementation complexity of the  $_{3}$ - $\Phi$  current DC-link PFC rectifier front-end stages since two inverseseries connected transistors can be substituted by only one device with a single drift region for blocking both voltage polarities [48].

#### 1.3 Main Contributions

As outlined above, 3- $\Phi$  bB PFC AC/DC converter systems are fundamental building blocks for conventional isolated and future non-isolated EV battery chargers. Thus, this thesis focuses on two advanced  $3-\Phi$  buck-boost PFC AC/DC converter systems employing either a current DC-link or a voltage DC-link, and their loss-optimal synergetic control over an ultra-wide output voltage range, i.e., from 200 V up to maximum 1000 V. Furthermore, regarding the selected 3-Φ bB current DC-link PFC AC/DC converter system (see Fig. 1.6b), the synergetic control strategy is extended to regulate two independent DC outputs for applications with voltage asymmetries and/or load asymmetries. Moreover, a novel virtual grounding control (VGC) and a ground current control (GCC) are proposed to enable future non-isolated EV chargers, where the ground current is measured and closed-loop controlled to avoid the nuisance tripping of RCDs and to ensure end-user safety. Finally, the proposed synergetic control strategy, operating efficiency, and EMI performance of the 3-Φ bB current DC-link and the 3-Φ Bb voltage DC-link PFC AC/DC converter systems are verified and comparatively evaluated.

#### 1.3.1 Scientific Contributions

The following points, which so far have not been studied in the literature, are carefully analyzed in this thesis:

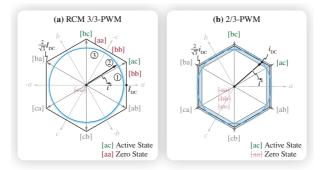

► Advanced PWM Schemes Enabling Optimal Clamping – Conventional space vector pulse-width modulation (SVPWM) schemes are typically utilized for generating the required 3-Φ sinusoidal quantities, either 3-Φ PWM voltages or currents, by modulating a *constant* DC-link voltage in voltage source converters or a *constant* DC-link current in

current source converters. Accordingly, the degrees of freedom associated with a time-varying DC-link voltage/current have typically been disregarded. In this thesis, advanced PWM schemes that enable time-varying DC-link voltage/current are comprehensively reviewed. These include 2/3-PWM operation for current source topologies, as well as 1/3-PWM operation and a proposed 2/3-PWM scheme for voltage source topologies. The focus is on enhancing efficiencies and reducing conducted EMI noise emissions.

- ▶ Synergetic Control / Loss-Optimal Buck-Boost Operation The ultra-wide output voltage range from 200 V up to 1000 V, requiring buck-boost functionality, is necessary for EV charger applications. Therefore, the analyzed 3-Φ buck-boost PFC AC/DC converter systems need to operate in different modes, such as buck-mode (step-down), boost-mode (step-up), and transition-mode in between buck and boost operation. However, a comprehensive analysis and experimental verification of the loss-optimal operations of the two selected 3- $\Phi$  buck-boost current/voltage DC-link PFC AC/DC converter systems under such a wide output voltage range is still missing. This thesis derives lossoptimal operation modes that minimize semiconductor losses for any output voltage level by ensuring the minimum possible DC-link voltage/current and the minimum number of switching actions. Synergetic control strategies are then proposed to achieve democratic/automatic decisions concerning the switching action of the converter stages and a seamless transition between these loss-optimal operating modes, with thorough experimental verifications.

- ► Independent Output Voltage Control for Heavy-Duty EVs To address voltage and load asymmetries occurring in specific applications, such as heavy-duty EVs and high-power heaters, an extended synergetic control strategy is proposed in this thesis. This approach utilizes the 3-Φ bB current DC-link PFC AC/DC converter system (illustrated in Fig. 1.6b) to fully leverage the hardware capacity and supply two independent loads. The proposed extended synergetic control strategy maintains the aforementioned loss-optimal operation, which reduces the number of switching instants by clamping a phase of the CSR-stage (employing only two out of the three phases, i.e., 2/3-PWM, for input current shaping), or by individually clamping the two half-bridges of the DC/DC-stage while minimizing the DC-link current, for any operating point.

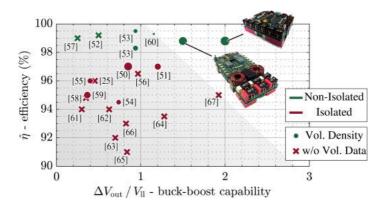

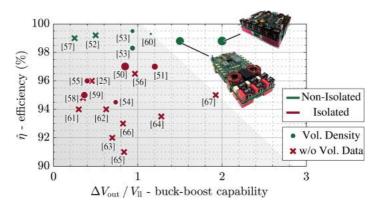

Fig. 1.7: Overview of 3- $\Phi$  EV charger prototypes and products reported in the literature in the coordinate system of peak efficiency  $\hat{\eta}$  and buck-boost capability  $\Delta V_{\rm out}$  /  $V_{\rm ll}$ , where  $\Delta V_{\rm out} = V_{\rm out,max} - V_{\rm out,min}$  and  $V_{\rm ll}$  denominates the RMS value of the grid line-to-line voltage. The two EV chargers built in this thesis are highlighted. University demonstrators: [25,50–60]. Industry products: [61–67]. The volumetric power density values are indicated by according symbol sizes.

▶ VGC and GCC for Non-Isolated EV Chargers – Many EV chargers on the market incorporate LF or HF galvanic isolation stages to ensure electric safety, but this comes at a cost of increased losses, system complexity, and reduced power density. As a result, non-isolated EV chargers are becoming more attractive as they rely on RCDs to protect users from electric shocks. However, the challenge with non-isolated EV chargers is the risk of RCD nuisance tripping. In this thesis, two control strategies, VGC and GCC, are proposed to address this issue. These methods involve measuring and controlling the ground current to limit the LF CM leakage current to less than 6 mA RMS, which is well below typical RCD trip levels. Using the human-body impedance model specified in UL 2202 [49], the proposed method achieves a test voltage of only 110 mV, which is significantly below the most stringent limit of 250 mV in the standard. The new concepts are successfully verified using a 10 kW hardware demonstrator.

# 1.3.2 Demonstrator Systems and Performance Benchmark

As shown in **Fig. 1.7**, the peak efficiencies of most isolated EV chargers described in the literature are below 97 %, while non-isolated solutions can achieve operating efficiencies above 98 %. Similar performance improvements have already been demonstrated for PV inverter systems: compared to traditional solutions that include galvanic isolation, their transformerless counterparts feature an efficiency improvement of 1 % to 2 % and about twice the power density [33, 34].

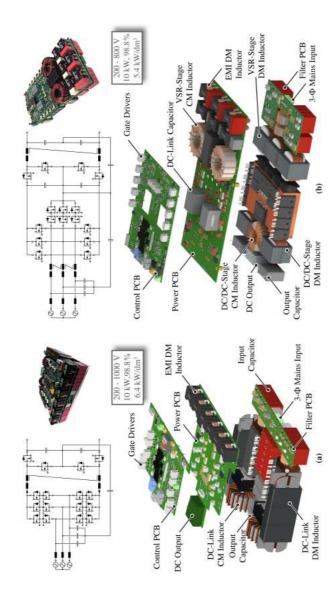

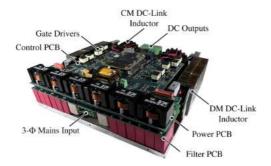

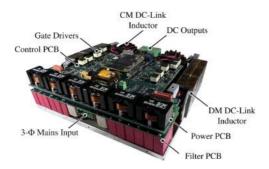

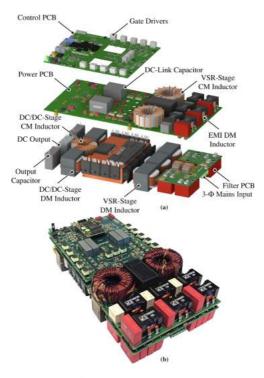

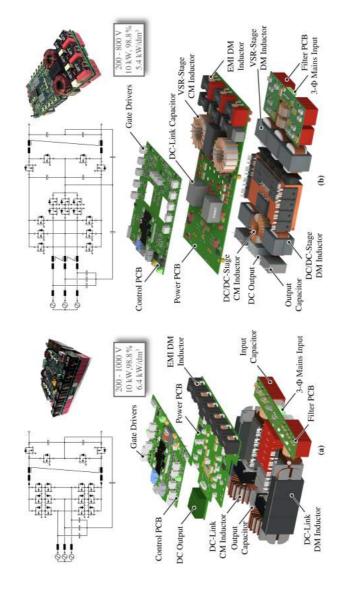

The achieved performance of both hardware demonstrators realized in the course of this thesis is significantly beyond the state-of-the-art in terms of efficiency, power density, and buck-boost capability. The built 3- $\Phi$  bB current DC-link PFC AC/DC converter system (see **Fig. 1.8a**) can cover an ultra-wide output voltage range from 200 V up to 1000 V, i.e., buck-boost capability  $\Delta V_{\rm out}$  /  $V_{\rm II}$  = ( $V_{\rm out,max}$  –  $V_{\rm out,min}$ ) /  $V_{\rm II}$  = 2, with a peak efficiency of 98.8 % and a volumetric power density of 6.4 kW/dm³ (107.5 W/in³). The realized 3- $\Phi$  Bb voltage DC-link PFC AC/DC converter system (see **Fig. 1.8b**) can cover a very wide output range from 200 V up to 800 V, i.e., provides a buck-boost capability of  $\Delta V_{\rm out}$  /  $V_{\rm II}$  = 1.5, with a peak efficiency of 98.8 % and a volumetric power density of 5.4 kW/dm³ (90.9 W/in³).

#### 1.4 List of Publications

Key insights presented in this thesis have already been published or will be published in international patents, international scientific journals, conference proceedings, or presented at workshops. The publications created as part of this thesis, or also in the scope of other related projects, are listed below.

#### 1.4.1 Patents

- [P.4] D. Zhang, J. Huber, and J. W. Kolar, "Virtual Grounding Control and Ground Current Control of Non-Isolated EV Chargers," Patent Application, 2023 (Under Review).

- [P.3] D. Zhang, J. Huber, J. W. Kolar, and N. Nain, "Method for Operating a Current Source Converter, Control Circuit, and Current Source Converter," U.S. Patent, 179/67 588, 2023.

Fig. 1.8: Circuit schematics, exploded views, and photos of the realized 10 kW hardware demonstrators, i.e., (a) a 3-\$ bB current DC-link and (b) a 3-\$\Phi\$ Bb voltage DC-link PFC AC/DC converter system.

- [P.2] D. Zhang, J. Huber, J. W. Kolar, and J. Everts, "Electrical Converter with Overvoltage Protection Circuit," International Patent, WO2022243423A1, 2022.

- [P.1] D. Zhang, M. Guacci, J. W. Kolar, and J. Everts, "Electrical Power Converter," International Patent, WO2021219761A1, 2021.

#### 1.4.2 Journal Papers

- [J.5] D. Zhang, J. Huber, and J. W. Kolar, "A Three-Phase Synergetically Controlled Buck-Boost Current DC-Link EV Charger," IEEE Trans. Power Electron. (Early Access).

- [J.4] D. Zhang, C. Leontaris, J. Huber, and J. W. Kolar, "Optimal Synergetic Control of High-Efficiency Three-Phase/Level Boost-Buck Voltage DC-Link Very Wide Output Voltage Range EV Charger," IEEE J. Emerg. Sel. Topics Power Electron. (Early Access).

- [J.3] D. Zhang, D. Cao, J. Huber, J. Everts, J. W. Kolar, "Non-Isolated Three-Phase Current DC-Link Buck-Boost EV Charger with Virtual Output Midpoint Grounding and Ground Current Control," IEEE Trans. Transp. Electrific. (Early Access).

- [J.2] D. Zhang, D. Cittanti, P. Sun, J. Huber, R. Bojoi, and J. W. Kolar, "Detailed Modeling and In-Situ Calorimetric Verification of Three-Phase Sparse NPC Converter Power Semiconductor Losses," IEEE J. Emerg. Sel. Topics Power Electron, Vol. 11, No. 3, pp. 3409-3423, June 2023.

- [J.1] D. Zhang, D. Cao, J. Huber, and J. W. Kolar, "Three-Phase Synergetically Controlled Current DC-Link AC/DC Buck-Boost Converter with Two Independently Regulated DC Outputs," IEEE Trans. Power Electron., Vol. 38, No. 4, pp. 4195-4202, April 2023.

Moreover, part of the research activity of the author supported, which is reflected in the co-authorship of the following publications:

[J] P. Czyz, T. Guillod, **D. Zhang**, F. Krismer, R. Färber, J. Huber, C. M. Franck, and J. W. Kolar, "Analysis of the Performance Limits of 166 kW / 7 kV Air-Core and Magnetic-Core Medium-Voltage Medium-Frequency Transformers for 1:1-DCX Applications," IEEE J. Emerg. Sel. Topics Power Electron., Vol. 10, No. 3, pp. 2989-3012, June 2022.

[J] M. Guacci, D. Zhang, M. Tatic, D. Bortis, J. W. Kolar, Y. Kinoshita, and H. Ishida, "Three-Phase Two-Third-PWM Buck-Boost Current Source Inverter System Employing Dual-Gate Monolithic Bidirectional GaN e-FETs," CPSS Trans. Power Electron. Appl., Vol. 4, No. 4, pp. 339-354, December 2019.

#### 1.4.3 Conference Papers

- [C.4] D. Zhang, D. Cao, J. Huber, and J. W. Kolar, "Advanced Synergetic Charge Control of Three-Phase PFC Buck-Boost Current DC-Link EV Chargers," Proc. IEEE Workshop Control Modeling Power Electron. (COMPEL), Tel Aviv, Israel, June 20-23, 2022.

- [C.3] D. Zhang, M. Guacci, J. W. Kolar, and J. Everts, "Synergetic Control of a Three-Phase Buck-Boost Current DC-Link Bidirectional EV Battery Charger Considering Wide Output Range and Irregular Mains Conditions," Proc. IEEE Int. Power Electron. Motion Control Conf. (IPEMC-ECCE Asia), Nanjing, China, November 29-December 2, 2020.

- [C.2] D. Zhang, M. Guacci, J. W. Kolar, and J. Everts, "Three-Phase Bidirectional Ultra-Wide Output Voltage Range Current DC-Link AC/DC Buck-Boost Converter," Proc. Annu. Conf. IEEE Ind. Electron. Soc. (IECON), Singapore, October 18-21, 2020.

- [C.1] D. Zhang, M. Guacci, M. Haider, D. Bortis, J. W. Kolar, and J. Everts, "Three-Phase Bidirectional Buck-Boost Current DC-Link EV Battery Charger Featuring a Wide Output Voltage Range of 200 to 1000 V," Proc. IEEE Energy Conversion Congr. Expo. (ECCE USA), Detroit, MI, USA, October 11-15, 2020.

Moreover, part of the research activity of the author supported, which is reflected in the co-authorship of the following publications:

- [C] D. Cao, D. Zhang, J. W. Kolar, J. Huber, "Conceptualization of a Cryogenic 250-A Power Supply for High-Temperature-Superconducting (HTS) Magnets of Future Particle Accelerators," Proc. IEEE Int. Power Electron. Motion Control Conf. (IPEMC-ECCE Asia), Jeju, Korea, May 22-25, 2023.

- [C] N. Nain, **D. Zhang**, J. Huber, J. W. Kolar, K. Leong, and B. Pandya, "Synergetic Control of Three-Phase AC-AC Current-Source Converter

Employing Monolithic Bidirectional 600 V GaN Transistors," Proc. IEEE Workshop Control Modeling Power Electron. (COMPEL), Bogotá, Colombia, November 2-5, 2021. – *Best Paper Award*

#### 1.4.4 Keynotes and Tutorials

- [W.5] D. Zhang, and J. W. Kolar, "Synergetic Control of Non-Isolated Three-Phase Voltage & Current DC-Link EV Chargers," IEEE Power Electronics Society USU (Utah State University, USA) Chapter Events 2023, Online presentation, July 17, 2023.

- [W.4] J. W. Kolar, J. Huber, D. Menzi, and D. Zhang, "Next Generation SiC GaN 3-Φ PFC Rectifier / PWM Inverter Systems," Tutorial at IEEE Southern Power Electron. Conf. (SPEC), Fiji, December 5-8, 2022.

- [W.3] J. W. Kolar, J. Huber, and D. Zhang, "Monolithic Bi-Directional Switches Opening New Horizons in Power Electronics," Keynote Presentation at IEEE Int. Power Electron. Appl. Conf. (PEAC), Xiamen, China, November 4-7, 2022.

- [W.2] J. W. Kolar, J. Huber, and D. Zhang, "Monolithic Bi-Directional Switches Opening New Horizons in Power Electronics," Plenary Talk at Int. Conf. Silicon Carbide Related Materials (ICSCRM), Davos, Switzerland, September 11-16, 2022.

- [W.1] J. W. Kolar, J. Huber, **D. Zhang**, and N. Nain, "Emerging Bidirectional Switches and Their Impact on Future AC Power Converter Applications," Tutorial at IEEE Energy Conversion Congr. Expo. (ECCE USA), Vancouver, Canada, October 10-14, 2021.

#### 1.4.5 Supervised Projects and Theses

- [M.8] M. Akbas, "Design and Realization of High-Efficiency Low-Voltage and High-Current Cryogenic Power Supply Unit for HTS Magnet Systems," ETH Zurich, 2023, Master Thesis LEM2310. Supervision: **D. Zhang**.

- [M.7] J. Kaufmann, "Design and Realization of Three-Phase Boost-Buck Voltage DC-Link Non-Isolated EV Charger," ETH Zurich, 2023, Master Thesis LEM2311. Supervision: D. Zhang.

- [M.6] A. Schneider, "Realization of Cryogenic Test Setup and Components Characterization under Cryogenic Conditions," ETH Zurich, 2023, Bachelor Thesis LEM2312. Supervision: **D. Zhang**.

- [M.5] D. Cao, "Modeling and Control of Three-Phase Buck-Boost Current DC-Link Converter," ETH Zurich, 2021, Master Thesis LEM2142. Supervision: **D. Zhang**.

- [M.4] C. Leontaris, "Design and Realization of a 10 kW Three-Level Three-Phase Boost-Buck Rectifier for EV Charging Applications," ETH Zurich, 2021, Master Thesis LEM2124. Supervision: **D. Zhang**.

- [M.3] P. Sun, "Design and Realization of a Three-Phase Sparse Neutral Point Clamped Converter," ETH Zurich, 2021, Master Thesis LEM2102. Supervision: **D. Zhang**, Davide Cittanti.

- [M.2] D. Cao, "Modulation Scheme Evaluation of Three-Phase Buck-Boost Current DC-Link EV Battery Charger," ETH Zurich, 2020, Semester Project LEM2036. Supervision: **D. Zhang**.

- [M.1] S. Leuch, "DM/CM Inductor Design for Three-Phase Bidirectional Buck-Boost Current DC-Link EV Battery Charger," ETH Zurich, 2020, Semester Project LEM2009. Supervision: **D. Zhang**.

### 1.5 Thesis Outline

According to the goals and contributions mentioned above, the content of the thesis is divided into six main chapters and conclusions. All the chapters can be read independently since the interdependencies have been reduced to a strict minimum.

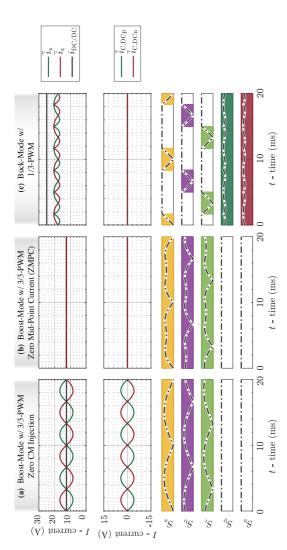

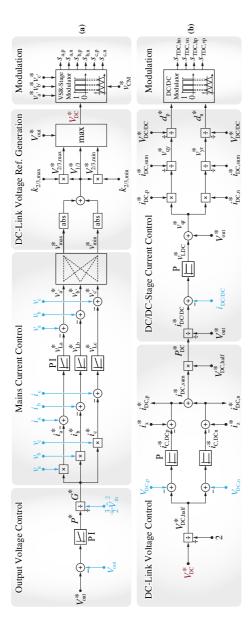

Chapter 2 presents a comprehensive analysis of the advanced 2/3-PWM concept for current DC-link systems, comparing it with the conventional 3/3-PWM scheme. Additionally, a straightforward synergetic control concept of 3-Φ bB current DC-link PFC AC/DC converter system is introduced to cover the loss-optimal operating modes in a wide output voltage range (200 V to 1000 V). For the first time, a complete experimental verification of loss-optimal synergetic operation ensured by the proposed synergetic control is provided, quantifying the loss savings achieved by 2/3-PWM. The results show a flat efficiency characteristic, with efficiencies higher than 98 % for most operating points with output voltages above 400 V and more than 25 % of rated load

- ► Chapter 3 extends the synergetic control strategy of the 3-Φ bB current DC-link PFC AC/DC converter system introduced in Chapter 2 to provide two independently regulated DC outputs and advantageously retain loss-optimum operation, i.e., reduced number of switching instants due to clamping of a phase of the CSR-stage (switching only two out of the three phases, i.e., 2/3-PWM) or individual clamping of the DC/DC-stage's two half-bridges, and minimum possible DC-link current, for any operating point, especially for two *different* output voltages and/or two *different* loads connected to the two outputs.

- ▶ Chapter 4 proposes VGC and GCC techniques to effectively address the nuisance tripping problem of RCDs in future *non-isolated* EV chargers based on the analyzed 3-Φ bB current DC-link PFC AC/DC converter system, while reducing the system complexity and cost compared to traditional isolated solutions. The chapter presents experimental results showing that the proposed VGC and GCC techniques can limit the LF CM leakage current to values below typical RCD trip levels and achieve a touch voltage below the most stringent limit of the standard, thus ensuring end-user safety. The study also discusses the advantages and limitations of the proposed non-isolated converter concept.

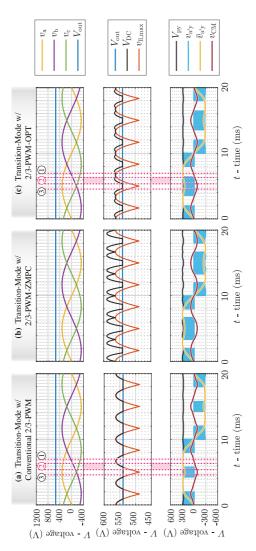

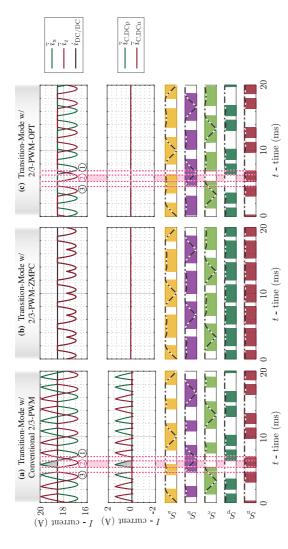

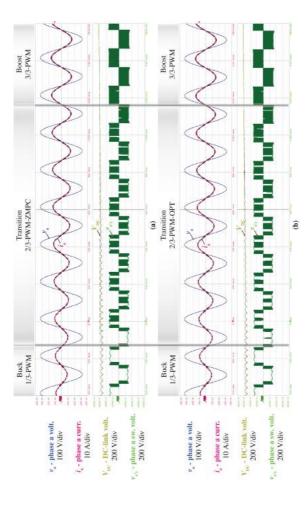

- ▶ Chapter 5 studies the loss-optimum operations of the 3-Φ Bb voltage DC-link AC/DC converter system, considering a wide output voltage range from 200 V to 800 V. Two new 2/3-PWM schemes for the transition-mode, i.e., the operating region between the pure buck-mode and pure boost-mode, are proposed to ensure loss-optimum converter operation. The proposed synergetic operating principle requires only three (out of five) half-bridges to operate with PWM at any given point in time and the minimum possible DC-link voltage is used to ensure minimum switching losses.

- ▶ Chapter 6 first compares the performance of current and voltage DC-link systems, based on the previous analyses and experimental results, in terms of implementation complexity, efficiency, and conducted EMI noise emissions. Then, the most significant findings of this thesis, i.e., loss-optimal operation over an ultra-wide output voltage range and its synergetic control, ground current control enabling future non-isolated EV chargers, and independent output voltage control for heavy-duty EVs are summarized. The thesis concludes with an outlook on topics for further research.

# 2

# A Three-Phase Synergetically Controlled Buck-Boost Current DC-Link EV Charger

#### \_ Chapter Abstract \_\_\_\_\_

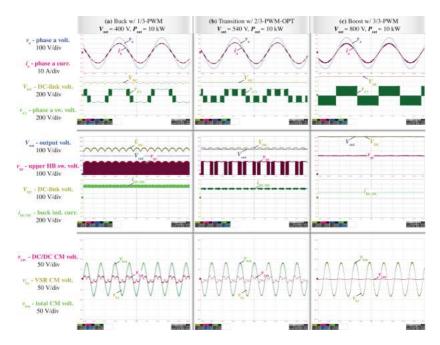

With the ever-increasing share of electric vehicles (EVs) comes a need for highly efficient and compact EV chargers. EV charger modules should provide a wide output voltage range (200 V to 1000 V) to ensure compatibility with various EV battery voltages. Thus, buck-boost functionality is needed, which can advantageously be realized by a current DC-link topology: a buck-type current-source rectifier (CSR) stage and a downstream three-level (3-L) boosttype DC/DC-stage share the main magnetic component (the DC-link inductor). Furthermore, the two stages can operate collaboratively: for low output voltages, the CSR-stage controls the output voltage and the DC/DC-stage is clamped to avoid switching losses; for high output voltages, the DC/DC-stage shapes the DC-link current such that the CSR-stage operates with 2/3-PWM (switching limited to two out of the three phases) and hence with reduced switching losses. This chapter thus introduces a simplified synergetic control concept that ensures this loss-optimum operation of the two-stage system for any output voltage. A compact 10-kW hardware demonstrator with a power density of 6.4 kW/dm³ (107.5 W/in³) is then used to verify the control concept and the seamless transitions between operating modes. For the first time, a system-level experimental demonstration of the loss savings achieved by 2/3-PWM is provided, and pre-compliance conducted EMI test results meet CISPR 11 / Class A. Moreover, a detailed experimental characterization of losses/efficiency over the full range of output voltage and power confirms the loss models and the design procedure presented earlier. Finally, the demonstrator shows quite a flat efficiency characteristic (higher than 98% for most operating points with output voltages above 400 V and more than 25% of rated load) with a peak efficiency of 98.8% at 520 V output voltage and 5 kW. All in all, the presented current DC-link buck-boost PFC rectifier system features a promising solution for future isolated or non-isolated EV charger modules.

#### 2.1 Introduction