Diss. ETH No. 23209

## Advanced Modeling and Multi-Objective Optimization of Power Electronic Converter Systems

A thesis submitted to attain the degree of

DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

> presented by RALPH M. BURKART

MSc ETH born on 10.04.1985 citizen of Luzern, Switzerland

accepted on the recommendation of

Prof. Dr. Johann W. Kolar, examiner Prof. Dr. Hans-Peter Nee, co-examiner

ETH Zurich Power Electronic Systems Laboratory Physikstrasse 3 | ETL I14 8092 Zurich | Switzerland

http://www.pes.ee.ethz.ch

$\bigodot$  2016 by Ralph M. Burkart

Für meine Eltern Rosa und Joe

"I suppose it is tempting, if the only tool you have is a hammer, to treat everything as if it were a nail."

Abraham Maslow

## Acknowledgments

Foremost, I would like to thank Prof. Dr. Johann W. Kolar for giving me the opportunity to conduct my Ph.D. studies at the Power Electronic Systems Laboratory (PES). In particular, I would like to express my gratitude for his generous way of guidance in which he offered me significant scientific freedom regarding my research. At the same I recognize and appreciate the flat hierarchy at PES where the Professor is virtually always available for his Ph.D. students to share with them his valuable advice and incredibly broad expertise. Furthermore, I would like to thank Prof. Dr. Hans-Peter Nee for being part of the examination committee, his valuable inputs towards this thesis and his interest into my work.

I was very lucky to count with the help of the permanent staff of PES, namely Monica Kohn-Müller, Roswitha Coccia, Peter Seitz, Peter Albrecht, Prisca Maurantonio, Damaris Egger and Claudia Stucki. Their outstanding support makes a Ph.D.'s everyday life inestimably easier, thank you very much.

The working conditions at PES could have hardly been better. Besides the excellent facilities which I was privileged to enjoy, it is mostly the people who greatly contributed to the fantastic and motivating working environment. Here I would like to firstly thank my office mate Matthias Kasper for the lively discussions, helpful advice and the countless laughs we had together. I was lucky to share the same experiences also with the rest of the group. These highly skilled and talented researchers are Dominik Bortis, Florian Krismer, Arda Tüysüz, Yanick Lobsiger, Thomas Baumgartner, Patricio Cortés, David Boillat, Roman Bosshard, Jonas Huber, Lukas Fässler, Toke Andersen, Christoph Gammeter, Michael Leibl, Hirofumi Uemura, Thomas Guillod, Daniel Rothmund, Oliver Knecht, Michael Flankl, Pedro Bezerra, Mario Mauerer, Lukas Schrittwieser and Dominik Neumayr. I would like to say thank you for the valuable discussions and the great times we shared together at the conferences and during activities away from work.

The end of my Ph.D. studies sadly also marks the end of another fantastic and unforgettable experience. To my dear friends in appreciation of a glorious time in our shared flat: Thomas Hutter, Matthias Günther, Basil Böhni and Manuel Mühlebach.

Special thanks go to my tennis buddy Stephan Ebneter who substantially helped me to maintain a minimum physical fitness during the last steps of this project. I would like to thank Selina Haeny for her admirable and encouraging way of looking at life. I am very thankful for her love and for her support during the many ups and downs along the way.

Finally, this thesis would not have been possible without the constant support of my family. I therefore wish to express my sincere gratitude to my parents Joe and Rosa, and my brothers Marc and Adrian.

Zurich, August 2016 Ralph M. Burkart

# Contents

| Kurzfassung x |              |                                                    |           |  |  |  |

|---------------|--------------|----------------------------------------------------|-----------|--|--|--|

| Al            | ostra        | act                                                | xv        |  |  |  |

| 1             | Introduction |                                                    |           |  |  |  |

|               | 1.1          | Performance Trends in Power Electronics            | 2         |  |  |  |

|               |              | 1.1.1 Examples                                     | 4         |  |  |  |

|               |              | 1.1.2 Enablers of Performance Trends               | 6         |  |  |  |

|               | 1.2          | Multi-Objective Optimization                       | 9         |  |  |  |

|               |              | 1.2.1 Fundamentals                                 | 10        |  |  |  |

|               |              | 1.2.2 Application to Converter Optimizations       | 13        |  |  |  |

|               |              | 1.2.3 History and State of the Art                 | 15        |  |  |  |

|               |              | 1.2.4 Necessity of Cost Considerations             | 20        |  |  |  |

|               | 1.3          | Scientific Contributions                           | 22        |  |  |  |

|               |              | 1.3.1 Opportunities                                | 26        |  |  |  |

|               |              | 1.3.2 Challenges                                   | 28        |  |  |  |

|               | 1.4          | Outline of the Thesis                              | 29        |  |  |  |

|               | 1.5          | List of Publications                               | 30        |  |  |  |

| <b>2</b>      | Vir          | tual Prototyping Routine                           | 35        |  |  |  |

| -             | 2.1          | Main Design Routine                                | 36        |  |  |  |

|               | 2.1          | 2.1.1 Problem Analysis                             | 36        |  |  |  |

|               |              | 2.1.2 Approach                                     | 38        |  |  |  |

|               |              | 2.1.2 Approach                                     | 43        |  |  |  |

|               | 2.2          | Component Design Routines                          | 47        |  |  |  |

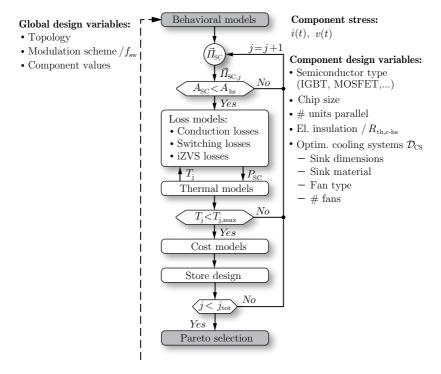

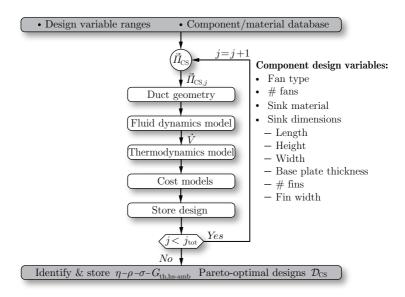

|               | 2.2          | 2.2.1 Semiconductors and Cooling System            | 47        |  |  |  |

|               |              | 2.2.2 Magnetics                                    | 51        |  |  |  |

|               |              | 2.2.3 Capacitors                                   | 53        |  |  |  |

|               | 2.3          | Software Implementation                            | 55        |  |  |  |

|               | 2.0          | 2.3.1 Execution of the Virtual Prototyping Routine | 56        |  |  |  |

|               |              | 2.3.2 Identification of the Pareto front           | 56        |  |  |  |

|               |              |                                                    |           |  |  |  |

| 3             |              | lti-Physics Component Modeling                     | <b>59</b> |  |  |  |

|               | 3.1          | Semiconductors                                     | 60        |  |  |  |

|               |              | 3.1.1 Conduction Losses                            | 60        |  |  |  |

|               |              | 3.1.2 Switching Losses                             | 63        |  |  |  |

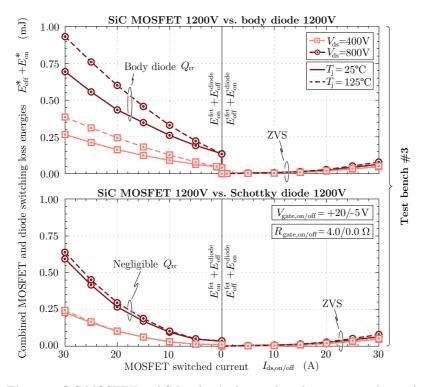

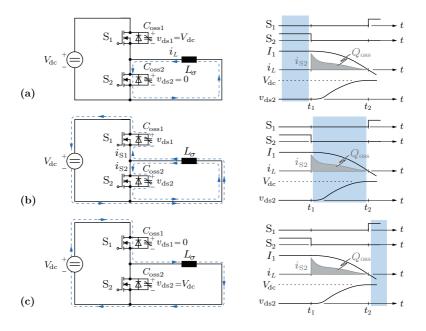

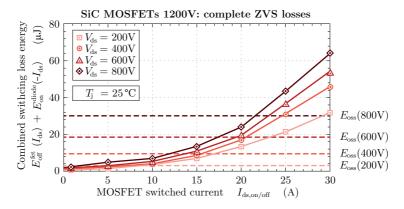

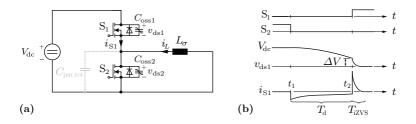

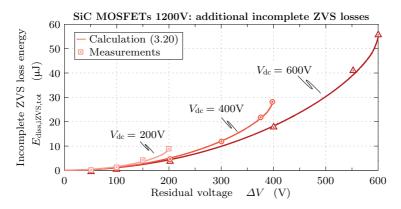

|               |              | 3.1.3 Incomplete ZVS Losses                        | 69        |  |  |  |

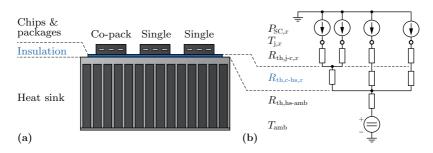

|               |              | 3.1.4 Thermal Modeling                             | 77        |  |  |  |

|   | 3.2                                    | Coolii | ng Systems                                                              | 79  |  |  |  |  |  |

|---|----------------------------------------|--------|-------------------------------------------------------------------------|-----|--|--|--|--|--|

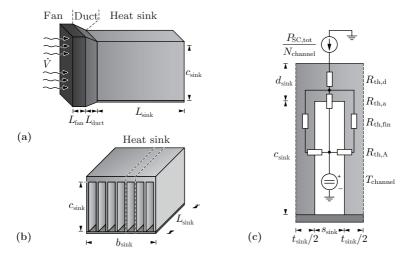

|   |                                        | 3.2.1  | Fluid Dynamics Model                                                    | 80  |  |  |  |  |  |

|   |                                        | 3.2.2  | Thermodynamics Model                                                    | 80  |  |  |  |  |  |

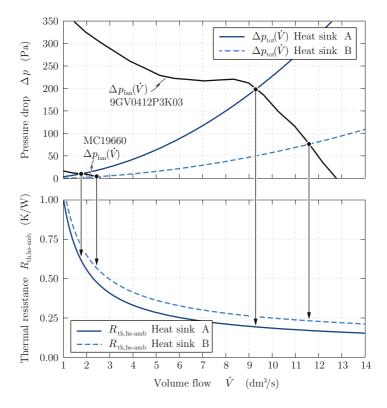

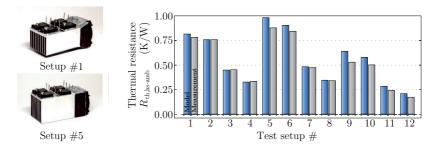

|   |                                        | 3.2.3  | Experimental Verification                                               | 82  |  |  |  |  |  |

|   | 3.3                                    | Magn   | etics                                                                   | 83  |  |  |  |  |  |

|   |                                        | 3.3.1  | Reluctance Model                                                        | 83  |  |  |  |  |  |

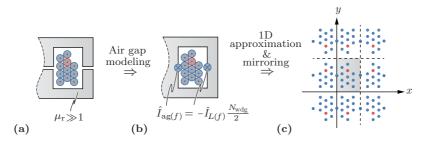

|   |                                        | 3.3.2  | Winding Losses                                                          | 84  |  |  |  |  |  |

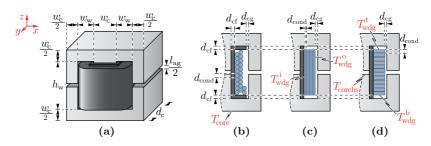

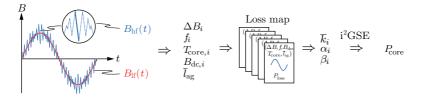

|   |                                        | 3.3.3  | Core Losses                                                             | 89  |  |  |  |  |  |

|   |                                        | 3.3.4  | Thermal Modeling                                                        | 94  |  |  |  |  |  |

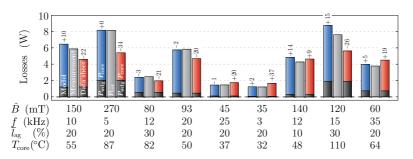

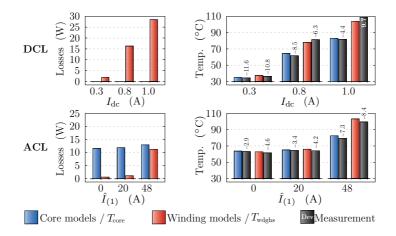

|   |                                        | 3.3.5  | Experimental Verifications                                              | 97  |  |  |  |  |  |

|   | 3.4                                    | Capac  | citors                                                                  | 100 |  |  |  |  |  |

|   |                                        | 3.4.1  | Loss Models                                                             | 100 |  |  |  |  |  |

|   |                                        | 3.4.2  | Parametrization                                                         | 101 |  |  |  |  |  |

| 4 | Cos                                    | st Mod | leling                                                                  | 103 |  |  |  |  |  |

|   | 4.1                                    |        | ture Review                                                             | 104 |  |  |  |  |  |

|   | 4.2                                    | Challe | enges and Approach                                                      | 106 |  |  |  |  |  |

|   | 4.3                                    |        | ation of Component Cost Models                                          | 108 |  |  |  |  |  |

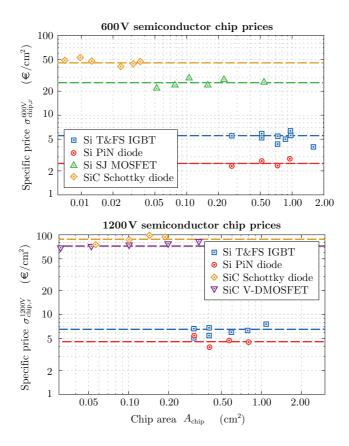

|   |                                        | 4.3.1  | Power Semiconductors                                                    | 108 |  |  |  |  |  |

|   |                                        | 4.3.2  | Magnetics                                                               | 111 |  |  |  |  |  |

|   |                                        | 4.3.3  | Capacitors                                                              | 113 |  |  |  |  |  |

|   |                                        | 4.3.4  | Cooling Systems                                                         | 115 |  |  |  |  |  |

|   |                                        | 4.3.5  | PCBs and Auxiliary Electronics                                          | 117 |  |  |  |  |  |

|   | 4.4                                    | Concl  | usion and Outlook $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 120 |  |  |  |  |  |

| 5 | Case Study I: DC/DC Converter System 1 |        |                                                                         |     |  |  |  |  |  |

| Ŭ | 5.1                                    | Motiv  |                                                                         | 122 |  |  |  |  |  |

|   | 5.2                                    |        | ogies, Modulation Schemes and Components                                | 126 |  |  |  |  |  |

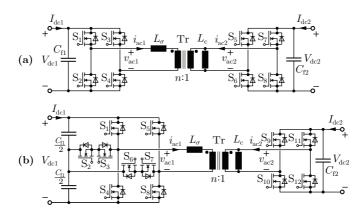

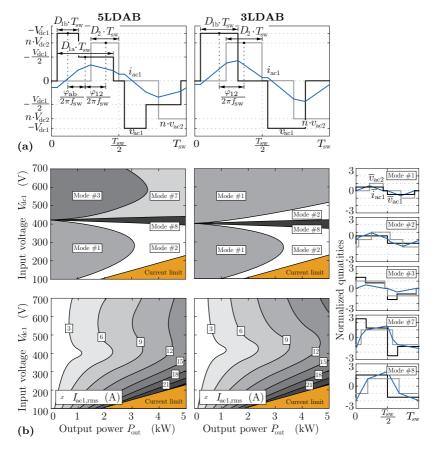

|   | 0                                      | 5.2.1  | Topologies and Modulation Schemes                                       | 126 |  |  |  |  |  |

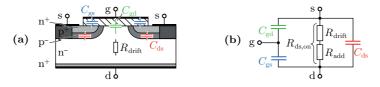

|   |                                        | 5.2.2  | Semiconductors                                                          | 129 |  |  |  |  |  |

|   |                                        | 5.2.3  | Cooling System                                                          | 133 |  |  |  |  |  |

|   |                                        | 5.2.4  | Magnetics                                                               | 133 |  |  |  |  |  |

|   |                                        | 5.2.5  | Capacitors                                                              | 134 |  |  |  |  |  |

|   |                                        | 5.2.6  | PCB                                                                     | 134 |  |  |  |  |  |

|   |                                        | 5.2.7  | Auxiliary Electronics                                                   | 134 |  |  |  |  |  |

|   | 5.3                                    | Mode   |                                                                         | 135 |  |  |  |  |  |

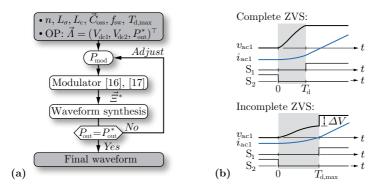

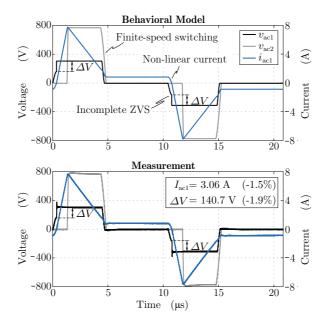

|   |                                        | 5.3.1  | Behavioral Model                                                        | 135 |  |  |  |  |  |

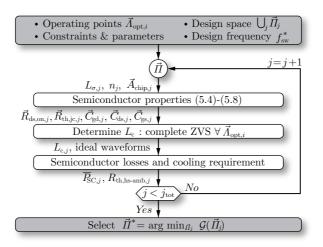

|   |                                        | 5.3.2  | Semiconductors                                                          | 136 |  |  |  |  |  |

|   |                                        | 5.3.3  | Cooling System                                                          | 138 |  |  |  |  |  |

|   |                                        | 5.3.4  | Passives                                                                | 138 |  |  |  |  |  |

|   |                                        | 5.3.5  | PCB                                                                     | 138 |  |  |  |  |  |

|   |            | 5.3.6                                         | Auxiliary Electronics                                                                                                                         |

|---|------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.4        | Exper                                         | imental Verification                                                                                                                          |

|   | 5.5        | Desigr                                        | and Optimization Routines                                                                                                                     |

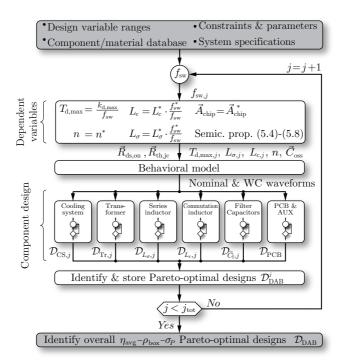

|   |            | 5.5.1                                         | Virtual Prototyping Routine                                                                                                                   |

|   |            | 5.5.2                                         | Dependent Global Design Variables                                                                                                             |

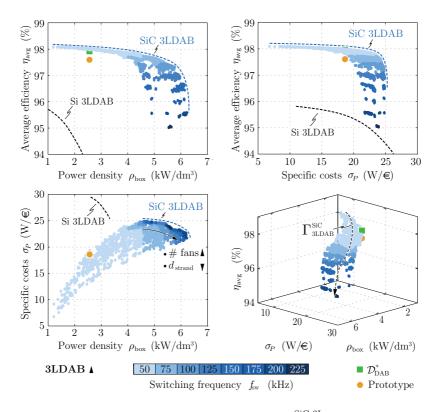

|   | 5.6        | Perfor                                        | mance Space Analysis                                                                                                                          |

|   |            | 5.6.1                                         | Comparison of the Topologies                                                                                                                  |

|   |            | 5.6.2                                         | Best Converter Concept                                                                                                                        |

|   |            | 5.6.3                                         | Impact of Parasitic Capacitances                                                                                                              |

|   |            | 5.6.4                                         | Increasing Inductor Volumes                                                                                                                   |

|   |            | 5.6.5                                         | Comparison to Prototype                                                                                                                       |

|   | 5.7        | Summ                                          | ary                                                                                                                                           |

|   |            | 5.7.1                                         | Findings                                                                                                                                      |

|   |            | 5.7.2                                         | Conclusion                                                                                                                                    |

| ~ | a          | <u>a</u> , 1                                  |                                                                                                                                               |

| 6 |            |                                               | y II: DC/AC Converter System 171                                                                                                              |

|   | 6.1        | Motiva                                        |                                                                                                                                               |

|   | 6.2        | -                                             | pgies and Modulation Schemes                                                                                                                  |

|   |            | 6.2.1                                         | Boost Converter Stages                                                                                                                        |

|   |            | 6.2.2                                         | Inverter Stages                                                                                                                               |

|   | <i>c</i> 2 | 6.2.3                                         | EMI Filter Stages                                                                                                                             |

|   | 6.3        | -                                             | onents and Materials                                                                                                                          |

|   |            | 6.3.1                                         | Semiconductors $\dots$ 182                                                                                                                    |

|   |            | 6.3.2                                         | Cooling System                                                                                                                                |

|   |            | 6.3.3                                         | Inductors                                                                                                                                     |

|   |            | 6.3.4                                         | Capacitors                                                                                                                                    |

|   | <u> </u>   | 6.3.5                                         | PCB and Auxiliary Electronics                                                                                                                 |

|   | 6.4        | Model                                         | 0                                                                                                                                             |

|   |            | 6.4.1                                         | Behavioral Models                                                                                                                             |

|   |            | 6.4.2                                         | Semiconductor Models                                                                                                                          |

|   |            | 6.4.3                                         | 0                                                                                                                                             |

|   |            | 6.4.4                                         | Inductors                                                                                                                                     |

|   |            | $\begin{array}{c} 6.4.5 \\ 6.4.6 \end{array}$ | Capacitors                                                                                                                                    |

|   | 6 5        |                                               | PCB and Auxiliary Electronics                                                                                                                 |

|   | 6.5        | -                                             | and Optimization Routines $\dots \dots \dots$ |

|   |            | 6.5.1                                         | Virtual Prototyping Routine                                                                                                                   |

|   | 6.6        | 6.5.2<br>Domfor                               | Separation of Global Design Variables 194                                                                                                     |

|   | 0.0        | 6.6.1                                         | mance Space Analysis                                                                                                                          |

|   |            | 6.6.1<br>6.6.2                                | Core Materials                                                                                                                                |

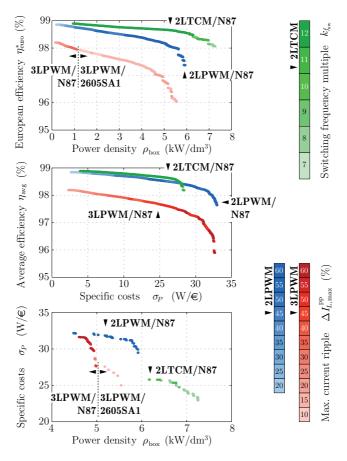

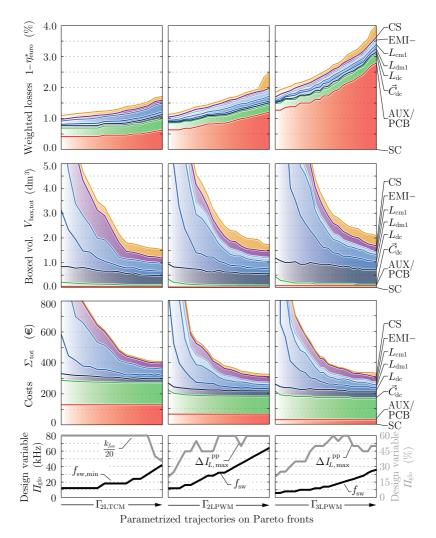

|   |            | 0.0.2                                         | Comparison of Topologies                                                                                                                      |

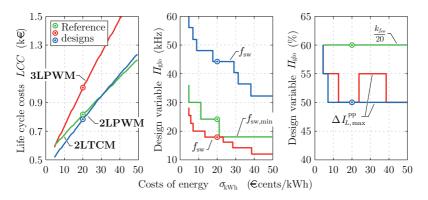

|                  | 6.7 | LCC Mission Cost Space Analysis          | 210        |  |  |  |

|------------------|-----|------------------------------------------|------------|--|--|--|

|                  |     | 6.7.1 Mission Cost Function              | 212        |  |  |  |

|                  |     | 6.7.2 Comparison                         | 214        |  |  |  |

|                  |     | 6.7.3 Proposed Candidate Design          | 215        |  |  |  |

|                  | 6.8 | Summary                                  | 215        |  |  |  |

|                  |     | 6.8.1 Findings                           | 216        |  |  |  |

|                  |     | 6.8.2 Conclusions                        | 219        |  |  |  |

| 7                | Con | clusion and Outlook                      | <b>221</b> |  |  |  |

|                  | 7.1 | Conclusions: Virtual Prototyping Routine | 223        |  |  |  |

|                  | 7.2 | Conclusions: Case Studies                | 224        |  |  |  |

|                  | 7.3 | Outlook                                  | 225        |  |  |  |

|                  |     | 7.3.1 SiC Transistors                    | 225        |  |  |  |

|                  |     | 7.3.2 Further Potentials of MOO          | 226        |  |  |  |

| Nomenclature     |     |                                          |            |  |  |  |

| Bibliography     |     |                                          |            |  |  |  |

| Curriculum Vitae |     |                                          |            |  |  |  |

# Kurzfassung

Dank der anhaltenden Fortschritte im Bereich der Leistungselektronik erfährt eine Vielzahl von Anwendungen elektrischer Energie eine stetig wachsende Durchdringung mit leistungselektronischen Konvertersystemen. Prominente Beispiele sind die Umwälzungen im Bereich der Energieerzeugung und –übertragung (Solar- und Windenergie, "Smart-Grid") und die voranschreitende Elektrifizierung der Mobilität, welche beide durch erhöhtes Umweltbewusstsein und gesteigerte Funktionalitätsansprüche der modernen Gesellschaft getrieben sind. Für die Zukunft kann erwartet werden, dass der Bedarf nach noch leistungsfähigeren Konvertersystemen mit erhöhter Effizienz, Zuverlässigkeit und Funktionalität bei gleichzeitiger Reduktion von Kosten, Gewicht, Bauvolumen und Entwicklungszeit weiter steigen wird.

Das Studium der Fachliteratur zeigt, dass die Auslegungen und Optimierungen von Konvertersystemen oft nur punktuell und unter dem Gesichtspunkt von nur einem Zielkriterium oder wenigen Zielkriterien durchgeführt werden. Dies ist oft bedingt durch das Fehlen eines systematischen Ansatzes, der den typisch auftretenden Zielkonflikten zwischen den Performancegrössen (z.B. Bauvolumen gegen Effizienz) hinreichend Rechnung trägt. Darüber hinaus fehlen oft auch die geeigneten Modelle für die Quantifizierung von zusätzlichen Kenngrössen. Dies trifft in besonderem Masse für die Kostenbewertung von typischen Konverterkomponenten zu. Insgesamt können diese Umstände dazu führen, dass die optimale Lösung (Topologie, Modulationsverfahren und Auslegung) nicht gefunden wird, da die betrachteten Konvertersysteme und Technologien zu wenig umfassend bewertet und miteinander verglichen werden können.

Der Schwerpunkt dieser Dissertation liegt daher in der Entwicklung von Methoden welche systematische Mehrkriterien-Optimierungen sowie umfassende Vergleiche von leistungselektronischen Konvertersystemen hinsichtlich Effizienz, Volumen, Gewicht und Kosten ermöglichen. Hierzu werden auf Basis von analytischen Rechnungen, Simulationen und Messungen neue Modelle entwickelt, die typische Komponenten von Konvertersystemen wie Leistungshalbleiter, Induktivitäten, Kondensatoren, Kühler und Leiterplatten hinsichtlich dieser Kenngrössen bewerten können. Des Weiteren werden Modelle zur Beschreibung des Konverterverhaltens und der sich einstellenden Strom- und Spannungsverläufe abhängig vom Modulationsverfahren und Betriebspunkt hinzugefügt, wobei der Modellierung der Netzrückwirkungen und der elektromagnetischen Verträglichkeit (EMV) besondere Beachtung geschenkt wird. Das Ziel der Methodik besteht in der möglichst präzisen Voraussage der Eigenschaften eines Konvertersystems. Dies erlaubt eine effektive Systemoptimierung bei gleichzeitiger Reduktion der Anzahl gebauter Hardware Prototypen und insgesamt kürzerer Entwicklungszeit.

Die vorgeschlagenen Methoden werden für die Mehrkriterien-Optimierung und den Vergleich verschiedener DC/DC- und DC/AC-Anwendungen im Bereich der erneuerbaren Energien und unter Miteinbezug von SiC Leistungshalbleiter der neuesten Generation verwendet. Die Anwendungsbeispiele verdeutlichen einerseits die Fähigkeit der Methoden, hochkomplexe Optimierungsprobleme mit vergleichsweise kleinem Rechen- und Zeitaufwand lösen zu können. Andererseits beweisen Messungen anhand eines implementierten DC/DC Laborprototyps die hohe Modellgenauigkeit der Methoden. Die Ergebnisse der beiden Mehrkriterien-Optimierungen zeigen auf, dass der Einsatz von SiC Leistungshalbleiter in den betrachteten Anwendungen trotz höherer Bauteilkosten gegenüber herkömmlichen Si Leistungshalbleiter sinnvoll ist. In beiden Beispielen ermöglichen die überlegenen Eigenschaften von SiC Leistungshalbleiter erhebliche Verbesserungen der Effizienz, Leistungsdichte und Funktionalität der Konvertersysteme bei vergleichbaren Kosten des Gesamtsystems.

## Abstract

As a result of the ongoing improvements in the area of power electronics, the penetration of power electronic converter systems into numerous traditional and modern applications has continuously been increasing. A prominent example is the developments in today's electric power systems towards smart grids featuring high shares of new renewable energy sources such as solar and wind. Another example is the growing utilization of electric propulsion in automobiles and aircraft. Both examples are driven by the increased environmental awareness and the demand for higher functionality of the modern society. Based on the observed trends in state-of-the-art applications, it can be expected that the need for enhanced power electronic converter systems with a higher efficiency, reliability and functionality at concurrently lower costs, weight, volume and development time will further increase in the near future.

The analysis of the relevant literature shows that the dimensioning and optimization of converter systems is often carried out with a limited scope and focusing on only one or a few performance criteria. This is often a consequence of a missing systematic approach which enables a comprehensive consideration of the inherent trade-offs between different performance measures (e.g. converter volume vs. losses). Furthermore, the employment of such an approach is often prohibited due to incomplete modeling frameworks to quantitatively assess the respective performance measures. Notably, suitable cost models to assess the costs of the typical components in converter systems are rare to find in literature. As a result of these deficits, it is unlikely that the optimal solution (topology, modulation scheme and component dimensioning) for a given application can be found by such limited approaches.

The main focus of this thesis is thus set on the derivation of a suitable methodology which enables a systematic multi-objective optimization and comprehensive comparison of power electronic converter systems regarding achievable efficiency, volume, weight and costs. Thereby, a modeling framework is established which allows for the assessment of typical converter components such as semiconductors, inductors, capacitors, cooling systems and printed circuit boards regarding the selected performance measures. In addition to the component models, further models are developed which describe the converter behavior and the resulting current and voltage waveforms in the system depending on the employed modulation scheme and operating point. The models and their parameters are derived based on analytical calculations, simulations, measurements and empirical research. The primary aim of the proposed design method is the precise prediction of the converter characteristics which enables an effective and efficient system optimization with fewer hardware prototype iterations and a shorter time to market.

The proposed methodology is applied to the multi-objective optimization and comparison of various DC/DC and DC/AC converter systems under consideration of the latest available SiC semiconductors. The case studies on the one hand highlight the capability of the employed methodology to handle complex optimization problems and to find the corresponding solutions with a comparably low computational effort and time need. Experimental measurements on an implemented DC/DC hardware prototype on the other hand verify the high accuracy of the employed models. The results of the two case studies reveal that the employment of SiC semiconductors in the considered applications is attractive despite the higher costs of SiC semiconductors in contrast to conventional Si components. In both examples, the superior performance of SiC enables considerable improvements regarding efficiency, power density and functionality of the converter systems at comparable overall system costs.

# Introduction

THE start of the Industrial Revolution in the late 18. century marked the beginning of an ongoing period in which technological advancements and innovations have become the main driver of increased wealth and economical growth. In this context, the utilization of electrical power by means of power electronic converter systems has made major contributions towards a higher productivity and prosperity. Power electronics was a prerequisite for the automation in industry, for modern wireless communication, the world wide web and the enabler of electromobility. At present time, power electronics represents the key technology to overcome some of the most urgent challenges of modern society, i.e. the rapidly growing energy demand, the scarcity of fossil fuels and the global warming associated with the predominant utilization of fossil fuels in the energy supply. One of the most promising options to combat these challenges is the replacement of conventional fossil-fueled technologies with renewable energy sources such as photovoltaics (PV), wind power and wave power. Here, power electronics is the enabling technology which allows the large-scale integration into the grid and the efficient distribution to the loads.

The increasing utilization of electrical equipment and appliances in most areas of modern society has been accompanied by significant improvements of the corresponding power electronic converter systems. In fact, further and steady improvements, i.e. a higher performance of the power electronic converter systems are mandatory to guarantee a continuous growth of the productivity and wealth, to open up new fields of application and to overcome the challenge of clean energy generation.

In this chapter, different performance measures of power electronic converter systems are defined and shown to be continuously improving in commercial systems. Furthermore, it is discussed by what means performance can be improved. Eventually, system optimization and in particular multi-objective optimization-based virtual prototyping considering the power conversion efficiency, the volume and the costs is proposed as a powerful means to boost the performance of today's power electronic converter systems.

## 1.1 Performance Trends in Power Electronics

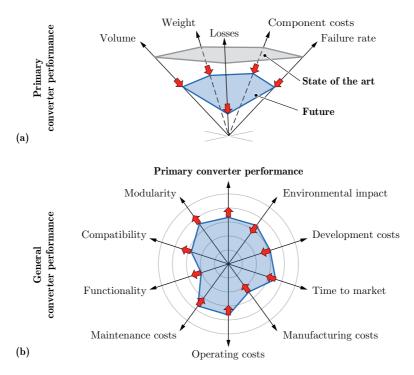

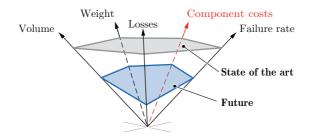

The performance of a power electronic converter system can be defined using a range of converter performance measures. Typical technical quantitative measures are the losses of the power conversion, the converter weight, the volume, the component costs and the failure rate as depicted in Fig. 1.1(a). These measures are largely determined by the implementation of the converter system, i.e. the selection of the topology, modulation scheme, components and the converter layout according to a set of given specifications (e.g. required output power, operating conditions, etc.). For the remainder of this thesis, these measures are referred to as primary performance measures. In contrast, a more generalized definition of the performance of a power electronic converter system may, in addition to the primary converter performance, also include further measures which can also be of nontechnical and/or qualitative nature and furthermore not only be determined by the converter's implementation. Examples of such general converter measures are given in Fig. 1.1(b). Measures such as the converter functionality or the compatibility (with other systems) are rather qualitative measures and are determined by features such as galvanic isolation, bidirectional power flow or the offered grid services. Factors other than the converter's implementation which have an impact on the general converter performance measure are the labor costs (having an impact on the development, manufacturing and maintenance costs) or the manufacturing processes in the factory (influencing the environmental impact and again the manufacturing costs). The analysis of the historical evolution of commercial power electronic converter systems shows a general trend towards a higher converter performance, i.e. a continuous improvement of both the primary and general performance measures.

Fig. 1.1: Performance measures and future trends of power electronic converter systems. (a) Primary converter performance defined by technical quantitative measures which are largely determined by the implementation of the converter, i.e. the selection of the topology, modulation scheme, components and the converter layout. (b) General converter performance which in addition to the primary converter performance also includes non-technical, qualitative performance measures which are not only determined by the implementation of the converter but also other factors (e.g. labor costs as part of the manufacturing costs). A general trend towards a higher performance, i.e. a continuous improvement of all performance measures as indicated by red arrows can be observed in commercial systems (cf. Fig. 1.2). This thesis mainly deals with the improvement of the primary performance of power electronic converter systems.

#### 1.1.1 Examples

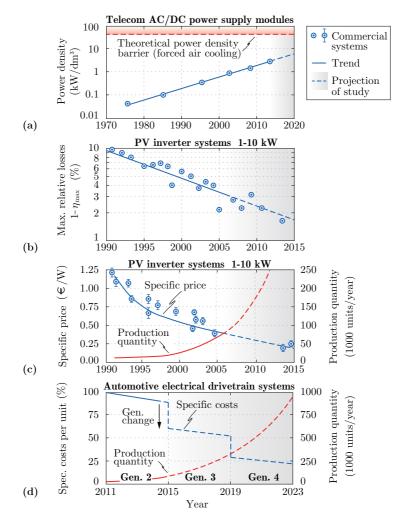

The following examples depict performance trends for commercial telecom AC/DC power supply modules, PV inverters and converters in automotive applications based on market surveys and conference contributions of the respective industries.

- ▶ In Fig. 1.2(a), the continuous reduction of the relative volume, i.e. the increase of the power density is shown for 2-stage telecom AC/DC power supply modules comprising a power factor correction (PFC) rectifier and a DC/DC converter stage [1–4]. The trend line based on the shown real commercial systems indicates an increase of the power density by a factor of 10 every 20 year. The reduction in volume has mainly been achieved by changing from natural convection to forced air cooling and by increasing the switching frequency [8]. Assuming forced air cooling, the theoretical power density barrier [3] can only be overcome with new semiconductor technologies allowing for higher junction temperatures and/or lower losses.

- ▶ Fig. 1.2(b) shows the historical loss reduction, i.e. the increase of the efficiency of PV inverter systems with a rated power of 1-10 kW. Such systems are predominantly used in residential applications. The data representing commercial systems proves a loss reduction by a factor of 2 every 10 years. A market survey on the losses of state-of-the-art systems reveals that the projection of the studies in 2006 [5,6] were accurate.

- ► The reduction of the relative price of PV inverter systems with a rated power of 1-10 kW can be seen in Fig. 1.2(c). In addition, the underlaying study [5] emphasizes the importance of economy of scale to reduce the costs which eventually translates into lower system prices. A factor of 2 in price reduction every 10 years is projected by the study. A market survey on commercial systems in 2015 proof the study to be accurate, i.e. system costs of approximately 0.2 €/w in contrast to 0.4 €/w in 2005 were found.

- ▶ In Fig. 1.2(d), The projected evolution of the costs of electrical drivetrain systems in automotive applications [7] shows that the cost reduction is driven by different factors. On the one hand, economy of scale allows for continuously decreasing production costs at a rate of approximately 3% per year. On the other hand,

Fig. 1.2: Performance trends of commercial power electronic converter systems. (a) Increase of the power density of 2-stage telecom AC/DC PFC rectifier modules [1–4] and theoretical barrier as calculated in [3]. (b), (c) Loss and price reduction of PV inverter systems as shown in [5, 6]. The systems for the projected years were added based on a market survey. (d) Cost reduction enabled by economy of scale and generation changes (modularization and standardization of the converters) for automotive systems as projected in [7].

major optimizations of the system (here modularization and integration) lead to generation changes. A generation change is typically accompanied by a significant and stepwise reduction of the costs within a short time. On overall, a cost reduction of 10 % per year is expected.

▶ The evolution of PV inverter systems serves as an example for the continuously increasing functionality (general performance measure) of power electronic converter systems. Due to the fast growing penetration of distributed renewable energy sources on all levels of the distribution grid, PV inverters are required to offer more and more grid services. Modern PV inverters must feature low-voltage ride-through (LVRT) capabilities, must support the grid voltage control with reactive power provision and facilitate the frequency stability by means of dynamic output power control [9–11].

The above examples emphasize the reality of the trend towards higher system performances in power electronics. Whereas the *driver* of these performance improvements is the obvious urge towards a higher productivity and economical growth, it remains to be discussed what the *enablers* of the performance trends are.

### 1.1.2 Enablers of Performance Trends

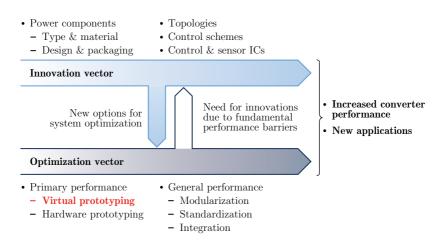

Consider the simplified conceptual view on the research and development activities in power electronics depicted in **Fig. 1.3**. The shown activities can be grouped and summarized into two distinct vectors

#### Innovation Vector

The innovation vector summarizes the activities aiming at the search and introduction of new building blocks for the converter design. In this thesis, building blocks denote the converter topologies, the control schemes and the converter components. Examples of innovations are:

- ▶ Novel power components, i.e. semiconductors, magnetics, capacitors, cooling systems and printed circuit boards (PCB). Possible novelties include:

- Novel types, e.g. the insulated-gate bipolar transistor (IGBT) in 1979 [12],

Fig. 1.3: Main vectors of research and development activities in power electronics aiming at higher converter performances and new applications. On the one hand, innovation deals with the search for *novel* building blocks for the converter design. On the other hand, optimization attempts to optimize the converter performance based on *given* building blocks. The main topic of this thesis is the research and application of advanced concepts in the field of virtual prototyping.

- Novel materials, e.g. wide bandgap (WBG) materials for semiconductors or new core materials,

- Novel designs and shapes, e.g. flexible PCBs or core shapes, or

- Novel packaging, e.g. discrete semiconductor packages with Kelvin source [13];

- ▶ Novel topologies, e.g. the H5 topology for PV inverters [14] or the modular multi-level converter (MMC) [15];

- ▶ Novel control schemes, e.g. minimum rms current control for dual active bridge (DAB) topologies [16,17]; or

- ▶ Novel control and sensor ICs, e.g. the introduction of microcontrollers enabling digital control in the 1970s.

#### **Optimization Vector**

Contrary to the innovation vector, activities summarized by the optimization vector are restricted to the *given* building blocks and attempt to optimize the primary and general converter performance (cf. **Fig. 1.1**) solely based on the available topologies, control schemes and components. Some of the possible strategies which can be pursued are:

- ▶ Virtual prototyping: the employment of mathematical models and/or multi-physics simulations to digitally synthesize converter systems can be summarized as virtual prototyping [8,18,19]. Virtual prototyping tools can be used to investigate and optimize the converter performance as a function of the available building blocks.

- ▶ *Hardware prototyping*: the investigation and optimization of the performance of a particular converter system can also be carried out by means of experimental measurements and (iterative) hardware prototyping [8, 19].

- ▶ *Modularization* focuses on increasing the reusability of subsystems based on defined interfaces. This strategy increases the flexibility in the system design process, reduces the time to market and may lower the maintenance effort [20].

- ▶ Standardization is an important enabler of system modularization by means of providing standardized interfaces between the subsystems [20]. Furthermore, standardization may also include the aim of employing the same components, topologies and control schemes in as many systems or subsystems as possible [21]. This strategy can help to reduce the development costs, the complexity of the manufacturing as well as the involved logistics.

- ▶ Integration is the replacement of a number of building blocks with a single building block offering the same functionality. Advantages may include higher compactness, reduced development costs and a lower manufacturing complexity [22,23]. Examples are the use of ICs rather than discrete logics or the employment of power semiconductor modules replacing discrete semiconductors and their interconnecting wiring.

Virtual and hardware prototyping is typically employed to study and optimize the primary performance measures (i.e. the losses, the weight or the component costs) of the converter system. Contrarily, the common feature of modularization, standardization and integration is the predominant focus on improving general performance measures such as increased flexibility, lower complexity and a shorter time to market. The common approach to achieve this is by restricting the available building blocks, i.e. by narrowing down the choice of the components, topologies and control schemes.

#### Interaction between Innovation and Optimization

The above discussed research and development activities have in common that they eventually aim at increasing the performance of a power electronic converter system and at enabling new fields of application. Both innovation and optimization interact and stimulate each other: on the one hand, innovation, i.e. novel topologies, control schemes and components always offers new options and opportunities for optimization. On the other hand, systematic optimization can be used to identify the absolute performance trade-offs and performance barriers (cf. **Fig. 1.2**) of the available technologies and thus indicates where innovation is mandatory and the most remunerative.

## 1.2 Multi-Objective Optimization

This thesis deals with the investigation and application of new concepts and methods in the field of virtual prototyping for power electronic converter systems. An advanced multi-objective optimization (MOO) approach based on detailed mathematical multi-physics models of the system and underlaying converter components is proposed. The optimization objectives are the power conversion efficiency, the converter volume and the component costs. The ultimate goal of the approach is the determination of the Pareto fronts, i.e. the absolute performance trade-off limits for a given set of converter building blocks (topologies, control schemes and components).

This section first revises the fundamental principles of MOO. In a subsequent step, it is discussed how MOO can be incorporated into virtual prototyping of power electronic converter systems. A historical review of the topic as well as a discussion of state-of-the-art contributions which can be found in the relevant literature are presented in the

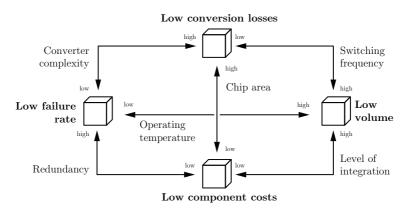

Fig. 1.4: Fundamental performance trade-offs in power electronic converter systems. The effects of the manipulating variables are shown in a simplified form. Exemplary, increasing the power semiconductor switching frequency may not only increase the conversion losses (here the switching losses) while decreasing the volumes of the passive components but also reduce the corresponding costs of the passives.

third section. Finally, the requirement for quantitative cost considerations is derived.

#### 1.2.1 Fundamentals

The basic concept of optimization is the search for optimal solutions amongst a set of alternatives with respect to defined performance measures. Regarding the optimization of power electronic converter systems, a fundamental observation is the fact that typical primary performance measures (but also general performance measures) are coupled, i.e. inherent trade-offs complicate the concurrent improvement of multiple or all performance measures. Examples are given in **Fig. 1.4**. Consequently, single-objective optimizations should be avoided as the aggressive improvement of a particular performance measure will usually result in poor performance regarding other performance measures (e.g. [24]).

Mathematically, a constrained  $m\mbox{-}objective$  MOO problem can be stated as

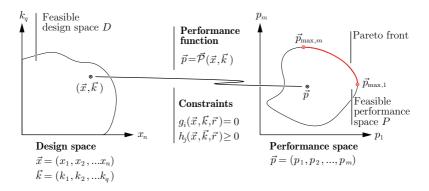

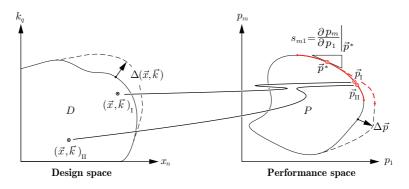

Fig. 1.5: Fundamentals of constrained MOO. The vector-valued performance function  $\vec{\mathcal{P}}$  maps the constrained set D of design vectors  $(\vec{x}, \vec{k})$  into the set Pof feasible performance vectors  $\vec{p}$  in the multi-dimensional performance space. MOO aims at identifying the Pareto front, i.e. the set of vectors  $\vec{p}$  representing the best possible compromise regarding the performance measures  $p_i$ . In contrast, single-objective optimization based on a scalar performance function would only identify a single vector to be optimal (here either  $\vec{p}_{\max,1}$  or  $\vec{p}_{\max,m}$ ).

$$\max \vec{\mathcal{P}}(\vec{x}, \vec{k}) = \max \left( \mathcal{P}_{1}(\vec{x}, \vec{k}), \mathcal{P}_{2}(\vec{x}, \vec{k}), ... \mathcal{P}_{m}(\vec{x}, \vec{k}) \right),$$

such that  $g_{i}(\vec{x}, \vec{k}, \vec{r}) = 0, \quad i = 1, ...s,$

$h_{j}(\vec{x}, \vec{k}, \vec{r}) \geq 0, \quad j = 1, ...t.$  (1.1)

Following the relevant literature (e.g. [25]),  $(\vec{x}, \vec{k})$  with  $\vec{x} = (x_1, x_2, ..., x_n)$ and  $\vec{k} = (k_1, k_2, ..., k_q)$  denotes a vector of design variables and constants in the  $n \times q$ -dimensional design space  $\mathbb{R}^n \times \mathbb{R}^q$ . The vector-valued performance function (alternatively called objective function)  $\vec{\mathcal{P}} : \mathbb{R}^n \times \mathbb{R}^q \mapsto \mathbb{R}^m$  assigns each vector  $(\vec{x}, \vec{k})$  a performance vector  $\vec{p} = (p_1, p_2, ..., p_m)$ in the *m*-dimensional performance space. The constraints  $g_i$  and  $h_j$  in conjunction with the set of parameters  $\vec{r} = (r_1, r_2, ..., r_l)$  define the set of feasible design vectors,

$$D = \{ (\vec{x}, \vec{k}) | (\vec{x}, \vec{k}) \in \mathbb{R}^n \times \mathbb{R}^q \\ \land g_i(\vec{x}, \vec{k}, \vec{r}) = 0, \quad i = 1, ...s \\ \land h_j(\vec{x}, \vec{k}, \vec{r}) \ge 0, \quad j = 1, ...t \} ,$$

(1.2)

which is referred to as the feasible design space D . Thus, the problem  $\left( 1.1\right)$  can be reformulated as

$$\max \left. \vec{\mathcal{P}}(\vec{x}, \vec{k}) \right|_{(\vec{x}, \vec{k}) \in D}.$$

(1.3)

Mapping D into the performance space using the performance function  $\vec{\mathcal{P}}$  yields the set of feasible performance vectors,

$$P = \vec{\mathcal{P}}(D) , \qquad (1.4)$$

which is referred to as the feasible performance space P or image of D. See **Fig. 1.5** for an illustration of the introduced sets and mappings.

The fundamental aim of MOO is the identification of the optimal design vectors  $(\vec{x}, \vec{k})$  in D and corresponding optimal performance vectors  $\vec{p}$  in P. For this purpose, criteria for optimality must be defined. In a non-trivial MOO problem no single vector exists which concurrently maximizes each performance measure, i.e. the performance functions  $\mathcal{P}_i$  are conflicting. Therefore, the concept of Pareto optimality is usually employed [25]. A particular design  $(\vec{x}^*, \vec{k}^*)$  is said to be Pareto-optimal if there is no other design for which all performance measures can simultaneously be improved with respect to  $(\vec{x}^*, \vec{k}^*)$ . Alternatively,  $(\vec{x}^*, \vec{k}^*)$  is Pareto-optimal if the improvement of one or more of the performance measures can only be achieved if a degradation in at least one of the remaining measures is accepted. Mathematically, this can be stated as

$$(\vec{x}^*, \vec{k}^*) \in D \quad \text{Pareto-optimal} \iff \nexists (\vec{x}, \vec{k}) \in D \quad \text{such that} p_i = \mathcal{P}_i(\vec{x}, \vec{k}) > \mathcal{P}_i(\vec{x}^*, \vec{k}^*) = p_i^* \quad \forall \quad i = 1...m \;.$$

(1.5)

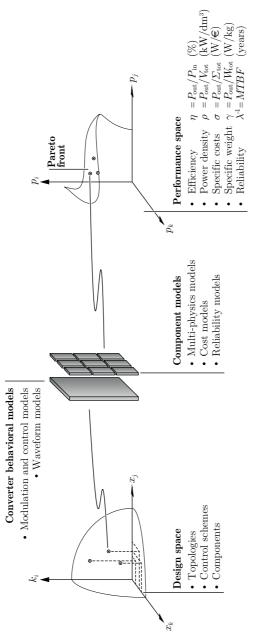

Searching for the Pareto-optimal performance vectors yields the Pareto front which consists of the vectors  $\vec{p}$  representing the best possible compromise with respect to the selected m performance measures  $p_i$ . For m = 2, the Pareto front has the shape of a boundary curve in the performance space (cf. **Fig. 1.5**). For m = 3, the Pareto front can be described by a boundary surface (cf. **Fig. 1.6**) and for m > 3 a hypersurface will result. For simplicity reasons, however, for the remainder of this thesis the term Pareto front will be used independent from the number of involved dimensions.

#### 1.2.2 Application to Converter Optimizations

The theoretical concept of optimization and in particular MOO can be applied to the field of virtual prototyping of power electronic converter systems [8,18]. With reference to the fundamentals of MOO discussed in the previous section, the most general form of MOO-based virtual prototyping is explained in detail below. An illustration of the concept can be found in **Fig. 1.6**.

#### **Design Space**

In converter optimization, the range of available building blocks, i.e. the range of different topologies, control schemes (including the switching frequency) and components account for the design variables  $x_i$ . Analogously, the design constants  $k_i$  represent the material and component characteristics such as the permeability of the core materials, switching loss energies and on-state resistances of semiconductors or fixed parameters of the control schemes. Consequently, each possible combination of building blocks and associated characteristics forming an individual converter design are allocated to a point  $(\vec{x}, \vec{k})$  in the design space.

#### Constraints

Usually, a large number of both implicit and explicit constraints apply to the selection of the design variables. On the one hand, every topology consists of a fixed number of components of specified kinds (inductors, power semiconductors, etc.) which translates into implicit constraints on the permissible design variable combinations. On the other hand, in most cases the consideration of the entire set of permissible combinations of building blocks is not desirable and is thus explicitly constrained. E.g., the combination of litz wire with laminated grainoriented electrical steel (GOES) is usually not practically meaningful in the inductor design as expensive litz wire can only be justified for highfrequency operation where GOES performs poorly. Further constraints arise e.g. from (user-defined) maximum permissible junction temperatures of the semiconductors or maximum permissible flux densities in the magnetics. Many constraints depend on the converter specifications such as the operating points (e.g. voltages, power level, ambient temperature). These converter specifications can be described with the parameters  $\vec{r}$ . Finally, the range of applicable constraints can be cap-

tured by means of formulating constraint equalities  $g_i(\vec{x}, \vec{k}, \vec{r}) = 0$  and inequalities  $h_j(\vec{x}, \vec{k}, \vec{r}) \ge 0$ . The remaining combinations of building blocks that are both of interest to the designer and meet all requirements form the feasible design space D.

#### Performance Function

In MOO-based converter design, the performance space is spanned by performance measures  $p_i$  such as the power conversion efficiency  $\eta$ , the power density  $\rho$ , the (specific) component costs  $\sigma$ , the (specific) weight  $\gamma$  and the reliability  $\lambda^{-1}$ . In order to determine the performance of each of the feasible system designs in D, mathematical models must be employed which describe the system behavior and waveforms as a function of the modulation scheme and operating point and determine the performance of each component, i.e. the losses, volume, weight, costs and failure probability. This procedure can be interpreted as the mapping of the designs in the feasible design space D into the feasible performance space P. Thus, in analogy to the fundamentals of MOO, the employed system and component models correspond to the performance function  $\vec{\mathcal{P}}$ .

#### Pareto Front

As mentioned above, MOO in virtual prototyping aims at finding the Pareto-optimal converter designs for which the best possible compromise between the selected performance measures can be attained. The identification of the Pareto front enables the study of the converter properties and the performance trade-offs solely focused on the set of optimal designs rather than considering all converter designs. Furthermore, the designs making up the Pareto front obviously represent the most attractive choices to serve as candidate systems for a hardware prototype. Further benefits of the presented MOO-based virtual prototyping approach are discussed in Section 1.3.1.

#### 1.2.3 History and State of the Art

This section presents a short overview of past and state-of-the-art contributions to virtual prototyping. Note that in this work the methodology of virtual prototyping is defined as the computation and optimization of the primary performance (i.e. the efficiency, weight or the volume) of power electronic converter systems based on computer-aided design (CAD) tools such as mathematical models and/or multi-physics simulations. The CAD tools are mainly used to design and optimize the converter components. Algorithms which draw and optimize the 3D layout of the converter may be included but are not considered as a necessary part.

#### Early References

First references to systematic virtual prototyping of power electronic converter systems can be dated back to the mid 1970s. The formulation of a power electronics design task as a mathematical optimization problem is first shown in [26] and subsequently applied to the weight optimization of a buck converter [18,27,28]. In [29], the same approach was employed to weight-optimize an isolated half-bridge DC/DC converter. In addition to [18, 27, 28], the analysis in [29] was repeated for several switching frequencies revealing the fundamental trade-off between weight and efficiency. These early pioneering publications discovered and stated the potential of a systematic mathematical treatment and optimization of the converter design procedure in contrast to approaches which are solely based on the designer's experience and subjective judgment. Not only does virtual prototyping result in designs closer to the real optimum but also does it allow to reduce the development costs and the number of hardware prototyping iterations. The major challenge at that time was found to be the high number of design variables, the strong non-linearities of the model functions and the number of constraints which are inherent to any converter optimization problem. Closed-form solutions as presented in [26] can thus only be found for simple cases and numerical means were usually employed instead. As a consequence, high emphasis was put on the investigation of suitable search strategies which minimize the - at that time - expensive computational effort. [18, 27–29] employ non-linear programming techniques. Three main limitations of the proposed virtual prototyping framework were identified in [18, 30]: i) the convergence of the search algorithm and the final solution strongly depend on the provided initial values and the scaling of the variables; ii) only continuous design variables can be processed which frequently results in unfeasible solutions (e.g. unavailable core size); iii) the lack of accurate models (e.g. models that take into account the HF effects in the magnetics) as well as the lack of comprehensive sets of model constants (e.g. operating

point-dependent switching loss energies) may yield optimization results of dubious value.

#### 1990s and 2000s

In later years, i.e. during the 1990s, the major work published in literature focused on the optimization of specific components and subsystems rather than entire topologies and systems. This reorientation was partly triggered by the emerging and increasingly powerful commercial simulation tools for fluid dynamics, thermodynamics and magnetics problems as well as for the simulation of electrical circuits. [31] describes a simulation-based optimization of heat sinks. [32] and [33] both present a CAD tool based on finite element methods (FEM) for automated design of magnetic components. Further simulation-based optimization tools are proposed in [34] and [35] for the optimization of a gate driver circuit for lowest switching losses and for the power semiconductor package design. Contrary to the aforementioned contributions, purely analytical problem descriptions were used in [36] and [37] for the minimization of the loop inductances in electrical circuits and the minimization of the instantaneous value of the active filter rating of hybrid filter systems, respectively.

In the early 2000s, virtual prototyping of entire converter systems regained attention in literature. Purely mathematical problem descriptions and optimizations rather than simulations were again employed in [38-40]. The mathematical problem formulation was supported by the growing available computational power which allowed for the analysis of more complex systems. A combined PFC and associated EMI filter design was presented in [39]. The introduction of genetic search algorithms (GA) in the optimization procedure by [41] marked a major improvement. In contrast to previously used continuous search algorithms, GAs could fully capture the discrete nature of converter design and perform optimizations taking into account databases of feasible and commercially available components. In [41], a buck converter in conjunction with an analog control circuit is optimized using GAs and mathematical formulations whereas [42,43] optimize the PFC converter of [39] regarding component costs using this new method. Optimization approaches based on a direct search method, i.e. a systematic variation of the design variables instead of heuristic search methods are proposed in [44] and [45]. There, partly simulation-supported tools are used to optimize converter systems with respect to efficiency [44] or power density [45].

#### State of the Art

Until the beginning of the 2010s, publications on virtual prototyping in power electronics such as [18, 26–45] were exclusively dealing with single-objective design and optimization problems. The major research effort was spent on the search for efficient optimization algorithms due to the limited available computational power and the high complexity of the involved problems.

Whereas the concurrent optimization of multiple objectives (or performance measures) using MOO-based approaches had already been demonstrated in other areas such as the design of liquid-cooled semiconductor modules [46], aeronautics and space applications [47,48] and analog circuit design [49], [8, 19, 50] were the first to propose MOO for virtual prototyping of power electronic converter systems. [8] discusses the fundamental limitations of single-objective optimization and proposes a virtual prototyping scheme based on systematic mathematical modeling and MOO as similarly presented in Section 1.2.2. The converter losses, volume and costs are declared to be the most important performance measures which should concurrently be considered in future research. Furthermore, the proposed approach is considered to be a valuable tool to support roadmapping initiatives. It allows to determine the best attainable design trade-offs for the available technology base and to identify the need for disruptive technologies at an early stage to overcome fundamental performance barriers. Although [50] and other publications such as [51–53] present Pareto fronts showing the trade-offs between efficiency and power density ( $\eta$ - $\rho$  Pareto front) of PFC and PV inverters, no real MOO is employed as the Pareto fronts are obtained by means of efficiency- or power density-maximizations at varying switching frequencies. A wide range of virtual prototyping examples employing true MOO can be found in recent literature. In [54–57],  $\eta$ - $\rho$ MOO is employed. The use of  $\eta$ - $\gamma$  MOO (with  $\gamma$  being the specific weight) proves to be beneficial mainly in airborne and space applications [58–61]. [62–65] perform  $\eta$ - $\sigma$  (with  $\sigma$  being the specific costs) for PV, solid state transformer (SST) and inductive power transfer (IPT) applications. Finally, [66] demonstrates an  $\eta$ - $\rho$ - $\sigma$  MOO, [67] shows an  $\eta$ - $\sigma$ - $\lambda^{-1}$  MOO with  $\lambda^{-1}$  representing the mean time between failures and [68] performs an  $\eta$ - $\rho$ - $\lambda^{-1}$  MOO.

The state of the art of MOO-based virtual prototyping of power

electronic converter systems can be summarized by the following observations:

- ▶ Performance measures: the large majority of contributions which employ MOO consider two performance measures. [66–68] represent the only exceptions found in the literature considering three objectives. The most popular performance measure was found to be the converter efficiency which is considered in all analyzed contributions [54–68]. The second performance measure is usually either the power density [54–57] or the specific weight [58–61]. Cost considerations are becoming more prominent recently. Examples are shown in [62–67] where [63,65] employ the cost models presented in this thesis.

- ► Search methods: apart from [54,60,64,66–68] using GAs or [58] using particle swarm optimization, an increasing number of state-of-the-art contributions employ direct search methods, i.e. methods which do not rely on metaheuristics but systematically enumerate all possible design variables for the search of the Pareto front.

- ▶ *Modeling detail*: although the detail and complexity of the underlaying models has generally greatly improved since the beginnings of virtual prototyping in the mid 1970s, significant differences in the modeling detail can be observed among state-of-the-art contributions. Whereas the temperature-dependence of the semiconductor losses are only neglected in [55, 59, 61, 67], the use of (often incomplete) data sheet values for the switching loss energies which may largely differ depending on the application and layout can frequently be found (e.g. [54, 58, 60, 64, 66-68]). A major modeling challenge represent the magnetic components and especially the core losses which are mostly calculated based on data sheet values neglecting important dependencies like the core temperature or DC flux biases ([54, 58-62, 64, 66-68]). Furthermore, details on the thermal models for the magnetics or the cooling system are often missing (e.g. [55, 58, 62–65, 67, 68]) or simple models without experimental verification are employed [54,60,66]. Finally, the publications that employ cost models often miss to state the numerical values of the model parameters and their origin [62, 64, 66, 67].

- Sensitivity analysis: most contributions mainly focus on the presentation of the Pareto front, i.e. the optimal solutions. On the

other hand, sensitivity analysis, i.e. the analysis of the impact of modeling errors on the Pareto front or the systematic study of the impact of parameter variations (e.g. the converter specifications or the statistics of the operating points/mission profile) are rarely performed yet. Some of the few exceptions are [50, 69, 70].

#### 1.2.4 Necessity of Cost Considerations

As seen in the previous section, the majority of literature dealing with virtual prototyping of converter systems does not implement cost models in the optimization. However, numerous practical reasons render inevitable the consideration of costs. The most compelling reason seems the fact that cost is by far the most important performance objective and thus the main driver of innovation and optimization in most applications of power electronics. Prominent industries facing a high cost pressure are PV, IT and telecom, automotive and consumer electronics [2, 5–7, 10, 63, 71–74]. Consequently, the exclusive consideration of the converter losses, the volume and weight in MOO is thus mostly insufficient. This limited approach is likely to result in impractical systems as many of the fundamental design trade-offs of **Fig. 1.4** become ineffective. The following examples demonstrate that the concurrent reduction of the losses, volume and weight is technically often feasible, however, usually only at higher costs.

Consider the fictitious design example depicted in Fig. 1.7. In Fig. 1.7(a), a state-of-the-art 2-level 6-switch AC/DC inverter based on Si IGBT technology for low-voltage drive applications [75] is shown. Fig. 1.7(b) shows the same system employing advanced SiC MOS-FETs. The significantly lower switching losses of SiC allow to concurrently reduce the converter losses and the volume of the passives and the cooling system by means of a moderate increase of the switching frequency (cf. Fig. 1.7(c)). A MOO with respect to the losses and volumes only would hence suggest using SiC for obvious reasons. However, in reality such a system has low chances to be built due to the higher overall system costs in this example (3-4 times higher costs of SiC). Whether a more pronounced increase of the switching frequency could compensate the higher semiconductor costs can only be assessed with quantitative component cost models. Further examples demonstrating the need of cost considerations in MOO are given below.

▶ The losses, volume and weight of DC or 50 Hz magnetic compo-

Fig. 1.7: Fictitious example illustrating the necessity of cost considerations in MOO. (a) State-of-the-art Si IGBT AC/DC inverter system for low-voltage drive applications [75]. (b) Same system based on advanced SiC MOSFETs. (c) The low switching losses of SiC allow to concurrently reduce the converter losses and volume by means of a higher switching frequency. Despite obvious advantages regarding losses and volume in this example, the shift from Si to SiC would have only low chances in reality due to the higher overall system costs (3-4 times higher costs of SiC). Such effects can only be evaluated with quantitative cost models of the components.

nents can often concurrently be reduced using high-performance nanocrystalline core materials. Analogously, the volume and losses of HF inductors can be reduced employing litz wires with a lower strand diameter. However, both options are expensive and thus likely to increase the component costs.

- Multi-layer PCBs facilitate more compact auxiliaries and short power traces resulting in lower conduction losses. Multi-layer PCBs are, however, considerably more expensive than two-sided PCBs.

- Other optimization strategies rather than virtual prototyping, e.g. integration and modularization (cf. Fig. 1.3), usually aim at

improving the general converter performance measures such as lowering the development and manufacturing costs. Here, virtual prototyping using cost models is imperative to assess the possibly adverse impact on the converter component costs (e.g. the use of power modules instead of discretes may lower the development and manufacturing costs but typically increases the component costs).

Finally, it is obvious that the consideration of the reliability – apart from the efficiency, volume and the costs – would further boost the significance and usefulness of the results of MOO-based virtual prototyping. A prerequisite of such analysis is the availability of comprehensive and resilient reliability data for the considered components. Obtaining such data, however, is deemed impractical for academia as i) such data often does not exist, ii) conducting large-scale reliability tests is beyond the means of most research groups and iii) the access to such data compiled by manufacturers is largely restricted to buying customers. Furthermore, relying on the reliability prediction models published in the Military Handbook 217F Notice 2 (MIL-HDBK-217F) [76] as frequently proposed (e.g. [67]) is not recommended. On the one hand, important components such as MOSFETs are not described and the generalized models based on reliability data of components from the 1980s might not apply to modern and more specialized components. On the other hand, the application-specific stresses on the components (which have a crucial impact on the reliability) cannot directly be considered.

## **1.3** Scientific Contributions

This thesis proposes a novel advanced  $\eta$ - $\rho$ - $\sigma$  virtual prototyping routine for power electronic converter systems which is considerably more comprehensive, detailed and accurate than previous contributions in this field. The usefulness of the virtual prototyping routine is furthermore demonstrated by means of two case studies employing the routine. A more detailed discussion of the main contributions of this thesis are given below.

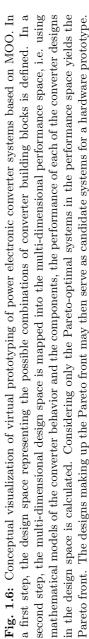

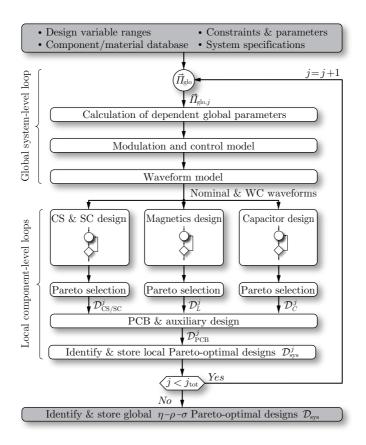

▶ This thesis proposes an advanced virtual prototyping routine for MOO of power electronic converter systems regarding the efficiency, volume and the costs. An intelligent direct search method in conjunction with an efficient software implementation is employed to identify the  $\eta$ - $\rho$ - $\sigma$  Pareto surface.

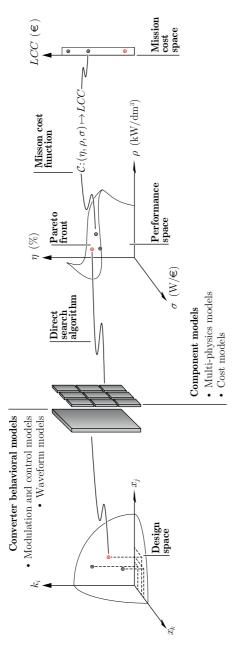

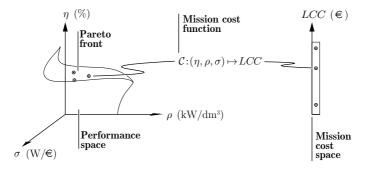

- ▶ The original MOO approach of **Fig. 1.6** is extended by an additional optimization step as illustrated in Fig. 1.8. The resulting Pareto front usually comprises a large number of system designs which all represent a compromise between the chosen performance measures. In order to facilitate a systematic selection of a single candidate system, it is proposed to assign each system of the Pareto front a single (i.e. 1D) key figure as a function of its performance,  $\mathcal{C}: (\eta, \rho, \sigma) \mapsto \mathbb{R}$ . The corresponding mission cost function  $\mathcal{C}$  may represent the (arbitrary) preferences of the design engineer. The candidate design is then found in a systematic and straightforward manner by selecting the system which achieves the best key figure value as shown in Fig. 1.8. The advantage of this multi-objective two-step optimization approach with an *a posteriori* selection of the candidate system in contrast to a conventional single-objective approach (which directly results in a single candidate system) is twofold: on the one hand, the Pareto-front is obtained which provides valuable insight of the design trade-offs. On the other hand, the design engineer's preferences of how to select the candidate system, i.e. the mission cost function  $\mathcal{C}$  can easily be modified without re-executing the time-consuming optimization step. In this thesis, a mission cost function estimating the life cycle costs (LCC) depending on the efficiency, volume and costs is proposed.

- ▶ Detailed and comprehensive system models and multi-physics component models are employed. Accurate experimentally verified model parameters are systematically derived and incorporated into the models. Model simplifications based on the abstraction of components (e.g. cooling system design based on a cooling system performance index [50, 53] or volumes of passives as a function of the stored energy [75]) was avoided in the component modeling.

- ▶ The modeling framework is complimented with novel cost models for power semiconductors, cooling systems, magnetic components, capacitors, PCBs and a selection of auxiliary circuits such as gate drivers.

- ▶ The proposed virtual prototyping routine is utilized to optimize a bidirectional galvanically isolated 5 kW universal power con-

MOO regarding the efficiency, power density and the specific component costs. A direct search algorithm based on modeling framework comprises detailed and experimentally verified multi-physics and cost models. In contrast to existing MOO routines, the proposed routine is extended by an additional optimization step in which an arbitrary mission cost function  $\mathcal{C}: (\eta, \rho, \sigma) \to \mathbb{R}$  is used to map the Pareto surface into a 1D mission cost space. This step acilitates the identification of the optimal system based on a single user-defined key figure. In this work, the optimal system on the Pareto surface is determined using life cycle cost evaluations based on the converter efficiency, volume Fig. 1.8: Proposed approach for advanced virtual prototyping of power electronic converter systems based on computationally-efficient design routines is employed to identify the  $\eta$ - $\sigma$ - $\sigma$  Pareto front. The system and component and costs.

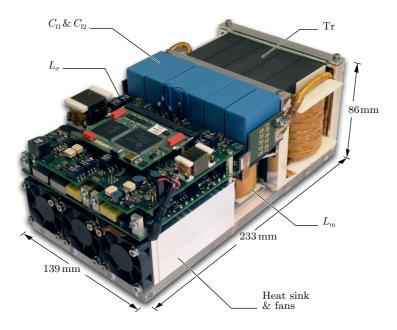

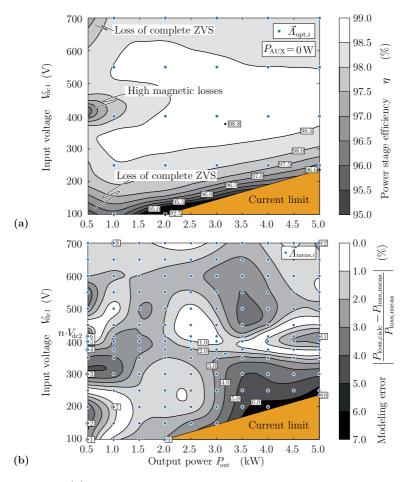

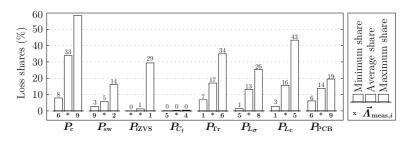

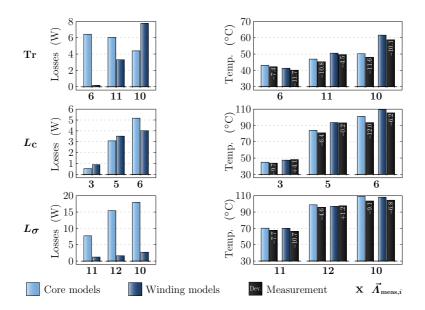

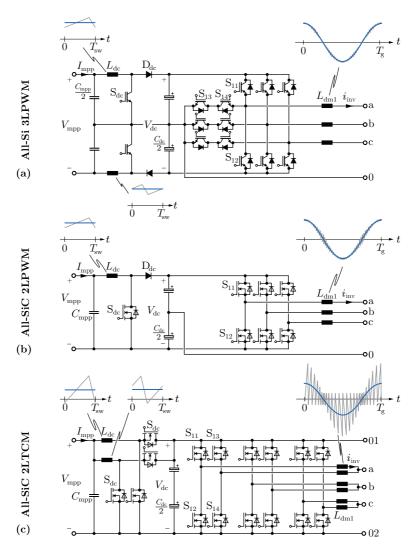

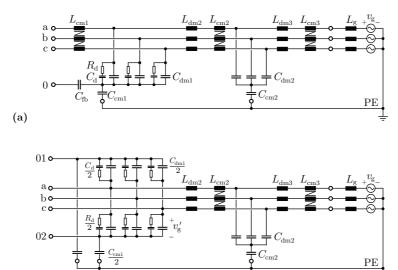

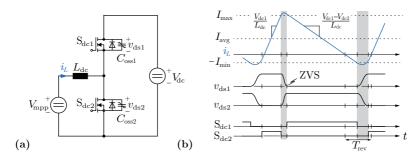

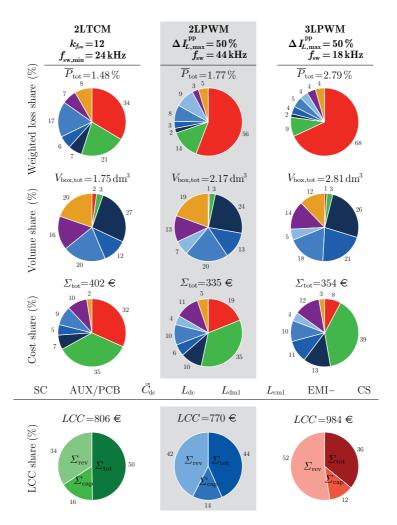

Fig. 1.9: Considered case studies for which the proposed advanced MOObased virtual prototyping routine is employed. (a) Bidirectional galvanically isolated 5 kW universal power conditioner with ultra-wide input voltage range for residential DC-microgrid applications. A conventional 3L dual active bridge (DAB) converter system is compared to a 5L DAB which features a higher control degree of freedom. The analysis includes the investigation of the employment of either SiC MOSFETs or Si IGBTs. (b) 10 kW PV inverter system consisting of a DC/DC boost converter input stage, DC/AC inverter stage and EMI filter output stage. A state-of-the-art hard-switched PWMmodulated all-Si 3L T-type converter system is compared to a hard-switched PWM-modulated all-SiC 2-level 6-switch system and a to a soft-switched TCM-modulated all-SiC 2-level double-interleaved system.

ditioner with ultra-wide input voltage range for residential DCmicrogrid applications (cf. **Fig. 1.9(a)**). The purpose of this case study is to check whether the use of SiC allows the implementation of a highly functional converter system while still achieving a high efficiency and low volume at competitive costs. Two different topologies are optimized and comprehensively compared. A hardware prototype is built to verify the employed MOO routine.

▶ The proposed virtual prototyping routine is further utilized to investigate the potential of SiC in PV applications. For this purpose, a state-of-the-art Si IGBT-based system and two SiC MOSFET-based concepts are optimized regarding the efficiency, volume and component costs and compared with respect to the achievable minimum LCC.

Different parts of the presented research in this thesis have already been published in international scientific journals, conference proceedings, tutorials and workshops. The respective list of publications can be found at the end of this chapter.

### 1.3.1 Opportunities

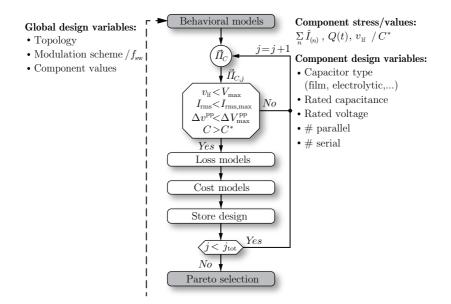

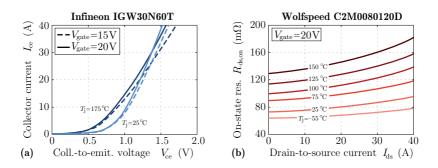

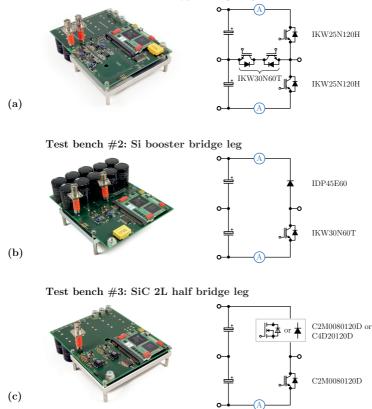

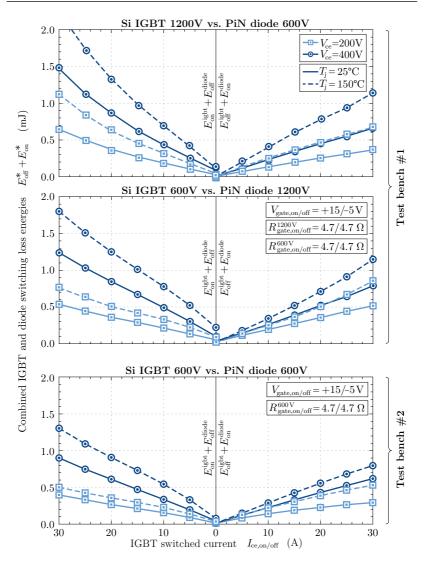

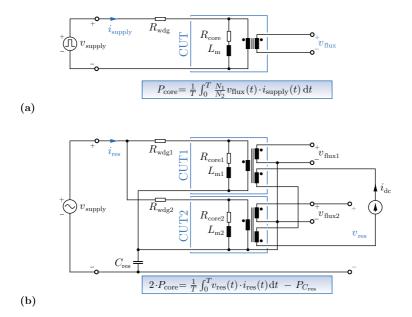

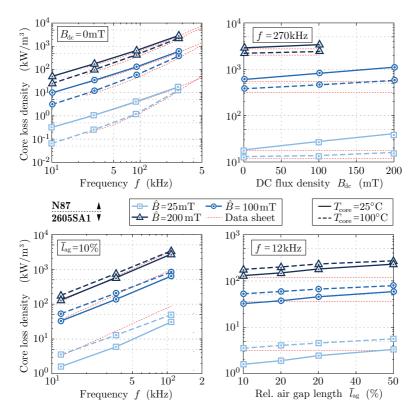

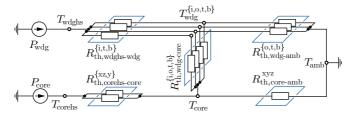

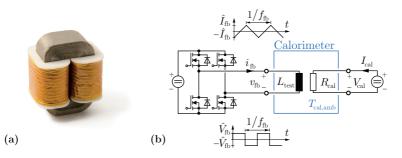

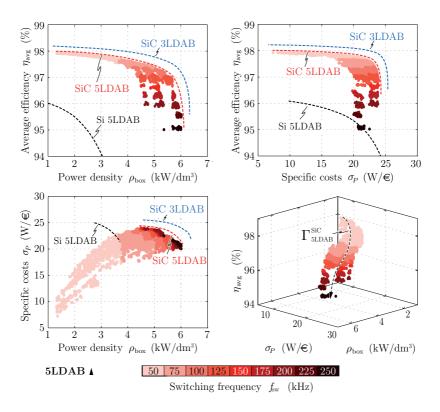

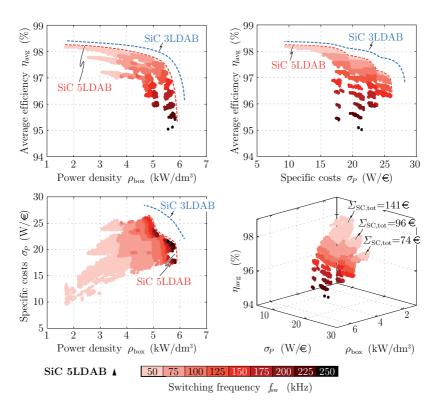

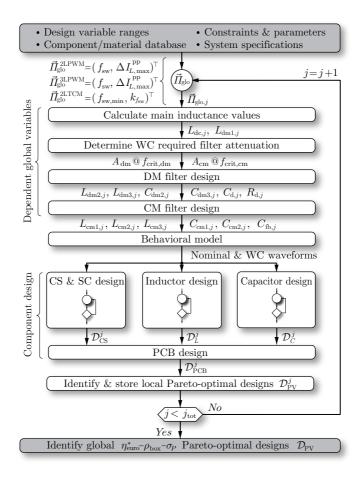

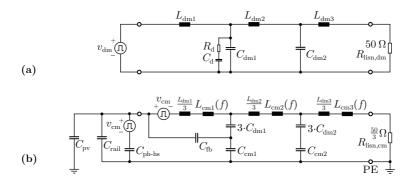

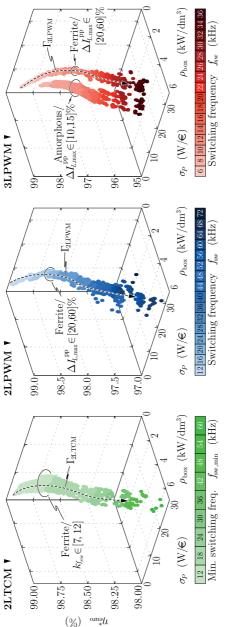

The opportunities offered by the MOO-based virtual prototyping routine proposed in this thesis are discussed below.