### Modular High Bandwidth Switch-Mode Three-Phase AC Voltage Source

A thesis submitted to attain the degree of

### DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

presented by DAVID OLIVIER BOILLAT

MSc ETH born on 14.08.1985 citizen of Le Bémont, Switzerland

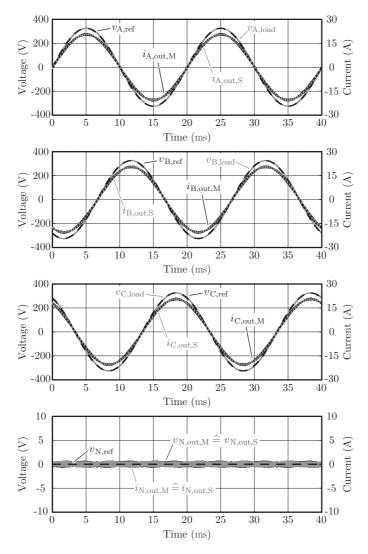

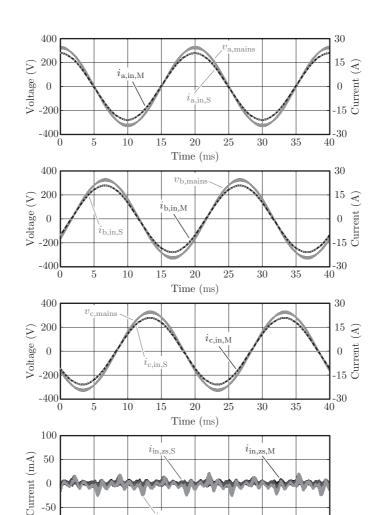

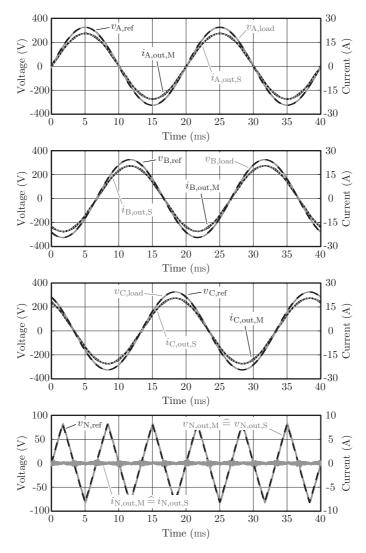

accepted on the recommendation of

Prof. Dr. Johann W. Kolar, examiner Prof. Dr. Paolo Mattavelli, co-examiner

2016

ETH Zurich Power Electronic Systems Laboratory Physikstrasse 3 | ETL 116 8092 Zurich | Switzerland

http://www.pes.ee.ethz.ch

© 2016 by David Olivier Boillat

Pour ma famille tant aimée

## Acknowledgment

In the first place, I am very thankful to Professor Johann W. Kolar, Head of the Power Electronic Systems (PES) Laboratory of ETH Zurich, for his great support and expertise as well as for his always critical remarks and improving suggestions throughout my Ph.D., which helped me to broaden my scientific knowledge and skills. He offered a challenging working environment to me and gave me the opportunity to participate in various international conferences, to write patents and journal papers, and to collaborate with industry.

I also wish to express my appreciation to Professor Paolo Mattavelli, full Prof. at the University of Padova, Vicenza, Italy and adjunct Prof. at CPES of Virginia Tech, Blacksburg, VA, USA, for his interest in my work, for acting as an expert, and for taking part in the Ph.D. defense as a co-examiner.

Very special thanks are due to Thomas Friedli, Jonas Mühlenthaler, and Florian Krismer for their academic collaboration and supporting supervision concerning different parts of my thesis. A warm word of thanks also to my office mates Michael Leibl, Christoph Gammeter, and Lukas Schrittwieser and my former office co-workers Thomas Friedli, Mario Schweizer, Matthias Kasper, Roman Bosshard, and Sebastian Schroth for the very interesting, stimulating, and helpful discussions, their friendship, and the very great time we spent together.

Because of the strong support of the PES' administrative staff members, I could stay fully focused on my research activities. My thanks go to Monica Kohn-Müller, Roswitha Coccia, Prisca Maurantonio, Beat Seiler, Damaris Egger, and Yvonne Schnyder for their assistance in conjunction with the coordination of my industry project, the organization of conference trips, the web page updates, the accounting, the infilling of patents, etc. Peter Albrecht's knowledge about electronic components, devices and tools was always of big help. Special thanks go to Peter Seitz for his assistance with the construction and soldering of various hardware prototypes and his practical advices. Last but not least, I thank Claudia Stucki for the proper maintenance of the IT infrastructure and for her always quick and effective help with computer issues.

I had the chance to assist the lectures "Railway Systems I&II" over many years. During this activity I could participate in diverse industry-oriented excursions and had a lot of interesting discussions. Many thanks therefore to Dr. Christian Gerster, Bombardier Transportation AG, and Dr. Markus Meyer, emkamatik GmbH.

The unforgettable time at PES was enriched by a lot of social activities, such as the Mondav morning coffee, the coffee breaks, and the Friday evening gathering, the diverse trips before and after the conferences, the events on the weekends, the various sports activities (including soccer, fitness, skiing, hiking, and trekking), and so forth. Many many thanks for the great time to my friends and colleges Toke Andersen, Thomas Baumgartner, Pedro Bezerra, Roman Bosshard, Ralph Burkart, Dominik Bortis, Daniel Christen, Patricio Cortes, Bernardo Cougo, Michael Flankl, Romeu Friedemann, Thomas Friedli, Christoph Gammeter, Thomas Guillod, Jonas Huber, Felix Jauch, Matthias Kasper, Oliver Knecht, Ivana Kovacevic, Michael Leibl, Andreas Looser, Yanick Lopsiger, Christoph Marxgut, Mario Mauerer, Jonas Mühlenthaler, Andreas Müsing, Thomas Nussbaumer, Gabriel Ortiz, Daniel Rothmund, Lukas Schrittwieser, Sebastian Schroth, Mario Schweizer, Thiago Soeiro, Claudia Stucki, Andrija Stupar, Arda Tüysüz, Hirofumi Uemura, Florian Vancu, and Benjamin Wrzecionko.

Finally, but upmost importantly, I would like to express my deep and heartiest gratitude to my lovely family and to my girlfriend's family: Claude, Susanne, Carol, and Res as well as Sylvia, Susi, Kurt, René, and Lisa. Your unlimited love, support, and family feeling of security throughout my Ph.D. work are inestimable!

Bern, January 2016 David Olivier Boillat

# Contents

| Kurzfassung |       |        |                                                   |     |

|-------------|-------|--------|---------------------------------------------------|-----|

| A           | bstra | act    |                                                   | xv  |

| 1           | Inti  | roduct | ion                                               | 1   |

| <b>2</b>    | Eva   | luatio | n of Key Technology                               | 7   |

|             | 2.1   | Topol  | ogy Evaluation                                    | 7   |

|             | 2.2   |        | ing Inductor Approach                             | 15  |

|             |       | 2.2.1  | CI: Definitions and Equivalent Circuits           | 17  |

|             |       | 2.2.2  | Transverse and Longitudinal Current Separation    |     |

|             |       |        | and Corresponding Magnetic Flux Densities         | 22  |

|             |       | 2.2.3  | Symmetric Core Magnetization:                     |     |

|             |       |        | Stationary Considerations                         | 29  |

|             |       | 2.2.4  | Symmetric Core Magnetization:                     |     |

|             |       |        | Dynamic Considerations                            | 32  |

|             |       | 2.2.5  | Experimental Verification                         | 33  |

|             |       | 2.2.6  | Summary                                           | 45  |

| 3           | Cor   | werter | Module Structure and Design                       | 49  |

|             | 3.1   | Decou  | pling of the Output Phases                        | 49  |

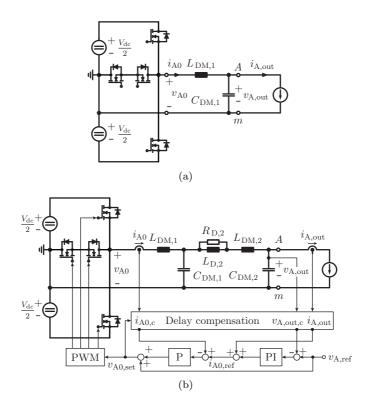

|             | 3.2   | Outpu  | ıt Stage – Single-Phase Filter Design             | 53  |

|             |       | 3.2.1  | Specifications of the AC Source                   | 57  |

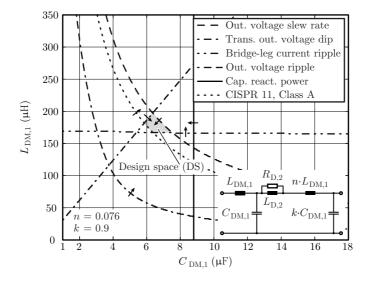

|             |       | 3.2.2  | Design Space Constraints                          | 59  |

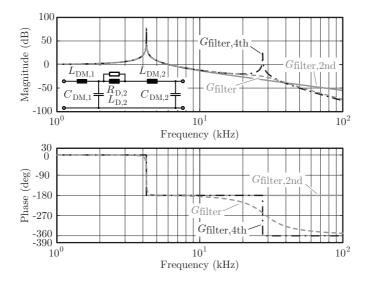

|             |       | 3.2.3  | Two-Stage Filter Design                           | 71  |

|             |       | 3.2.4  | Experimental Results                              | 80  |

|             |       | 3.2.5  | Design Space with Component Tolerances            | 92  |

|             |       | 3.2.6  | Summary                                           | 96  |

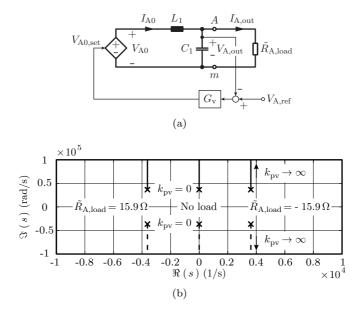

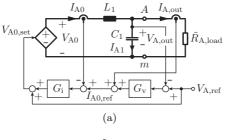

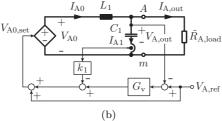

|             | 3.3   | -      | ıt Stage – Single-Phase Control                   | 99  |

|             |       | 3.3.1  | Derivation of the Investigated Control Structures | 102 |

|             |       | 3.3.2  | Small-Signal Modeling                             | 113 |

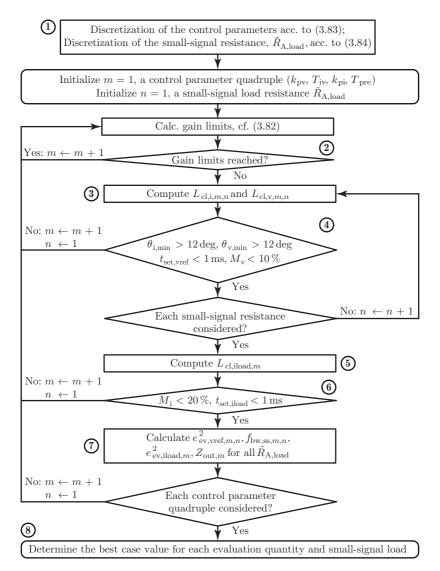

|             |       | 3.3.3  | Optimized Controller Design                       | 123 |

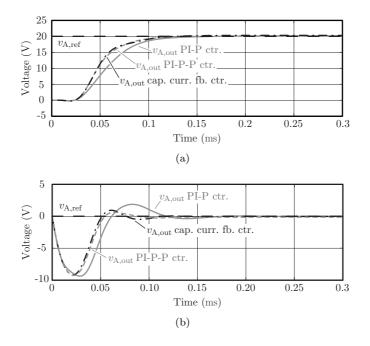

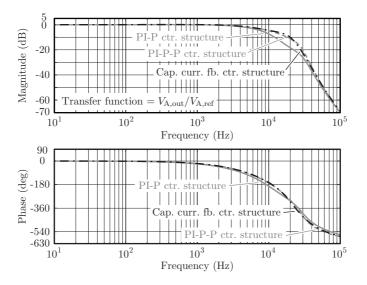

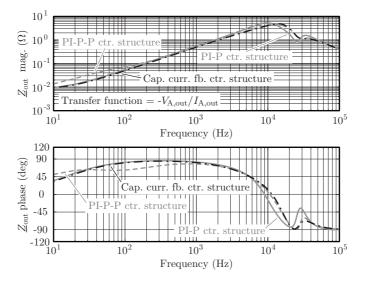

|             |       | 3.3.4  | Experimental Verification                         | 136 |

|             |       | 3.3.5  | Summary                                           | 147 |

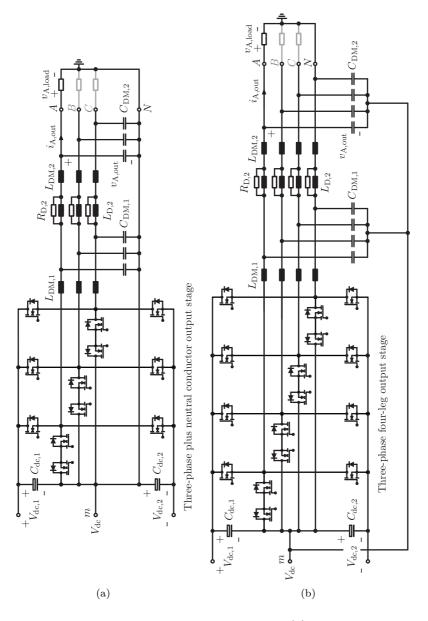

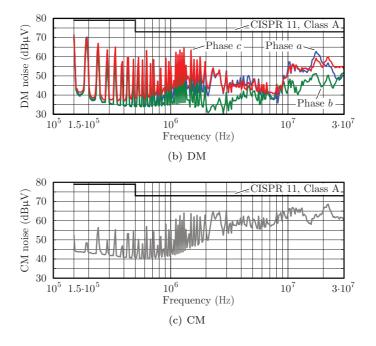

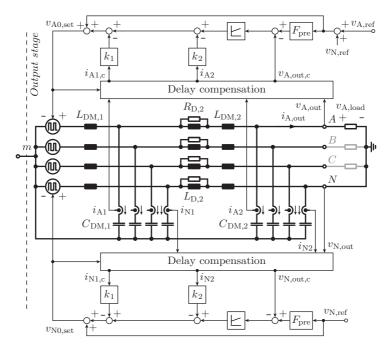

|             | 3.4   |        | -Phase Four-Leg Output Stage                      | 150 |

|             |       | 3.4.1  | Summary                                           | 156 |

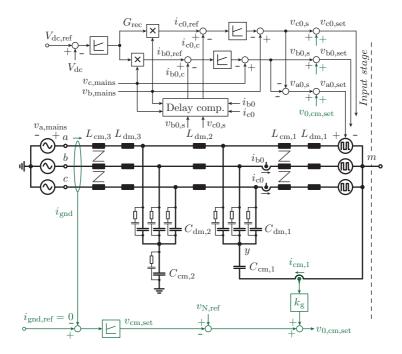

|             | 3.5   | Input  | Stage                                             | 157 |

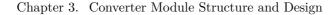

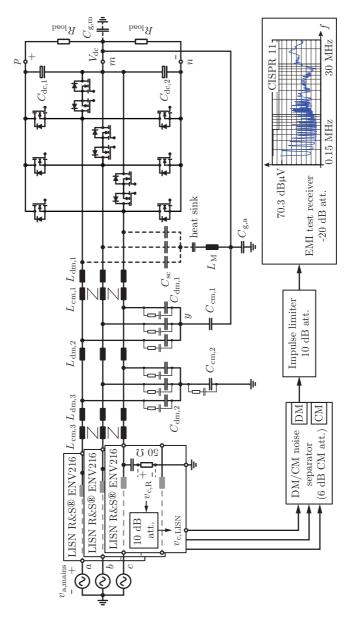

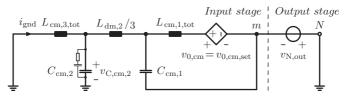

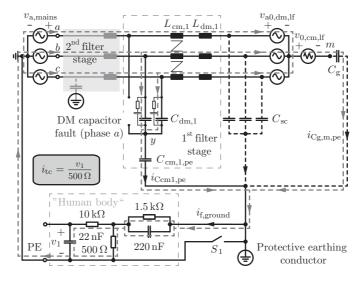

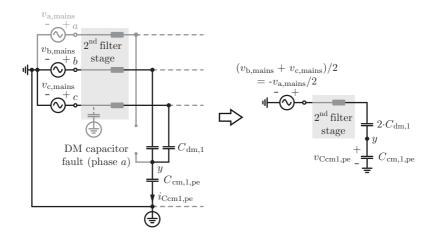

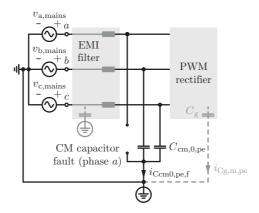

|          |     | 3.5.1  | Structure of the First Stage of the EMI Input<br>Filter              | 165        |

|----------|-----|--------|----------------------------------------------------------------------|------------|

|          |     | 3.5.2  | Electrical Side Conditions for the Minimization of the Filter Volume | 174        |

|          |     | 3.5.3  | Volume Minimization Approach                                         | 174        |

|          |     | 3.5.4  | CM and DM Inductor Modeling                                          | 180        |

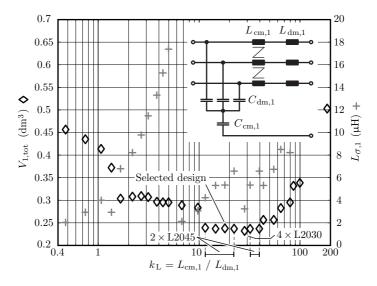

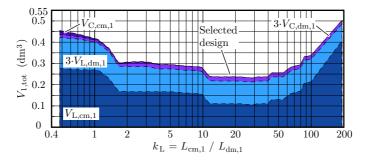

|          |     | 3.5.5  | Optimization Results                                                 | 187        |

|          |     | 3.5.6  | Design of the Second Filter Stage                                    | 192        |

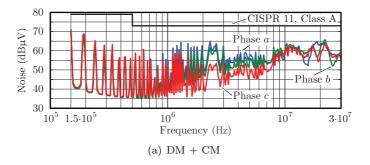

|          |     | 3.5.7  | Experimental Results                                                 | 200        |

|          |     | 3.5.8  | Summary                                                              | 217        |

| 4        | Con |        | Module Operation                                                     | <b>221</b> |

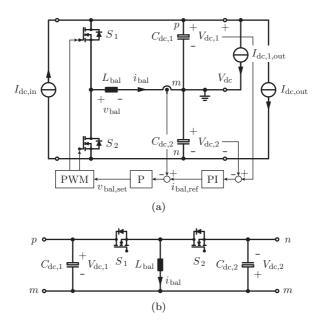

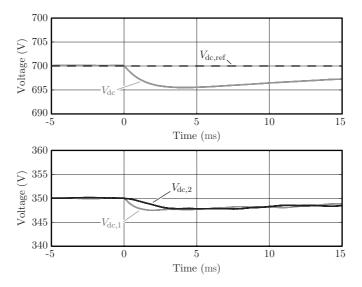

|          | 4.1 |        | ink Voltage Balancing                                                | 226        |

|          |     | 4.1.1  | Balancer Circuit                                                     | 226        |

|          |     | 4.1.2  | DC Link Voltage Balancing by the Fourth Output                       |            |

|          |     |        | Leg                                                                  | 229        |

|          |     | 4.1.3  | Summary                                                              | 234        |

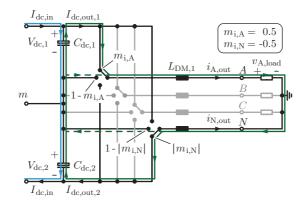

|          | 4.2 |        | d Current Control                                                    | 235        |

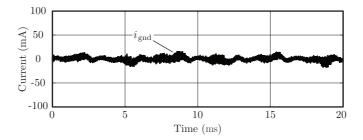

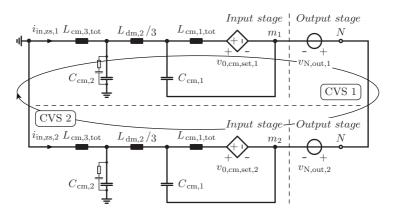

|          |     | 4.2.1  | Ground Current Control Scheme                                        | 236        |

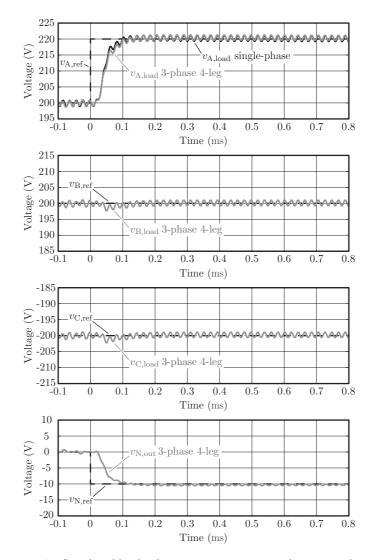

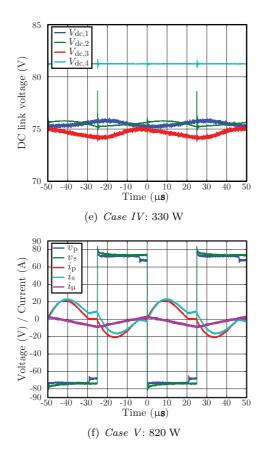

|          |     | 4.2.2  | Simulation Results                                                   | 239        |

|          |     | 4.2.3  | Summary                                                              | 240        |

|          | 4.3 | 0      | ated Isolation and Voltage Balancing Link $\ldots$ .                 | 242        |

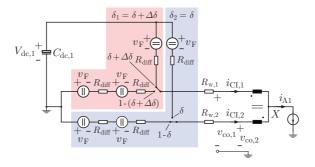

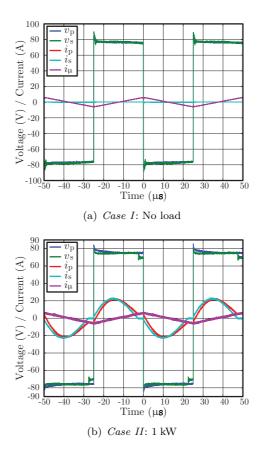

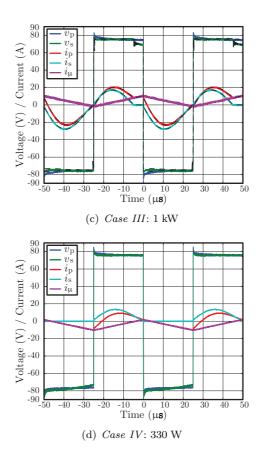

|          |     | 4.3.1  | HCDCM Operation Principle of the SRC with                            |            |

|          |     |        | Half-Bridges and Unequal Loading                                     | 244        |

|          |     | 4.3.2  | Design Guidelines for the SRC with Unequal Load-                     |            |

|          |     |        | ing                                                                  | 252        |

|          |     | 4.3.3  | Experimental Verification                                            | 256        |

|          |     | 4.3.4  | Summary                                                              | 262        |

|          | 4.4 | CVS N  | Module Operation                                                     | 263        |

| <b>5</b> |     |        | peration of Two Converter Modules                                    | 267        |

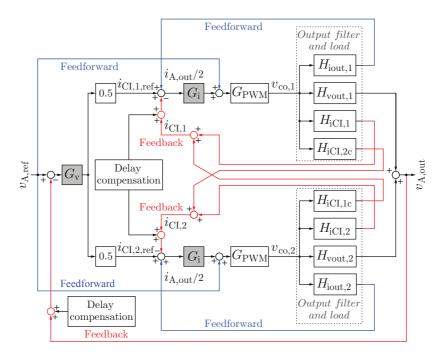

|          | 5.1 |        | r-Slave Control Concept                                              | 273        |

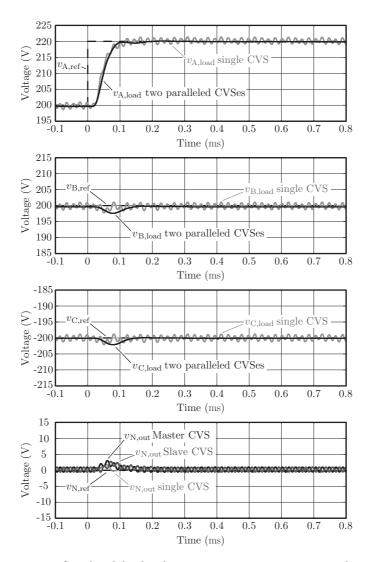

|          | 5.2 |        | ation Results                                                        | 279        |

|          | 5.3 | Summ   | nary                                                                 | 287        |

| 6        | Cor | clusio | n & Outlook                                                          | 289        |

|          | 6.1 |        | usion                                                                |            |

|          | 6.2 | Outloo | ok                                                                   | 304        |

| AĮ  | opendices                                                                                                                     | 307      |

|-----|-------------------------------------------------------------------------------------------------------------------------------|----------|

| A   | Coupling Inductor Literature Overview                                                                                         | 309      |

| в   | Stability Analysis for a Single-Stage LC FilterB.1 Two-Loop Control StructureB.2 Capacitor Current Feedback Control Structure |          |

| С   | Delay Compensation for the Capacitor Current Feed<br>back and the PI-P-P Control Structures                                   | -<br>325 |

| D   | Maximum Touch Current                                                                                                         | 329      |

| Lis | st of Publications                                                                                                            | 337      |

| Bi  | bliography                                                                                                                    | 341      |

| Cı  | ırriculum Vitae                                                                                                               | 393      |

# Kurzfassung

Die Entwicklung von vielseitig einsetzbaren, geregelten AC Spannungsquellen (ACS) mit einer hohen Bandbreite wurde in den letzten Jahren von der Industrie vorangetrieben, um kostengünstiger und effizienter leistungselektronische Geräte auszulegen und zu testen. Der mögliche Anwendungsbereich einer derartigen ACS ist überaus breit und es wird daher ein Gerät verlangt, das eine hohe Flexibilität in der Anbindung möglicher Lasten oder Generatoren bietet und das hohe Anforderungen an die Qualität sowie die dynamischen Eigenschaften der Ausgangsspannung erfüllt. Die Auslegung der ACS unterscheidet sich gerade durch die erhöhte Flexibilität und die einschränkenden Vorgaben von der Anwendung diverser Methoden, die in unterschiedlichen wissenschaftlichen Veröffentlichungen vorgeschlagen werden. Obgleich bis heute schon verschiedene ACS als Produkte auf dem Markt erhältlich sind, wurde die Auslegung wie auch die Optimierung der Regelung eines solchen leistungselektronischen Konvertersytems nur teilweise oder gar nicht in der Literatur behandelt.

In dieser Arbeit wird eine dreiphasige, geschaltete ACS mit einer Leistung von 100 kW untersucht, die einen Vierquadrantenbetrieb ermöglicht und gleichzeitig eine hohe Effizienz, ein kleines Bauvolumen, eine sehr hohe Bandbreite der Ausgangsspannung als auch einen sehr kleinen Ausgangsspannungsrippel erzielt. Um eine Leistung von 100 kW zu erreichen, werden zehn Module mit je einer Leistung von 100 kW parallel zueinander geschaltet. Jedes Modul weist eine AC–DC–AC Konverterstruktur auf, die aus einer dreiphasigen AC–DC Gleichrichter-Eingangsstufe, einem DC Spannungszwischenkreis mit geteilten Kondensatoren und einer vierphasigen Wechselrichter-Ausgangsstufe besteht.

In einem ersten Schritt werden zielübergreifende Konzepte zur Auslegung, Optimierung und Regelung der Eingangs- sowie Ausgangsstufe einer 10 kW-Einheit entworfen und auf das betrachtete System angewandt. Besonders im Mittelpunkt stehen dabei die Begründung, dass jede Ausgangsphase individuell betrieben wird, die daraus folgende Auslegung des zweistufigen, für jede Phase getrennt vorgesehenen Ausgangsfilters und der Ausgangsspannungsregelstruktur wie auch die Auslegung des dreiphasigen EMV Eingangsfilters. Allen Auslegungsroutinen liegt dabei eine Mehrkriterien-Optimierung zugrunde. Messungen, welche auf einem dreiphasigen, dreistufigen T-Typ Konverter-Prototypen mit SiC MOSFETs der neusten Generation durchgeführt wurden, unterstützen vollumfänglich die detaillierten theoretischen Untersuchungen. In einem zweiten Schritt werden die Eingangs- und die Ausgangsstufe elektrisch miteinander verbunden. Diesbezüglich werden umfassende Lösungen erarbeitet, die eine gleiche Spannungsaufteilung über den beiden Zwischenkreiskondensatoren erzwingen und die einen Erdstrom, im Falle der Erdung von Netz- und Laststernpunkt, verhindern. Ein Master-Slave Regelungskonzept, das den Betrieb mehrerer parallel-geschalteter ACS Modulen erlaubt, wird zum Schluss hergeleitet. Das Konzept wird anhand von zwei parallelen Einheiten und mit Hilfe exakter Schaltungssimulation untersucht.

Die wesentlichen neuen wissenschaftlichen Beiträge dieser Doktorarbeit sind:

- ▶ Individueller Betrieb jeder Phase der vierphasigen Ausgangsstufe mit einem zweistufigen Ausgangsfilter, das durch minimale Interaktion der Phasen gekennzeichnet ist (vgl. Abschnitt 3.1);

- ▶ Erarbeitung eines Mehrkriterien-Auslegungsalgorithmus für das individuell für jede Ausgangsphase vorgesehene zweistufige *LC* Ausgangsfilter, der auf das Design Space Konzept zurückgreift, mit Hilfe dessen mehrere Kriterien gleichzeitig berücksichtigt werden können (vgl. Abschnitt 3.2);

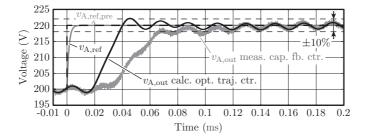

- ▶ Entwicklung einer Mehrkriterien-Optimierungsroutine für die Auslegung der Regelstruktur der Ausgangsspannung, mit der eine Ausgangsspannungs-Kleinsignalbandbreit von 7.1 kHz–15.5 kHz in Abhängigkeit der Last erreicht wird (vgl. Abschnitt 3.3);

- ▶ Bestimmung des optimalen Verhältnisses zwischen CM und DM Induktivität der Haupt DM / CM *LC* Stufe des EMV Eingangsfilters um das geringste Filtervolumen dieser Stufe zu erhalten (vgl. Abschnitt 3.5);

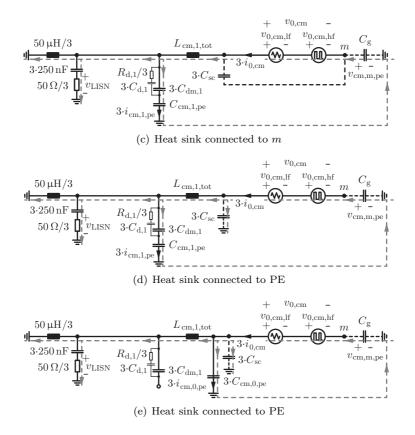

- ▶ Detaillierte Analyse ob der Kühlkörper an Erde oder den DC Mittelpunkt angebunden werde sollte, um die CM Störaussendung zufolge parasitärer Koppelkapazitäten der Leistungshalbleiter zu verringern (vgl. Abschnitt 3.5.1);

- Beweis, dass eine gleiche Spannungsaufteilung über den geteilten Zwischenkreiskondensatoren mit der vierten Phase nicht für alle

betrachteten Lastfälle und Betriebsbedingungen, unter Berücksichtigung der ACS's Spezifikationen, erreicht werden kann (vgl. Abschnitt 4.1.2);

- ▶ Regelungstechnische Unterdrückung eines Erdstromes für einen Netzsternpunkt und eine Last, welche beide mit Erde verbunden sind (vgl. Abschnitt 4.2);

- ▶ Einbindung der galvanischen Trennung und der Fähigkeit, eine gleiche Spannungsaufteilung über den geteilten Zwischenkreiskondensatoren zu erreichen, in einen einzelnen DC–DC Konverter (vgl. Abschnitt 4.3); und

- ▶ Entwicklung eines Master-Slave Konzeptes für die Regelung parallel geschalteter Module mit individuellen einphasigen Ausgangsspannungsregelstrukturen, die nicht auf den Brückenzweigausgangsstrom oder den Ausgangsstrom zurückgreifen (vgl. Abschnitt 5.1).

### Abstract

In recent years, the development of general purpose, high bandwidth controllable AC voltage sources (CVSes) is pushed by industry to accelerate the design and / or testing processes of power electronics equipment in order to save costs and efforts. As the term "general purpose" suggests, the potential application area of such a CVS is vast and hence demands for a device which is highly flexible regarding the connection of possible loads or generators and features stringent specifications related to quality and dynamic properties of the output voltage. It is precisely the great flexibility and the increased requirements which make the design of the CVS to be different from standard approaches found in diverse scientific publications. To this day, even though CVS products are already available in the market, the design of such a converter system as well as the optimization of its control have not or only partially been covered in literature.

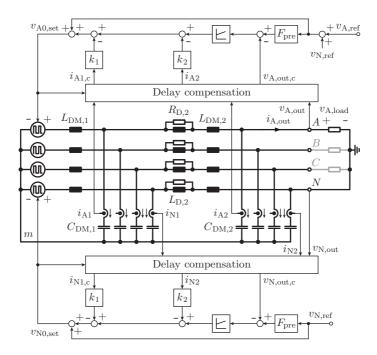

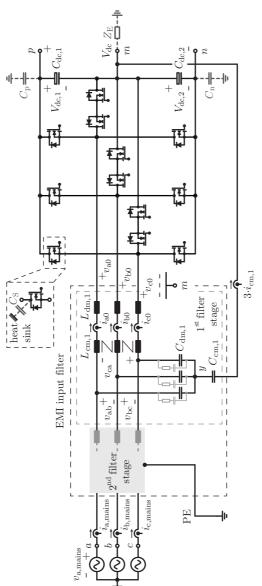

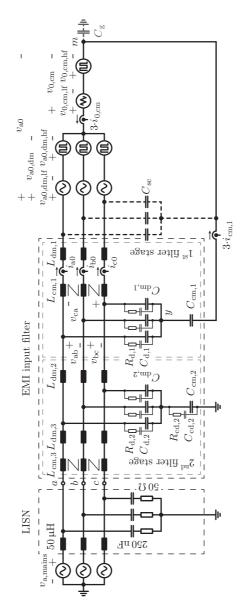

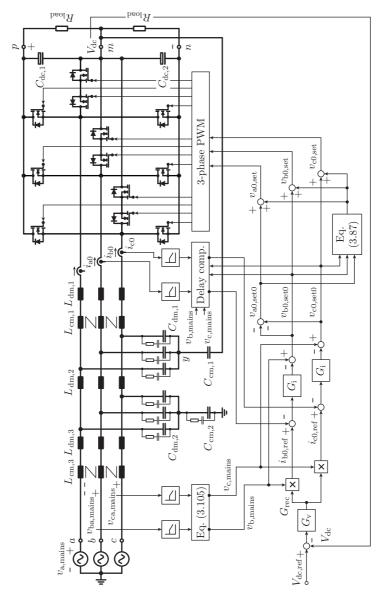

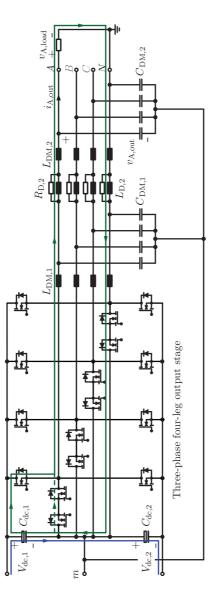

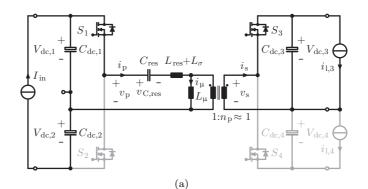

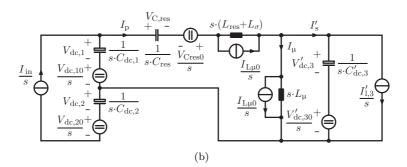

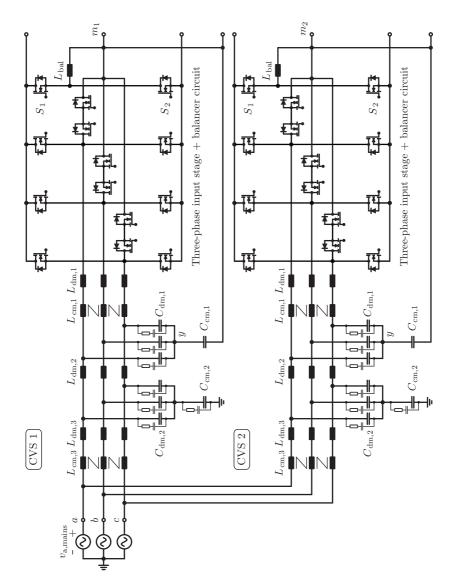

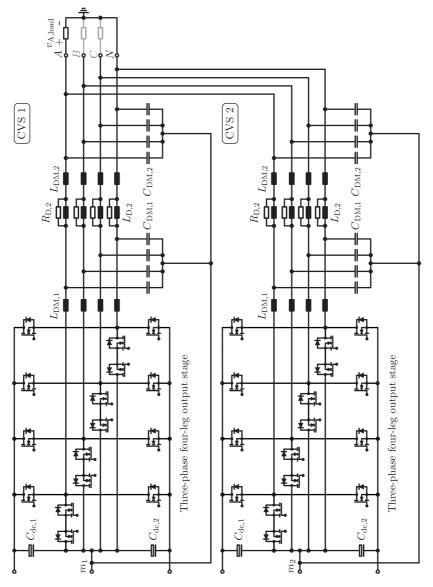

In this Ph.D. thesis, a 100 kW four-quadrant, three-phase, switchmode CVS is researched and designed to achieve a high efficiency, a low construction volume, a very high output voltage control bandwidth, and a very low output voltage ripple. The CVS is realized by connecting ten 10 kW modules in parallel, each of the modules being implemented as an AC-DC-AC converter, consisting of a three-phase AC-DC rectifier input stage, a split DC link with an intermediate voltage circuit, and a three-phase four-leg DC-AC inverter output stage.

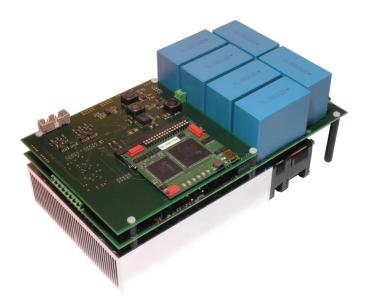

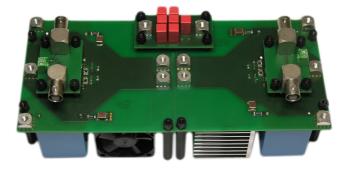

First, key multi-objective concepts to design, optimize, and control the output and input stages of one 10 kW unit are developed and applied to the system at hand. This especially comprises the motivation to operate each output phase individually, and subsequently the design of the output filter provided individually for each phase and of the output voltage control structure, and in a next step the three-phase EMI input filter design. All design routines are thereby based on multi-objective optimizations. The detailed analyses are fully supported by experimental results carried out on a three-phase three-level T-type converter prototype employing the newest generation of SiC MOSFETs. Second, the input and output stages are electrically interconnected and comprehensive solutions to balance the voltages of the split DC link and to eliminate a ground current for simultaneously grounded mains starpoint and load are elaborated. Finally, a Master-Slave control concept is derived to operate multiple parallel connected CVS modules. The concept is investigated by accurate circuit simulations on the basis of two paralleled units.

The major new scientific contributions of this Ph.D. thesis are:

- ▶ individual operation of each leg for the three-phase four-leg output stage with a four-line filter with minimum interaction between the lines (cf. Section 3.1);

- laboration of a multi-objective design algorithm for a per-phase, multi-stage LC output filter based on the design space concept, which simultaneously considers multiple criteria (cf. Section 3.2);

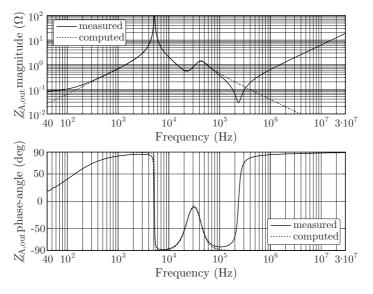

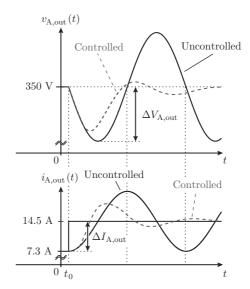

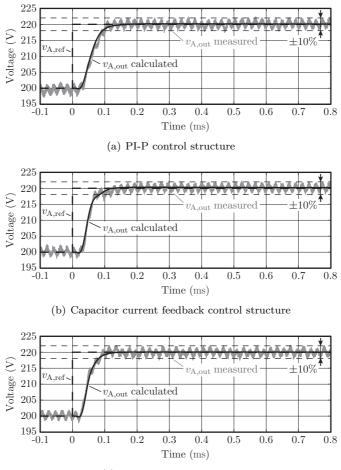

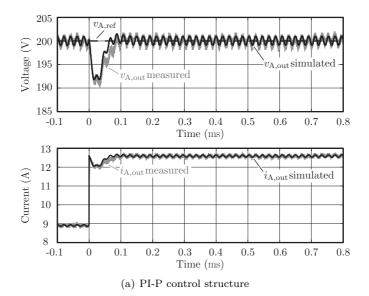

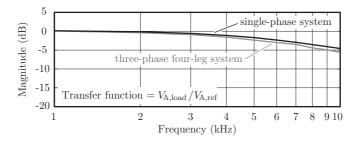

- ▶ development of a multi-objective optimization routine to lay out the output voltage control structure, helping to achieve an output voltage small-signal control bandwidth of 7.1 kHz–15.5 kHz, depending on the type of load (cf. Section 3.3);

- ▶ determination of the optimal ratio between CM and DM inductances of the main DM / CM *LC* stage of the EMI input filter to obtain the smallest volume of this filter stage (cf. Section 3.5);

- ▶ detailed discussion weather the heat sink should be connected to ground or to the DC midpoint in order to achieve a higher CM attenuation of the EMI input filter (cf. Section 3.5.1);

- demonstration that the balancing of the split DC link voltages by the fourth output leg is not possible for all considered load types and operating conditions, with regard to the given CVS' specifications (cf. Section 4.1.2);

- elimination of a ground current for a mains star-point and load connected to earth by means of control (cf. Section 4.2);

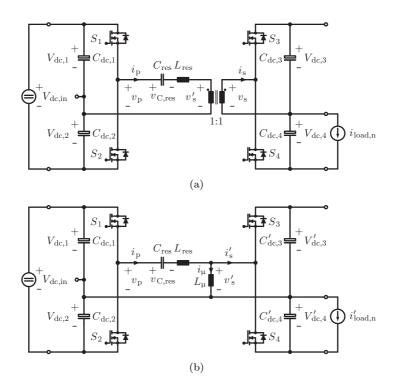

- ▶ integration of the DC link voltage balancing capability and galvanic isolation into a single DC–DC converter (cf. Section 4.3); and

- ▶ development of a Master-Slave concept for the control of parallel connected modules with individual single-phase output voltage control structures that do not involve the bridge-leg output current or the load current (cf. Section 5.1).

# Introduction

$G^{\rm ENERAL\ purpose\ high\ bandwidth\ Controllable\ AC\ Voltage\ Sources}_{\rm (CVSes),\ which\ have\ the\ capability\ to\ emulate\ certain\ electrical\ characteristics,\ are\ in\ recent\ years\ emerging\ in\ the\ area\ of\ Power-Hardware-In-the-Loop\ (PHIL)\ simulations$

- ▶ to emulate mains connected loads / generators to analyze power grid dynamics and control strategies [1, 2];

- ▶ to simulate grid faults to test power electronic equipment [3-5];

- ▶ to emulate motor / generator characteristics to verify the correct operation of novel drive systems [6,7]; and

- ▶ to develop and conduct type tests on power electronic converters [8–11], e.g. harmonic tests according to IEC 61000-3-11 and flicker tests according to IEC 61000-3-2 [12].

Such CVSes accelerate the development and / or testing processes for the mentioned application areas and hence allow saving costs and efforts [6,13–21]. This leads to an increased interest in high bandwidth CVSes and to a higher demand of such systems in the market.

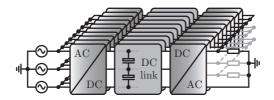

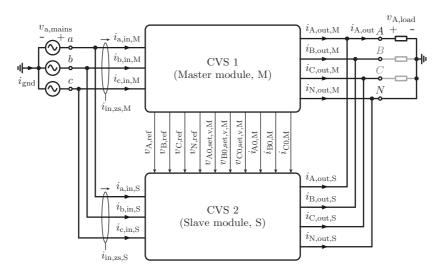

In this thesis, a four-quadrant three-phase CVS rated at 100 kW needs to be designed, which is realized by ten parallel connected 10 kW three-phase CVS modules as shown in **Fig. 1.1**. Compared to a single 100 kW converter unit, this has the advantages of

redundancy and thus higher reliability for part load operation [22–29];

Figure 1.1: Realization of a general purpose 100 kW four-quadrant, threephase, high bandwidth controllable AC voltage source (CVS) by ten 10 kW CVS modules. Each unit consists of an AC–DC rectifier input stage, an intermediate DC voltage link, and a DC–AC inverter output stage. As motivated in Section 2.1, three-level T-type bridge-legs are employed for the input and output stages and hence a split DC link results.

- reconfigurability leading to a higher flexibility in the usage of the modules [28, 29];

- higher efficiency in part load operation [23, 24, 26, 29];

- reduced ripple of the output voltages for synchronization and phase-shifting of the Pulse Width Modulator (PWM) carriers of the diverse modules [26]; and

- ▶ tighter control and / or faster dynamics of the output voltages [24, 26].

Due to the vast potential application areas of the CVS and because it is typically avoided to have a specific device for each task, the CVS should handle a large number of different applications and hence it needs to be highly flexible regarding the connection of possible loads or generators. Documented loads for the CVS include linear, e.g. DC, single-phase AC, and three-phase AC (balanced and unbalanced) resistive and / or inductive loads [3, 8, 11, 30, 31], and non-linear loads. Possible non-linear loads are constant power loads, e.g. DC for investigating a DC microgrid [32] and AC for emulating a low voltage supply system [33]), diode rectifiers (single-phase [6, 30] and three-phase [3]), and single-phase triac loads [8]. Due to the high flexibility of the CVS the outputs of multiple CVSes can be connected together by means of a common DC or AC bus, with some of the CVSes acting as energy sources and other as energy sinks. This, for example, enables the emulation of an island network [1,2,34]. Table 1.1: Electrical specifications of a 10 kW three-phase module of the 100 kW four-quadrant controllable AC voltage source (CVS). The quantities for the output and input stages are indicated for one phase, i.e. phase A for the output stage and phase a for the input stage.

<sup>1)</sup> line-to-neutral; <sup>2)</sup> line-to-line

| $Entire \ CVS$                                      |                      |  |  |  |  |

|-----------------------------------------------------|----------------------|--|--|--|--|

| Nominal power, $P_{\rm n}$                          | 10 kW                |  |  |  |  |

| Nominal efficiency, $\eta_{tot,n}$                  | $\geq 95\%$          |  |  |  |  |

| Output stage                                        |                      |  |  |  |  |

| Nominal rms output voltage, $V_{A,out,n}^{(1)}$     | 230  V               |  |  |  |  |

| Nominal peak output voltage, $V_{A,out,n,pk}^{(1)}$ | $325 \mathrm{V}$     |  |  |  |  |

| Max. peak output voltage, $V_{A,out,max,pk}^{(1)}$  | $350 \mathrm{V}$     |  |  |  |  |

| Nominal rms output current, $I_{A,out,n}$           | $14.5 \; {\rm A}$    |  |  |  |  |

| Nominal peak output current, $I_{A,out,n,pk}$       | $20.5 \mathrm{A}$    |  |  |  |  |

| Full power output frequency, $f_{out}$              | 0 - min. 1 kHz       |  |  |  |  |

| Output voltage small-signal bandwidth               | $\geq 4 \text{ kHz}$ |  |  |  |  |

|                                                     | CISPR 11,            |  |  |  |  |

| Conducted EMI                                       | Class A $[36]$       |  |  |  |  |

| Input stage                                         |                      |  |  |  |  |

| Rms mains voltage, $V_{\text{mains}}^{2)}$          | $400 V_{11}$         |  |  |  |  |

| KIIIS IIIallis voltage, V <sub>mains</sub>          | (+10%, -14% [37])    |  |  |  |  |

| Nominal rms input current, $I_{a,in,n}$             | 14.5 A               |  |  |  |  |

| Nominal peak input current, $I_{a,in,n,pk}$         | 20.5  A              |  |  |  |  |

| Mains frequency, $f_{\text{mains}}$                 | 50  Hz               |  |  |  |  |

|                                                     | CISPR 11,            |  |  |  |  |

| Conducted EMI                                       | Class A $[36]$       |  |  |  |  |

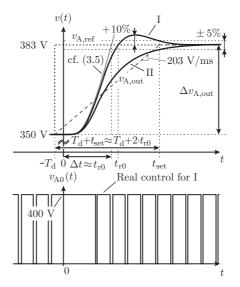

The required high flexibility of the CVS's scope of applications leads to stringent specifications of one CVS module as summarized in **Tab. 1.1**, where the mains connected and load connected parts are referred to as input stage and output stage, respectively. Furthermore, the system needs to comply with requirements regarding quality and transient responses of the output voltage given in **Tab. 1.2**, which are motivated in Section 3.2. Additionally, a small-volume realization of the CVS is aimed for because in many applications, especially for on-site testing of power electronic circuits, e.g. avionics and telecommunication

**Table 1.2:** Required output properties of one CVS module, motivated in Section 3.2. The quantities are indicated for one phase, i.e. phase A.<sup>1)</sup> THD: Total Harmonic Distortion

| Output voltage quality                | $  \text{THD}_{v}^{(1)} < 2.5\% \text{ (cf. IEEE 1547 [53])}$                                                  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Output voltage slew rate              | $SR \ge 209 \text{ V/ms}$                                                                                      |

| Max. transient output                 |                                                                                                                |

| voltage dip $\Delta v_{A,out}$ due    | $ \Delta v_{\rm A,out}  < 30 \text{ V} - 6 \text{ O}$                                                          |

| to a stepwise output                  | $\left  rac{\Delta v_{ m A,out}}{\Delta i_{ m A,out}}  ight  \leq rac{30 \ { m V}}{5 \ { m A}} = 6 \ \Omega$ |

| current change $\Delta i_{\rm A,out}$ |                                                                                                                |

systems, space is rather limited [35]. Even though each CVS module allows a bidirectional power flow, this work almost exclusively focuses on the case where the converter system supplies a load.

Nowadays, CVSes are already commercially available, are covering power ratings from 1 kW up to 30 MW, and are employing linear [35, 38–40], switch-mode [41–47], or hybrid, i.e. a combination of linear and switch-mode [48–51], power amplifiers. The realization of the CVSes with linear power amplifiers leads to heavy, bulky, and very expensive systems which typically have a low efficiency of only 50%–70% [35, 52] and hence cannot fulfill the efficiency requirement, i.e.  $\eta_{tot,n} \geq 95\%$  given in Tab. 1.1. To increase the efficiency drastically and to decrease the weight and the volume of the CVS, switch-mode amplifiers are employed. It is noted that it remains unclear to which extend hybrid concepts could be competitive alternatives to the switchmode amplifiers. However, combinations of switch-mode and linear amplifiers definitely add a significant amount of complexity to the CVS and are for this reason not further investigated in this thesis.

On the one hand, the switch-mode CVS can be realized as a forced commutated AC–AC converter without explicit intermediate energy storage, i.e. as a matrix converter [54]. On the other hand, an intermediate energy storage element can be employed leading to an AC– DC–AC converter structure typically consisting of three parts: an AC– DC rectifier input stage, a DC link, and a DC–AC inverter output stage. The bottleneck of the matrix converters is that they do not have any voltage boosting capabilities, i.e. their maximum output voltage is limited to  $\sqrt{3}/2 = 86.6\%$  of the maximum input voltage (for sinusoidal modulation) [55]. This leads, in the best case, to a maximum line-to-neutral output voltage of  $110\% \times \sqrt{2} \cdot V_{\text{mains}}/\sqrt{3} \cdot \sqrt{3}/2 = 110\% \times V_{\text{mains}}/\sqrt{2} = 311 \text{ V}$ , considering an increase of the mains voltage by 10% (cf. Tab. 1.1), which, however, is still smaller than the maximum required output voltage  $V_{\text{A,out,max,pk}} = 350 \text{ V}$ . Accordingly, an AC–DC–AC converter structure, as given in Fig. 1.1, is selected for the implementation of the CVS.

To store the energy in the DC link, an intermediate voltage or current circuit can be utilized, resulting in a Voltage Source Converter (VSC) or a Current Source Converter (CSC) topology.<sup>1</sup> Typically, for the targeted power of 10 kW per module, the VSC is the preferred solution to realize the converter system for reasons of lower costs and higher efficiency compared to the CSC [56–59].

The derived structure of one CVS module is depicted in Fig. 1.1, where each unit consists of an AC–DC rectifier input stage, an intermediate DC voltage link, and a DC–AC inverter output stage. To handle three-phase unbalanced loads and, because of further considerations explained in Section 3.1, a three-phase four-leg output stage is employed.

As it will be explained throughout this thesis, the miscellaneous application areas of the CVS mentioned at the beginning of the Introduction (see page 2) imposes advanced requirements for all three parts of the AC source and their operational interactions, but especially on the output stage as can immediately be seen from Tabs. 1.1 and 1.2. Even though CVS products are already available in the market, the design of the system as well as the optimization of its control and the consideration of a higher number of units operating in parallel have not or only partially been covered in literature. Thus, the focus of this dissertation is on the scientific investigation and design of a low-volume and efficient CVS, which achieves a very high output voltage control bandwidth and a very low output voltage ripple. This thesis is structured as follows.

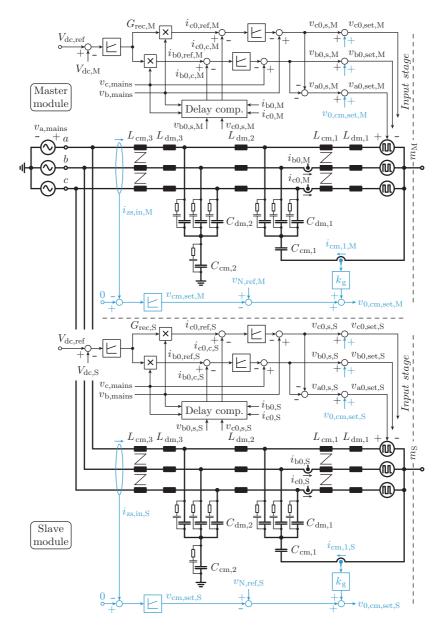

In Chapter 2, it is first explained that a bidirectional active front end is required that regulates the DC link voltage to 700 V–800 V, followed by the motivation for the employment of a three-level T-type bridge-leg topology, which leads to a split DC link, and a switching frequency of 48 kHz for the input and output stages of one CVS module. To increase the current rating of the unit and thus to enhance the output frequency  $f_{\rm out}$  at which full power can be delivered and / or to enlarge the over-current-carrying capacities for a limited time, bridge-

$<sup>^{1}</sup>$ Converters with a voltage-current DC link, such as the Z-source or T-source topology [55] are disregarded in this thesis.

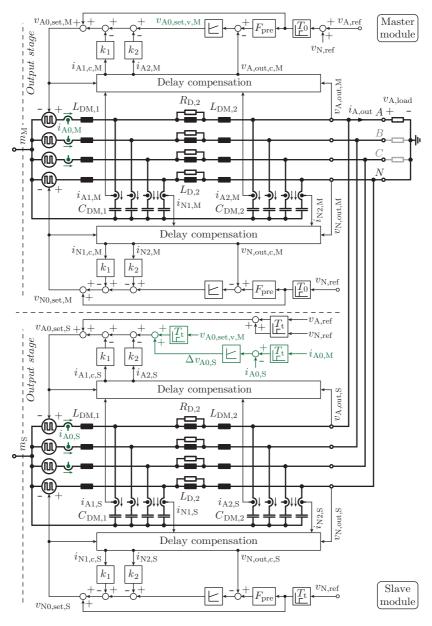

legs can be paralleled by employing a Coupling Inductor (CI). This is analyzed in detail in the second part of the chapter. Suitable converter topologies of the CVS's output and input stage are identified in Chapter 3 and a strong motivation for an individual operation of the output phases is given. The design of the two stages, especially of the per-phase output and the three-phase Electro-Magnetic Interference (EMI) input filters and of the per-phase output voltage control structure, are then thoroughly elaborated based on multi-objective optimizations. Furthermore, extensive measurement results are provided to verify the theoretical considerations. Chapter 4 electrically links the input and output stages of one module and analyzes solutions to achieve in average balanced split DC link voltages for all different load scenarios mentioned on page 2 and operating conditions of each phase within the specifications given in Tab. 1.1. Moreover, the problem of a ground current  $i_{\text{gnd}}$  for earthed mains star-point and load is discussed and two options to prohibit this current are presented: suppressing  $i_{gnd}$ by means of control or by inserting a galvanic isolation in the DC link. The explanation of the module operation for grounded and floating loads concludes the chapter. Finally, a Master-Slave control concept to parallel 10 kW CVS modules is elaborated and motivated in Chapter 5, where simulation results for two systems in parallel support the theoretical analysis. Chapter 6 draws the conclusion and gives an outlook on further investigations.

# 2

### Evaluation of Key Technology

The considered 100 kW CVS is a switch-mode system and is realized by paralleling ten 10 kW modules, as motivated in the Introduction. In this chapter the topology of one such module is justified in Section 2.1, which comprises the selection of the input stage converter topology, the assignment of the DC link voltage, the determination of the bridge-leg topology, and the definition of the switching frequency for the input and output stages.

To enhance the current-carrying capacity of the CVS module, which also elevates the large-signal bandwidth of the output voltage, i.e. the output frequency up to which full power can be delivered, bridge-legs can be paralleled. An interesting option is to magnetically couple the output of the bridge-legs by a Coupling Inductor (CI), which is constituted and analyzed in detail in Section 2.2 for two bridge-legs operated in parallel, focusing on the output stage.

### 2.1 Topology Evaluation

A three-phase line-commutated passive diode rectifier would be the simplest realization of the input stage. Among other disadvantages, such an interface does however not permit a bidirectional power flow and accordingly is not an option. Unidirectional switch-mode mains interfaces [60, 61], such as the Vienna rectifier [62], the Swiss rectifier [63], or simple three-phase buck / boost rectifiers [64], suffer from the same latter mentioned drawback.

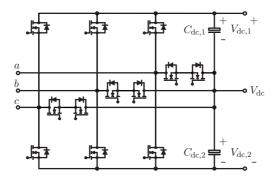

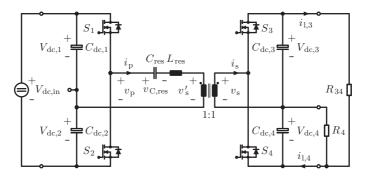

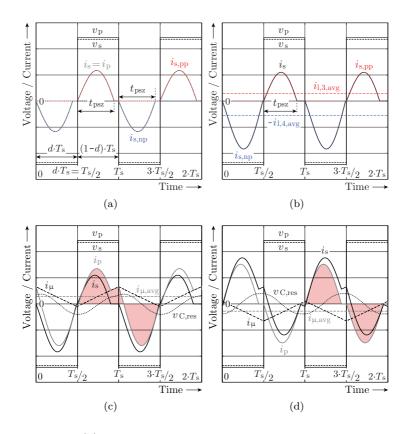

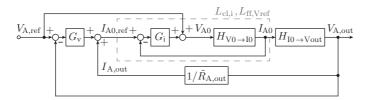

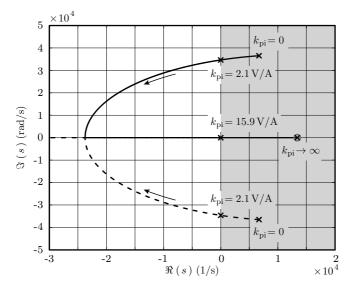

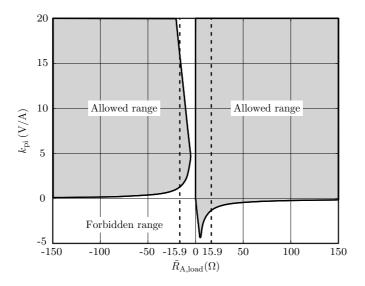

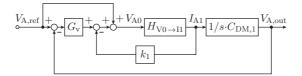

To allow for a bidirectional power flow, the three-phase PWM rectifier shown in **Fig. 2.1**, which has power factor correction and DC link

Figure 2.1: Bidirectional three-phase PWM rectifier building the input stage of the CVS. In anticipation of the results presented hereafter, a three-level T-type bridge-leg topology with SiC MOSFETs is depicted.

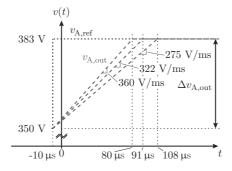

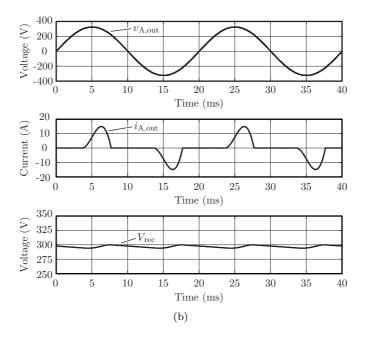

voltage,  $V_{dc}$ , control capabilities, must be employed. The maximum DC link voltage is set to  $V_{dc,max} = 800$  V, to facilitate the generation of an output stage phase voltage (e.g.  $v_{A,out}$  for phase A, cf. **Fig. 2.2**), with high dynamics in the range of  $[\pm 350 \text{ V}]^1$  for the different kind of loads specified on page 2.<sup>2</sup> In this case, the minimum absolute difference between  $V_{dc,max}$  and  $v_{A,out}$  is 50 V, which is regarded to be enough to achieve the targeted dynamic requirements given in Tab. 1.2 (cf. Section 3.2). For the nominal conditions given in Tab. 1.1, the DC link voltage is reduced to  $V_{dc,n} = 700$  V to enhance the efficiency of the CVS.

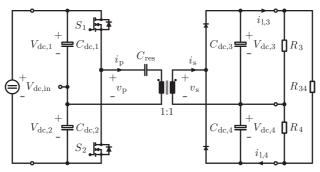

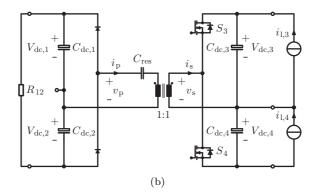

In a first attempt, the bidirectional output stage is realized with the same three-phase PWM converter as employed for the input stage (cf. Fig. 2.2). A refinement of the output stage inverter topology is carried out in Section 3.1. Because the reasoning for the bridge-leg topology selection is identical for the input and output stages, it is hence only explained for the output stage in the following.

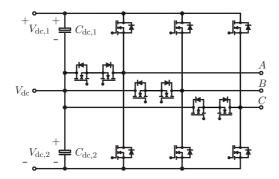

The bridge-legs of the three-phase converter given in Fig. 2.2 can in the simplest form be realized with a two-level topology, as shown in **Fig. 2.3(a)**, with power semiconductors rated at a blocking voltage of 1200 V for the determined DC link voltage of 700 V–800 V. Because it

<sup>&</sup>lt;sup>1</sup>The maximum output phase voltage is  $V_{\rm A,out,max,pk} = 350$  V (cf. Tab. 1.1).

$<sup>^{2}</sup>$ It is noted that for three-phase output voltage systems, overmodulation is not always possible (cf. Section 4.2).

**Figure 2.2:** Bidirectional three-phase PWM inverter building the output stage of the CVS. In anticipation of the results presented hereafter, a three-level T-type bridge-leg topology with SiC MOSFETs is depicted.

is preferred to select a switching frequency  $f_s$  which is not located in the audible range, i.e.  $f_{s,out} \geq 20$  kHz, a three-level bridge-leg topology [cf. Figs. 2.3(b), 2.3(c), 2.3(d), and 2.3(e)] leads to a significantly higher efficiency of the converter than a two-level structure [65–67]. Moreover, such a three-level topology requires for the same switching frequency less filtering to achieve the quality of the output voltage specified in Tabs. 1.1 and 1.2 [65,66]. Accordingly, the volume of the output filter can be reduced, increasing the power density of the CVS, because passive components typically take the major part of the entire converter system's volume. In addition, lower component values are also a direct consequence of the reduced filtering requirement and hence it is expected that the compliance to the dynamic requirements summarized in Tab. 1.2 can be achieved with less effort for a three-level than for a two-level topology.

The required filtering can even be further reduced by increasing the number of voltage levels at the bridge-leg output. However, such topologies drastically increase the circuit and modulation complexity of the converter and are for this reasons not regarded any further. A thorough classification, review, and comparison of multi-level converters can be found in [68–71], including modular multi-level converters with cascaded half-bridges and hybrid topologies [e.g. a combination of NPC / flying capacitor topologies with cascaded H-bridges (cf. Fig. 2.3)].

Figure 2.3: Bridge-leg topologies considered for the realization of the input and output stage converters: (a) two-level, (b) three-level T-type, (c) threelevel neutral point clamped (NPC), (d) three-level flying capacitor (FC), and (e) H-bridge topologies. Only one phase, i.e. phase A, is depicted and, in anticipation of the results elaborated in the following, SiC MOSFETs are employed. Because it is required that the bridge-leg output voltage,  $v_{A0}$ , takes positive as well as negative values, a split DC link is considered and / or a DC link voltage midpoint m is defined also for the two-level and the threelevel FC topology.

Possible basic bridge-leg topologies which generate three voltage levels at their output are [66, 68, 69]:

▶ the three-level transistor clamped, i.e. T-type, topology with

600 V / 650 V and 1200 V power semiconductors [cf. Fig. 2.3(b)];

- ▶ the three-level diode clamped, i.e. Neutral Point Clamped (NPC), topology with 600 V / 650 V power semiconductors [cf. Fig. 2.3(c)];

- ▶ the three-level capacitor clamped, i.e. Flying Capacitor (FC), topology with 600 V / 650 V power semiconductors [cf. Fig. 2.3(d)]; and

- ▶ the H-bridge converter with 600 V / 650 V power semiconductors [cf. Fig. 2.3(e)].

These hard-switching topologies are considered to be the most competitive ones for the realization of the output stage. Nevertheless, it is remarked that there exists other, however more complex, three-level topologies such as the split-inductor converter [72], the active NPC topology [73], or soft-switched bridge-leg topologies [74–76].

Considering Fig. 2.3, it is observed that the T-type topology embodies a two-level structure. Accordingly, this topology links the positive features of a two-level bridge-leg, such as low conduction losses, a small part count, and a simple operation principle, with the benefits of a three-level topology, which are low switching losses and superior output voltage quality [66,67]. On the one hand, the T-type structure does not require the two additional clamping diodes  $D_1$  and  $D_2$  compared to the NPC topology nor an additional, possibly bulky, clamping capacitor  $C_{\rm cl}$  [77] as it is the case for the FC bridge-leg (cf. Fig. 2.3). Furthermore, with the T-type topology direct bridge-leg output voltage transitions from the positive voltage  $V_{\rm dc}/2$  to the negative voltage  $-V_{\rm dc}/2$  or vice versa are possible. For the NPC structure such transitions might lead to an uneven blocking voltage share in the transient stage when both power semiconductors in series turn-off at the same time [66]. On the other hand, the H-bridge converter given in Fig. 2.3(e) is built with the same number of power semiconductors than the T-type topology but requires a separate DC source for each output phase [68, 70, 77]. For a three-phase output stage converter, an additional massive DC link capacitor is hence needed, considering the power pulsation with twice the output frequency. Accordingly, the just given reasons clearly favor to realize the input and output stages with a T-type bridge-leg topology.

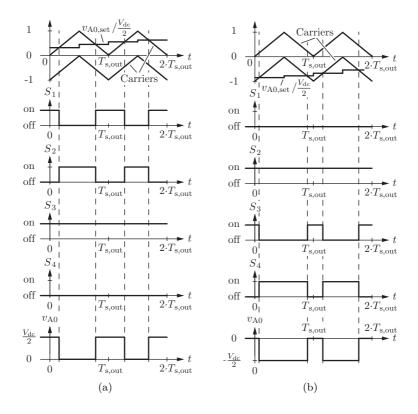

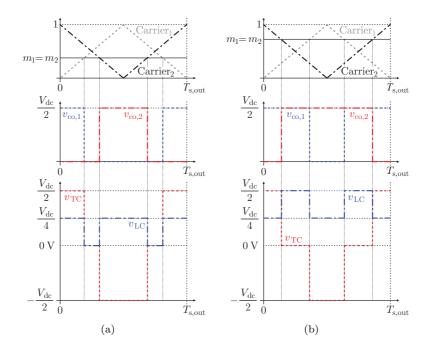

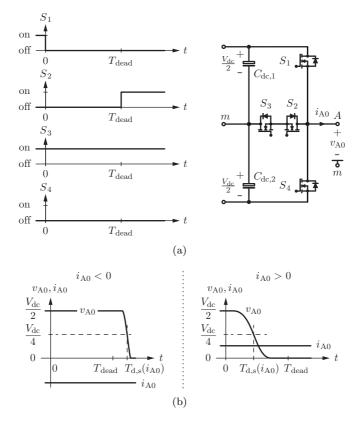

The operation of the T-type converter is explained to its full extent in [71]. The converter is actuated by a digital microprocessor, as further explain in Chapter 3, and is run employing the carrier-based modulation scheme shown in **Fig. 2.4** for a positive and negative set-point bridge-leg output voltage, e.g.  $v_{A0,set}$  for phase A. Two in-phase triangular carriers with period  $T_{s,out} = 1/f_{s,out}$ , where  $f_{s,out}$  is the switching frequency, are used to generate positive and negative bridge-leg output voltages  $v_{A0}$  as shown in the figure. The process is asymmetrical, regular sampled [78], i.e.  $v_{A0,set}$  and required measurements for the control of the converter are updated twice in one switching period, thus when the carriers are at their minimum and maximum.<sup>3</sup>

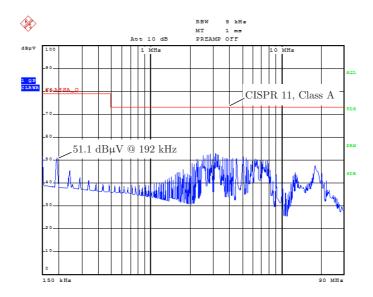

To achieve the requested small-signal bandwidth  $\geq 4$  kHz of the output voltage (cf. Tab. 1.1), an output stage switching frequency  $f_{s,out}$  which is roughly one order of magnitude higher than 4 kHz, is necessary, i.e.  $f_{s,out} \stackrel{>}{\approx} 40$  kHz. In addition, the compliance to the conducted EMI limits given in CISPR 11, Class A [36] imposes further constraints on  $f_{s,out}$  as explained in the following.

The harmonic spectrum of the output voltage of a switch-mode converter shows harmonics at multiples of the switching frequency. Depending on the modulation, more or less wide sidebands around these harmonics are generated [78–80]. The CISRP 11 standard limits the conducted electromagnetic emissions of a converter (measured in  $dB\mu V$  in the frequency range of [150 kHz, 30 MHz] and thus directly restricts the amplitudes of the output voltage harmonics in the indicated frequency range. Typically, to design the output filter in compliance to CISPR 11, the first harmonic with ordinal number n located in [150 kHz, 30 MHz] is decisive. Therefore,  $f_{s,out}$  is selected such that this particular harmonic component is pushed as much as possible to higher frequencies to maximally exploit the attenuation provided by the filter. This implies that the frequency of the  $(n-1)^{\text{th}}$  harmonic is located just below 150 kHz. Often, this harmonic is placed at 144 kHz < 150 kHz - 4.5 kHz = 145.5 kHz, because the conducted EMI measurement procedure [81] employs a test receiver bandwidth of  $\pm 4.5$  kHz around the center frequency. Further explanations concerning EMI measurements are given throughout Chapter 3.

Based on the above elaboration, 144 kHz needs to be an integral multiple of the switching frequency  $f_{\rm s,out}$ , and thus considering  $f_{\rm s,out} \approx 40$  kHz, possible values of  $f_{\rm s,out}$  are 36 kHz, 48 kHz, and 72 kHz. On the one hand, the higher the switching frequency the higher the switching

$<sup>^3\</sup>mathrm{For}$  such a sampled process the term "double-update-mode" is sometimes used.

Figure 2.4: Illustrative drawing of the employed asymmetrical regular sampled carrier-based modulation scheme to actuate each T-type bridge-leg of the input and output stage converters (a) for a positive and (b) for a negative bridge-leg output set-point voltage  $v_{A0,set}$  (exemplary shown for phase A of the output stage).

losses and typically also the lower the efficiency of the converter.<sup>4</sup> On the other hand, a higher  $f_{\rm s,out}$  potentially leads to a smaller filter volume and also allows for a faster dynamic response of the output voltage.

$<sup>^{4}</sup>$ For the designed converter system (cf. Chapter 3), the total nominal losses are composed of roughly 2/3 semiconductor (including the gate driving) and 1/3 filter losses. The semiconductor losses are further separated into approximately 4/5 of switching (and gate driving) and 1/5 of conduction losses.

Thus, as a compromise between a high efficiency, a small filter volume, and fast dynamic response, a switching frequency of  $f_{\rm s,out} = 48$  kHz is selected for the output stage. For the input stage the same switching frequency of  $f_{\rm s,in} = f_{\rm s,out} = 48$  kHz is utilized, although the input stage has by far lower input voltage dynamic specifications. With this choice of  $f_{\rm s,in}$ , a low-volume realization of the input filter is targeted.

Due to the rapid development of Silicon Carbide (SiC) power semiconductors in the last years, which feature continuously increasing power capacities and present lower losses and higher temperature operation compared to Silicon (Si), SiC MOSFETs [82] have been chosen to realize the switching devices for the selected T-type bridge-leg topology and the switching frequency of 48 kHz. In a first step, Cree's 1200 V C2M0080120D MOSFETs (with a channel resistance of 80 m $\Omega$ ) are employed (cf. Section 3.2) and in a second step, because of the development occurred in the meantime, Cree's 1200 V C2M0025120D MOSFETs (with a channel resistance of  $25 \text{ m}\Omega$ ) are utilized. All four switching devices of the T-type topology are realized with the same type of 1200 V MOSFET (C2M0080120D or C2M0025120D), even though the two middle switches  $S_2$  and  $S_3$  could be realized with 600 V / 650 V devices [cf. Fig. 2.3(b)]. However, no 600 V / 650 V SiC MOSFET with comparable performance regarding switching and conduction losses than the two selected devices have been available up to this moment.

### 2.2 Coupling Inductor Approach

To increase the current-carrying capacity and to enhance the largesignal bandwidth of one 10 kW module of the high bandwidth controllable AC voltage source (CVS) given in Fig. 1.1, i.e. to increase the frequency  $f_{\rm out,max}$  up to which the CVS delivers full power, the current rating of each phase leg can be doubled by using two paralleled bridgelegs per phase (cf. **Tab. 2.1**).<sup>5</sup> For the filter designed in Section 3.2, a large-signal bandwidth of 2 kHz is from there expected, which complies to the specification indicated in Tab. 1.1. For output frequencies  $f_{\rm out} < f_{\rm out,max}$ , the CVS hence reveals over-current capabilities, i.e. it is able to provide an output current which is higher than the nominal one. At  $f_{\rm out} = 50$  Hz twice the nominal current of  $I_{\rm out,n} = 14.5$  A (rms), i.e.  $I_{\rm out,max} = 29$  A (rms), can be delivered for instance.

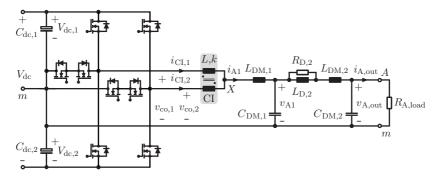

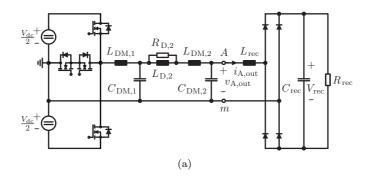

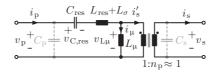

In [83,84], it is revealed that the total volume of the converter stage and filter is reduced if a Coupling Inductor (CI) [cf. **Fig. 2.5**] is employed for the two bridge-legs of each phase instead of two single inductors. Since, to the knowledge of the author, a comprehensive discussion of CIs for a coupling factor  $k \approx 1$  is missing in literature (cf. **Appendix A**), the section at hand focuses on the main aspects of CI design and application for  $k \approx 1$ , including the basic modeling and the control as well as the experimental verification of a CI as employed in the considered CVS, and thus partly extends the knowledge base for CIs. As motivated in Section 3.1, each output phase is operated individually and hence the analysis presented below is based on single-phase considerations. The single-phase circuit for phase A in which the CI is utilized is depicted in Fig. 2.5; Tab. 2.1 summarizes the specifications of the CVS which are relevant for this section.

The outline of this part is as follows: definitions and different equivalent circuits of a CI are derived in Section 2.2.1. Section 2.2.2 introduces a splitting of the CI currents into a transverse (DM) and a longitudinal (CM) component and analyzes their influence on the magnetic flux density in the core. Stationary and dynamic conditions to guarantee a

<sup>&</sup>lt;sup>5</sup>It is remarked that theoretically the large-signal bandwidth  $f_{\rm out,max}$  of the output voltage can be extended up to the value of the small-signal bandwidth  $f_{\rm bw,ss}$ . However, practically,  $f_{\rm out,max}$  is often smaller than  $f_{\rm bw,ss}$  due to the limited current-carrying capability of the converter's bridge-legs and filter to conducted the elevated capacitive filter current. Accordingly, augmenting the current rating of the CVS by placing bridge-legs in parallel is an appropriate means to boost the large-signal bandwidth.

**Table 2.1:** For Section 2.2 relevant electrical specifications of the CVS(cf. Fig. 1.1).

<sup>1</sup>) line-to-neutral; <sup>2</sup>)  $V_{dc} = V_{dc,1} + V_{dc,2}$ ; <sup>3</sup>) Current-derating:  $I_{out,max} @ f_{out} = 50 \text{ Hz and } I_{out,n} \text{ for } f_{out,max} = 2 \text{ kHz}.$

| Nominal output power, P <sub>out,n</sub>               | 10 kW                |

|--------------------------------------------------------|----------------------|

| Nominal output voltage, $V_{\text{out,n}}^{(1)}$ (rms) | $230 \mathrm{V}$     |

| Nominal DC link voltage, $V_{dc,n}^{(2)}$              | 700 V                |

| Maximum DC link voltage, $V_{\rm dc,max}^2$            | 800 V                |

| Nominal output current, $I_{out,n}$ (rms)              | 14.5 A               |

| Maximum output current, $I_{out,max}$ (rms)            | 29 A                 |

| Output frequency, $f_{out}$                            | $0-2 \mathrm{kHz^3}$ |

| Converter switching frequency, $f_{\rm s}$             | $48 \mathrm{kHz}$    |

| Nominal efficiency, $\eta_n$                           | $\geq 95\%$          |

Figure 2.5: Equivalent circuit of one output phase, e.g. phase A, of the CVS realized with two bridge-legs coupled by a coupling inductor. In anticipation of the results obtained in Section 3.2 a two-stage LC output filter with a passive series RL damping branch is employed.

symmetrical CI core magnetization are elaborated in Section 2.2.3 and Section 2.2.4, respectively. To verify the theoretical analysis and the simulations, experimental results are finally presented in Section 2.2.5. Furthermore, a selection and summary of relevant literature of CIs is presented in Appendix A to support the discussion of the CI concept in the following.

#### 2.2.1 CI: Definitions and Equivalent Circuits

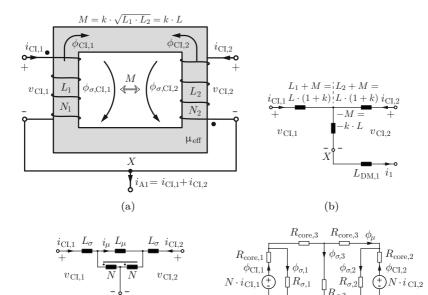

The definitions of the currents, voltages, and fluxes as well as of the winding directions for the CI are shown in **Fig. 2.6(a)**.  $L_1$  and  $L_2$  are the self-inductances, M is the mutual inductance given by  $M = k \cdot \sqrt{L_1 \cdot L_2} \ge 0$  and k is the coupling factor defined as  $k = \sqrt{1 - \sigma} \land k \in [0, 1]$ , where  $\sigma \in [0, 1]$  is the total leakage-factor.

Assuming perfect symmetry, both windings of the CI are identical, and hence they have the same number of turns  $(N = N_1 = N_2)$  and the same self-inductances  $L = L_1 = L_2$ . Consequently, the voltage across the CI windings are given by

$$\begin{aligned} v_{\mathrm{CI},1} &= L \cdot \frac{\mathrm{d}_{i_{\mathrm{CI},1}}}{\mathrm{d}_{t}} - M \cdot \frac{\mathrm{d}_{i_{\mathrm{CI},2}}}{\mathrm{d}_{t}}, \\ v_{\mathrm{CI},2} &= -M \cdot \frac{\mathrm{d}_{i_{\mathrm{CI},1}}}{\mathrm{d}_{t}} + L \cdot \frac{\mathrm{d}_{i_{\mathrm{CI},2}}}{\mathrm{d}_{t}}, \end{aligned}$$

$$(2.1)$$

which directly leads to the equivalent circuit model depicted in **Fig. 2.6(b)** [85–87] - which does not contain an ideal transformer for galvanic isolation as both windings are connected at node X. It is especially pointed out that M and k are defined to be positive quantities, which differs from the definition in other publications.

It can be deduced from Fig. 2.6(a) that the low-frequency components of the fluxes  $\phi_{\text{CI},1}$  and  $\phi_{\text{CI},2}$  in the core, resulting from equal lowfrequency components of the bridge-leg currents  $i_{\text{CI},1}$  and  $i_{\text{CI},2}$ , have the same value for  $N = N_1 = N_2$ . For a high coupling factor  $k \approx 1$ , the fluxes almost completely cancel each other and only the leakage flux components remain. This allows employing a smaller core cross-section compared to two single inductors. However, a series inductor  $L_{\text{DM},1}$ then has to be provided for the DM filtering [cf. Fig. 2.8(a)]. It has to be noted that a low coupling factor could be realized by a proper selection of the core geometry, i.e. by reducing the length of the leakage path [87–94].

The time derivatives of both CI winding currents for Fig. 2.5 are given by

$$\frac{di_{CI,1}}{dt} = \frac{1}{L_{CI,f}} \cdot \left[ v_1 \cdot (L_{DM,1} + L) + v_2 \cdot (k \cdot L - L_{DM,1}) \right] \\

\approx \frac{1}{k^{\pm 1,L \gg L_{DM,1}}} \frac{1}{4 \cdot L_{DM,1}} \cdot (v_1 + v_2), \\

\frac{di_{CI,2}}{dt} = \frac{1}{L_{CI,f}} \cdot \left[ v_2 \cdot (L_{DM,1} + L) + v_1 \cdot (k \cdot L - L_{DM,1}) \right] \\

\approx \frac{1}{k^{\pm 1,L \gg L_{DM,1}}} \frac{1}{4 \cdot L_{DM,1}} \cdot (v_1 + v_2),$$

(2.2)

$L_{\rm DM\,1}$

(c)

Figure 2.6: (a) Definitions of the CI currents, voltages, and fluxes, (b) equivalent circuit of the (symmetric,  $N = N_1 = N_2$ ) CI based on the self-inductances and the mutual inductance, (c) equivalent circuit based on the leakage inductance and the magnetizing inductance, and (d) simplified reluctance model.

$R_{\text{core},3}$

(d)

where  $L_{\text{CI,f}} = L^2 \cdot (1 - k^2) + 2 \cdot L_{\text{DM,1}} \cdot (1 + k) \cdot L$ .  $v_1 = v_{\text{co,1}} - v_{\text{A1}}$ and  $v_2 = v_{\text{co,2}} - v_{\text{A1}}$  are the differences between the bridge-leg output voltages  $v_{\text{co,1}}$ ,  $v_{\text{co,2}}$  and the voltage across the first DM filter capacitor  $C_{\text{DM,1}}$ . From the above equations, it can be directly derived that, if the parallel bridge-legs are operated in an interleaved manner, both CI winding currents show a ripple with twice the switching frequency  $f_s$  of a bridge-leg. Furthermore, both winding currents are equal if k = 1 and  $L \gg L_{\text{DM,1}}$ . In this case, the DM filtering is only achieved by  $L_{\text{DM,1}}$ without contribution of the CI. This is not immediately obvious from Fig. 2.6(b) (series inductance  $-k \cdot L$ ), but can be seen directly from **Fig. 2.6(c)** considering (2.3).

*Remark*: To achieve the interleaving, the two carriers for the PWM of the bridge-legs are phase-shifted by  $180^{\circ}$ . An interleaved operation of the two bridge-legs is assumed for the rest of this section.

It is noted, that for k = 1 and  $L \gg L_{\text{DM},1}$ , the voltage at node X (cf. **Fig. 2.6**) with reference to the DC input voltage midpoint m is approximately  $(v_{\text{co},1} + v_{\text{co},2})/2$  and shows five levels. Therefore, the number of voltage levels is increased from three (for each bridge-leg) to five as also mentioned in Appendix A.

Since the CI is assumed to be electrically and magnetically symmetrical, the leakage inductances  $L_{\sigma}$  and the magnetizing inductance  $L_{\mu}$  can be distributed equally to the primary and secondary side of a transformer equivalent circuit. This results in the circuit depicted in **Fig. 2.6(c)**, because both windings are connected to the same node X. The derivation of this circuit is step-by-step shown in **Fig. 2.7**. A similar CI equivalent circuit is presented in [89, 95–97]. A parameter identification of the electrical properties to Fig. 2.6(b) results in

$$L_{\sigma} = L \cdot (1 - k),$$

$$L_{\mu} = 4 \cdot k \cdot L.$$

(2.3)

Consequently, the magnetizing inductance is roughly 4 times the selfinductance (for  $k \approx 1$ ). The transformer shown in Fig. 2.6(c) is ideal, and clearly points out the coupling of  $i_{\text{CI},1}$  and  $i_{\text{CI},2}$  which are, however, only identical if  $L_{\mu} \gg L_{\text{DM},1}$  and thus  $L \gg L_{\text{DM},1}$ . For completeness a simplified reluctance model is shown in **Fig. 2.6(d)**. Especially for multi-phase systems with more than two phases, this model is a preferred approach to analyze the CI [98–105].

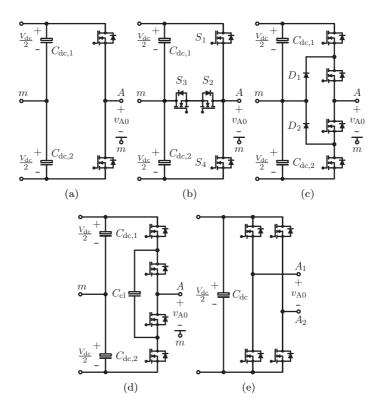

Before analyzing the coupling inductor in more details, the two single-stage LC filter structures shown in Fig. 2.8 (one with a CI and one without) are compared with respect to the required filter inductances and capacitances for two difference cases:

▶ Same maximum peak-to-peak bridge-leg current ripples: In industrial converters, the maximum peak-to-peak bridge-leg output current ripples  $\Delta i_{\rm CI,1,pp,max}$  and  $\Delta i_{\rm CI,2,pp,max}$  are typically limited to 20%-60% of the nominal output current peak value in order to restrict current sampling errors, the peak current stress and / or the switching losses of the power semiconductors as well as the high-frequency losses in the inductive components. Thus, on one hand, compared to a standard interleaved parallel operation of

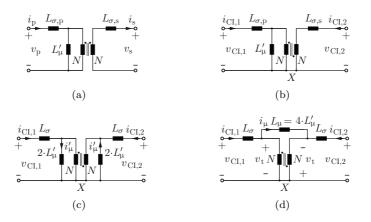

Figure 2.7: Derivation of the equivalent circuit depicted in Fig. 2.6(c) for a symmetrical CI ( $N = N_1 = N_2$ ): (a) transformer equivalent circuit with primary and secondary leakage inductances  $L_{\sigma,p}$  and  $L_{\sigma,s}$  as well as magnetizing inductance  $L'_{\mu}$ ; (b) equivalent circuit for a CI, as employed in Fig. 2.5; (c) equal distribution of the leakage ( $L_{\sigma} = L_{\sigma,p} = L_{\sigma,s}$ ) and magnetizing inductances to the primary and secondary side for a symmetric CI; and (d) combining the two inductances  $2 \cdot L'_{\mu}$  to a single magnetizing inductance  $L_{\mu} = 4 \cdot L'_{\mu}$ , since both windings are connected at X, resulting in the circuit of Fig. 2.6(c).

The equivalence of (c) and (d) can also be shown by calculating the voltages across the CI windings: for (c) the voltages  $v_{\text{CI},1} = L_{\sigma} \cdot di_{\text{CI},1}/dt + 2 \cdot L'_{\mu} \cdot di'_{\mu}/dt$  and  $v_{\text{CI},2} = L_{\sigma} \cdot di_{\text{CI},2}/dt - 2 \cdot L'_{\mu} \cdot di'_{\mu}/dt$  result. The ideal transformer forces a magnetizing current  $i'_{\mu} = (i_{\text{CI},1} - i_{\text{CI},2})/2$  as shown in (c) [equal voltages across  $2 \cdot L'_{\mu}$  on both sides of the ideal transformer] which leads to  $v_{\text{CI},1} = (L_{\sigma} + L'_{\mu}) \cdot di_{\text{CI},1}/dt - L'_{\mu} \cdot di_{\text{CI},2}/dt$  and  $v_{\text{CI},2} = -L'_{\mu} \cdot di_{\text{CI},1}/dt + (L_{\sigma} + L'_{\mu}) \cdot di_{\text{CI},2}/dt$ . For (d) the voltage  $v_t$  across the ideal transformer is  $v_t = L_{\mu}/2 \cdot di_{\mu}/dt$  with a magnetizing current of  $i_{\mu} = (i_{\text{CI},1} - i_{\text{CI},2})/2 = i'_{\mu}$ . Thus, the winding voltages yield  $v_{\text{CI},1} = L_{\sigma} \cdot di_{\text{CI},1}/dt + v_t = L_{\sigma} \cdot di_{\text{CI},1}/dt + L_{\mu}/2 \cdot di_{\mu}/dt = (L_{\sigma} + L_{\mu}/4) \cdot di_{\text{CI},1}/dt - L_{\mu}/4 \cdot di_{\text{CI},2}/dt$  and  $v_{\text{CI},2} = L_{\sigma} \cdot di_{\text{CI},2}/dt + v_t = L_{\sigma} \cdot di_{\text{CI},1}/dt + (L_{\sigma} + L_{\mu}/4) \cdot di_{\text{CI},2}/dt - L_{\mu}/2 \cdot di_{\mu}/dt = -L_{\mu}/4 \cdot di_{\text{CI},1}/dt + (L_{\sigma} + L_{\mu}/4) \cdot di_{\text{CI},2}/dt - L_{\mu}/2 \cdot di_{\mu}/dt = -L_{\mu}/4 \cdot di_{\text{CI},1}/dt + (L_{\sigma} + L_{\mu}/4) \cdot di_{\text{CI},2}/dt$ . A factor comparison then identifies  $L_{\mu} = 4 \cdot L'_{\mu}$  as derived for (d).

two bridge-legs with individual inductors  $L_{\rm f}$  [cf. Fig. 2.8(b)], the inductance value of  $L_{\rm DM,1}$  [cf. Fig. 2.8(a)], to obtain the same

Figure 2.8: Single-stage LC filter structures: (a) parallel connection of two bridge-legs with a coupling inductor (CI - without DM filter influence for k = 1) and a filter stage formed by  $L_{\text{DM},1}$  and  $C_{\text{DM},1}$ ; and (b) parallel connection of two bridge-legs with individual inductors  $L_{\rm f}$ , where the LC filter stage is then effectively formed by  $\frac{L_{\rm f}}{2}$  (parallel connection of both inductors  $L_{\rm f}$ ) and  $C_{\text{DM},1}$ .

maximum peak-to-peak current ripples  $\Delta i_{\text{CI},1,\text{pp,max}} = \Delta i_{\text{CI},2,\text{pp,max}}$  in both bridge-legs is

$$L_{\text{DM},1} = \frac{L}{2 \cdot \left(4 \cdot \frac{L}{L_{\text{f}}} - 1\right)} \underset{L\gg L_{\text{f}}}{\approx} \frac{L_{\text{f}}}{8}, \qquad (2.4)$$

for  $k \approx 1$ , i.e. for a bifilar arrangement of the CI windings. However,  $L_{\text{DM},1}$  has to conduct a low-frequency current as well as a maximum peak-to-peak current ripple  $\Delta i_{\text{A1,pp,max}}$  which is twice the one through  $L_{\text{f}}$ .

On the other hand, regarding EMI noise suppression, the capacitance  $C_{\text{DM},1}$  in this case needs to be 4 times greater for the filter structure with a CI [cf. Fig. 2.8(a)] than for the filter without a CI [cf. Fig. 2.8(b)] to reach the same *LC* filter cut-off frequency. Or, for  $L_{\text{DM},1} = L_{\text{f}}/8$  and equal capacitance values  $C_{\text{DM},1}$  for both filter structures, the high-frequency roll-off of the filter in Fig. 2.8(a) is reduced by 12 dB compared to the filter in Fig. 2.8(b).

► Same maximum peak-to-peak current ripple of  $i_{A1}$ : In this case,  $L_{\text{DM},1}$  is given by

$$L_{\text{DM},1} \stackrel{k=1,L\gg L_{\text{f}}}{\approx} \frac{L_{\text{f}}}{2},$$

(2.5)

resulting in the same filter cut-off frequency for equal capacitance values of  $C_{\text{DM},1}$  for both filter structures depicted in Fig. 2.8.

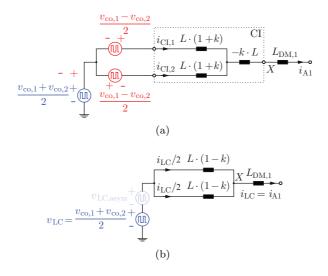

Figure 2.9: (a) Division of the bridge-leg voltages into a longitudinal current  $i_{\rm LC}$  (in the direction of the power flow) forming voltage  $v_{\rm LC}$  and a transverse current  $i_{\rm TC}$  forming voltage  $v_{\rm TC}$ , (b), (c) equivalent circuits for longitudinal voltages and currents, and (d) equivalent circuit for transverse voltages and currents. In (c), compared to (b), the negative inductance part  $-k \cdot L$  of both branches is concentrated into a single negative inductance  $-k \cdot L/2$ .

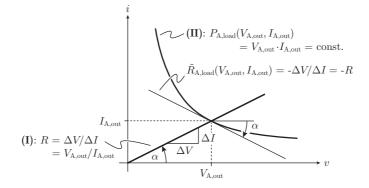

## 2.2.2 Transverse and Longitudinal Current Separation and Corresponding Magnetic Flux Densities

An illustrative method to analyze the CI is to distinguish between an equivalent circuit for the Longitudinal Current [LC - **Fig. 2.9(b)**] and for the Transverse Current [TC - **Fig. 2.9(d)**]. In [83,92,96,98,102,104, 106–120], the LC is denominated as a Common Mode (CM) current and the TC as a Differential Mode (DM) current. However, these denominations are associated to EMI investigations and hence to avoid confusion with the EMI nomenclature, the terms *Longitudinal Current* (in the direction of the power flow) and *Transverse Current* (and / or cross current between the converter bridge-legs) are preferred (cf. **Fig. 2.9**).

The voltages  $v_{\rm LC}$  and  $v_{\rm TC}$  which drive the longitudinal and the

Fig. 2.9: Continued.

transverse current, respectively, are given by

$$\begin{aligned}

v_{\rm LC} &= \frac{v_{\rm co,1} + v_{\rm co,2}}{2}, \\

v_{\rm TC} &= v_{\rm co,1} - v_{\rm co,2}

\end{aligned}$$

(2.6)

and are depicted in Fig. 2.10(a) and Fig. 2.10(b) for interleaved voltages  $v_{co,1}$  and  $v_{co,2}$ . The associated effective longitudinal inductance  $L_{LC}$  and transverse inductance  $L_{TC}$  are

$$L_{\rm LC} = L \cdot (1-k) = L_{\sigma}, L_{\rm TC} = L \cdot (1+k).$$

(2.7)

Comparing Fig. 2.9(d) to Fig. 2.6(c), it is clear that the transverse current  $i_{\rm TC}$  is equal to the magnetizing current  $i_{\mu}$  [106,114]. Using a CI and a separate filter inductor  $L_{\rm DM,1}$  allows suppressing the transverse current by an inductance which is four times the self-inductance L of the CI [for  $k \approx 1$ , cf. Eq. (2.3)]. This explains why (for the same maximum peak-to-peak bridge-leg current) considerable higher inductance values [cf. Eq. (2.4)] are required for two single inductors  $L_{\rm f}$  in each bridgeleg than for employing a CI and just one filter inductance  $L_{\rm DM,1}$  as depicted in Fig. 2.9(a).

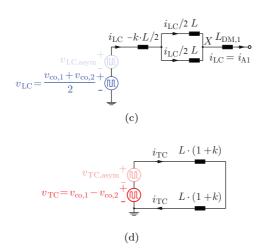

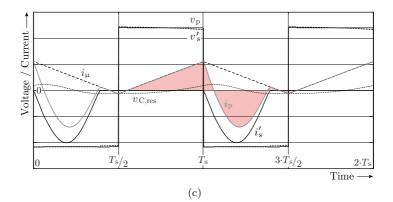

Figure 2.10: (a)  $v_{\rm LC}$  and  $v_{\rm TC}$  for a modulation index of  $m_{\rm i} \leq 0.5$  and (b)  $v_{\rm LC}$  and  $v_{\rm TC}$  for a modulation index of  $m_{\rm i} \geq 0.5$ . The resulting longitudinal current  $i_{\rm LC} = i_{\rm LC,lf} + \Delta i_{\rm LC}$  (consisting of a low-frequency and a ripple component) as well as the transverse current  $i_{\rm TC}$  for (a) and (b) are shown qualitatively in (c) and (d), respectively. A second set of triangular carriers is employed for modulation indices  $0 > m_{\rm i} \geq -1$  (not shown; cf. Fig. 2.4).

For an ideal coupling of both CI windings (k = 1),  $L_{\rm LC}$  becomes zero (as the leakage inductance) and  $L_{\rm TC} = 2 \cdot L = L_{\mu}/2$  is equal to half of the magnetizing inductance  $L_{\mu}$  [ $L_{\mu,k=1} = 4 \cdot L$ , cf. (2.3)]. Thus, the longitudinal current  $i_{\rm LC}$  is filtered by  $L_{\rm DM,1}$  and the transverse current  $i_{\rm TC}$  is filtered by  $2 \cdot L_{\rm TC}$ , which is also described in [96, 116, 121]. This means on the other hand that the CI, for k = 1, is "transparent" to the longitudinal current  $i_{\rm LC}$  and affects only the transverse current  $i_{\rm TC}$  [122]. Illustratively, this can be seen from Fig. 2.9(a), where the inductances  $L \cdot (1+k)$  become  $2 \cdot L$  for k = 1. For the longitudinal current  $i_{\rm A1}$  the mentioned inductances with the value  $2 \cdot L$  are in parallel, re-

Fig. 2.10: Continued.

sulting in  $2 \cdot L \| 2 \cdot L = L$ . This, together with  $-k \cdot L = -L$ , leads to zero inductance for the longitudinal components  $[k = 1, \text{ cf. Fig. } 2.9(\mathbf{c})]$ .

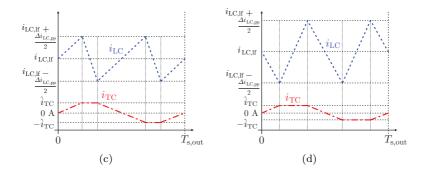

The ripples of both current components are depicted in Fig. 2.10(c) and Fig. 2.10(d). They reveal the following characteristics:

▶ Longitudinal current  $i_{LC} = i_{AI}$ : The current ripple shows twice the switching frequency of the bridge-legs. The low-frequency value of the longitudinal current  $i_{LC,lf}$  is given by the sum of the load current  $i_{A,out}$  and the reactive capacitor currents of the output filter. The peak-to-peak current ripple is maximal for a modulation index of  $m_i = 0.25$  and can be calculated as follows:

$$\Delta i_{\rm LC,pp} = \frac{V_{\rm dc}}{\left(L_{\rm DM,1} + \frac{L \cdot (1-k)}{2}\right) \cdot f_{\rm s,out}} \cdot \left(\frac{m_{\rm i}}{4} - \frac{m_{\rm i}^2}{2}\right) \\ \underset{m_{\rm i}=0.25}{\leq} \frac{V_{\rm dc}}{32 \cdot \left(L_{\rm DM,1} + \frac{L \cdot (1-k)}{2}\right) \cdot f_{\rm s,out}}.$$

(2.8)

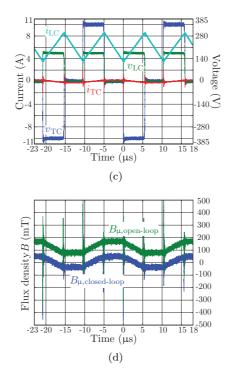

▶ Transverse current  $i_{TC}$ : The current ripple shows the switching frequency  $f_{s,out}$  of the bridge-legs. If both bridge-legs and the CI are completely symmetrical, the mean (low-frequency) value of  $i_{TC}$  is zero. If asymmetries are present (as given in practice), a proper current control scheme needs to guarantee that a low-frequency value of  $i_{TC,If} \approx 0$  A is achieved as discussed in Section 2.2.3. The peak-to-peak ripple of  $i_{TC}$  is maximal at a mod-

ulation index of  $m_i = 0.5$  and is given by

$$\Delta i_{\rm TC,pp} = \frac{m_i \cdot V_{\rm dc}}{4 \cdot L \cdot (1+k) \cdot f_{\rm s,out}}$$

$$\leq \frac{V_{\rm dc}}{m_i = 0.5} \frac{V_{\rm dc}}{8 \cdot L \cdot (1+k) \cdot f_{\rm s,out}}.$$

(2.9)

As already pointed out earlier, both CI winding currents are only equal if  $L \gg L_{\text{DM},1}$  - mathematically strictly only for  $L \to \infty$ . Since the winding currents can be formed by superposition of  $i_{\text{LC}}/2$  and  $i_{\text{TC}}$ for a symmetrical CI

the only difference between both winding currents is the transverse current  $i_{\rm TC}$  (equal winding currents can only be reached if  $i_{\rm TC} = 0$  A, i.e. theoretically for an infinite magnetizing inductance and therefore for  $L \to \infty$ ).

The CI shown in Fig. 2.6(a) is in some publications [87, 123, 124] called "inversely coupled inductors" (inverse coupling inductor), because a positive current change in one winding results in a negative voltage drop at the other winding [represented by the negative inductance -M in Fig. 2.6(b)]. If the winding direction of one winding is reversed, "directly coupled inductors" (direct coupling inductor) are obtained. In this case, the longitudinal and transverse inductances are given by

$$L'_{\rm LC} = L \cdot (1+k) = L_{\rm TC}, L'_{\rm TC} = L \cdot (1-k) = L_{\rm LC}$$

(2.11)

and for k = 1 the CI is "transparent" to the transverse current and only filters the longitudinal current (thus, not applicable for interleaved operation of the bridge-legs).

*Remark*: Some publications make the difference between "transient" and "steady-state" inductances of a CI [123–126], which are synonyms for the longitudinal and transverse inductances, respectively.

The magnetic fluxes through both windings  $(N = N_1 = N_2)$  associated with the longitudinal and transverse currents are given by

$$\phi_{1,\mathrm{LC}} = \phi_{2,\mathrm{LC}} = \frac{L_{\mathrm{LC}} \cdot i_{\mathrm{LC}}}{2 \cdot N} = \frac{L \cdot (1-k) \cdot i_{\mathrm{LC}}}{2 \cdot N},

\phi_{1,\mathrm{TC}} = \frac{L_{\mathrm{TC}} \cdot i_{\mathrm{TC}}}{N} = \frac{L \cdot (1+k) \cdot i_{\mathrm{TC}}}{N},

\phi_{2,\mathrm{TC}} = -\frac{L_{\mathrm{TC}} \cdot i_{\mathrm{TC}}}{N} = -\frac{L \cdot (1+k) \cdot i_{\mathrm{TC}}}{N},$$

(2.12)

and

$$\begin{aligned}

\phi_{\text{CI},1} &= \phi_{1,\text{TC}} + \phi_{1,\text{LC}}, \\

\phi_{\text{CI},2} &= \phi_{2,\text{TC}} + \phi_{2,\text{LC}}.

\end{aligned}$$

(2.13)

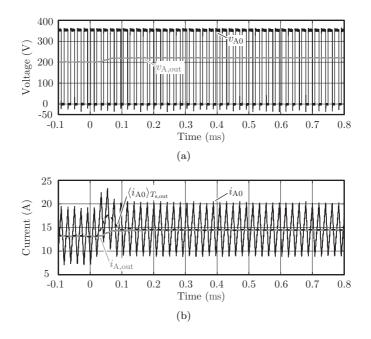

Referring to the given converter system (cf. Tab. 2.1) and the built filter with a CI (cf. **Tab. 2.3**), the maximum longitudinal and transverse current ripples ( $\Delta i_{\rm LC}$  and  $\Delta i_{\rm TC}$ ) as well as the maximal low-frequency longitudinal current  $i_{\rm LC,lf,max}$  ( $i_{\rm LC} = i_{\rm LC,lf} + \Delta i_{\rm LC}$ ) were calculated for the maximum DC link voltage of  $V_{\rm dc,max} = 800$  V and for a switching frequency of  $f_{\rm s,out} = 48$  kHz per bridge-leg:

$$\begin{array}{lll} \Delta i_{\rm TC,pp,max} &= 1.06 \ {\rm A}, \\ \Delta i_{\rm LC,pp,max} &= 5.94 \ {\rm A}, \\ i_{\rm LC,lf,max} &= \sqrt{2} \cdot 29 \ {\rm A} = 41.0 \ {\rm A}. \end{array}$$

(2.14)

For the employed ETD 59/31/22 core (N87) from EPCOS with an equivalent magnetic cross-section area  $A_e = 368 \text{ mm}^2$ , the related values of the CI magnetic flux densities result for a symmetric magnetization in

$$B_{1,\text{TC,pk}} = \frac{\phi_{1,\text{TC,pk}}}{A_{e}} = B_{2,\text{TC,pk}} = \frac{\phi_{2,\text{TC,pk}}}{A_{e}} = 0.11 \text{ T},$$

$$\Delta B_{1,\text{LC,pk}} = \frac{\Delta \phi_{1,\text{LC,pk}}}{A_{e}} = \Delta B_{2,\text{LC,pk}} = \frac{\Delta \phi_{2,\text{LC,pk}}}{A_{e}} = 0.21 \text{ mT},$$

$$B_{1,\text{LC,lf,max}} = \frac{\phi_{1,\text{LC,lf,max}}}{A_{e}} = B_{2,\text{LC,lf,max}} = \frac{\phi_{2,\text{LC,lf,max}}}{A_{e}} = 2.9 \text{ mT},$$

(2.15)

where exemplary (alike for winding 2)

$$\begin{aligned}

\phi_{1,\mathrm{TC,pk}} &= \frac{L_{\mathrm{TC}} \cdot i_{\mathrm{TC,pk}}}{N} = \frac{L_{\mathrm{TC}} \cdot \Delta i_{\mathrm{TC,pp,max}}}{2 \cdot N}, \\

\Delta\phi_{1,\mathrm{LC,pk}} &= \frac{L_{\mathrm{LC}} \cdot \Delta i_{\mathrm{LC,pk}}}{2 \cdot N} = \frac{L_{\mathrm{LC}} \cdot \Delta i_{\mathrm{LC,pp,max}}}{4 \cdot N}, \\

\phi_{1,\mathrm{LC,lf,max}} &= \frac{L_{\mathrm{LC}} \cdot i_{\mathrm{LC,lf,max}}}{2 \cdot N}.

\end{aligned}$$

(2.16)

For the flux density due to  $i_{\rm LC}$ , the part resulting from the current ripple  $\Delta i_{\rm LC,pp,max}$  and the one coming from the low-frequency component  $i_{\rm LC,lf,max}$  are considered separately. From (2.15), it follows that  $B_{1,\rm TC,pk} = B_{2,\rm TC,pk} \gg \Delta B_{1,\rm LC,pk} = \Delta B_{2,\rm LC,pk} \wedge B_{1,\rm LC,lf,max} =$  $B_{2,\rm LC,lf,max}$  and accordingly  $B_{\rm CI,1,pk} = \frac{\phi_{\rm CI,1,pk}}{A_{\rm e}} = B_{\rm CI,2,pk} = \frac{\phi_{\rm CI,2,pk}}{A_{\rm e}} \approx$  $B_{1,\rm TC,pk} = B_{2,\rm TC,pk}$ . Thus, for coupling factors k close to 1, the magnetizing flux determines the maximum flux density in the entire core and can be directly computed to

$$B_{\mu,\rm pk} = \frac{4 \cdot k \cdot L}{2 \cdot N \cdot A_{\rm e}} \cdot i_{\rm TC,pk} \approx B_{1,\rm TC,pk} = B_{2,\rm TC,pk} = 0.11 \text{ T.}$$

(2.17)

27

**Table 2.2:** Comparison between different placements of the first filter stage inductance for the same peak-to-peak current ripple in both bridge-legs [cf. Fig. 2.5] with respect to the required inductance value, volume and losses [referred to configuration (a)]. The comparison is based on simplified similarity relations, as could be derived by a more detailed analysis. The volume and losses of the coupling inductor  $CI_1$  are not considered.

<sup>1)</sup> The direct coupling inductor  $\text{CI}_2$  in configuration (c) can only be used to filter the longitudinal current and / or is "transparent" to the transverse current (for  $\tilde{k} \approx 1$ ); accordingly, an inverse coupling inductor  $\text{CI}_1$  (or individual inductors) must be employed to limit the transverse current.

|                                | $\begin{array}{c} L,k \\ L_{\mathrm{DM},1} \\ CI_1 \end{array}$ |                                                                                                                                                             | $\begin{array}{c} L,k \widetilde{L},\widetilde{k} \\ \bullet \\ \hline CI_1 CI_2 \end{array} \bullet$                           |

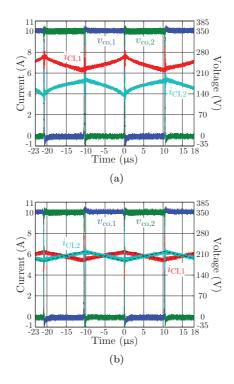

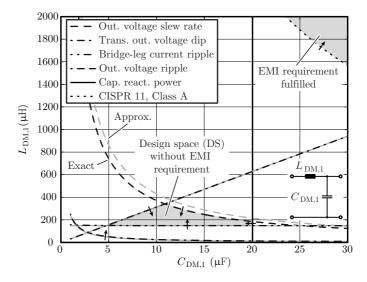

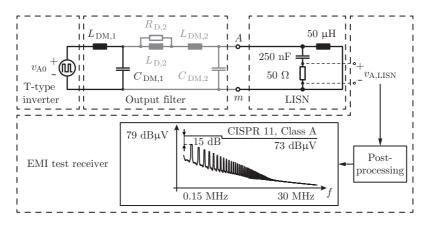

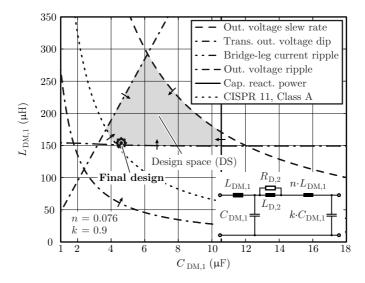

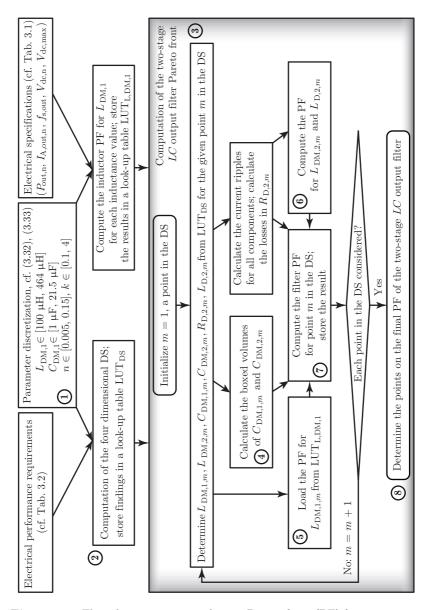

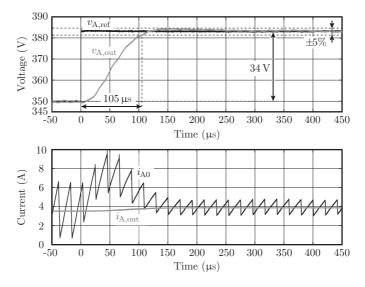

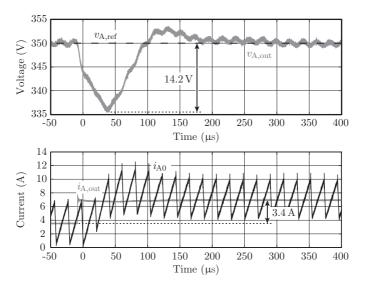

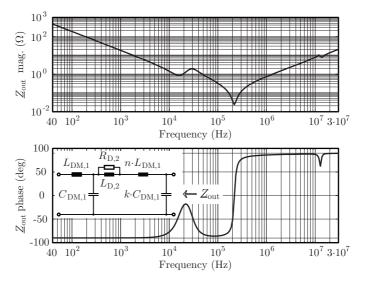

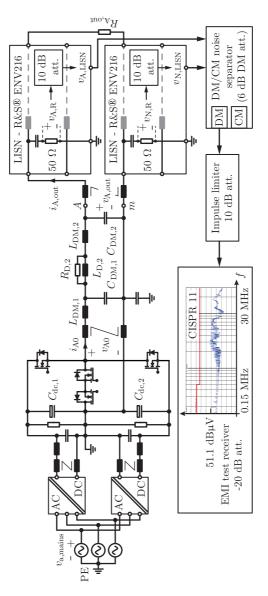

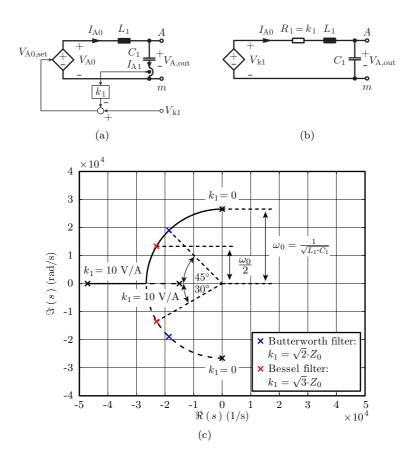

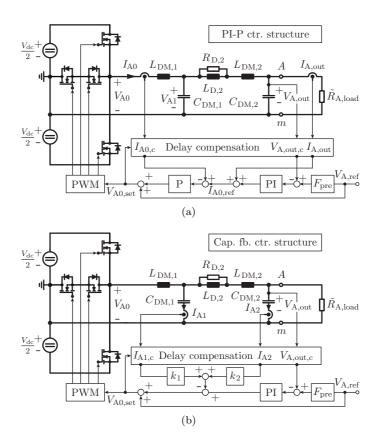

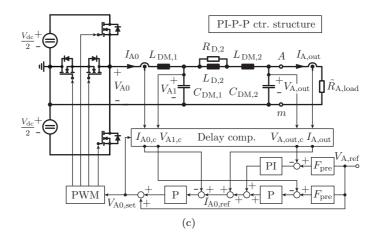

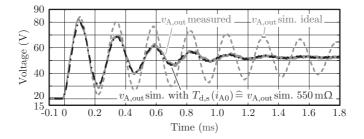

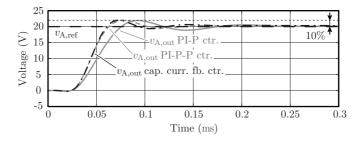

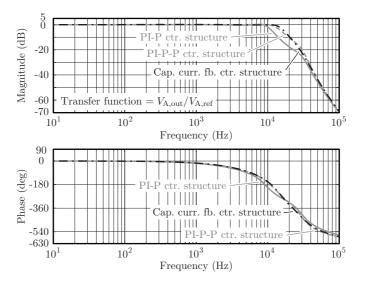

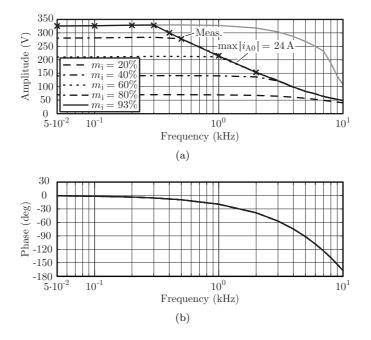

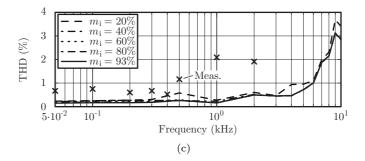

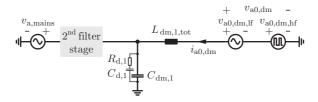

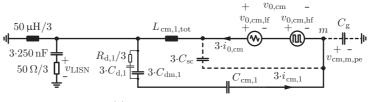

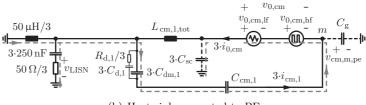

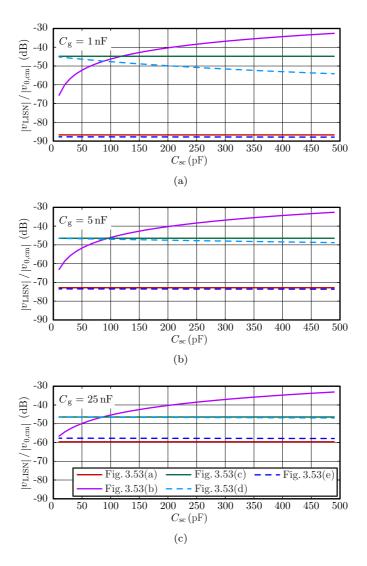

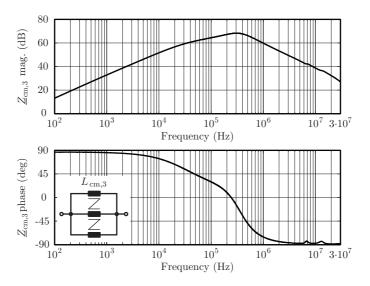

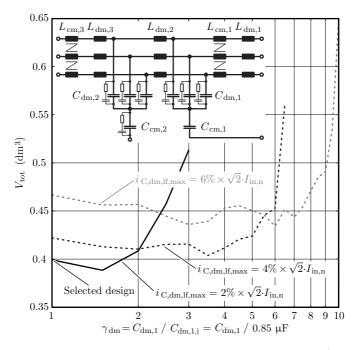

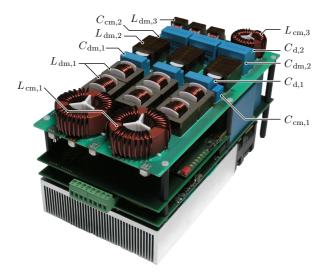

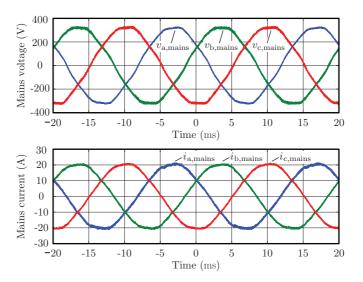

|--------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|