# SiC vs. Si – Evaluation of Potentials for Performance Improvement of Power Electronics Converter Systems by SiC Power Semiconductors

J. Biela, M. Schweizer, S. Waffler, B. Wrzecionko, and J.W. Kolar

ETH Zurich, Power Electronic Systems Laboratory biela@lem.ee.ethz.ch; www.pes.ee.ethz.ch

Keywords: DC-DC Converter, PFC Converter, SiC JFETs, Optimisation

Abstract. Switching devices based on wide band gap materials as SiC offer a significant performance improvement on the switch level compared to Si devices. A well known example are SiC diodes employed e.g. in PFC converters. In this paper, the impact on the system level performance, i.e. efficiency/power density, of a PFC and of a DC-DC converter resulting with the new SiC devices is evaluated based on analytical optimisation procedures and prototype systems. There, normally-on JFETs by SiCED and normally-off JFETs by SemiSouth are considered.

### Introduction

In power electronic systems there has been a continuous trend towards a higher system power density in the last decades and due to environmental concerns and rising energy costs, also the efficiency of the systems became an important system performance criteria, over the past years besides costs. For meeting these demands, the development of power semiconductors is a crucial enabling factor besides passive components, control, cooling and EMC.

With the recent technological progress in manufacturing power devices based on wide band gap materials as e.g. silicon carbide (SiC) or gallium nitride (GaN), the operating voltage range, the switching speed and/or specific on-resistance have been and will be improved significantly compared to silicon power devices. In case these new devices are applied in power electronic systems, the improvements on the device level will impact also the system performance, which is usually measured by power density, efficiency, weight, reliability, and costs.

In this paper, the system level performance of a single phase PFC converter and of an isolated DC-DC converter, which is achievable with the new SiC devices, is evaluated by means of analytical optimisation algorithms, which provide a design that enables an optimal usage of the features of the new devices. The models used in optimisation algorithms have been verified by measurements on prototype system.

In hard switched applications, SiC Schottky diodes already proved a significant loss reduction and an increase of efficiency/power density. Also switching losses can be reduced enabling either a higher efficiency or an higher switching frequency, i.e. higher power density.

Additionally, SiC devices offer the advantage of high temperature operation. However, the application of this feature is limited by the available packaging technology, the reliability, which significantly decreases with increasing temperature, and the temperature limit of commercial electronic components as gate drive, control IC or capacitors, which is usually below 125°C and which make the design of a high temperature SiC system considerably more complicated and costly. Therefore, a limitation of  $T_i$  below 175°C is assumed here.

Before the system performance of the PFC and the DC-DC converter is evaluated in Section III and Section IV, first the specifications of the applied SiC devices is shortly presented in Section II.

#### Data of SiC Switches

In the following the performance of current SiC devices considered in the system performance evaluation is discussed. There, the focus is on devices, which are relatively mature and which could become commercially available soon.

In Table 1 the data of the SiC devices is listed for the normally-on JFETs by SiCED and the normally-off JFET (SJEP120R125) by SemiSouth. Besides the breakdown voltage and the  $R_{DS(on)}$  at  $T_j=25^{\circ}$ C, also the specific output capacitance and the figure of merit FOM =  $\frac{1}{R_{DS(on)}E_{400V}}$ , which are important for hard switched applications, are listed. Furthermore, the data of the reference Si devices is given. For soft switching applications, the switching losses and also the output capacitance plays only a minor role and the main focus is on the specific  $R_{DS(on)}$ , which determines how much chip area is required for achieving a specific performance/efficiency.

In the table, the significant improvement of the specific  $R_{DS(on)}$  with SiC devices could be clearly seen, so that lower conduction losses at a given chip area can be expected with SiC devices. However, looking at the specific output capacitance, the SiC devices do not offer an improvement yet. A tremendous reduction as with the  $R_{DS(on)}$  could not be expected, as with the shrinking die area, also the length of the drift region must become smaller, in order to limit the resistance of the drift region.

The 1.2kV JFET from SemiSouth has a relatively low capacitance value, which also results in a relatively high FOM. There, it is important to note, however, that due to the vertical channel, which is required for the normally-off behaviour of the JFET, the  $R_{DS(on)}$  basically depends significantly on  $I_D$  at higher current densities and – especially at higher temperatures – the increase of  $R_{DS(on)}$  will result in a significant deterioration of the FOM.

Also with the other SiC devices, the  $R_{DS(on)}$  increases with rising  $T_j$ , what finally also results in a reduction of the FOM. This reduction, however, is not as large as with the JFETs by SemiSouth at higher current densities. In applications striving for high efficiency, the current density in the switches is limited to relatively small values in order to reduce the conduction losses, so that this disadvantage of the SemiSouth JFETs does not have a significant effect.

Due to the  $R_{DS(on)}$  of the JFETs, which increases more than linearly with  $T_j$ , there is an optimal operation  $T_j$  with respect to a maximal current density [4]. At higher junction temperatures than the optimal one, the current density must be decreased in order to avoid a thermal runaway.

Table 1: Current status of SiC switches. Further information could be e.g. found on [1, 2].  $E_{400V}$  is the energy stored in the output capacitance, when charged form 0V...400V, and the figure of merit  $FOM=1/(R_{DS(on)}E_{400V})$  is a performance index for hard switching [3]. As max.  $I_D$  depends significantly on the cooling, the values should just give a hint on the capabilities of the switch for operation at  $T_j \ge 125^{\circ}$ C. The (specific)  $R_{DS(on)}$  is given for 25°C and for the total chip area and for  $R_{DS(on)}$  typical values are depicted.

|                      | $V_{(BR)DSS}$ | $I_{\rm D}$          | $R_{\rm DS(on)}$ | $R_{\rm DS(on)}A_{\rm Chip}$                  | $C_{\rm Out}/A_{\rm Chip}$ @25V       | FOM         | $A_{\rm Chip}$             | $E_{400V}$   |

|----------------------|---------------|----------------------|------------------|-----------------------------------------------|---------------------------------------|-------------|----------------------------|--------------|

| JFET (SiCED)         | 500V          | $\sim 5A$            | $0.2\Omega$      | $11.5 \mathrm{m}\Omega \mathrm{cm}^2$         | $59.3 \mathrm{pF}/\mathrm{mm}^2$      | 0.37        | $5.76 { m mm}^2$           | $13.4 \mu J$ |

| JFET (SiCED)         | 1.2kV         | $\sim 5A$            | $0.33\Omega$     | $19 m\Omega cm^2$                             | $35.7 \mathrm{pF/mm^2}$               | 0.33        | $5.76 { m mm}^2$           | $9.1 \mu J$  |

| JFET (SiCED)         | 1.2kV         | $\sim 17 \mathrm{A}$ | $0.12\Omega$     | $21 \mathrm{m}\Omega \mathrm{cm}^2$           | $35.6 \mathrm{pF}/\mathrm{mm}^2$      | 0.3         | $17.3 \mathrm{mm}^2$       | $28.2\mu J$  |

| JFET (SemiSouth)     | 1.2kV         | >15A                 | $0.125\Omega$    | $5 m \Omega cm^2$                             | $24.5 \mathrm{pF/mm^2}$               | $\sim 1.65$ | $4 \text{mm}^2$            | $4.9\mu J$   |

| MOSFET (Cree)        | 1.2kV         | >20A                 | $0.075\Omega$    | $12.5 \mathrm{m}\Omega \mathrm{cm}^2$         | $39 \mathrm{pF}/\mathrm{mm}^2$        | 0.76        | $16.6 \mathrm{mm}^2$       | $17.5 \mu J$ |

| Si Reference Devices |               |                      |                  |                                               |                                       |             |                            |              |

| IPP60R099CP          | 650V          | 31A                  | $0.09\Omega$     | $25.2 \mathrm{m}\Omega \mathrm{cm}^2$         | $130 \mathrm{pF}/\mathrm{mm}^2$       | 0.97        | $28 \mathrm{mm}^2$         | $11.5 \mu J$ |

| APT50M75B2           | 500V          | 57A                  | $0.075\Omega$    | $90 \text{m}\Omega \text{cm}^2$               | $9.8 \mathrm{pF/mm^2}$                | 0.53        | $120.1  \text{mm}^2$       | $25.1 \mu J$ |

| STW77N65M5           | 650V          | 41A                  | $0.03\Omega$     | $\approx 21.3 \mathrm{m}\Omega \mathrm{cm}^2$ | $\approx 6 \mathrm{pF}/\mathrm{mm}^2$ | 1.94        | $\approx 71 \mathrm{mm}^2$ | $17.2 \mu J$ |

The transient behaviour of the 1200V JFETs by SiCED and by SemiSouth shows similar di/dt & dv/dt values at turn on and different values at turn off because of the different drain source capacitance values. Both devices turn on faster than 50ns and the turn off transient is mainly governed by the parasitic output capacitance of the devices.

### Single Phase Rectifier

A typical low voltage application in the kW range with hard switching are PFC converters, where the switching losses only can be avoided with relatively complex soft switching topologies, which have not gained a significant market share so far. Such hard switched PFC converters are e.g. applied in telecom power supplies. There, a major driving force has been the power density besides costs. Due to rising energy prices and the continuous operation of such systems, the efficiency became more and more important, so that now a multi-criteria optimisation of such systems as shown in [3] is necessary for determining the optimal set of design parameters. In [3] a ultra efficient PFC system with 99.1% efficiency (cf. Fig. 1a) and a highly compact system with a power density of almost  $6 \text{kW/dm}^3$  are presented.

This ultra high efficiency PFC converter is based on Si CoolMOS devices and in the following, the achievable performance with SiC devices is evaluated. Further details about the design can be found in [3].

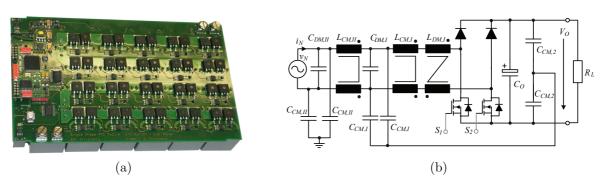

For the prototype system a bridgeless PFC system has been chosen, as the conduction losses are in principle lower than with a standard boost PFC [3]. Furthermore, a capacitive coupling between the mains and the output is inserted to limit the CM noise [3]. During normal operation one switch is always closed and the other one is shaping the input current and controlling the power flow by PWM.

For identifying the set of design parameters, which result in the maximal efficiency, analytical models of the converter including the magnetic components, EMI filter and the thermal design as well as an automatic optimisation procedure have been developed [3]. With this procedure the optimal geometric design of the inductors, the turn number as well as the optimal chip area for the MOSFETs and the diodes is determined. There, the on-resistance as well as the parasitic capacitances are considered for evaluating the semiconductor losses.

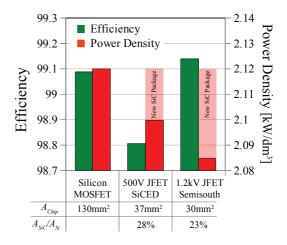

Based on this procedure the optimal parameters for the Si and the SiC devices for different cases as shown in Fig. 2 have been determined. Due to the relatively high specific output capacitance of the 500V JFET and the resulting low FOM, the efficiency and the power density are lower with the SiC devices than with the Si reference MOSFETs + SiC diodes.

Fig. 1: a) Prototype of the efficient 3.2 kW dual-boost PFC rectifier composed of two interleaved 1.6 kW units with an input voltage of 230 V and an output voltage of 365 V; dimensions:  $275 \times 130 \times 85 \text{mm}$ ; power density: 1.1 kW/l. b) Circuit diagram of the dual boost rectifier with capacitive coupling.

The optimal area for the 500V JFET is 37mm<sup>2</sup>, which is approximately 28% of the Si MOSFET area. With the low specific capacitance of the 1.2kV JFET by SemiSouth, a slightly better efficiency could be achieved at a chip area of 30mm<sup>2</sup>, i.e. 23% of the area of the Si MOSFET. A SemiSouth JFET with a lower blocking voltage could probably achieve a higher efficiency, but is not available at the moment.

The power density is roughly the same for all three designs and just varies slightly due to the different semiconductor packages and the number of parallel connected devices. There, the major share of the volume is occupied by the passives and all components are naturally cooled.

Fig. 2: Efficiency and power density for an optimised PFC system with Si MOSFETs (IPP60R099CP), 500V and 1200V JFETs.

The major benefit of SiC for hard switched applications are the Schottky diodes, which show no reverse recovery losses and which have a forward voltage drop comparable to Si diodes.

# **DC-DC** Converter

As a  $2^{nd}$  example an isolated DC-DC converter for telecom power supplies is considered. There, the most important performance criteria are costs and power density, besides efficiency.

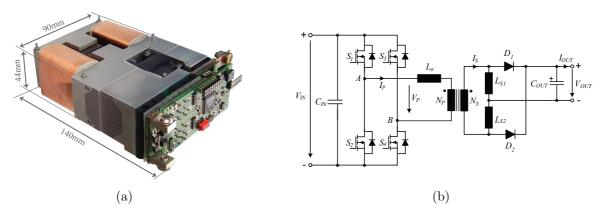

Here, a phase-shift converter with current doubler rectifier as shown in Fig. 3 is considered. The design of the converter is based on an optimisation algorithm, which includes also the thermal/electromagnetic design besides the electrical model. Further details on the design/optimisation procedure can be found in [5].

Due to the leakage inductance  $L_{\sigma}$  of the transformer and the phase shift modulation, all four switches operate under ZVS condition resulting in negligible switching losses at a very low effort on circuit and control side. Thus, only the conduction losses and therewith the  $R_{DS(on)}$ is interesting. For achieving ZVS conditions, a minimum output capacitance is required, which depends on the switching speed. With a smaller capacitance, witching losses increase, but can help to increase part load efficiency.

Fig. 3: a) 5kW prototype of the 400V/48V...54V phase-shift full bridge converter with current doubler rectifier: Height: 1U, volume:  $0.56dm^3$ , power density: 9kW/dm<sup>3</sup>. b) Schematic of the converter.

In spite of the negligible switching losses, the optimal switching frequency of the converter, which results in maximal power density, is just 200kHz. Increasing the frequency results in a smaller power density and efficiency [6].

Based on the optimisation procedure, the full-bridge converter has been optimised with the data of the APT50M72B2 from Microsemi and for the 500V normally-on JFET from SiCED. For the details about the optimisation please refer to [5].

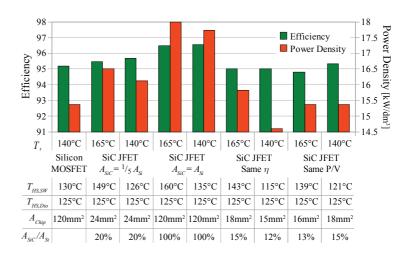

In Fig. 4 the results for the case, where the chip area of the SiC devices is fixed to 1/5 and/or to 1/1 of the Si MOSFET and where the chip area is adapted, so that the efficiency  $\eta$  and/or the power density P/V is the same for the Si and the SiC based converter are shown. In all cases, results for a junction temperature limit of the SiC JFET of 140°C and of 165°C are shown and

Fig. 4: Efficiency/power density for the DC-DC converter with Si MOSFETs (APT50M75B2) and/or the 500V JFETs for the cases where the chip area of the SiC devices is  $1/5 (A_{SiC} = 1/5A_{Si})$  and the same  $(A_{SiC} = A_{Si})$  of the one of the Si MOSFET and for the cases where the SiC chip area is scaled so that the converters have the same  $\eta$  or P/V. For the SiC devices a 140°C and a 165°C limit for the junction temperature and separate heat sinks for the Si rectifier diodes and the switches of the full-bridge have been assumed. Below the graph, the heat sink temperature  $T_{HS,SW}$  of switch and  $T_{HS,Dio}$ of the rectifier diodes is given. In the power density only the net component volume is included, i.e. the power density decreases by roughly 1/3, due to mounting/insulation requirements and due to geometrically not matching component housings.

it is assumed that the switches of the full-bridge are mounted on a different heat sink than the output rectifier diodes. With  $T_j \leq 165^{\circ}$ C the heat sink temperature reaches a peak temperature of 160°C for the case  $A_{SiC} = A_{Si}$ , what requires a thermal isolation between the heat sink and the other components. Limiting the heat sink temperature to lower temperatures with a junction temperature of 165°C is not reasonable since this case only could be achieved by artificially deteriorating the thermal resistance between junction and heat sink.

The calculated peak power density of  $18 \text{kW/dm}^3$  also has to be considered against the background of the high heat sink temperature, because a thermal isolation is not included in the power density calculation, so that in the real system the power density might be lower.

For achieving the same efficiency with SiC devices app. 12% to 15% of the chip area is required for the SiC JFET. Due to the higher thermal resistance of the smaller SiC devices the high power density only could be achieved by increasing the junction and the heat sink temperature. With  $T_j = 140^{\circ}$ C the power density decreases from 15.4kW/dm<sup>3</sup> to 14.6kW/dm<sup>3</sup>.

The same power density could be achieved if the the SiC devices have 13% to 15% of the Si MOSFET chip area. There, with a lower junction temperature a bit a higher efficiency could be achieved with the SiC devices as the  $R_{DS(on)}$  increases with  $T_j$ .

#### Conclusion

Currently, SiC switching devices show very fast turn on/off transients (comparable to Si MOS-FETs) and low specific  $R_{DC,on}$ , which are significantly lower than the ones of unipolar Si devices. However, due to the relatively high output capacitance, the figure of merit  $1/R_{DS(on)}/E_{Out}$ , which is important for hard switching, is not better than the one of Si devices. This is confirmed by the efficiency optimisation results for a 1- $\Phi$  PFC converter, where some of the JFETs by SiCED are worse than the Si switches and only the JFETs by SemiSouth show an slight improvement from 99.09% to 99.14% efficiency. However, it is important to note, that the SiC freewheeling diodes offer an substantial improvement, as has been shown in various publications. It is also important to bare in mind, that the SiC devices are relatively young and will improve significantly in future. Furthermore, at higher operating voltage levels, there are no superjunction FETs and if a fast switching speed is required, SiC components show a significantly better performance than Si ones.

In the area of low voltage DC-DC converter, where very often soft switching conditions can be achieved with low effort, SiC devices mainly offer the possibility to reduce the chip area for a desired efficiency. This could help to increase the power density. Due the limited space in this publication, the results proofing this statement using the example of a non-isolated bidirectional buck boost converter must have been omitted but will be provided in an IEEE journal publication. There, also results for inverter drives are given.

For isolated DC-DC converter, for which a phase shift converter with current doubler rectifier has been evaluated in the paper, the main benefit is an improvement of power density and efficiency. There, however, the costs for the SiC devices play an important role, since these benefits often can be realised by significantly increasing the costs for the semiconductors. This might change in future if the prize of SiC devices drops.

Besides the semiconductors, in all the high performance systems, passive components, isolation issues and converter design also play an important role and are often the limiting devices. A good example are motor drives, where the dv/dt often must be reduced even with IGBTs, in order not to harm the isolation of the windings or to limit capacitive charging currents.

Besides SiC also other WBG materials as e.g. gallium nitride (GaN) show interesting properties and theoretically enable a tremendous reduction of the specific  $R_{DS(on)}$ , which has an even lower theoretical limit than SiC. Furthermore, the processing of the material is simpler and might allow a faster decrease of production costs than is possible with SiC.

## References

- [1] P. W. Research. [Online]. Available: http://www.ecn.purdue.edu/WBG/Index.html

- [2] D. Marckx, "Breakthrough in power electronics from SiC," National Renewable Energy Laboratory (NREL), Subcontract Report NREL/SR-500-38515, March 2006.

- [3] J. Kolar, J. Biela, and J. Miniboeck, "Exploring the pareto front of multi-objective single-phase pfc rectifier design optimization - 99.2% efficiency vs. 7kW/dm<sup>3</sup> power density," in *Plenary Publication* at the IEEE International Power Electronics and Motion Control Conference, May 2009.

- [4] B. Wrzecionko, J. Biela, and J. W. Kolar, "SiC power semiconductors in HEVs: Influence of junction temperature on power density, chip utilization and efficiency," in 35th Conference of the IEEE Industrial Electronics Society (IECON). Porto, Portugal, Nov. 2009.

- [5] U. Badstuebner, J. Biela, B. Faessler, D. Hoesli, and J. W. Kolar, "An optimized 5kW, 147 W/in<sup>3</sup> telecom phase-shift DC-DC converter with magnetically integrated current doubler," in *Proc. 24th IEEE Applied Power Electronics Conference and Exposition APEC*, 2009, pp. 21–27.

- [6] J. Biela, U. Badstuebner, and J. Kolar, "Impact of power density maximization on efficiency of DC-DC converter systems," *IEEE Transactions on Power Electronics*, vol. 24, pp. 288–300, 2009.