# EHzürich

# Research Collection

**Doctoral Thesis**

# 10 kV SiC-Based Medium-Voltage Solid-State Transformer Concepts for 400V DC Distribution Systems

Author(s): Rothmund, Daniel

Publication Date: 2018

Permanent Link: https://doi.org/10.3929/ethz-b-000331208 →

Rights / License: In Copyright - Non-Commercial Use Permitted →

This page was generated automatically upon download from the <u>ETH Zurich Research Collection</u>. For more information please consult the <u>Terms of use</u>.

### 10 kV SiC-Based Medium-Voltage Solid-State Transformer Concepts for 400 V DC Distribution Systems

A thesis submitted to attain the degree of

DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

> presented by DANIEL ROTHMUND

> > MSc ETH born on 20.01.1989 citizen of Germany

accepted on the recommendation of

Prof. Dr. Johann W. Kolar, examiner Prof. Dr. Hans-Peter Nee, co-examiner

ETH Zurich Power Electronic Systems Laboratory Physikstrasse 3 | ETL H23 8092 Zurich | Switzerland

http://www.pes.ee.ethz.ch

O 2018 by Daniel Rothmund

Printed in Switzerland

Für Claudia und meine Eltern

# Acknowledgments

**F**<sup>IRST</sup> of all, I would like to thank Prof. Dr. Johann W. Kolar for offering me a PhD position at the Power Electronic Systems Laboratory (PES) at ETH Zurich. Johann knew about my enthusiasm for high voltages and gave me the rare chance to work with 10 kV SiC devices in the field of SSTs. He was always highly interested in this work, and I am thankful for his valuable advice, the sharing of his extensive knowledge, and his trust in my work.

I would like to thank Prof. Dr. Hans-Peter Nee for his interest in my project and I sincerely appreciate that he found time to read my thesis and to be the co-examiner at my PhD defense.

Furthermore, I thank the Swiss National Science Foundation for enabling this project as part of the National Research Program 70. I would like to thank Prof. Nicola Schulz for the organization of the umbrella project and the meetings. Furthermore, I would like to thank all the involved researchers for the valuable discussions and their contributions.

I would also like to thank my supervisors Gabriel Ortiz, Florian Krismer, and Dominik Bortis for the valuable inputs, discussions, and the review of my work.

Furthermore, I would like to thank Oliver Knecht, Thomas Guillod and Pantelis Papamanolis as my office mates for the interesting discussions and the funny moments in the office. Especially Pantelis increased the amount of fun-time in the office and I would like to thank him for spreading his positive attitude. Special thanks belong to Thomas Guillod for sharing his scripts and his knowledge about medium-voltage insulation with me and for designing the MF MV transformer for the isolated DC/DC stage. I would especially like to thank him for his company and his valuable advice in the laboratory during the commissioning and testing of the SST. Furthermore, I want to thank him for the great time at various concerts, events, and recently at ECCE USA 2018 in Portland.

I would also like to thank Raphael Färber from the High-Voltage Laboratory at ETH Zurich for sharing his expertise in the field of MV insulation materials and also for sharing the equipment for applying the insulation on the magnetic components.

Special thanks belong to Jonas Huber, who supervised my MSc thesis and later in my time as a PhD student shared his knowledge, his scripts, and his experience in the field of SSTs. I would also like to thank him for the great experiences at various concerts and events. Further thanks go to the staff from the ITET workshop for manufacturing the mechanical parts of the SST in the highest precision and a perfect finishing: Martin Vogt, Daniel Wegmann, and Stefan Brassel.

I am grateful for the contributions of all of my students to this work and I would like to thank them for their engagement. Special thanks belong to Dominik Neumayr for his excellent results.

The great working environment at PES is to a large extent a result of the teamwork and the mutual support among the PES team members. Therefore, I would like to thank all of them for their contributions and their support: Jon Azurza, Julian Böhler, Piotr Czyz, Mattia Guacci, Christoph Gammeter, Arda Tüysüz, Hirofumi Uemura, Michael Haider, Morris Heller, Gustavo Knabben, David Menzi, Spasoje Miric, Pascal Niklaus, Jannik Schäfer, David Boillat, Roman Bosshard, Cédric Dittli, Eli Hanak, Michael Antivachis, Dominik Neumayr, Lukas Schrittwieser, Mario Mauerer, Matthias Kasper, Maurus Kaufmann, Michael Flankl, Michael Leibl, Pedro Bezerra, Ralph Burkart, Toke Andersen, and Yanick Lobsiger.

Moreover, I would like to thank the PES administration for enabling a smooth running of the scientific work: Monica Kohn, Roswitha Coccia, Prisca Maurantonio, Damaris Egger, Yvonne Schnyder-Liebherr, Beat Seiler, Peter Seitz, Peter Albrecht, Claudia Stucki, and Marina Eisenstat.

Finally, I would like to express my highest gratitude to my parents Anna and Alfred, who enabled my studies and always supported me in any phase of my life. I would also like to thank my brothers Armin and Jürgen for their help and encouragement, and I thank my girlfriend Claudia for her unconditional love and support during this intense time in my life. Without all of you, this work would not have been possible.

> Zurich, October 2018 Daniel Rothmund

## Abstract

$\mathbf{A}^{\mathrm{T}\ \mathrm{THE}}$  present time, the globalization and the digital revolution are the main drivers of the global economic growth, which, however, goes hand in hand with a significant increase of the world's energy consumption. To reduce the emission of greenhouse gases despite the rising energy demand, there are clear trends towards an increasing share of electric vehicles (EVs) on the automotive market and towards the integration of more renewable energy into the utility grid. Power electronics is one of the main enabling technologies for this fundamental change, since the distribution of the electrical power is taking place at medium-voltage (MV)-AC, whereas EV batteries or e.g. data centers (on the load-side) and photovoltaic (PV) power plants as well as wind turbines (on the generation-side) represent low-voltage (LV)-DC loads or sources, which means that MV-AC to LV-DC interfaces are required. The state-of-the-art solution for such MV-AC to LV-DC interfaces are low-frequency transformers (LFTs) with subsequent (bidirectional) AC/DC converters. There, the LFT provides the required voltage transfer ratio and galvanic isolation.

For a further reduction of greenhouse gas emissions, the available electrical energy should be utilized to the highest possible extent, i.e. the energy efficiency of the entire power supply chain from the generationside to the load-side has to be increased. In this context, Solid-State Transformers (SSTs), i.e. power electronic converters with an MV connection and galvanic isolation by means of a medium-frequency (MF) transformer, are a highly attractive alternative for the realization of MV-AC to LV-DC interfaces due to their higher efficiency, high power density, and their additional control features compared to the state-of-the-art solution.

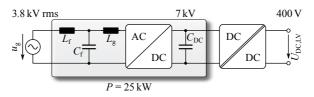

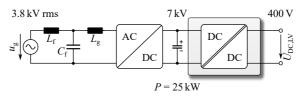

One group of high-power LV-DC loads are e.g. data centers, whose energy demand will increase significantly in the near future due to the exploding internet IP traffic. In data centers, the benefit of utilizing SSTs is even higher than for other applications, since their traditional power supply chain consists of several cascaded conversion stages with a low total efficiency, which can be omitted by the use of MV-AC to 400 V DC SSTs. There, it is intended to supply individual server racks, which can reach power levels in the range of  $20 \dots 40 \text{ kW}$ , with separate SSTs with the additional advantage of substantially lower cable cross sections and/or lower losses compared to LV distribution. Therefore, a highly efficient 25 kW, 3.8 kV single-phase AC to 400 V DC SST with a target efficiency of  $98\,\%$  is realized and experimentally verified in this thesis.

Instead of interfacing the MV-AC grid with a cascaded multi-cell AC/DC converter, which consists of several series-connected converter cells employing e.g. 1200...1700 V semiconductors, a single-cell approach based on the latest generation of 10 kV SiC MOSFETs is selected due to the significantly lower complexity and the higher resulting power density. There, a bidirectional single-cell AC/DC converter faces the MV-AC grid, whereas a subsequent isolated single-cell DC/DC stage converts the intermediate DC-link voltage of 7 kV into 400 V DC. To utilize the full potential of these 10 kV SiC MOSFETs, in this work a complete technology package containing all the required concepts and circuits necessary to realize a highly efficient, highly compact, and reliable 10 kV SiC MOSFET-based MV-AC to LV-DC SST is developed.

To enable an integration of the isolated gate driver into future intelligent MV SiC modules, which would enhance the switching behavior and would significantly simplify the design of MV converters, the volume of the isolated gate driver supply has to be decreased substantially compared to state-of-the-art solutions. Therefore, a highly compact gate driver isolation transformer with a coupling capacitance of only 2.6 pF is realized. Furthermore, the gate driver features an ultra-fast overcurrent protection with a reaction time of only 22 ns and the capability of clearing hard-switching faults and even flashover faults within less than 200 ns at a DC-link voltage of 7 kV.

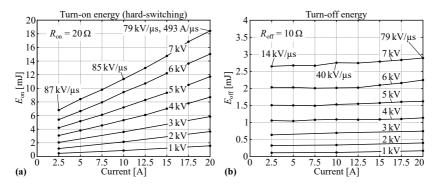

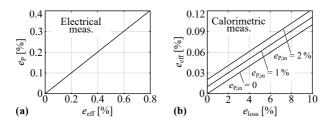

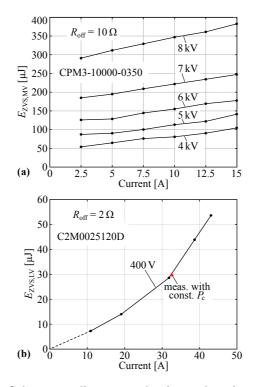

Since there has not been any switching loss data available for the employed 10 kV SiC MOSFETs (especially in the case of soft-switching), these losses have to be determined experimentally. However, an error analysis shows that electrical soft-switching loss measurements can lead to large errors and therefore these measurement methods are unsuitable. To obtain reliable data for the switching losses, a highly accurate calorimetric soft-switching loss measurement method is developed and the results show that, compared to hard-switching, the soft-switching losses are a factor of 30 lower.

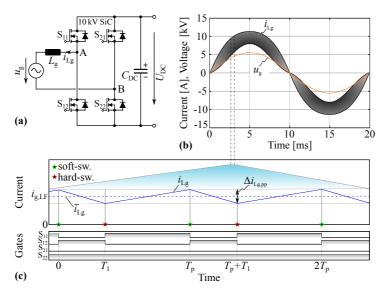

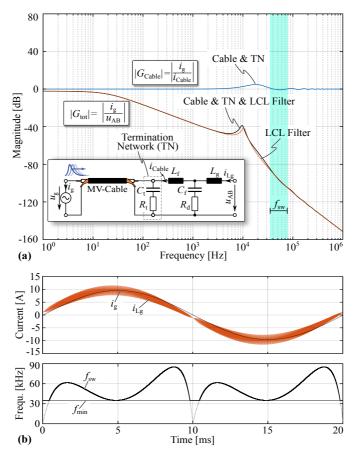

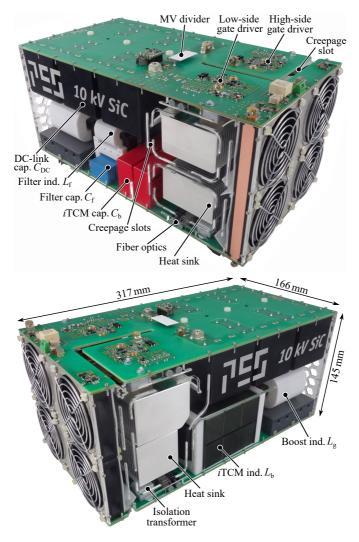

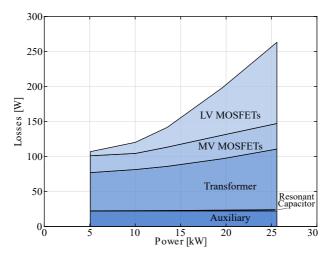

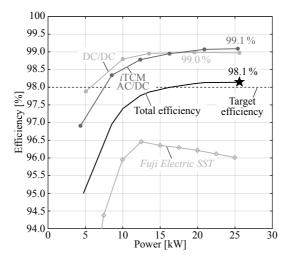

For this reason, the goal is to operate all switches under soft-switching conditions, since this allows for a high efficiency and enables the downsizing of passive components by employing a high switching frequency. Therefore, a novel bidirectional AC/DC converter topology is developed, which enables soft-switching over the entire AC grid period by adding a simple LC-branch to the well-known full-bridge AC/DC converter, which internally superimposes a high triangular current on the AC grid current to reverse the current direction in each switching cycle. Hence, this concept is called *integrated* Triangular Current Mode (*i*TCM) operation. Furthermore, the design of the required ACside LCL filter is discussed in detail and a quasi lossless method to eliminate current oscillations in MV cables independently of the cable length is presented. Based on a theoretical analysis, which shows that it is very important in case of MV converters of this power class to minimize parasitic capacitances, a low-capacitive design of the magnetic components and the PCB layout is realized. Highly accurate calorimetric efficiency measurements show that the *i*TCM single-phase AC/DC converter achieves a full-load efficiency of 99.1 %, while it features an unprecedented power density of  $3.28 \,\mathrm{kW/L}$ .

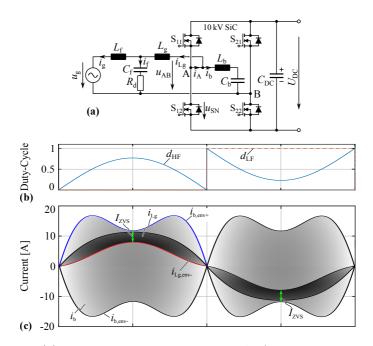

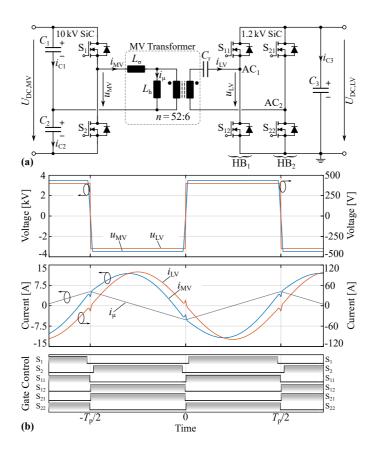

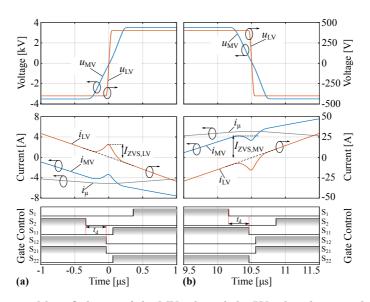

For the subsequent isolated DC/DC back end of the SST, an LLC series resonant converter topology is selected and operated at resonance frequency as "DC transformer" providing a tight coupling of the converter's input and output voltages. In order to achieve soft-switching of all switches under all load conditions and especially for both power flow directions, a special modulation scheme is developed which allows the active sharing of the turn-off current among the MV-side and the LV-side. Furthermore, the MF MV transformer is Pareto-optimized regarding its efficiency and power density and special attention is paid to its MV insulation and the selection and application of a proper insulation material. Calorimetric efficiency measurements show that the isolated DC/DC converter achieves an efficiency of 99.0 % between 50 % rated power and full load, while it features a power density of 3.8 kW/L.

Therefore, the complete MV-AC to LV-DC SST system achieves a full-load efficiency of 98.1 % and a power density of 1.76 kW/L. Compared to an SST with similar specifications presented in 2017 by *Fuji Electric*, which achieves an efficiency of 96% and a power density of 0.4 kW/L, the SST realized in this work generates less than half the losses and is more than four times smaller.

# Kurzfassung

IE heutige Zeit ist massgeblich von der Globalisierung und der digitalen Revolution als stärkste treibende Kräfte für das globale wirtschaftliche Wachstum geprägt, das jedoch mit einer deutlichen Zunahme des weltweiten Energieverbrauchs einhergeht. Um die Emission von Treibhausgasen trotz des steigenden Energiebedarfs zu reduzieren, zeichnen sich klare Trends hin zu einem grösseren Marktanteil von Elektrofahrzeugen (electric vehicles, EV) und zu einer zunehmenden Integration von erneuerbaren Energien in das Energienetz ab. Eine der Schlüsseltechnologien, die diese fundamentale Umstellung ermöglichen, ist die Leistungselektronik, da die Verteilung der elektrischen Energie auf der AC-Mittelspannungsebene (medium-voltage, MV) erfolgt, während sowohl EV Akkus und Datencenter als auch Photovoltaik (PV)-Kraftwerke und Windkraftanlagen Niederspannungs- (low-voltage, LV)-DC-Verbraucher bzw. -Quellen darstellen, weshalb MV-AC zu LV-DC Interfaces zwingend erforderlich sind. Die Standardlösung für derartige Interfaces sind Niederfrequenztransformatoren mit nachgeschalteten (bidirektionalen) AC/DC Konvertern. Dabei stellt der Niederfrequenztransformator die notwendige Spannungsübersetzung und die galvanische Trennung bereit.

Zur Minimierung der Treibhausgasemissionen sollte die vorhandene elektrische Energie so effizient wie möglich genutzt werden, d.h. die Effizienz der gesamten Energieversorgungskette von der Erzeugung bis hin zum Verbraucher muss einen möglichst hohen Wert aufweisen. In diesem Zusammenhang sind Solid-State Transformatoren (SST), d.h. leistungselektronische Konverter mit einem Mittelspannungsanschluss und mittelfrequenter Potentialtrennung aufgrund ihrer höheren Effizienz und Leistungsdichte sowie der zusätzlichen Regelbarkeit eine attraktive Option für die Realisierung von MV-AC zu LV-DC Interfaces, alternativ zu Standardlösungen.

Eine Kategorie von Hochleistungs-LV-DC-Verbrauchern sind z.B. Datencenter, deren Energiebedarf in naher Zukunft aufgrund des rasanten Anstiegs des Datenverkehrs im Internet signifikant zunehmen wird. In Datencentern ist der Einsatz von SSTs noch vorteilhafter als in anderen Applikationen, da die traditionelle Energieversorgungskette aus mehreren kaskadierten Konverterstufen mit entsprechend niedriger Gesamteffizienz besteht, die durch den Einsatz von MV-AC zu 400 V DC SSTs jedoch vermieden werden können. Dabei ist die Energieversorgung einzelner Server-Racks, die einen Leistungsbedarf im Bereich von 20...40 kW aufweisen, durch individuelle SSTs vorstellbar, was den Vorteil von deutlich kleineren Kabelquerschnitten und/oder kleineren Verlusten gegenüber einer LV-Energieverteilung mit sich bringt. Aus diesem Grund wird in dieser Arbeit ein 25 kW, 3.8 kV Einphasen-AC zu 400 V DC SST mit einer Zieleffizienz von 98 % realisiert und experimentell verifiziert.

Anstatt das Mittelspannungsnetz über einen kaskadierten Multizellen-AC/DC-Konverter anzukoppeln, der aus mehreren in Serie geschalteten Konverterzellen auf Basis von z.B. 1200...1700 V Halbleitern besteht, wird aufgrund geringerer Komplexität und der daraus resultierenden höheren Leistungsdichte eine Einzellen-Topologie basierend auf der neuesten Generation von 10 kV SiC MOSFETs ausgewählt. Dabei wird ein Einzellen-AC/DC-Konverter an das MV-AC Netz angekoppelt, wobei eine nachfolgende isolierte Einzellen-DC/DC-Stufe die Zwischenkreisspannung von 7 kV in 400 V DC umsetzt. Um das volle Potential dieser Lösung auszuschöpfen, wird ein umfängliches Technologiepaket entwickelt, welches alle erforderlichen Konzepte und Schaltungen enthält, die zur Realisierung eines hocheffizienten, hochkompakten und zuverlässigen 10 kV SiC MOSFET-basierten MV-AC zu LV-DC SSTs benötigt werden.

Um eine Integration des isolierten Gatetreibers in ein zukünftiges intelligentes HV SiC Modul zu ermöglichen, was zu einer Verbesserung des Schaltverhaltens und zu einer deutlichen Vereinfachung des Designprozesses von MV-Konvertern führen würde, muss das Volumen der isolierten Gatetreiber-Spannungsversorgung im Vergleich zu bisherigen Lösungen deutlich reduziert werden. Deshalb wird ein hochkompakter Gatetreiber-Isolationstransformator mit einer Koppelkapazität von nur 2.6 pF realisiert. Des Weiteren verfügt der Gatetreiber über eine ultraschnelle Überstromabschaltung mit einer Reaktionszeit von nur 22 ns, die in der Lage ist, Brückenkurzschlüsse und sogar Kurzschlüsse aufgrund eines Funkenüberschlags bei einer Zwischenkreisspannung von 7 kV innerhalb von weniger als 200 ns sicher abzuschalten.

Seitens des Herstellers werden für 10 kV SiC MOSFETs (insbesondere für weiches Schalten) keine Schaltverlustdaten zur Verfügung gestellt; entsprechend müssen diese Verluste experimentell bestimmt werden. Durch eine Fehleranalyse wird allerdings deutlich, dass elektrische Schaltverlustmessungen für weiches Schalten mit sehr hohen Fehlern behaftet und deshalb ungeeignet sind. Um verlässliche Daten zu erhalten, wird ein hochgenaues kalorimetrisches Schaltverlust-Messverfahren entwickelt, wobei die Resultate zeigen, dass die Schaltverluste bei weichem Schalten um einen Faktor 30 geringer sind als bei hartem Schalten.

Aus diesem Grund ist es das Ziel, alle Schalter weich schaltend zu betreiben, da dies eine höhere Effizienz und eine Volumenreduktion der passiven Komponenten durch die Wahl einer höheren Schaltfrequenz ermöglicht. Dazu wird eine neuartige bidirektionale AC/DC Konvertertopologie entwickelt, die weiches Schalten während der kompletten Netzperiode ermöglicht, indem die bekannte Vollbrücken-AC/DC-Konvertertopologie mit einem einfachen LC-Netzwerk erweitert wird, das brückenintern einen hohen Stromrippel auf den Netzstrom aufprägt, um dadurch die Stromrichtung in jeder Schaltperiode umzukehren bzw. für den jeweils abschaltenden Transistor einen positiven Strom sicherzustellen. Dieses Konzept wird daher als integrated Triangular Current Mode (*i*TCM) Betrieb bezeichnet. Weiterhin wird die Auslegung des AC-seitig benötigten LCL-Filters detailliert diskutiert und es wird eine quasi verlustlose Methode zur Eliminierung von Stromoszillationen in der Mittelspannungszuleitung unabhängig von deren Länge aufgezeigt. Basierend auf einer theoretischen Analyse die verdeutlicht, dass es für Mittelspannungskonverter dieser Leistungsklasse von hoher Wichtigkeit ist parasitäre Kapazitäten zu minimieren, wird ein niederkapazitives Design der magnetischen Komponenten und des PCB Lavouts realisiert. Mithilfe hochgenauer kalorimetrischer Effizienzmessungen wird gezeigt, dass der *i*TCM AC/DC Konverter eine Volllasteffizienz von  $99.1\,\%$  erreicht, wobei zu beachten ist, dass das System eine für Mittelspannungs-Einphasen-AC/DC-Konverter bisher unerreichte Leistungsdichte von 3.28 kW/L aufweist.

Als Konvertertopologie für den nachgeschalteten isolierten DC/DC Konverter wird ein LLC Serienresonanzkonverter gewählt, der bei Resonanzfrequenz betrieben wird, womit eine starre Kopplung der Eingangsund Ausgangsspannung bzw. letztlich ein "DC Transformator" resultiert. Um weiches Schalten für alle Schalter über den kompletten Lastbereich und im Speziellen für beide Energieflussrichtungen zu erreichen, wird ein spezielles Modulationsschema entwickelt, welches eine aktive Aufteilung des Abschaltstroms zwischen der MV- und der LV-Seite erlaubt. Des Weiteren erfolgt eine Pareto-Optimierung des Transformators hinsichtlich Effizienz und Leistungsdichte. Spezielle Beachtung kommt der MV Isolation des Transformators und der Auswahl sowie der Anwendung eines geeigneten Isolationsmaterials zu. Kalorimetrische Effizienzmessungen zeigen, dass der isolierte DC/DC Konverter zwischen  $50\,\%$ Nennlast und Volllast eine Effizienz von  $99.0\,\%$ erreicht, während er eine Leistungsdichte von  $3.8\,\rm kW/L$ aufweist.

Das komplette MV-AC zu LV-DC SST System erreicht damit eine Volllasteffizienz von 98.1 % und weist eine Leistungsdichte von 1.76 kW/L auf. Im Vergleich zu einem SST mit ähnlichen Spezifikationen, der 2017 von *Fuji Electric* vorgestellt wurde und eine Effizienz von 96 % sowie eine Leistungsdichte von  $0.4\,\rm kW/L$  erreicht, generiert das in dieser Arbeit realisierte SST System weniger als die halben Verluste und weist weniger als ein Viertel des Bauvolumens auf.

# Abbreviations

| 3D Three-Dimensional                            |         |

|-------------------------------------------------|---------|

| AC Alternating Current                          |         |

| BESS Battery Energy Storage System              |         |

| BEV Battery Electric Vehicle                    |         |

| CAD Computer Aided Design                       |         |

| CL Conduction Losses                            |         |

| CM Common Mode                                  |         |

| DAB Dual Active Bridge                          |         |

| DC Direct Current                               |         |

| DM Differential Mode                            |         |

| DOI Digital Object Identifier                   |         |

| DSP Digital Signal Processor                    |         |

| DUT Device Under Test                           |         |

| ESR Equivalent Series Resistance                |         |

| EV Electric Vehicle                             |         |

| FEM Finite Element Method                       |         |

| FFT Fast Fourier Transform                      |         |

| FOF Flashover Fault                             |         |

| FPGA Field Programmable Gate Array              |         |

| FUL Fault Under Load                            |         |

| GDT Gas Discharge Tube                          |         |

| HF High-Frequency                               |         |

| HSF Hard-Switching Fault                        |         |

| HSL Hard-Switching Losses                       |         |

| HV High-Voltage                                 |         |

| IBE Isolated Back-End                           |         |

| IEEE Institute of Electrical and Electronics En | gineers |

| IFE Isolated Front-End                          |         |

| IGBT Insulated-Gate Bipolar Transistor          |         |

| IPT Inductive Power Transfer                    |         |

| ISOP Input-Series Output-Parallel               |         |

| IT Information Technology                       |         |

| LF Low-Frequency                                |         |

| LFT Low-Frequency Transformer                   |         |

| MF Medium-Frequency                             |         |

| MMLC Modular Multilevel Converter               |         |

| MOSFET               | Metal-Oxide Semiconductor Field-Effect |

|----------------------|----------------------------------------|

|                      | Transistor                             |

| MV                   | Medium-Voltage                         |

| OCP                  | Overcurrent Protection                 |

| PC                   | Personal Computer                      |

| PCB                  | Printed Circuit Board                  |

| PFC                  | Power Factor Correction                |

| PHEV                 | Plug-in Hybrid Electric Vehicle        |

| PI                   | Proportional-Integral                  |

| PV                   | Photovoltaic                           |

| PWM                  | Pulse-Width Modulation                 |

| Si                   | Silicon                                |

| $\operatorname{SiC}$ | Silicon Carbide                        |

| $\operatorname{SL}$  | Switching Losses                       |

| SRC                  | Series Resonant Converter              |

| SSL                  | Soft-Switching Losses                  |

| SST                  | Solid-State Transformer                |

| UPS                  | Uninterruptible Power Supply           |

| ZCS                  | Zero Current Switching                 |

| ZVS                  | Zero Voltage Switching                 |

# Contents

| A        | bstra | $\mathbf{ct}$                                            | vii                    |

|----------|-------|----------------------------------------------------------|------------------------|

| K        | urzfa | ssung                                                    | xi                     |

| A        | bbre  | viations                                                 | $\mathbf{x}\mathbf{v}$ |

| 1        | Intr  | oduction                                                 | 1                      |

|          | 1.1   | Solid-State Transformer Characteristics and Applications | 3                      |

|          | 1.2   | SSTs for Data Center Power Supplies                      | 4                      |

|          | 1.3   | System Specifications                                    | 6                      |

|          | 1.4   | SST Key Challenges                                       | 7                      |

|          |       | 1.4.1 Interfacing of the MV Grid                         | 7                      |

|          |       | 1.4.2 Medium-Voltage Insulation                          | 7                      |

|          |       | 1.4.3 Efficiency, Power Density, and Cost                | 8                      |

|          |       | 1.4.4 Reliability $\ldots$                               | 8                      |

|          | 1.5   | Suitable MV-AC to LV-DC SST Topologies                   | 9                      |

|          |       | 1.5.1 Isolated Back End SSTs                             | 9                      |

|          |       | 1.5.2 Isolated Front End SSTs                            | 10                     |

|          |       | 1.5.3 Modular Multilevel Converter-Based SSTs            | 11                     |

|          |       | 1.5.4 Single-Cell IBE SSTs Using MV SiC Devices          | 12                     |

|          | 1.6   | Previous Work                                            | 13                     |

|          | 1.7   | Aims and Contributions                                   | 14                     |

|          | 1.8   | Outline of the Thesis                                    | 18                     |

|          | 1.9   | List of Publications                                     | 20                     |

| Li       | st of | Publications                                             | 20                     |

| <b>2</b> | Hig   | hly Compact Isolated Gate Driver                         | <b>23</b>              |

|          | 2.1   | Introduction                                             | 24                     |

|          | 2.2   | Isolated Power Supply                                    | 28                     |

|          |       | 2.2.1 Isolated Power Supply Topology                     | 29                     |

|          |       | 2.2.2 Isolation Transformer                              | 31                     |

|          |       | 2.2.3 Experimental Verification of the Isolated          |                        |

|          |       | Power Supply                                             | 41                     |

|          | 2.3   | Ultra-Fast Overcurrent Protection                        | 43                     |

|          |       | 2.3.1 Functional Principle of the OCP                    | 44                     |

|          |       | 2.3.2 Flashover Fault Simulation                         | 47                     |

|          | 0.4   | 2.3.3 Experimental Results                               | 50                     |

|          | 2.4   | Summary                                                  | 53                     |

| 3 |                |        | ric Measurement of 10 kV SiC Soft-Switching       |     |

|---|----------------|--------|---------------------------------------------------|-----|

|   | $\mathbf{Los}$ |        |                                                   | 55  |

|   | 3.1            |        | luction                                           | 56  |

|   | 3.2            |        | ng SL Measurement Methods                         | 58  |

|   |                | 3.2.1  | Electrical Measurement Methods                    | 58  |

|   |                | 3.2.2  | Error Analysis for Electrical SSL Measurement     |     |

|   |                |        | Methods                                           | 61  |

|   |                | 3.2.3  | Calorimetric SL Measurement Methods               | 69  |

|   | 3.3            |        | ional Principle of the Proposed SSL Measurement   | -   |

|   | ~ .            |        | od                                                | 70  |

|   | 3.4            |        | ssion and Experimental Results                    | 77  |

|   |                | 3.4.1  | Error Analysis for the Proposed SSL Measure-      |     |

|   |                |        | ment Method                                       | 77  |

|   |                | 3.4.2  | Measurement Results                               | 82  |

|   | 3.5            |        | it Capacitance Charging and Discharging Losses .  | 84  |

|   |                | 3.5.1  | Description of the Charging/Discharging Loss Mea- | ~ ( |

|   |                |        | surement Method                                   | 84  |

|   | ~ ~            | 3.5.2  | Measurement Results                               | 88  |

|   | 3.6            | -      | arison of SSL and HSL                             | 92  |

|   | 3.7            | Summ   | nary                                              | 93  |

| 4 | 10 k           | V SiC  | -Based ZVS PFC Single-Phase AC/DC Stage           | 95  |

|   | 4.1            | Introd | luction                                           | 96  |

|   | 4.2            | Integr | ated Triangular Current Mode $(iTCM)$ Concept .   | 100 |

|   |                | 4.2.1  | State-of-the-Art PWM AC/DC Converter Oper-        |     |

|   |                |        | ation                                             | 100 |

|   |                | 4.2.2  | Derivation of the $i$ TCM Topology                | 103 |

|   |                | 4.2.3  | iTCM Modulation                                   | 106 |

|   | 4.3            | Syster | n Design                                          | 111 |

|   |                | 4.3.1  | General HV-SiC-Based Converter Design Consid-     |     |

|   |                |        | erations                                          | 111 |

|   |                | 4.3.2  | Inductor Design                                   | 116 |

|   |                | 4.3.3  | Dimensioning of the Capacitor $C_{\rm b}$         | 123 |

|   |                | 4.3.4  | DC-Link                                           | 124 |

|   |                | 4.3.5  | Semiconductors                                    | 125 |

|   |                | 4.3.6  | LCL Input Filter Design                           | 126 |

|   |                | 4.3.7  | Connection to the MV Grid                         | 128 |

|   |                | 4.3.8  | <i>i</i> TCM Hardware Prototype                   | 132 |

|   | 4.4            | Exper  | imental Setup                                     | 134 |

|          |       | 4.4.1 Electrical Efficiency Measurement                                                                                                                         |    |

|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          |       |                                                                                                                                                                 | 35 |

|          |       | 4.4.2 Calorimetric Efficiency Measurement 13                                                                                                                    | 36 |

|          | 4.5   |                                                                                                                                                                 | 42 |

|          | 4.6   |                                                                                                                                                                 | 44 |

|          |       | 4.6.1 Measured Waveforms $\ldots \ldots \ldots$ | 44 |

|          |       | 4.6.2 Efficiency Measurements                                                                                                                                   | 46 |

|          | 4.7   | Summary                                                                                                                                                         | 49 |

| <b>5</b> | 10 k  | V SiC-Based Isolated Bidirectional $7\mathrm{kV}/400\mathrm{V}\mathrm{DC}/\mathrm{D0}$                                                                          | С  |

|          |       |                                                                                                                                                                 | 51 |

|          | 5.1   | Introduction                                                                                                                                                    | 52 |

|          | 5.2   | Topology and Modulation                                                                                                                                         | 54 |

|          |       | 5.2.1 Modulation Scheme of the SRC                                                                                                                              | 54 |

|          | 5.3   | System Design 1                                                                                                                                                 | 57 |

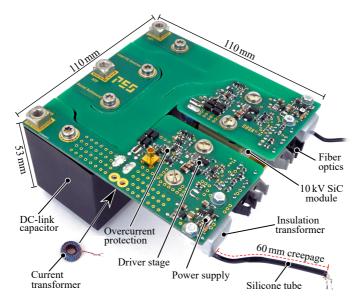

|          |       | 5.3.1 MV-Side 10 kV SiC MOSFET Half-Bridge 18                                                                                                                   | 57 |

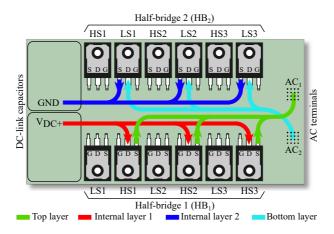

|          |       | 5.3.2 LV-Side 1200 V SiC MOSFET Full-Bridge 10                                                                                                                  | 61 |

|          |       | 5.3.3 Resonance Capacitor                                                                                                                                       | 65 |

|          |       | 5.3.4 MF MV Transformer                                                                                                                                         | 66 |

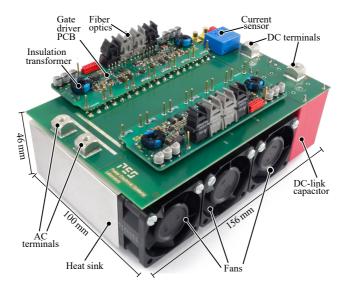

|          | 5.4   | Experimental Setup and Results 1'                                                                                                                               | 78 |

|          |       | 5.4.1 Measured Waveforms 1'                                                                                                                                     | 79 |

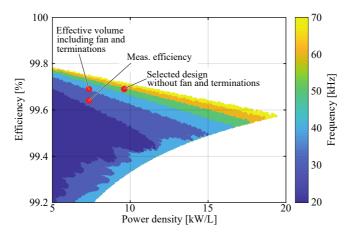

|          |       | 5.4.2 Efficiency Measurements                                                                                                                                   | 81 |

|          | 5.5   | Summary                                                                                                                                                         | 84 |

| 6        | Con   |                                                                                                                                                                 | 87 |

|          | 6.1   | Results and Conclusions                                                                                                                                         | 88 |

|          | 6.2   | Future Research Areas                                                                                                                                           | 92 |

| Bi       | bliog | raphy 19                                                                                                                                                        | 95 |

| Cι       | irric | llum Vitae 22                                                                                                                                                   | 25 |

# Introduction

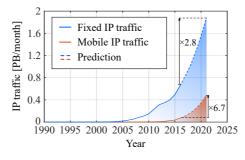

$\mathbf{T}^{\text{ODAY's}}$  society and its future development is substantially influenced by the digital revolution and the globalization, which are two of the main drivers for economic growth. This is e.g. reflected in the exploding internet IP traffic, which will triple between 2016 and 2021 (cf. **Fig. 1.1**) whereby the vast amount of data has to be processed in highly energy-demanding data centers; furthermore, passenger and freight transportation on the ground, on the sea, and in the air is rapidly increasing. Due to the tremendous energy consumption, this growth is mainly happening at the expense of the environment. The conspicuous consequences of the resulting climate change, such as the rise of the CO<sub>2</sub> concentration, the global warming, and the rise of the sea level [1], have led to an increasing environmental awareness of society and politics.

To mitigate the effects of the climate change, e.g. in 2010 the European Commission defined the *Europe 2020* strategy [2], which states that by 2020 the greenhouse gas emissions should be reduced by 20...30 % compared to 1990, and the United Nations Climate Change Conference 2015 developed the *Paris Agreement*, whose main goal is to limit the long-term global average temperature increase to well below  $2 \,^{\circ}$ C compared to pre-industrial levels [3].

To achieve these goals, a significant decarbonisation of the transportation sector and the electricity generation sector, as well as a substantial increase in energy efficiency are necessary. Therefore, the consumption of fossil fuels has to be reduced, e.g. by the electrification of passenger cars and freight trucks, i.e. by utilizing so-called electric vehicles (EV), as well as the public transport sector. At the same time, the energy required by EVs and other large-scale consumers such as data centers has to be delivered from renewable sources, for instance

Fig. 1.1: Global internet IP traffic for fixed devices (computers) and mobile devices. Data originates from the Cisco Visual Networking Index [5] and [6].

wind power, solar power, and hydro power in order to reduce the environmental footprint sustainably. One example is the *Lefdal Mine Data Center* in Norway. Its energy consumption is growing from the current 10 MW to 200 MW over the next three years [4], but it is entirely powered from renewable sources.

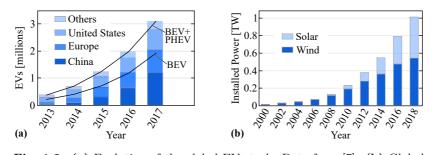

Representative indicators to demonstrate the current development towards a more environmental-friendly energy policy are e.g. the global number of EVs and the installed renewable power generation capacity. **Fig. 1.2(a)** shows the evolution of the global number of EVs between 2013 and 2017 and as can be seen, the total number of EVs (battery electric vehicles (BEV) and plug-in hybrid electric vehicles (PHEV)) has significantly increased by almost a factor of 10 during this period. Furthermore, **Fig. 1.2(b)** shows the installed wind power and photovoltaic (PV) power generation capacity between 2000 and 2018, which has grown more than fivefold in the last 10 years.

One of the key technologies enabling this fundamental change in the power flow chain between the renewable energy sources and the consumers is power electronics, since e.g. EV batteries and data centers are low-voltage (LV) DC-loads, whereas the typical distribution grids are medium-voltage (MV)-AC grids, i.e. an MV-AC to LV-DC conversion is necessary for interfacing high-power DC-loads to the utility grid. On the generation side, if wind power and PV power is considered, another LV-DC to MV-AC conversion is required, since more and more modern wind-generators are incorporating variable speed drives [9–12] and hence, besides the PV panels, also represent DC-sources seen from their rectifier's DC-link.

Fig. 1.2: (a) Evolution of the global EV stock. Data from [7]. (b) Global installed PV power and wind power generation capacity. Data from [8].

To interface an MV-AC grid to an LV-AC grid, usually low-frequency transformers (LFTs), which provide galvanic isolation and the required voltage transfer ratio between the primary-side and the secondary-side, are employed. In case an MV-AC to LV-DC conversion is required, a power electronic AC/DC conversion stage is added on the LV-side of the LFT, as shown in [13] for wind turbines, in [14] for PV power plants, in [15] for EV high-power battery charging, and in [16] for data centers.

#### 1.1 Solid-State Transformer Characteristics and Applications

As a widely discussed alternative to LFTs, Solid-State Transformers (SSTs) could be used to interface an MV grid to an LV grid. There, the term SST (also referred to as Smart Transformer [17], Electronic Transformer [18], Intelligent Universal Transformer [19], Energy Router [20], or Energy Control Center [21]) represents a class of power electronic converters with medium-frequency (MF) galvanic isolation operating between an arbitrary MV grid and an arbitrary LV grid [22–25]. However, in contrast to LFTs, SSTs can not only operate between two AC grids [18, 19, 26–28], but can also directly interface DC grids either on the MV-side [29, 30], the LV-side [31–33], or on both sides [34–39].

The benefits of SSTs are mainly the controllability, i.e. reactive power compensation, fault handling, grid monitoring, and energy routing, as well as a potential increase in power density and efficiency compared to LFT-based solutions. However, it has been shown in [40] that typical SSTs perform worse than LFTs in AC/AC operation, but outperform the standard solution (LFT + AC/DC converter) in terms of lower weight, lower volume and lower losses when it comes to MV-AC to LV-DC conversions. Therefore, SSTs are especially well suited for the following applications:

- ▶ Data center power supplies [33, 41–43];

- ▶ MV-connected high-power EV battery charging [15, 32, 44–46];

- Integration of PV power plants into the MV-AC distribution grid [47–52];

- Connection of wind turbines to the MV-AC distribution grid [53– 55];

- Integration of battery energy storage systems (BESS) into the MV-AC grid [13, 15, 48, 56];

- ▶ Traction applications [31, 57, 58];

- ▶ DC collection grids for large-scale renewable power plants [37,39, 59–62];

- Integration of power-to-gas facilities for hydrogen generation into the MV-AC grid [63–65]

#### **1.2** SSTs for Data Center Power Supplies

It is estimated that the information and communication technology (ICT) sector currently consumes 10% of the world's generated electric energy [66] and e.g. in 2014, the 14 million installed servers in the U.S. consumed 1.8% of the national electricity generation [67]. Furthermore, it is reported that 12...27% of the energy provided to data centers at MV level is dissipated in the power conversion stages which convert the voltage from several kilovolts down to the chip voltage level [42, 68, 69]. For economical and ecological reasons and due to the strongly increasing internet IP traffic (cf. **Fig. 1.1**) with the resulting demand for more computing power and hence for more electrical energy, the interest of research institutions and industry on more efficient data center power supplies has grown rapidly over the past decade.

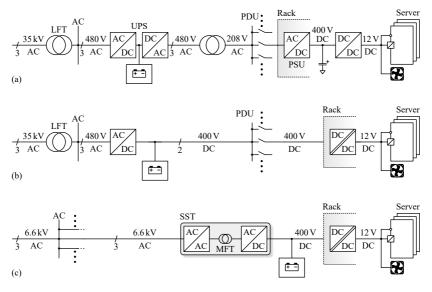

Fig. 1.3(a) shows the traditional power supply chain in a data center from the MV-AC grid to the 12 V supply for the servers. An

Fig. 1.3: (a) Traditional data center power supply chain from MV-AC to the 12 V DC server supply voltage. (b) Power supply chain based on 400 V DC distribution for a reduced complexity and increased efficiency. (c) SST-based power supply chain which allows to omit the LFT for an even higher efficiency and power density. The figures are taken from [70] and have been slightly modified.

LFT provides the galvanic isolation from the MV grid and transforms the voltage down to 480 V AC from where an uninterruptible power supply (UPS) with its backup batteries feeds another LFT, which is part of the power distribution unit (PDU), stepping down the voltage to 208 V, since the subsequent conversion stages are only rated for an input voltage range of 90...264 V [70]. The PDU then feeds the individual server racks, which contain a PFC rectifier and a 400 V/12 V DC/DC converter. As can be noted, there are several cascaded conversion stages, i.e. the total efficiency decreases with each conversion stage and hence is relatively low.

In order to increase the efficiency and to reduce the complexity (and therewith the probability of failure) of the power supply chain of data centers, a shift to 380/400 V DC distribution systems is considered [16,69] and is partly already implemented [71]. Fig. 1.3(b) shows

the block diagram of a 400 V DC distribution-based data center power supply and as can be seen, the UPS, one LFT, and the rack-internal PFC rectifier can be omitted, whereby the backup batteries are now connected to the 400 V DC bus. Consequently, according to [72], an efficiency improvement of 7% can be expected compared to the traditional power supply chain.

As a further step, SSTs are considered to provide a direct power electronic interface from the MV-AC grid to the 400 V DC bus, in order to improve the efficiency and the power density also of this part of the conversion chain [33,41,42]. There, the power supply of each server rack (which can reach power demands in the range of  $20 \dots 40 \, \text{kW}$  [68,73,74]) with a separate SST is intended. Fig. 1.3(c) shows the SST-based data center power supply chain, where the SST replaces the bulky LFT and the rectifier by directly interfacing the MV-AC grid. With this concept, the power could be distributed on MV level (e.g. 6.6 kV phase-to-phase rms, i.e. 3.8 kV rms phase-to-neutral) in the data center with the advantage of substantially lower realization efforts and/or cable cross sections and lower ohmic losses compared to LV distribution. Individual singlephase SSTs (single-phase for a low complexity) could then convert the MV-AC into 400 V DC and feed individual server racks or clusters, whereby the three phases of the MV utility grid could be symmetrically loaded. For a cost-effective construction of the building, it would be important that the SSTs are compact and lightweight. Additionally, the SSTs should allow a bidirectional energy flow, e.g. to feed energy from the 400 V DC bus back into the AC grid in case PV power is integrated in the 400 V DC bus and generates more power than required by the servers [75, 76].

To contribute to the reduction of the environmental footprint of data centers (and other applications that require an MV-AC to 400 V DC conversion), this thesis focuses on the realization of a highly efficient and highly compact SST for the supply of single server-racks.

#### **1.3** System Specifications

From the considerations of **Section 1.2**, the system specifications given in **Tab. 1.1** arise for the bidirectional SST treated in this thesis. As can be seen, the efficiency goal of  $\eta_{t,SST} = 98\%$  is highly ambitious and has been defined by the *Swiss National Research Program 70* [77] as a part of the *Swiss Energy Strategy 2050*, which specifies a 13% per

| Parameter                | Symbol             | Value            |

|--------------------------|--------------------|------------------|

| Power                    | P                  | $25\mathrm{kW}$  |

| MV-side AC voltage (rms) | $u_{ m g}$         | $3.8\mathrm{kV}$ |

| LV-side DC voltage       | $U_{\rm DC,LV}$    | $400\mathrm{V}$  |

| Mains frequency          | $f_{ m g}$         | $50\mathrm{Hz}$  |

| Target efficiency        | $\eta_{\rm t,SST}$ | 98%              |

Tab. 1.1: SST Specifications.

capita decrease of the electric energy consumption by 2035 compared to the year 2000. Therefore, a substantial increase in energy efficiency compared to standard solutions is necessary and will be one of the main goals of this thesis.

#### 1.4 SST Key Challenges

#### 1.4.1 Interfacing of the MV Grid

One of the key challenges of SST technology is the interfacing of the comparably high voltages with semiconductors on the MV-side of the SST. Up to now, this is typically solved by utilizing multilevel converters based on e.g.  $1200 V \dots 1700 V$  SiC MOSFETs or IGBTs. However, this leads to highly complex topologies with a high number of components and a complex modulation. Instead of sharing the total blocking voltage among several converter cells, the recent development of MV SiC devices with blocking voltages in the  $10 \dots 15 \, kV$  range enable the direct interfacing of MV with a single-cell converter. In this case, the complexity of the topology is significantly reduced, however for the price of the much more challenging handling of the MV SiC devices compared to LV devices and the insulation of the components for the full voltage instead of only a small share of the total voltage in case of the multi-cell approach.

#### 1.4.2 Medium-Voltage Insulation

The electrical insulation of MV equipment in the AC distribution grid is well-known. E.g. high-power LFTs are typically oil-insulated and can withstand high overvoltages. However, since the power density of LFTs is comparably low due to their low operating frequency, the additional isolation distances are small compared to the size of the LFT itself. In contrast, in case of SSTs where MF transformers with a considerably higher power density are incorporated, the isolation distances are much more significant. Furthermore, due to the higher power density, the surface area for the extraction of the dissipated heat through the insulation material is considerably lower and therefore, insulation materials with a high thermal conductivity are required for SST applications. Additionally, the combination of MV and MF imposes a high dielectric stress on the insulation [78], such that the insulation material has to feature a low dissipation factor and a high electric breakdown field strength to enable a compact MF MV transformer design. A detailed study on MF MV transformers is given in [79].

#### 1.4.3 Efficiency, Power Density, and Cost

For power electronic converters (including SSTs), there is always an application-specific trade-off between efficiency, power density, and cost, among others [80]. When the state-of-the-art MV-AC to LV-DC solution, i.e. an LFT and a subsequent rectifier is taken as a reference, the SST-based solution can outperform the LFT solution regarding efficiency and power density, whereby the initial cost of an SST is typically higher [40]. However, the higher initial cost of SSTs can eventually be compensated by the lower operating costs due to the lower losses and therefore, the efficiency is one of the most important aspects for the design of SSTs. Considering that space in a data center is rare and thus very expensive (since it could be used for more servers, whose computation power would generate more revenue), the space consumption of the power and signal provisioning systems should be minimized. Accordingly, a high power density of the power supply is desired. This is underlined by the fact that the developed technology in this thesis is not limited to the use in data centers but can also be utilized in even more space-limited applications such as traction or more-electric aircrafts, i.e. a high power density of the developed SST is in general of high relevance.

#### 1.4.4 Reliability

One highly important aspect from the perspective of utility grid operators but, e.g., also for data center operators is the reliability of the equipment, since equipment failures can potentially cause high economic damage. Whereas LFTs are highly robust and can withstand e.g. lightning impulses, SSTs are much more sensitive and require more complex protection measures [81]. However, for the supply of data centers with a large number of SSTs as intended in this work, the protection measures could be implemented centrally, such that the individual SSTs are connected to a protected MV grid. Furthermore, the approach to supply each server rack with an individual SST automatically offers a high level of redundancy, i.e. if one SST fails, only one server rack is out of operation until the SST is replaced, without affecting the operation of the other servers. In this case, however, the faulty SST has to be disconnected from the MV-AC grid, which is not further discussed in this thesis. Nevertheless, failures of the SSTs have to be avoided by implementing e.g. overcurrent protection features and by a proper design of the MV insulation.

#### 1.5 Suitable MV-AC to LV-DC SST Topologies

In the following, a brief overview over the most promising MV-AC to LV-DC SST topologies and their fundamental functionality is provided.

#### 1.5.1 Isolated Back End SSTs

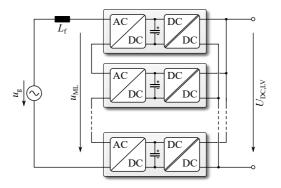

A common approach to interface an MV-AC grid without the use of MV semiconductors is the series connection of several AC/DC converter modules [42, 57, 58, 82, 83], as shown in **Fig. 1.4**. Thereby, the individual converter cells consist of a PFC AC/DC converter stage and a subsequent isolated back end (IBE) DC/DC stage. To decrease the turns ratio of the MF transformers and to achieve a natural voltage balancing among the converter cells [84], the outputs of the individual isolated DC/DC stages are connected in parallel, such that an inputseries output-parallel (ISOP) configuration of the converter cells results. In order to minimize the boost inductance  $L_{\rm f}$ , the AC/DC converters can be operated with phase-shifted carriers, resulting in a switched multilevel AC voltage  $u_{\rm ML}$ , which closely follows the MV grid voltage  $u_{\rm g}$ , and therefore leads to a small input current ripple. Even though multicell converters can achieve a high conversion performance and are very

**Fig. 1.4:** Multi-cell isolated back end realization of an MV-AC to LV-DC SST. The ISOP-connected cells consist of a front end PFC AC/DC stage and an isolated back end DC/DC converter.

flexible due to their modularity, they are also highly complex due to the high number of switches, gate drivers, isolated auxiliary supplies, and voltage/current measurements.

#### 1.5.2 Isolated Front End SSTs

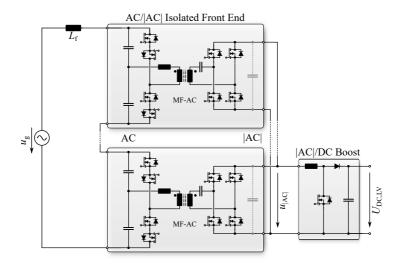

In contrast to an IBE topology, the galvanic isolation can also directly be performed in the front end of the SST, whereas the current shaping is taking place subsequent to the isolation barrier [85, 86]. Fig. 1.5 shows the isolated front end (IFE) topology, which consists of several ISOP-connected converter cells, each being realized as a series resonant converter (SRC) with bidirectional switches on the AC-side. The SRC is operated with a constant switching frequency and a 50 % duty cycle and, due to the isolation transformer and rectifier stage, generates an isolated and scaled AC voltage at its output (the capacitors on both sides of the SRC are comparably small and allow a full LF voltage swing). In case a variable interlock time is implemented, the SRC can be operated under soft-switching conditions [87], enabling a high switching frequency and therefore a compact design of the MF transformer. Eventually, a subsequent single |AC|/DC PFC boost converter performs the current shaping and generates the constant DC output voltage  $U_{\rm DC,IN}$ .

The advantage of the IFE approach compared to the IBE approach

Fig. 1.5: Multi-cell realization of an isolated front end (IFE) SST where each converter cell employs bidirectional switches on the AC-side, an MF isolation transformer, and a rectifier bridge generating a scaled |AC| voltage  $U_{|AC|}$ . A subsequent single-cell |AC|/DC PFC boost converter shapes the current and generates the DC output voltage.

is the lower number of SiC devices on the MV-side and in general a lower complexity on the MV-side (e.g. no voltage or current measurements), since the current shaping is performed on the LV-side. However, the disadvantage of this topology is the low utilization of the semiconductor chip area and the MF transformer, since these components have to be designed for the peak AC current (and in case of the transformer for the peak AC magnetic flux density), and the resulting lower full-load efficiency compared to an IBE approach [85].

For the sake of completeness, it has to be mentioned that an IFE SST could also be realized as single-cell system employing MV SiC devices, whereby the same advantages and disadvantages as in case of a multi-cell system would appear.

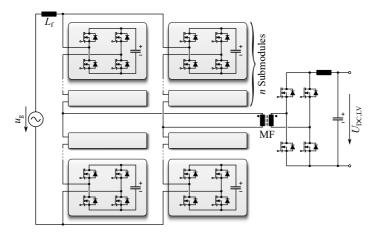

#### 1.5.3 Modular Multilevel Converter-Based SSTs

Another topology that does not require HV switches to interface an MV grid and has gained high interest since its patent registration in

**Fig. 1.6:** Modular multilevel converter (MMLC) realization of an MV-AC to LV-DC SST.

2001 is the modular multilevel converter (MMLC) [88–90]. Fig. 1.6 shows a variation of the MMLC, known from [33, 91], for interfacing an MV-AC grid to an LV-DC bus featuring galvanic isolation via an MF transformer. It consists of two inverter legs that are realized as a series-connection of several full-bridge submodules. With a suitable modulation scheme, the MMLC is able to generate an MF-AC voltage at the transformer terminals out of the MV-AC grid voltage without the necessity of supplying the individual submodules from their DC-side. However, in this case each of the converter arms (both inverter legs consist of an upper and a lower converter arm) has to be dimensioned to block the full peak AC grid voltage, which results in a very high number of semiconductors and associated circuitry. At the same time, this also leads to comparably high conduction losses due the high number of switches in the conduction path [33].

#### 1.5.4 Single-Cell IBE SSTs Using MV SiC Devices

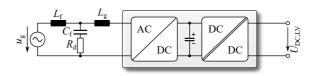

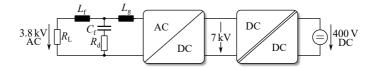

As already mentioned, with the new generation of  $10 \dots 15 \text{ kV}$  SiC MOS-FETs, it is possible to interface the MV-AC grid directly with a singlecell converter. Due to the higher efficiency, the IBE topology is preferred over the IFE topology and in this case the SST consists of a single-cell AC/DC PFC rectifier followed by an isolated single-cell DC/DC con-

**Fig. 1.7:** Single-cell IBE realization of an MV-AC to LV-DC SST utilizing MV SiC devices to interface the MV-AC grid.

verter, as shown in **Fig. 1.7**. The EMI noise (which is higher compared multilevel converters due to the lower number of voltage levels) is limited by an additional LCL-filter in front of the PFC rectifier, which is a typical filter structure used for MV converters [58]. The isolated DC/DC converter can e.g. be realized as dual active bridge (DAB) converter or as SRC and is interfaced to the AC/DC stage via an intermediate DC-link. Due to the greatly reduced complexity compared to the multi-cell IBE and IFE topologies as well as to the MMLC approach, a higher power density and possibly also a higher reliability are expected. Furthermore, MV SiC devices with outstanding switching behavior enable completely new dimensions in terms of switching frequency and efficiency compared to standard devices.

In order to explore the limits in efficiency and power density of the single-cell IBE approach, this topology is selected, realized, and tested in detail in this thesis. There,  $3^{rd}$  generation 10 kV, 20 A SiC MOSFETs of type *CPM3-10000-0350* from *Wolfspeed* are used on the MV-side of the SST.

#### 1.6 Previous Work

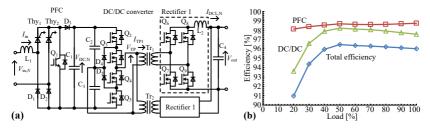

In 2017, Fuji Electric published an SST system (from now on referred to as Fuji Electric SST) for the power supply of IT equipment in data centers directly from the MV-AC grid [92]. The rated power is also 25 kW, and the input and output voltages are 2.4 kV AC (rms), and 54 V DC, respectively. Although the voltage levels are different from the system treated in this thesis, they are sufficiently close to use the Fuji Electric SST as a benchmark. The topology of one converter cell is shown in **Fig. 1.8(a)** and the system consists of five of these IBE cells in ISOP configuration. Furthermore, as can be seen, the topology only allows a unidirectional power flow from the MV-side to the LV-side,

Fig. 1.8: (a) Power circuit topology of one of five ISOP-connected converter cells of the *Fuji Electric SST* and (b) measured efficiency. The figures are taken from [92].

whereas the SST discussed in this thesis features bidirectional energy flow.

Fig. 1.8(b) shows the measured efficiency curves of the *Fuji Electric* SST and the total efficiency reaches 96% at full load. Furthermore, a power density of  $0.4 \,\mathrm{kW/L}$  is achieved [92].

#### 1.7 Aims and Contributions

The objective of this thesis is the design and experimental analysis of a  $10 \, \text{kV}$  SiC MOSFET-based 25 kW single-phase  $3.8 \, \text{kV}$  AC to  $400 \, \text{V}$  DC SST with a target efficiency of  $98 \, \%$ . Compared to the *Fuji Electric SST*, this efficiency means that the SST discussed in this thesis should feature half the losses. Furthermore, under this constraint, the power density of the SST should be maximized in order to make it suitable for volume restricted applications.

Besides these performance parameters, also the interaction between the MV-AC grid and the SST as well as the protection of the 10 kV SiC MOSFETs should be taken into account.

To achieve these performance goals and to enable a reliable operation of the SST in the grid, the following points, which have been identified as the main challenges, are treated in detail in this thesis:

▶ Highly compact isolated gate driver power supply - The gate driver of the high-side switch in a bridge-leg configuration is referenced to the switch-node potential and hence must be supplied with electrical energy in a galvanically isolated manner. To limit the CM currents arising from the fast switching transitions,

a low parasitic coupling capacitance across the isolation barrier is mandatory. Typically, air or tape insulated transformers are used in literature for 10...15 kV SiC gate driver power supplies. However, these isolation transformers are showing a large volume [93–96] and in some cases even exceed the volume of the SiC module considerably [97,98]. To enable an integration of the isolated gate driver into future MV SiC modules, which would significantly simplify the design of MV converters, a highly compact gate driver isolation transformer with a very low coupling capacitance is designed and realized utilizing a special transformer design and an advanced insulation material.

- ▶ Ultra-fast overcurrent protection To avoid severe damage of MV converters, whose DC-link capacitors normally store comparably large amounts of energy capable of causing explosions of semiconductor modules, gate drivers for MV switches are typically equipped with an overcurrent protection (OCP) circuit. The reaction times of existing OCP circuits are usually in the microsecond range, and typically OCP circuits are only tested for the standard hard-switching fault (HSF) and the fault under load (FUL) scenarios. However, in MV applications, flashover faults (FOF) with extremely high du/dt and di/dt values can occur due to insulation failures and are much more critical to handle for an OCP circuit. Therefore, an ultra-fast OCP circuit is realized, which is able to clear a FOF at a DC-link voltage of 7 kV and protects the 10 kV SiC devices from damage even in this worst-case scenario.

- ► Accurate calorimetric soft-switching loss measurement method - Soft-switching losses (SSL) of MOSFETs are typically not given in the device datasheets and therefore have to be determined by measurements. A detailed error analysis shows that electrical measurement methods, such as the double pulse test, are highly inaccurate and hence unsuitable for the measurement of SSL of modern fast-switching SiC MOSFETs. Therefore, a highly accurate transient calorimetric measurement method is developed and used for the determination of the SSL of the employed 10 kV SiC modules. An interesting and important result of these measurements is that the antiparallel SiC JBS diode causes the largest part of the soft-switching losses of the 10 kV SiC module due to losses occurring during the charging/discharging of the parasitic

capacitance of the diode.

- ▶ Impact of parasitics on the design of MV converters -For LV converters it is commonly known that parasitic commutation loop inductances should be minimized in order to avoid excessive ringing and/or voltage overshoots during the switching transitions. For this reason, low-inductive packaging especially of fast-switching wide bandgap devices has significantly gained in importance with the development of modern SiC and GaN power devices. However, a theoretical analysis shows that parasitic inductances play only a minor role for the MV converter treated in this thesis. In contrast, for MV converters of this power class it is highly important to minimize parasitic capacitances in order to limit the occurring capacitive currents during the switching transitions. These findings have an important impact on the design of the 10 kV SiC MOSFET-based SST, since special attention has to be paid to achieve a low-capacitive design of e.g. the magnetic components and the PCB layouts.

- ▶ Fully soft-switching SST topology Despite the outstanding switching performance of MV SiC MOSFETs compared to HV Si IGBTs, their hard-switching losses are still significant and are limiting the achievable efficiency and the power density of MV converters, since they define an upper bound for the switching frequency and hence inhibit the downsizing of passive components. To overcome these limitations, the SST topology is fully softswitching and therefore, the efficiency and the power density are significantly increased compared to state-of-the-art SSTs. Specifically, a novel bidirectional soft-switching single-phase AC/DC converter topology is developed, whereas the bidirectional LLC series resonant DC/DC converter is operated with a novel modulation scheme to achieve soft-switching for all devices.

- ▶ Calorimetric efficiency measurements The simplest method to measure the efficiency of a power electronic converter is to measure its input power and its output power and to calculate the ratio of both power values. However, for highly efficient systems in the range of 99% efficiency, already small power measurement errors can lead to large errors in the resulting efficiency. A detailed measurement error analysis shows that electrical efficiency measurements are unsuitable for the determination of the efficiency

of the converters developed in this work. Therefore, the losses of the individual semiconductors and the magnetic components are measured with the help of calorimetric measurement methods leading to a significantly higher accuracy. Furthermore, with these measurement methods, the distribution of the losses among the different components within the converters can be determined.

- ▶ EMI filter Existing standards for the maximum current harmonics generated by a converter in the MV grid only cover frequencies up to 2.5 kHz [99] or 9 kHz [100], since typically LFTs or converters with low switching frequencies are used in the MV-AC grid [50,101,102]. However, due to the low soft-switching losses of the latest generation of 10 kV SiC MOSFETs, switching frequencies in the 50...100 kHz range are possible. Moreover, the lack of harmonic standards does not mean that no AC-side input filter is needed, since harmonics in this frequency range could e.g. lead to grid resonances or aging of insulation materials in MV cables due to heating from dielectric losses. Therefore, the existing IEEE 519 harmonic standard is extrapolated to higher frequencies and an LCL-filter is designed accordingly.

- ▶ MV-AC cable resonances Most commonly, MV converters are connected to the utility grid via MV-AC cables with a certain length. From an electromagnetic field perspective, these cables can be regarded as almost undamped transmission lines with discrete resonance frequencies and high resonant gains. E.g., for a typical MV cable with a length of 500 m, the first resonance frequency is located at around 35 kHz. If the switching frequency of the AC/DC front end of the SST approaches one of these cable resonance frequencies, undesired current oscillations of significant magnitudes can occur. By adding the proposed passive and quasi lossless damping network between the LCL-filter and the MV cable, the oscillations can be completely avoided, independently of the cable length.

- ▶ MV insulation One of the most challenging aspects during the design of an MV system is the electrical insulation of the individual components and the insulation coordination within the converter system. Due to the high voltages in combination with the high switching frequencies enabled by the 10 kV SiC MOS-FETs under soft-switching conditions, a high dielectric stress is

imposed on the insulation material used to insulate e.g. magnetic components. Therefore, in case of standard insulation materials, considerable dielectric losses are generated, which could lead to local hot spots and finally to the destruction of the insulation. Consequently, to attain a reliable MV insulation, advanced insulation materials with a low dielectric dissipation factor and a high thermal conductivity are required in order to not only generate less dielectric losses, but also to extract the losses generated by the windings through the insulation material.

# 1.8 Outline of the Thesis

With the goal to guide the reader along the design and realization of the SST system, this thesis is divided into six chapters, which are briefly outlined in the following.

- ▶ The development of MV SiC MOSFETs with blocking voltages of 10 kV enables new levels of performance of MV-connected power electronic converters, but also demands for advanced isolated gate drivers and OCP circuits to fully and reliably utilize the potential of these novel MV SiC power semiconductors. Therefore, in **Chapter 2**, a highly compact isolated gate driver with an ultrafast overcurrent protection circuit is designed, constructed and experimentally verified with the goal to enable an integration of this circuitry into future intelligent 10 kV SiC modules in order to simplify the design and to increase the performance of MV converters.

- ▶ In Chapter 3, the soft-switching losses of the 10 kV SiC modules are determined experimentally, since the device datasheet does not provide any loss values for soft-switching (and for hard-switching). A detailed error analysis shows that electrical measurement methods are unsuitable for the measurement of soft-switching losses and therefore, a highly accurate transient calorimetric measurement method is developed and applied to the 10 kV SiC modules. Additionally, the hard-switching losses are also measured and compared to the soft-switching losses.

- ▶ For the design of the bidirectional 3.8 kV AC to 7 kV DC front end converter of the SST, the achievable performance is calcu-

lated in **Chapter 4** in case the standard hard-switched full-bridge PWM converter topology is employed. It is shown that the hardswitching losses significantly limit the efficiency and the power density, since a rather low switching frequency would have to be selected. To improve the efficiency and power density, the 10 kV SiC MOSFETs have to be operated under soft-switching conditions and to achieve this, a novel bidirectional soft-switching AC/DC converter topology, the *integrated* Triangular Current Mode (*i*TCM) topology is developed. Finally, the *i*TCM converter is designed and constructed with a special focus on the required inductors and their MV insulation, the AC-side LCL-filter and the problems arising from the connection of the converter to the MV-AC grid via an MV cable. The converter is experimentally verified at full load and its efficiency and loss distribution are determined accurately by calorimetric measurements.

- ▶ Chapter 5 treats the bidirectional isolated 7 kV/400 V DC/DC converter, which provides the required voltage step down and the mandatory galvanic isolation of the SST. Since the AC/DC front end converter is able to control the voltage, the DC/DC converter can be realized as SRC operated at resonance frequency and therefore acting as "DC transformer", i.e. providing a quasi load-independent voltage transfer ratio. In order to achieve zero voltage switching (ZVS) for all devices in all possible operating points, a novel highly robust modulation scheme is developed. Furthermore, the MV MF transformer is Pareto-optimized and special attention is paid to its MV insulation. The DC/DC converter is constructed and experimentally verified at full load. Finally, the efficiencies and loss distributions of the transformer and the complete DC/DC converter are determined with calorimetric measurement methods with high accuracy.

- ▶ At the end of each chapter, short summaries of the obtained results are given and the key findings are highlighted. Final conclusions obtained from the presented study are summarized in **Chapter 6**. The achieved performance is discussed and compared to the *Fuji Electric SST*. Finally, the thesis is concluded with suggestions for potential future research areas.

# 1.9 List of Publications

Different parts of the research findings presented in this thesis have already been published or will be published in international scientific journals, conference proceedings, or workshops. The publications developed in the course of this thesis are listed below.

# **Journal Papers**

- D. Rothmund, D. Bortis, and J. W. Kolar, "Highly Compact Isolated Gate Driver with Ultrafast Overcurrent Protection for 10 kV SiC MOSFETs," CPSS Trans. Power Electron. and Appl., vol. 3, no. 4, pp. 278-291, 2018.

- D. Rothmund, T. Guillod, D. Bortis, and J. W. Kolar, "99.1% Efficient 10 kV SiC-Based Medium Voltage ZVS Bidirectional Single-Phase PFC AC/DC Stage," *IEEE J. Emerg. Sel. Topics Power Electron.*, 2018.

- ▶ D. Rothmund, T. Guillod, D. Bortis, and J. W. Kolar, "99% Efficient 10 kV SiC-Based 7 kV/400 V DC-Transformer for Future Data Centers," *IEEE J. Emerg. Sel. Topics Power Electron.*, 2018.

- D. Rothmund, D. Bortis, and J. W. Kolar, "Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10 kV SiC MOSFETs and Diodes," *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 5240–5250, 2018.

# **Conference** Papers

- ▶ D. Rothmund, D. Bortis, J. Huber, D. Biadene, and J. W. Kolar, "10 kV SiC-Based Bidirectional Soft-Switching Single-Phase AC/DC Converter Concept for Medium-Voltage Solid-State Transformers," in *Proc. IEEE Int. Symposium on Power Electron. for Distributed Generation Systems (PEDG)*, Florianopolis, Brazil, 2017.

- ▶ D. Rothmund, D. Bortis, and J. W. Kolar, "Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10 kV SiC

MOSFETs," in Proc. IEEE Int. Symposium on Power Electron. for Distributed Generation Systems (PEDG), Vancouver, Canada, 2016.

- D. Rothmund, G. Ortiz, T. Guillod, and J. W. Kolar, "10 kV Sic-Based Isolated DC-DC Converter for Medium-Voltage-Connected Solid-State Transformers," in *Proc. IEEE Appl. Power Electronics Conf. (APEC)*, Charlotte, NC, USA, 2015.

- D. Rothmund, G. Ortiz, and J. W. Kolar, "SiC-Based Unidirectional Solid-State Transformer Concepts for Directly Interfacing 400 V DC to Medium-Voltage AC Distribution Systems," in *Proc. IEEE Int. Telco. Energy Conf. (INTELEC)*, Vancouver, Canada 2014.

- ▶ D. Rothmund, J. E. Huber, and J. W. Kolar, "Operating Behavior and Design of the Half-Cycle Discontinuous-Conduction-Mode Series-Resonant-Converter with Small DC Link Capacitors," in *Proc. IEEE Workshop on Control and Model. of Power Electron. (COMPEL)*, Salt Lake City, UT, USA, 2013.

# Workshops

▶ D. Rothmund, T. Guillod, D. Bortis, and J. W. Kolar, "Design and Experimental Analysis of a 10 kV SiC MOSFET Based 50 kHz Soft-Switching Single-Phase 3.8 kV AC / 400 V DC Solid-State Transformer," in *Proc. IEEE Energy Conversion Congr. and Expo. (ECCE USA), Special Session on Smart Transformers,* Portland, OR, USA, 2018.

# **Further Scientific Contributions**

- ▶ T. Guillod, D. Rothmund, and J. W. Kolar, "Dual-Active ZVS Phase Shift Modulation of a 7 kV/400 V Series-Resonant Converter," *IEEE Trans. Power Electron.* (under review), 2019.

- ► T. Guillod, R. Faerber, D. Rothmund, F. Krismer, C. Franck, and J. W. Kolar, "Dielectric Losses in Dry-Type Insulation of Medium-Voltage Power Electronic Converters," *IEEE J. Emerg. Sel. Topics Power Electron.* (under review), 2019.

- ▶ J. E. Huber, J. Böhler, D. Rothmund, and J. W. Kolar, "Analysis and Cell-Level Experimental Verification of a 25 kW All-SiC Isolated Front End 6.6 kV/400 V AC-DC Solid-State Transformer," *CPSS Trans. Power Electron. and Appl.*, vol. 2, no. 2, pp. 140-148, 2017.

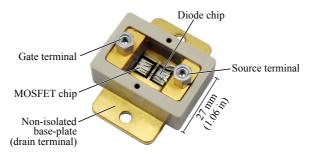

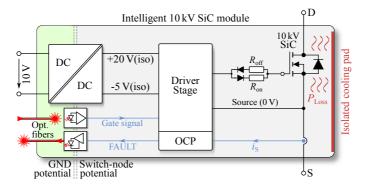

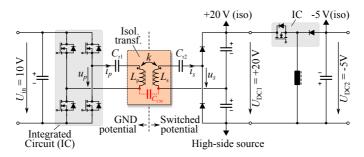

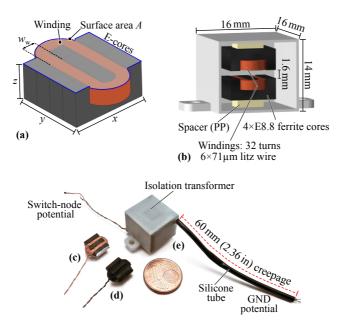

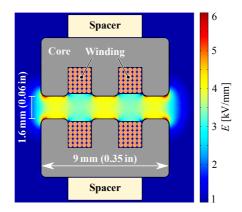

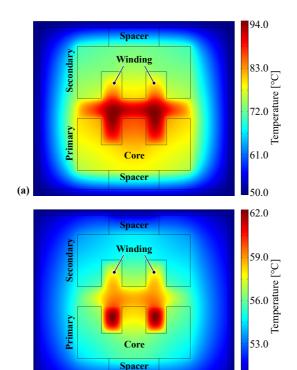

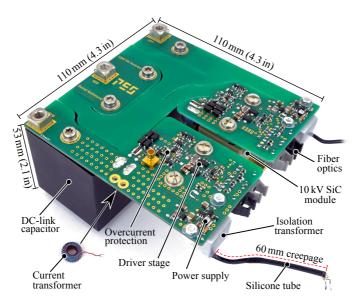

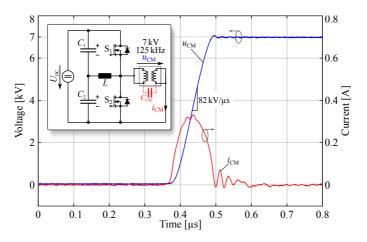

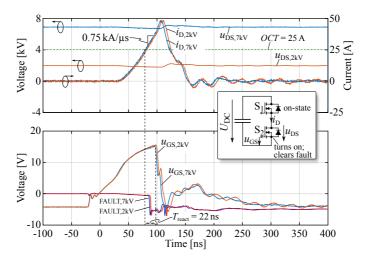

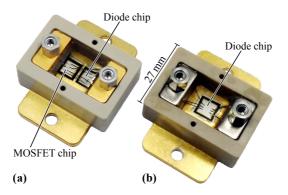

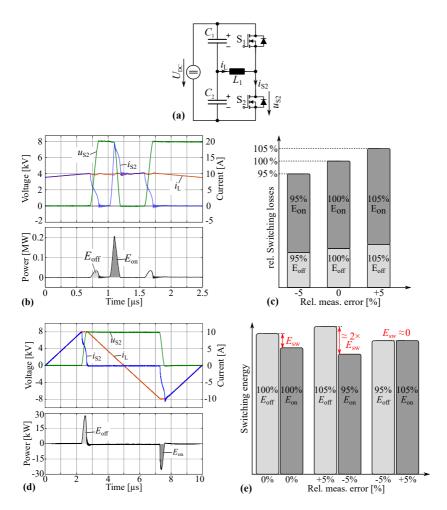

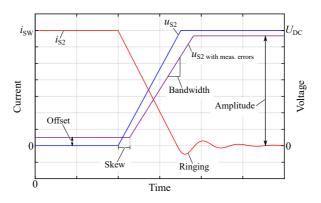

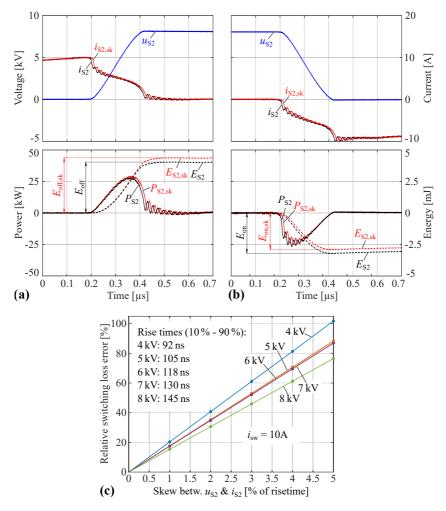

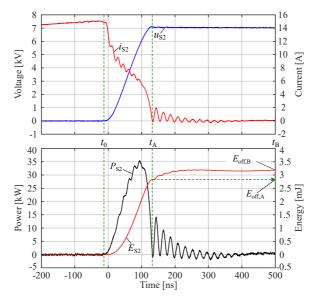

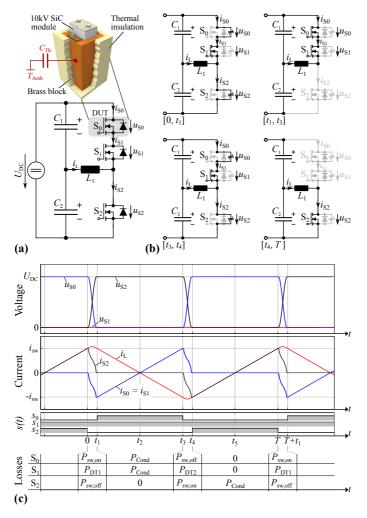

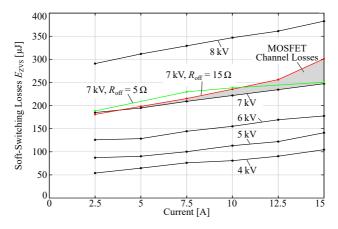

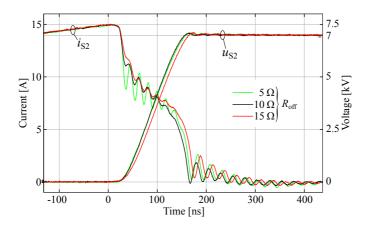

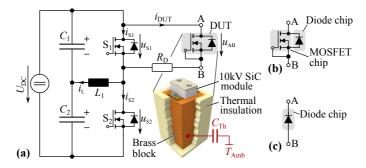

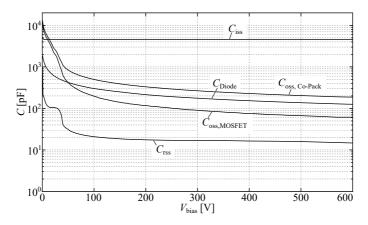

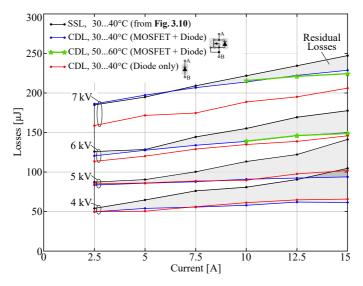

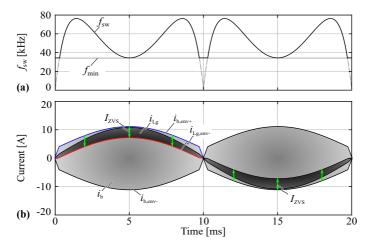

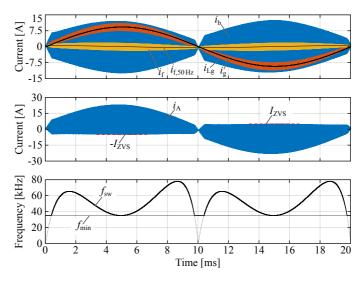

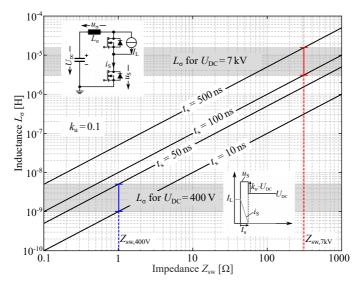

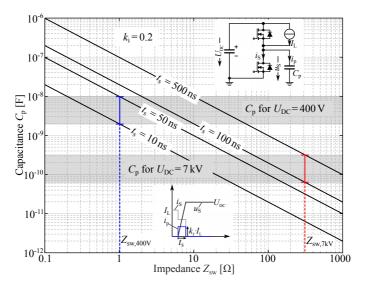

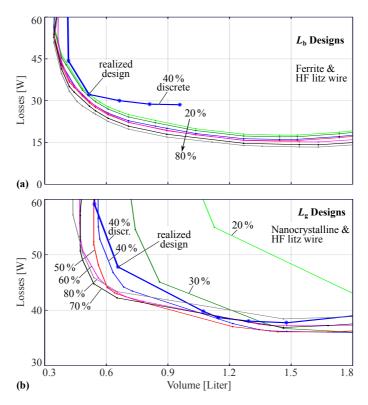

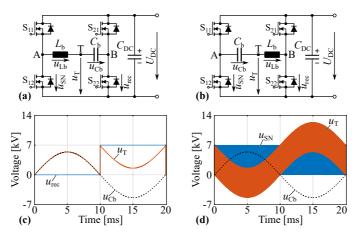

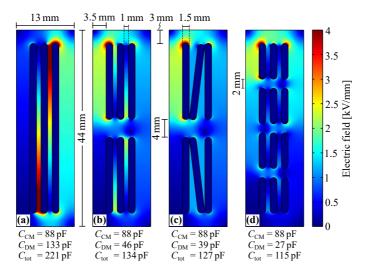

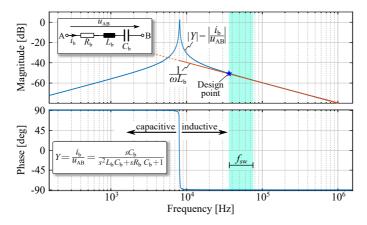

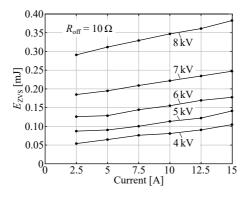

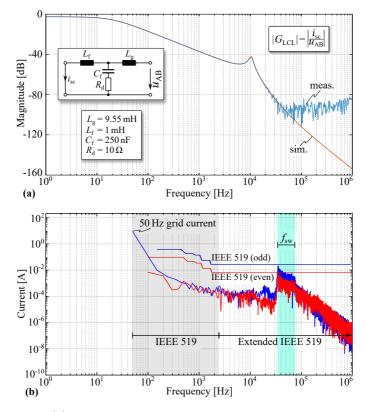

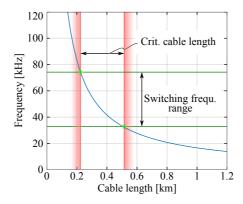

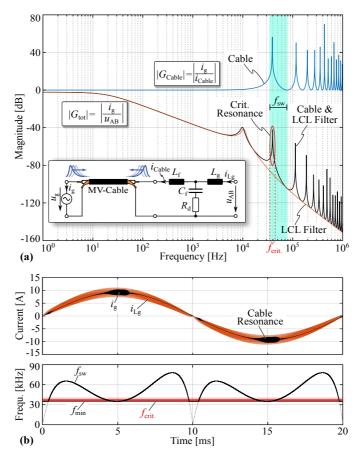

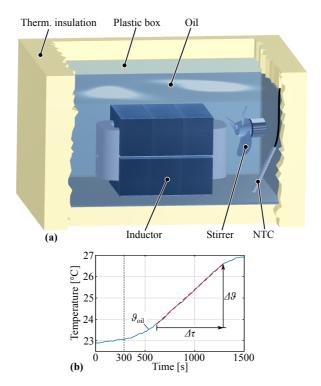

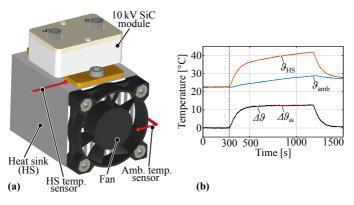

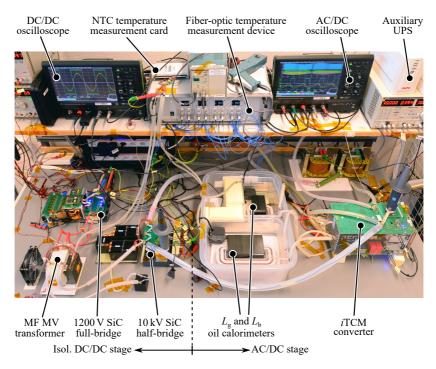

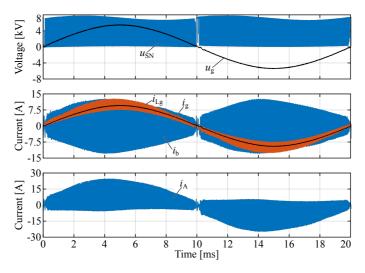

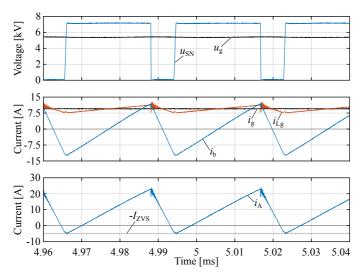

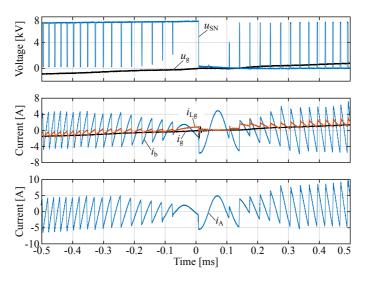

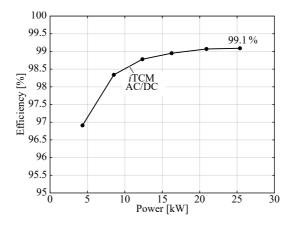

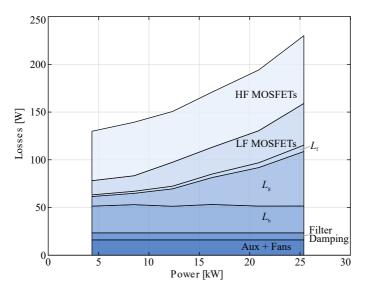

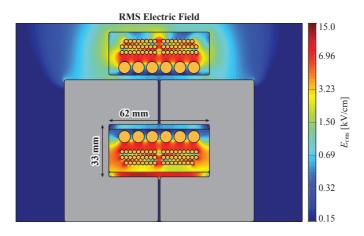

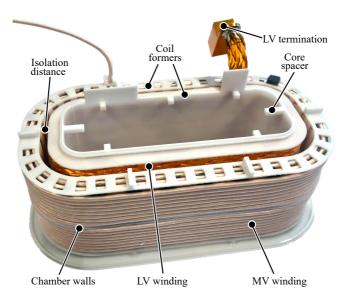

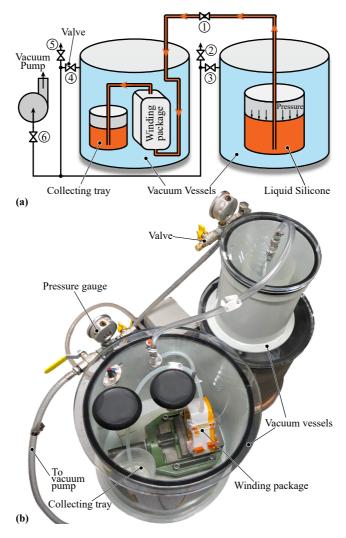

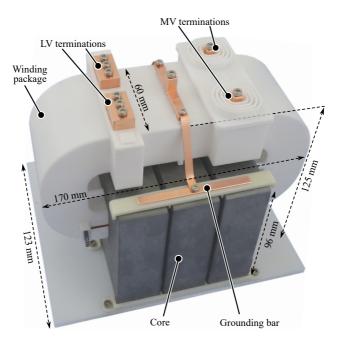

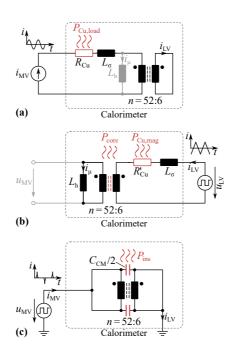

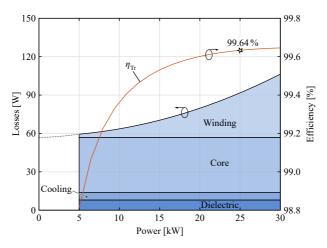

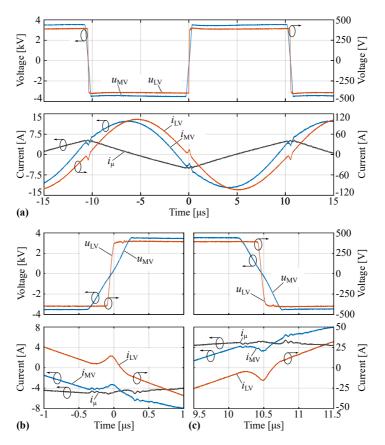

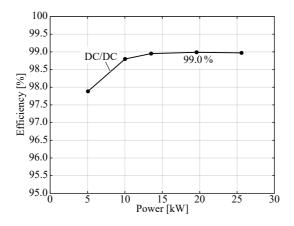

- ▶ J. E. Huber, D. Rothmund, L. Wang, and J. W. Kolar, "Full-ZVS Modulation for All-SiC ISOP-Type Isolated Front End (IFE) Solid-State Transformer," in *Proc. IEEE Energy Conversion Congr. and Expo. (ECCE USA)*, Milwaukee, WI, USA, 2016.