Diss. ETH No. 28115

## Next-Generation Ultra-Compact/Efficient Data-Center Power Supply Modules

A thesis submitted to attain the degree of

DOCTOR OF SCIENCES of ETH ZURICH (Dr. sc. ETH Zurich)

> presented by GUSTAVO CARLOS KNABBEN

> > MSc EE, UFSC born on 23.05.1992 citizen of Joinville, Brazil

accepted on the recommendation of

Prof. Dr. Johann W. Kolar, examiner Prof. Dr. Marcelo Lobo Heldwein, co-examiner

ETH Zurich Power Electronic Systems Laboratory Physikstrasse 3 | ETL H23 8092 Zurich | Switzerland

http://www.pes.ee.ethz.ch

© 2021, Gustavo C. Knabben

I am the way, and the truth, and the life; no one comes to the Father except through Me. – Jesus Christ (John 14:6)

Ich bin der Weg, und die Wahrheit, und das Leben; niemand kommt zum Vater als nur durch mich. – Jesus Christus (Johannes 14:6)

> Eu sou o caminho, e a verdade, e a vida; ninguém vem ao Pai senão por mim. – Jesus Cristo (João 14:6)

## Acknowledgments

**F**<sup>IRST</sup> and foremost, I would like to thank and praise Yahweh, the God of the Bible, the Father of my Lord Jesus Christ, the Creator and triune God: Father, Son and Holy Spirit—to Him be the glory forever, amen! He allowed me to accomplish this magnificent milestone, and without Him, I wouldn't be even alive to start. He not only gave me the breath of life, but also forgave me, a wretched and sinful man, and redeemed me through the sacrifice of His only begotten Son on the cross. And the one that died for me is alive, because He rose again on the third day, and lives to make intercession for me. He will give me a glorified body when the hour comes, to live forever with Him and all the saints—without sin—in heaven. Thank you Yahweh, my Lord!

As the hour has not yet come, I continue to work my best on earth for Him and His Kingdom; and for reasons that I don't yet exactly know, I'm becoming a doctor on power electronics. I'm very grateful for achieving this goal and would like to thank, from the bottom of my heart, my advisor Prof. Dr. Johann W. Kolar for this amazing opportunity. Johann, you are an extraordinary, visionary and committed researcher, with a passion for power electronics that goes way beyond anything one might imagine before knowing you personally. It was a life-changing experience—and also a great challenge—to working with you and being part of your excellent laboratory. Thank you so much for your scientific guidance along these four years and for choosing me as one of your carefully-selected students.

Also to Prof. Dr. Marcelo Lobo Heldwein goes my gratitude, as he served as both the bridge for starting the doctorate and the thesis's co-examiner at the end. I wouldn't have come to Switzerland if it wasn't for you—thank you for taking a chance on me and for being this altruistic person.

Another big thanks goes to Dr. Gerald Deboy, Dr. Matthias Kasper, M.Sc. Luca Peluso and Dr. Jon Azurza Anderson for the successful collaboration between PES and Infineon Technologies Austria. Working with you in this project was an immense pleasure! Our deep and rich discussions, your ongoing kindness and professionalism, and the trust you put in me were essential to boosting my motivation and leading me toward the finish line.

Thanks to all my PES colleagues as well: secretaries, technicians, postdoctorates, doctorates and students. Citing names would be very tough at this point—I would definitely forget someone. To all of you that made part of my PES life during these last four years goes my profound gratitude for all discussions, coffee breaks, events and good/bad times we had. You guys are incredibly-capable people and excellent companions. A special thanks goes to all my office mates and lab buddies, for the amazing time together, and to Dr. Jannik Schäfer, for being my project's supervisor and this practical, objective, skilled person that is always willing to help. Hope to see you all again in the course of this life, and pray to see you also in the life to come.

I had a very intense life outside ETH as well—and I couldn't be more grateful for that! Since Day 1 at PES, I already was part of a welcoming, biblically-faithful, doctrinally-sound church in Zurich, where I congregate with my brothers and sisters in Christ since then. Life for people moving alone to foreign countries can be tricky, and having people around who you can trust as your own family is priceless. This is exactly what God gave me by this church: a fellowship of believers that would do more for me than perhaps some of my relatives. Life-long friendships were established, and I praise the Lord for the people of the IELPZ; especially my pastors and close friends, who spared no effort and sacrificially supported me throughout the doctorate. Blessed be the name of the Lord for all of you!

My family from Brazil also played a key role in this accomplishment. Primarily because I'm their offspring, and wouldn't be here if it wasn't for their care, nourishment, protection, discipline and love. Mom, you are a superhero! It's mind blowing to think how you raised up three children alone under so difficult circumstances, and even kept us in the best school of our hometown despite the exorbitant tuition. Words really fail to thank you for your self-giving, sacrificial love! Also my grandparents were incredible during my childhood. They very much replaced the role of my dad, who died on a car accident when I was three, and helped my mom raising up me and my two brothers with the best they could provide. Many thanks also to all my relatives that, in one way or another, helped to make me what I am. A special thanks goes to the old, good friends whose friendship endures even up to this very day. Thank you all so much, from the bottom of my heart!

Finally, I want to thank God for the new family he is starting through me. One year ago, I left my father and mother, as the Bible says, and became one flesh with my beloved wife Raquel Knabben. How blessed I was when the Lord—and my dear in-laws—allowed me to begin a life-long relationship with such a smart, beautiful and God-loving person. Thank you for saying yes, for always being beside me, and for letting the Father use you to conform me to the image of His Son. *Schatz*, you are my best friend, a gift from God, and I eager—if the Lord wills—to expand our family and raise up children with you for the glory of our God.

> Zurich, November 2021 Gustavo Knabben

## Abstract

THE increasingly-electric future requires next-generation power supplies that are compact, efficient, low-cost, and ultra-reliable, even across mains failures, to power mission-critical electrified processes. Hold-up time requirements and the demand for ultra-high power density and minimum production costs, in particular, drive the need for DC/DC power converters with (i) a wide input voltage range, to reduce the size of the hold-up capacitor, (ii) soft-switching over the full input-voltage and load ranges, to achieve low losses that facilitate a compact realization, and (iii) complete PCB-integration for low-cost manufacturing. Wide-bandgap power semiconductors, with excellent on-resistance properties and low switching and reverse-recovery losses, come along these requirements toward the conceptualization of nextgeneration power-supply modules, but cannot alone catapult state-of-theart converter technology to the performance baseline of future automotive, automated manufacturing and hyperscale data-center applications. Instead, the combination of wide-bandgap devices with proper converter topology, control and magnetics design has proven to be the real enabler of power supplies for the increasingly-electric future.

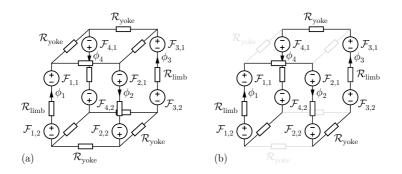

This thesis makes a case for the combination of these three features (widebandgap devices, proper topology/control and advanced magnetics) as the keys for paving the way toward next-generation power-supply modules. Therefore, a suitable low-complexity circuit topology with improved control scheme that operates across a wide-input-voltage range with complete softswitching is identified, which switches efficiently at higher frequencies and high output currents with PCB-integrated magnetics, improving significantly power density compared to state-of-the-art designs. This topology embeds a sophisticated PCB-integrated matrix transformer that has a single path for the magnetic flux, ensuring equal flux linkage of parallel-connected secondary windings despite possible geometric PCB-layout asymmetries or reluctance imbalances. The so-called *snake-core* transformer avoids the emergence of circulating currents between parallel-connected secondary windings and guarantees proper operation of parallel-connected, magnetically-coupled converter modules.

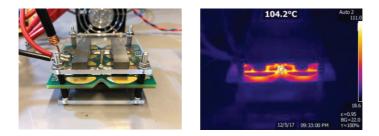

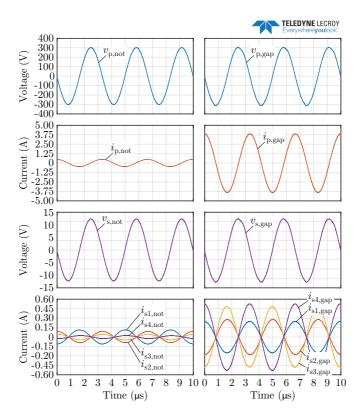

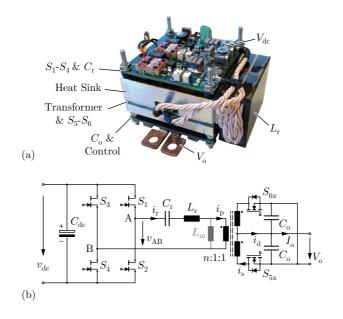

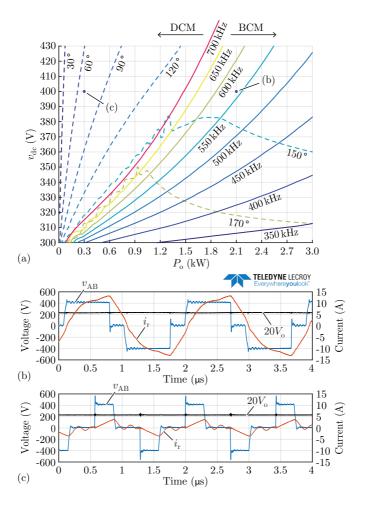

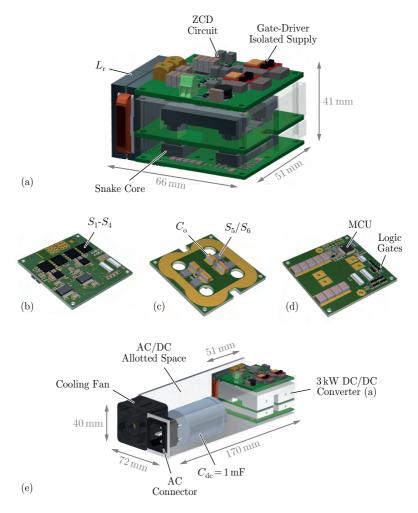

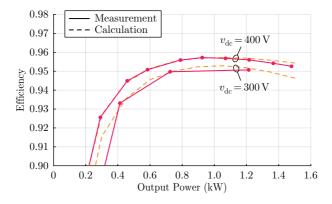

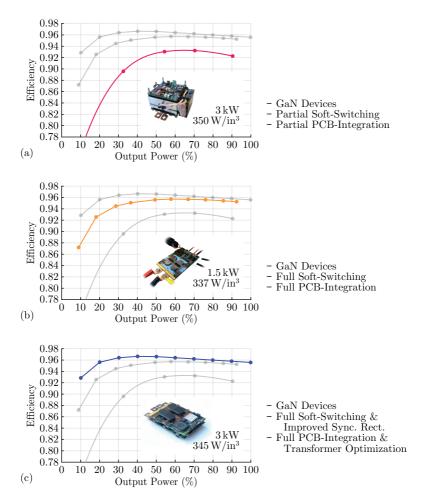

The benefits of the proposed topology, control scheme and transformer design are validated by three fabricated 300 V-430 V-input, 12 V-output DC/DC hardware demonstrators. The converters utilize an LLC-based control scheme for complete soft-switching and the snake-core transformer to divide the output current with a balanced flux among multiple secondary windings. First, a 3 kW DC/DC series-resonant converter achieves 350 W/in<sup>3</sup> (21.4 kW/dm<sup>3</sup>)

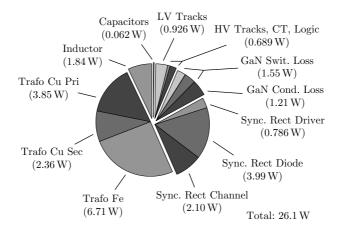

power density and 94 % peak efficiency, validating control and transformer operation. Then, a second hardware prototype with 1.5 kW showcases a peak efficiency close to 96 % and a power density of 337 W/in<sup>3</sup> (20.6 kW/dm<sup>3</sup>), with full PCB-integration and zero-voltage switching even down to zero load. Finally, the third demonstrator—a magnetically-coupled, input-parallel/outputparallel, two-1.5 kW-module DC/DC converter—achieves a peak efficiency of nearly 97 % and a power density of 345 W/in<sup>3</sup> (21.1 kW/dm<sup>3</sup>) with ideal current sharing among modules and stable operation, important characteristics enabled by the novel snake-core transformer. Detailed loss models are derived for every converter's component and the measurement results are in excellent agreement with the calculated values. These loss models are used to identify improvements to further boost efficiency, the most important of which is the minimization of delay times in synchronous rectification with either synchronous rectifier ICs embedded into the power-device's package or, at a minimum, Kelvin-source connections on high-current MOSFETs.

The results accomplished in this thesis indicate the necessity of careful topology/control selection and advanced-magnetics design for enabling WBG-based industrial power supplies that will outperform state-of-the-art solutions and catapult them to the next-generation performance standards. None of these features—be it WBG devices, wide-gain-range resonant converters, or advanced PCB-integrated magnetics—will alone enable next-generation power-supply modules, but the thoughtful combination of these technologies and their careful application to the particular application, with emphasis to high-frequency PCB magnetics and soft-switching topologies, which enable compact and cost-effective converters with competitive efficiencies.

## Kurzfassung

**D** IE zunehmende Elektrifizierung verschiedenster technischer Bereiche er-fordert bereite bereite fordert bereits heute, und insbesondere in Zukunft, Stromversorgungen, die immer kompakter, effizienter, kostengünstiger und zuverlässiger werden. Letzteres ist von besonderer Bedeutung für leistungselektronische Systeme, welche als Stromversorgungen ausfallskritischer elektrischer Prozesse eingesetzt werden, da die Energieversorgung auch im Falle eines kurzzeitigen Netzausfalls nicht unterbrochen werden darf. Insbesondere die Anforderungen an die Überbrückungszeit, sowie die Forderung nach ultrahoher Leistungsdichte und minimalen Produktionskosten, erfordern Gleichspannungswandler mit (i) einem weiten Eingangsspannungsbereich, um die Größe des Überbrückungskondensators zu reduzieren, (ii) einer effizienten Ansteuerung der Halbleiter über den gesamten Eingangsspannungs- und Lastbereich, um die Verluste zu minimieren, was wiederum eine kompakte Realisierung ermöglicht, und (iii) einer vollständigen PCB-Integration der Wicklungen der magnetischen Komponenten, was in einer kostengünstigen Fertigung resultiert. Auch wenn in den letzten Jahren dank der Entwicklung immer besserer Wide-Bandgap Halbleitertechnologien grosse Fortschritte bezüglich der Optimierung des Schaltverhaltens von elektrisch gesteuerten Schaltern erreicht wurden, so ist dies dennoch nicht genug, um die zuvor erwähnten Anforderungen an künftige leistungselektronische Systeme optimal zu erfüllen. Dies kann nur mit einer Kombination aus einer optimalen Schaltungstopologie, den neuesten Halbleitertechnologien, einer ausgefeilten Steuerung, sowie optimal entworfenen magnetischen Komponenten erreicht werden.

In dieser Arbeit werden die oben genannten Punkte zuerst einzeln analysiert und optimiert, um anschliessend die gewonnenen Erkenntnisse zu kombinieren und den Weg zu Gleichspannungswandlern der nächsten Generation zu ebnen. Im Detail wird auf diesem Weg zuerst eine geeignete Schaltungstopologie mit geringer Komplexität und einem verbesserten Steuerungsschema entwickelt, welche einen weiten Eingangsspannungsbereich abdecken und dabei die Halbleiter trotzdem weitestgehend verlustfrei schalten kann. Dies erlaubt einen effizienten Betrieb auch bei sehr hohen Frequenzen und hohen Ausgangsströmen, wodurch das Volumen der PCB-integrierten magnetischen Komponenten reduziert, und die Leistungsdichte des gesamten Systems, im Vergleich zum heutigen Standard, erheblich verbessert wird. Diese Topologie verwendet einen neuartigen PCB-integrierten Matrixtransformator, der dem magnetischen Fluss nur einen einzigen Pfad bietet und dadurch eine perfekte Symmetrierung der sekundärseitigen Ausgangsspannungen garantiert, auch wenn aufgrund möglicher geometrischer Asymmetrien in den PCB- integrierten Wicklungen in einem konventionellen Matrix Transformator unterschiedliche sekundärseitige Spannungen resultieren würden. Entsprechend vermeidet der sogenannte Snake-Core-Transformator aufgrund seines internen Aufbaus das Auftreten von Kreisströmen zwischen den parallel geschalteten Sekundärwicklungen und garantiert so auch einen symmetrischen und effizienten Betrieb im Falle mehrerer parallelgeschalteter, magnetisch gekoppelter Wandlermodule.

Die Vorteile der verwendeten Topologie, des entwickelten Steuerschemas und des Snake-Core-Transformators, gegenüber konventionellen Ansätzen, werden mittels drei DC/DC-Hardware-Prototypen mit einer Eingangsspannung von 300 V bis 430 V, einer Ausgangsspannung von 12 V und einer maximalen Ausgangsleistung von 3 kW validiert. Die Wandler verwenden dabei ein Steuerschema, welches auf demjenigen des bekannten LLC-Resonanzkonverters basiert, jedoch, im Gegensatz zu herkömmlichen Steuerverfahren, über den gesamten Eingangsspannungs- und Ausgangsleistungsbereich weiches Schalten der Halbleiter garantiert. Des Weiteren erlaubt es der Snake-Core-Transformator, den hohen Ausgangsstrom, dank des identischen magnetischen Flusses in allen Wicklungen, gleichmässig auf mehrere Sekundärwicklungen aufzuteilen, wodurch die sekundärseitige Synchrongleichrichtung des Ausgangsstroms erheblich erleichtert wird.

Der erste Hardwareprototyp, ein galvanisch getrennter Serienresonanzwandler, liefert eine maximale Ausgangsleistung von 3 kW bei einer Leistungsdichte von 350 W/in<sup>3</sup> (21.4 kW/dm<sup>3</sup>) und einem maximalen Wirkungsgrad von 94 %. Diese Hardware wurde primär für die Validierung des Steuerschemas sowie des reibungslosen Betriebs des Snake-Core-Transformators entwickelt. Der zweite Hardwareprototyp liefert eine maximale Ausgangsleistung von 1.5 kW und weist einen maximalen Wirkungsgrad von fast 96 % bei einer Leistungsdichte von 337 W/in<sup>3</sup> (20.6 kW/dm<sup>3</sup>) auf. Bei diesem Prototypen wurden erstmals die Wicklungen aller magnetischen Komponenten in die Leiterplatte (PCB) integriert und dank einer Erweiterung des Steuerschemas können die Halbleiter auch ohne Last am Ausgang weich geschaltet werden, was die Effizienz im Niedriglastbetrieb verbessert. Der dritte Demonstrator besteht aus zwei magnetisch gekoppelten 1.5 kW Modulen, welche sowohl eingangsseitig als auch ausgangsseitig parallelgeschaltet sind. Dieser Prototyp erreicht einen maximalen Wirkungsgrad von nahe 97 % bei einer Leistungsdichte von 345 W/in<sup>3</sup> (21.1 kW/dm<sup>3</sup>). Dabei teilt sich der Ausgangsstrom ohne aktive Symmetrierungsregelung perfekt symmetrisch auf beide Module auf, wodurch ein äusserst effizienter und stabiler Betrieb des Konverters resultiert, was nur dank des neuartigen Snake-Core-Transformators möglich ist.

Die Messresultate der Hardwareprototypen stimmen hervorragend mit den zuvor hergeleiteten Verlustmodellen der verschiedenen Leistungskomponenten überein, weshalb diese Verlustmodelle anschliessend verwendet werden, um mögliche weitere Verbesserungen bezüglich Effizienz der Systeme zu identifizieren. Einer der wichtigsten Punkte, welche in zukünftigen Wandlern die Effizienz noch weiter steigern könnte, ist, die Verzögerungszeit der sekundärseitigen Synchrongleichrichter zu minimieren, da die hohen sekundärseitigen Ströme, in Kombination mit dem Vorwärtsspannungsabfall der antiparallelen Diode der MOSFETs, zu hohen Leitverlusten während der Stromnulldurchgänge führen. Dies ist mit heutigen Halbleitern schwierig, könnte jedoch in Zukunft mit im Halbleiterchip integrierten Synchrongleichrichter-Steuer-ICs erheblich verbessert werden. Alternativ würden nur schon dedizierte Anschlüsse im Gehäuse der Schalter (Kelvin-Kontakte) für die Messung der Drain-Source Spannung über den MOSFETs das Problem entschärfen.

Die in dieser Arbeit erzielten Ergebnisse zeigen klar, dass es nicht reicht, nur eine einzelne Komponente eines kompletten Systems zu verbessern, da die Zusammenhänge zwischen dem Design-Space und dem Performance-Space extrem komplex und oft nicht bis ins letzte Detail analysierbar sind. Sprich, gibt es eine technologische Neuerung/Verbesserung für eine Komponente (z. B. die Entwicklung der Wide-Bandgap Halbleitertechnologie), ist es nicht ausreichend diese Technologie direkt in bestehende Systeme einzubauen, da ihr volles Potential so bei weitem nicht ausgenutzt wird. Um die neuen Möglichkeiten voll auszuschöpfen muss das gesamte System, vom Konzept über die Schaltungstopologie bis zur Optimierung der einzelnen Komponenten, von Grund auf neu analysiert werden. Nur so ist es möglich, neue, effiziente, kompakte und vor allem wettbewerbsfähige Wandler für verschiedene Anwendungen zu entwickeln.

## Abbreviations

| 3-D    | Three-Dimensional                                   |

|--------|-----------------------------------------------------|

| AC     | Alternating Current                                 |

| BCM    | Boundary Conduction Mode                            |

| CCM    | Continuous Conduction Mode                          |

| CNC    | Computerized Numerical Control                      |

| CPU    | Central Processing Unit                             |

| CT     | Current Transformer                                 |

| Cu     |                                                     |

| DAB    | Copper<br>Dual Active Bridge                        |

| DCM    | Dual Active Bridge<br>Discontinuous Conduction Mode |

| DSAB   |                                                     |

| DSAB   | Double-Stacked Active Bridge                        |

|        | Direct Current                                      |

| DCX    | Direct Current Transformer                          |

| EV     | Electric Vehicle                                    |

| Fe     | Iron/Ferrite                                        |

| FEM    | Finite Element Method                               |

| FHA    | Fundamental Harmonic Approximation                  |

| GaN    | Gallium Nitride                                     |

| HEMT   | High-Electron-Mobility Transistor                   |

| HV     | High Voltage                                        |

| IC     | Integrated Circuit                                  |

| ICT    | Information and Communication Technology            |

| IP     | Input Parallel                                      |

| IS     | Input Series                                        |

| IT     | Information Technology                              |

| LC     | Inductor-Capacitor                                  |

| LDO    | Low Drop Out                                        |

| LLC    | Inductor-Inductor-Capacitor                         |

| LV     | Low Voltage                                         |

| MCU    | Microcontroller Unit                                |

| MMF    | Magnetomotive Force                                 |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor   |

| OP     | Output Parallel                                     |

| OS     | Output Series                                       |

| PCB    | Printed Circuit Board                               |

| PE     | Protective Earth                                    |

| PSFB   | Phase-Shifted Full-Bridge                           |

|        | 0                                                   |

| PSU | Power Supply Unit                   |

|-----|-------------------------------------|

| PWM | Pulse-Width Modulation              |

| RMS | Root Mean Square                    |

| SCT | Snake-Core Transformer              |

| Si  | Silicon                             |

| SiC | Silicon Carbide                     |

| SR  | Synchronous Rectifier/Rectification |

| UAV | Unmanned Aerial Vehicles            |

| WBG | Wide Bandgap                        |

| ZCD | Zero-Current Detection              |

| ZCS | Zero-Current Switching              |

| ZVS | Zero-Voltage Switching              |

## Contents

| Ac | knov   | vledgments                                                   | v    |

|----|--------|--------------------------------------------------------------|------|

| Ab | ostrac | t                                                            | vii  |

| Ku | ırzfas | ssung                                                        | ix   |

| Ab | brev   | iations                                                      | xiii |

| 1  | Intr   | oduction                                                     | 1    |

|    | 1.1    | Challenges in Designing Next-Generation Power Supply         |      |

|    |        | Modules                                                      | 3    |

|    | 1.2    | State of the Art of DC/DC Power Supply Modules $\ .\ .\ .$ . | 6    |

|    | 1.3    | Aims and Contributions                                       | 11   |

|    | 1.4    | List of Publications                                         | 12   |

|    |        | 1.4.1 Journal Papers                                         | 12   |

|    |        | 1.4.2 Conference Papers                                      | 13   |

|    |        | 1.4.3 Workshops and Seminars                                 | 13   |

|    | 1.5    | Thesis Outline                                               | 13   |

| _  | т      | le ere & Constant for Comment on 1 Ff direct DC/DC Door      |      |

| 2  | -      | ology & Control for Compact and Efficient DC/DC Power        |      |

|    |        | ply Modules                                                  | 17   |

|    | 2.1    | Introduction                                                 | 17   |

|    | 2.2    | Topology Selection                                           | 18   |

|    |        | 2.2.1 Topology Options                                       | 18   |

|    |        | 2.2.2 Conceptualization                                      | 21   |

|    | 2.3    | Improving the Controllability of LLC Resonant Converters .   | 24   |

|    |        | 2.3.1 Gain Analysis                                          | 25   |

|    |        | 2.3.2 Resonant-Inductor Selection                            | 27   |

|    |        | 2.3.3 Frequency/Phase-Shift Synergetic Control               | 29   |

|    | 2.4    | Summary                                                      | 36   |

| 3  | "Sna   | ke-Core" Transformer                                         | 39   |

|    | 3.1    | Introduction                                                 | 39   |

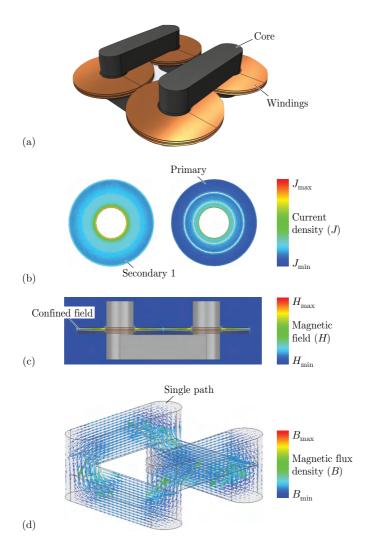

|    | 3.2    | Transformer Concept and Analysis                             | 40   |

|    |        | 3.2.1 Transformer Implementation                             | 41   |

|    |        | 3.2.2 Finite-Element-Method (FEM) Simulations                | 45   |

|    |        | 3.2.3 Circulating-Currents Analysis                          | 48   |

|    | 3.3    | Experimental Results                                         | 52   |

|                                                | 3.4  | Summary                                                              | 59           |

|------------------------------------------------|------|----------------------------------------------------------------------|--------------|

| 4                                              |      | Resonant Converter with Boundary/Discontinuous-Conduce<br>le Control | ction-<br>61 |

|                                                | 4.1  | Introduction                                                         | 61           |

|                                                | 4.2  | Hardware Prototype                                                   | 62           |

|                                                |      | 4.2.1 Overview                                                       | 62           |

|                                                |      | 4.2.2 BCM versus CCM                                                 | 65           |

|                                                |      | 4.2.3 Implementation of the Proposed Control Scheme                  | 67           |

|                                                |      | 4.2.4 Experimental Performance                                       | 74           |

|                                                | 4.3  | Design Improvements                                                  | 76           |

|                                                |      | 4.3.1 Additional Degree of Freedom                                   | 76           |

|                                                |      | 4.3.2 Design Considerations                                          | 79           |

|                                                |      | 4.3.3 Analysis Techniques & Loss Models                              | 81           |

|                                                |      | 4.3.4 Performance Comparison                                         | 82           |

|                                                |      | 4.3.5 Next-Iteration Hardware Prototype                              | 83           |

|                                                | 4.4  | Summary                                                              | 86           |

| 5 LLC Resonant Converter with Continuous/Disco |      | Resonant Converter with Continuous/Discontinuous-                    | -            |

|                                                | Con  | duction-Mode Control                                                 | 87           |

|                                                | 5.1  | Introduction                                                         | 87           |

|                                                | 5.2  | Converter Design                                                     | 88           |

|                                                |      | 5.2.1 Topology, Gain Analysis, and Control                           | 88           |

|                                                |      | 5.2.2 PCB-Integrated Transformer                                     | 93           |

|                                                |      | 5.2.3 PCB-Integrated Inductor                                        | 105          |

|                                                |      | 5.2.4 Capacitor and Power-Semiconductor Selection                    | 107          |

|                                                | 5.3  | Hardware Prototype                                                   | 108          |

|                                                | 5.4  | Efficiency Barriers                                                  | 116          |

|                                                | 5.5  | Summary                                                              | 122          |

| 6                                              | Inpu | nt-Parallel/Output-Parallel Association of LLC Resonant              |              |

|                                                | Con  |                                                                      | 123          |

|                                                | 6.1  | Introduction                                                         | 123          |

|                                                | 6.2  | Next-Generation DC/DC Module                                         | 124          |

|                                                | 6.3  | Paralleled DC/DC Modules                                             | 127          |

|                                                | 6.4  | Summary                                                              | 132          |

| 7   | Con   | clusion and Outlook                                        | 135 |

|-----|-------|------------------------------------------------------------|-----|

|     | 7.1   | Paving the Way Toward Next-Generation Power Supplies       | 135 |

|     | 7.2   | Main Contributions and Key Findings                        | 136 |

|     | 7.3   | Outlook and Future Research                                | 139 |

| Ap  | pend  | lices                                                      | 141 |

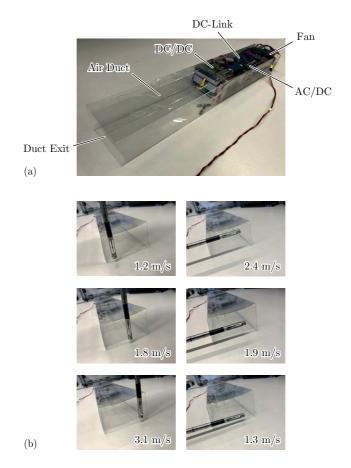

| A   | Pow   | er-Supply-Unit Heat Extraction                             | 143 |

|     | A.1   | Natural Convection Cooling                                 | 143 |

|     | A.2   | Forced Convection Cooling                                  | 144 |

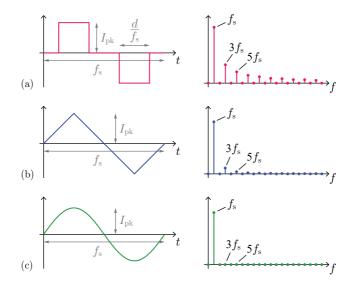

| В   | Har   | monic Analysis of Current Waveforms                        | 147 |

|     | B.1   | Introduction                                               | 147 |

|     | B.2   | Calculating the RMS-to-Average Ratios of Different Current |     |

|     |       | Waveforms                                                  | 148 |

| С   | Mat   | rix-Transformer Essentials                                 | 151 |

|     | C.1   | Calculation of Current and Flux Densities                  | 151 |

|     | C.2   |                                                            | 153 |

|     |       | C.2.1 General Model                                        | 153 |

|     |       | C.2.2 Particular Cases                                     | 156 |

|     |       | C.2.3 Circulating Currents                                 | 159 |

| Bil | bliog | raphy                                                      | 171 |

| Cu  | rricu | ılum Vitae                                                 | 183 |

# Introduction

A FTER centuries of curiosity around electrical phenomena—with ancient Egyptians already aware of shocks from electric fish even 2750 years before Christ [1]—and a rather slow progress in electrical science, the late 19th century would be marked by the greatest development in electrical engineering that the world had ever seen. Well-known names as Bell, Edison, Tesla, Westinghouse and many others [2] would turn electricity from a scientific curiosity into an essential tool for modern life—and use inventions/discoveries from Volta, Ampère, Faraday, Ohm and Maxwell (among other great scientists) to drive the way we handle energy in our current days. Since then, electric power usage continues to grow rapidly in a contemporary world reliant on electricity for its prime source of energy [3].

Three main areas could be pointed out when discussing the increasinglyelectric future, also illustrated in Fig. 1.1:

- Sustainable Transportation: as all-electric ships, more-electric aircraft and electric heavy-duty vehicles start to become reality along with the on-going electrification of automobiles and the established railway industry [4–6];

- Automated Manufacturing: with electricity as the primary source of energy driving different kinds of robots, CNC systems and automated processes in very efficient and reliable production lines [7,8]; and

- ▶ **Information Processing:** as digital data drives the current society in all spheres imaginable, not only in the day-by-day use of gadgets, but also in the so called Industry 4.0 [9], with server systems and data centers being the brains of what is now named as the Information Age [10].

**Fig. 1.1:** Non-exhaustive examples for the three main areas of electrification of the increasingly-electric future: (a) transportation, here illustrated by the EV Tesla Model S, (b) automated manufacturing, with different kinds of electronically-controlled machines here represented by a collaborative robot from ABB, and (c) information processing, for instance, the hyperscale data centers from Google. Images from the public domain.

In the midst of this very exciting context, power electronics plays a key role in designing supply systems to cope with the ultra-demanding specifications required by the aforementioned areas of electrification. These supplies may, for example, drive servo systems, charge EV batteries or energize IT systems, and the low-voltage output must deliver hundreds of amperes of current while the system still excels in performance [7,8], achieving:

- High power density: with real estate at a premium and supply cabinets already consuming space otherwise available for functional equipment;

- ► **High efficiency:** with supplies rarely operating at full load and heat generation in cabinets driving cooling needs; and

- Low cost: with low initial and/or installation costs as the critical metric for adoption.

Besides the ultra-demanding performance, such power supplies must also be reliable and fulfil hold-up time criteria. This is particularly important for the data industry, but not less critical in the other fields of electrification, as mere moments of power supply downtime potentially translate to costly hours of downtime for the plant. Therefore, the design of a next-generation power supply module that fulfils the demanding specifications of the increasinglyelectric future is a challenging task for the industry that requires attention.

#### 1.1 Challenges in Designing Next-Generation Power Supply Modules

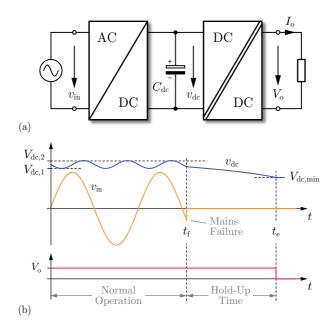

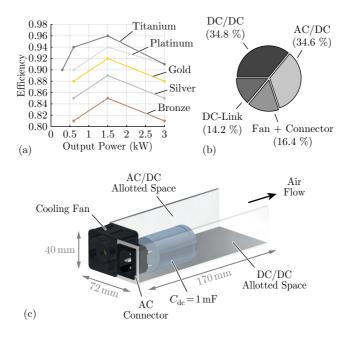

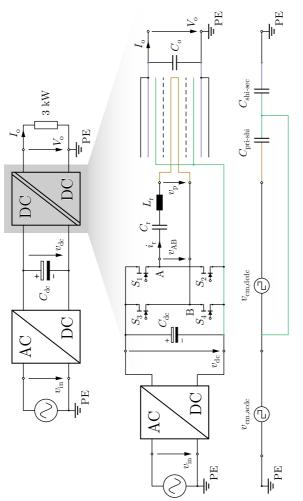

From all three fields of electrification mentioned, power supply units (PSU) for information and communication technology (ICT) have the most demanding requirements. It is therefore reasonable to take server and data-center PSUs as benchmarks to address challenges and derive key specifications for this next-generation power supply module. For the general PSU of Fig. 1.2(a), commercially-available solutions are galvanically-isolated and typically designed for an output power  $(P_0)$  between 2 kW and 3 kW, a low-output voltage  $(V_{0})$  of 12 V, and a single-phase-mains AC input voltage  $(v_{in})$  of 180-270 V at 47-63 Hz [11-13]. Although some hyperscale data centers have adopted the 48 V bus architecture [14-16], 12 V power supplies still dominate industrial applications, specially now that 380 V/400 V DC distribution and direct conversion to 12 V is being considered [17-19]. The PSU form factor in these applications is standardized to one-unit height (1U-44 mm) and to 72 mm width (with exceptions diverging only by few millimeters)-see Fig. 1.3. The length depends on the rated power and ultimately defines the supply's power density, which is linked to its efficiency: if striving for 80-PLUS-Titanium performance [20] (96 % efficiency at 50 % load), typical power densities in off-the-shelf products vary between 60 W/in<sup>3</sup> (3.7 kW/dm<sup>3</sup>) and 70 W/in<sup>3</sup> (4.3 kW/dm<sup>3</sup>) [11,12]. On the other hand, supplies certified for lower efficiencies achieve higher power densities, for instance up to 75 W/in<sup>3</sup> (4.6 kW/dm<sup>3</sup>) in 80-PLUS-Platinum certificates (94 % efficiency at 50 % load) [13].

The low-voltage output in these high-reliability supplies must bridge short mains faults and, with a complete mains failure, hold-up  $V_0$  long enough for a safe shutdown of the digital and physical systems (see Fig. 1.2(b)). This is so critical for continuous line operation that batteries are sometimes added to commercially-available industrial power supplies in this class to extend hold-up time [8]. When batteries are not installed, two stages of conversion is the typically-adopted solution, as the required energy for holding-up  $V_0$  is stored in the DC-link capacitor ( $C_{dc}$ ). The hold-up time requirement could also be met with additional converters, for example with (i) a partial-power pre-regulation converter and a fixed-voltage-ratio DC/DC converter [21], (ii) a hold-up time extension circuit [22], or (iii) a reverse-feeding concept [23]. Each of these solutions adds complexity, size and cost in the form of an additional power stage. Instead, the combination of a low-volume  $C_{dc}$  and a wide-input-voltage-range DC/DC converter offers the most cost-effective and low-complexity solution to meet the hold-up time requirement, and is

**Fig. 1.2:** (a) Industrial power supply block diagram to convert the AC-mains voltage to a low-voltage/high-current DC output. The capacitance of the DC-link capacitor ( $C_{dc}$ ) is mainly determined by the hold-up time requirements during fault conditions, as shown in (b).

**Fig. 1.3:** Lenovo ThinkSystem® server solution from the rear-side perspective, with highlight to the two available power supply units (PSUs) for a 1+1 redundancy scheme.

assumed here as the most promising approach to catapult state-of-the-art PSUs to the performance baseline of the next generation.

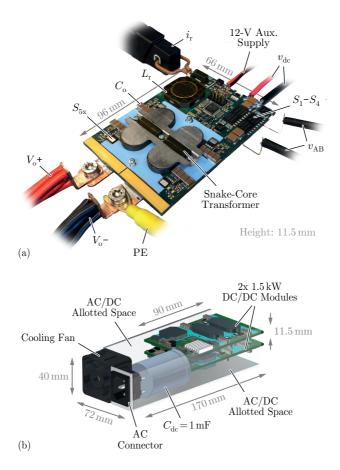

An ambitious industry- and academia-relevant target is to aim for a high-density 3 kW supply with 100 W/in<sup>3</sup> (6.10 kW/dm<sup>3</sup>) that fulfils the 8o-PLUS-Titanium efficiency standard (see Fig. 1.4(a)). For this power density, a volume of 491 cm<sup>3</sup> must be partitioned between all power supply elements, including AC/DC and DC/DC stages, DC-link capacitor, AC connector and cooling fan. Both connector and fan (ideal for this power range [24], see Appendix A) already account for 16 % of the total available volume. Furthermore, taking a typical specific capacitors, e.g. 450*USK1000MEFCSN35X55*),  $C_{dc} = 1 \text{ mF}$  would occupy additional 14 % of the allotted volume, leaving the remainder 70 % to be equally shared between AC/DC and DC/DC stages (see Fig. 1.4(b,c)), and requiring 300 W/in<sup>3</sup> (18.3 kW/dm<sup>3</sup>) designs for both.

**Fig. 1.4:** (a) Efficiency standards of the voluntary certification program 8o-PLUS launched in 2004 to promote efficient energy use in computer PSUs [20]. (b,c) Proposed volume partitioning of a 3kW PSU with  $100 \text{ W/in}^3$  (6.10 kW/dm<sup>3</sup>) to benchmark the next-generation power module.

This 1 mF DC-link capacitor would provide  $t_e - t_f = 10$  ms of hold-up time at 80 % load ( $P_o = 2.4$  kW), calculated from:

$$t_{\rm e} - t_{\rm f} = \frac{\eta_{\rm dc} C_{\rm dc}}{2P_{\rm o}} \left( V_{\rm dc,1}^2 - V_{\rm dc,min}^2 \right), \tag{1.1}$$

fulfilling one typical hold-up-time requirement of highly-compact server PSUs.  $\eta_{dc} = 0.96$  is the DC/DC expected efficiency at 80 % load,  $V_{dc,min} = 300$  V is the minimum allowed DC-link voltage (selected as a good compromise between the remaining stored energy and DC/DC controllability), and  $V_{dc,1}$  is calculated from the  $C_{dc} = 1$  mF voltage ripple:

$$V_{\rm dc,2} - V_{\rm dc,1} = \frac{P_{\rm o}}{2\pi f \eta_{\rm dc} C_{\rm dc} \frac{V_{\rm dc,2} + V_{\rm dc,1}}{2}},$$

(1.2)

assuming  $(V_{dc,2} + V_{dc,1})/2 = 400 \text{ V}$  as the nominal DC-link voltage and f = 47 Hz as the worst-case  $v_{in}$  frequency. Finally, with all these constraints and assumptions considered, the DC/DC converter would need to operate from  $V_{dc,min} = 300 \text{ V}$  to  $V_{dc,2} = 430 \text{ V}$ , a wide-input-voltage range. This input range is taken as a requirement, knowing that the required PSU power density will not be achieved if additional capacitance is added to narrow this range.

Ultimately, with power-density prescribing such a high switching frequency that soft-switching is required, and initial costs driving the need of full PCB integration (including magnetics), the major design challenge to be addressed is the topology and control of an isolated, soft-switching, PCBintegrated, wide-voltage-range-input, low-voltage-output DC/DC converter which simultaneously meets the efficiency *and* power-density specifications. The efficiency of this converter should be high enough that the PSU is certified as 80-PLUS-Titanium. A converter with such high-demanding prescriptions cannot be found in commercially-available supplies and is titled here as the next-generation DC/DC power supply module, whose specifications are summarized in Tab. 1.1. With the main challenges addressed and key specifications identified, we move to the analysis of state-of-the-art solutions and to the definition of the thesis's contribution and scope.

#### 1.2 State of the Art of DC/DC Power Supply Modules

Literature offers a broad range of solutions concerning DC/DC power modules. The challenges addressed in Section 1.1 and the design constraints of Tab. 1.1

| Full-load output power $(P_{o})$                  | 3 kW                                             |

|---------------------------------------------------|--------------------------------------------------|

| Output voltage ( $V_{\rm o}$ )                    | 12 V                                             |

| Input voltage range ( $V_{dc,min}$ - $V_{dc,2}$ ) | 300 V-430 V                                      |

| Full-load output current $(I_0)$                  | 250 A                                            |

| Power density                                     | 300 W/in <sup>3</sup> (18.3 kW/dm <sup>3</sup> ) |

| Efficiency at 1.5 kW                              | > 0.96                                           |

| Galvanically isolated                             | Yes                                              |

| Soft-switching                                    | Yes                                              |

| PCB-integrated                                    | Yes                                              |

**Tab. 1.1:** Design specifications of the isolated, soft-switching, PCB-integrated DC/DC power module for next-generation PSUs.

help to narrow down this range and to get more specific with the literature review, culminating in the selection of:

- Isolated over non-isolated topologies,

- Regulated over fixed-ratio converters,

- ▶ Wide over narrow input-voltage ranges,

- ► **Simple** over complex control schemes,

- ▶ **PCB** over litz-wire magnetics, and

- **Soft** over hard switching.

Following the survey conducted by [25], where potential topology candidates are sorted out according to the aforementioned categories, two big groups are identified as suitable:

▶ Buck-based topologies: essentially the full-bridge DC/DC converter, the dual-active-bridge (DAB) converter, or topological derivations. These isolated topologies support a wide-input-voltage range, but are hard-switched (over at least part of the regime) and therefore have low efficiency [26–29]. Moreover, due to the lack of soft-switching, these converters require voltage-clamping circuits to avoid voltage overshoots across semiconductor devices (in case of high output current/low output voltage [27]), or passive snubbers further decreasing efficiency, or active snubbers increasing their complexity, or additional resonant networks. They also suffer from currents with high harmonic content and increased conduction losses.

► LLC-based topologies: resonant converters with two, three or more resonant-tank elements, and the LLC combination as the most popular choice. These isolated converters are soft-switched, have low-harmonicdistortion currents and have high efficiencies even at high switching frequencies, but are limited by a narrow input voltage range [30-35] that, in this application, would result in an unreasonably-large DC-link capacitor to meet hold-up specifications. At the extreme of narrow input voltage ranges, DC transformers ("DCX") with a fixed voltage conversion ratio require a full additional pre-regulation stage or, at a minimum, a differential-power pre-regulation stage [21].

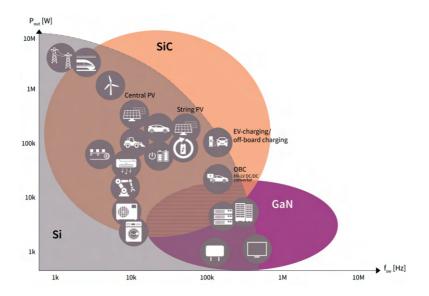

With these two topological groups in mind, a survey of published converters near the design specifications of Tab. 1.1 is conducted and compiled in Tab. 1.2. Three soft-switched, PCB-integrated and 12 V-output converters (see Fig. 1.5) stand out from all researched designs with unprecedented power densities and/or efficiencies, suggesting that soft-switching and PCB-integration are indeed key technologies to enable high-density and efficient DC/DC power modules. Moreover, at least two of these three converters take advantage of wide-bandgap (WBG) power semiconductors in their designs, in particular gallium nitride (GaN), indicating that GaN devices—with excellent specific  $R_{on}$  and zero reverse-recovery losses [36, 37]—are essential to increasing switching frequency and achieving higher power densities (see Fig. 1.6).

**Fig. 1.5:** Examples of PCB-integrated, soft-switched, 12 V-output DC/DC power modules with unprecedented efficiency and/or power density: (a) LLC with matrix transformer from CPES / Virginia Tech [32], (b) double-clamp ZVS from VICOR Corporation [38], and (c) PSFB with current injection from Rompower Energy Systems [39].

| Ref.     | Topology     | Full<br>ZVS | vdc                                     | $V_{\mathbf{o}}$ / $I_{\mathbf{o}}$ | Power Density             | Eff. Eff.<br>(1.0P <sub>o</sub> ) (0.5P <sub>o</sub> ) | Eff.<br>(0.5P <sub>o</sub> ) | PCB-<br>int. |

|----------|--------------|-------------|-----------------------------------------|-------------------------------------|---------------------------|--------------------------------------------------------|------------------------------|--------------|

| [30, 31] | ILC          | Yes         | 380 V                                   | 12 V / 83 A                         | $700 \mathrm{W/in^3}$     | 96.5 %                                                 | 97.1%                        | Yes          |

| [32]     | ILC          | Yes         | 380 V                                   | 12 V / 67 A                         | $900 \mathrm{W/in^3}$     | 97.2 %                                                 | 97.6 %                       | Yes          |

| [33]     | ILC          | Yes         | 200 V-420 V                             | 12 V / 83 A                         | I                         | 91.2~%                                                 | 96.0~%                       | No           |

| [33]     | PSFB         | No          | 200 V-420 V                             | 12 V / 83 A                         | Ι                         | 92.4~%                                                 | 96.0~%                       | No           |

| [41]     | PSFB         | Yes         | 270 V                                   | 22 V / 68 A                         | Ι                         | 93.2%                                                  | 96.0~%                       | No           |

| [42]     | PSFB         | Yes         | $230 \mathrm{V}{	ext{-}}430 \mathrm{V}$ | 14  V / 150  A                      | $170 \mathrm{W/in^3}$     | 95.0%                                                  | 96.0~%                       | Yes          |

| [39, 43] | PSFB         | Yes         | 330  V-420  V                           | 12 V / 83 A                         | $300 \mathrm{W/in^{3**}}$ | 97.8 %*                                                | $99.1\%^*$                   | Yes          |

| [38, 44] | Double-clamp | Yes         | 180 V-420 V                             | 12 V / 33 A                         | 826 W/in <sup>3***</sup>  | 93.0~%                                                 | 93.5%                        | Yes          |

| [29]     | Half-bridge  | No          | $150 \mathrm{V}\text{-}400 \mathrm{V}$  | 12 V / 167 A                        | Ι                         | 91.8~%                                                 | 94.7~%                       | No           |

| [27]     | DAB          | No          | 240 V-450 V                             | 12 V / 182 A                        | $25 \mathrm{W/in^3}$      | 93.5%                                                  | 95.0~%                       | No           |

| [28]     | DSAB         | No          | 350 V-410 V                             | 12 V / 25 A                         | $\approx 20  { m W/in^3}$ | 95.9%                                                  | 97.0~%                       | Yes          |

\*\*Apparently not including auxiliary circuits and control \*\*\*Package without external-required passives and heat sink

**Fig. 1.6:** Power-*versus*-frequency map of suitable semiconductor technologies in selected power-electronics applications, with GaN devices particularly enabling switching-frequency increase by one order of magnitude in kW-range server and data-center power supplies [40].

The CPES/Virginia Tech LLC power module [32] (see Fig. 1.5(a)) reaches 900 W/in<sup>3</sup> and a peak efficiency of 97.6 %, but operates with fixed input voltage and, therefore, does not qualify as a wide-voltage-range converter. The ultra-compact double-clamp *DCM4623xD2J13D0y7z* power module from VI-COR Corporation [38] (see Fig. 1.5(b)) has very high power density with a wide-voltage-range controllability, but has a maximum efficiency of only 93 %. Finally, the ultra-efficient phase-shifted-full-bridge (PSFB) power module from Rompower Energy Systems [39] (see Fig. 1.5(c)) achieves an unprecedented 99.1% peak efficiency with a wide-input-voltage range (without considering driving losses of switching elements [43]), but has limited power density and requires module scaling to reach the desired 3 kW output, which further reduces power density with additional interfacing PCBs and connectors [45]. Although power density could be traded off with efficiency here, this 99 %-efficient converter uses Rompower current-injection technology, which is legally protected [46–49] and adds significant complexity to the

control scheme (with additional voltage, current and temperature measurements [43]).

Indeed, upon reviewing the literature, there is no prior art that meets the demanding specifications of this next-generation DC/DC power module as specified in Tab. 1.1. In particular, wide-input-voltage range, complete soft-switching, and high-current 12 V output with PCB-integrated magnetics are rarely found together. Adding the low-complexity-control-scheme requirement makes the conceptualization, design and implementation of this next-generation DC/DC power module very challenging—but also appropriate to be investigated in the scope of this PhD thesis.

#### 1.3 Aims and Contributions

The goal of this work is to conceptualize, design, model, and fabricate a cost-effective power supply module that meets the demanding specifications of high-reliability industrial applications while maximizing efficiency and power density (Tab. 1.1). More specifically, this wide-range-input, low-voltage-output DC/DC converter has to be isolated, soft-switching, PCB-integrated and regulated by a simple control scheme, a combination that has not been realized previously in the literature.

To achieve these difficult specifications, we leverage GaN power semiconductors to push the switching frequency up by an order of magnitude and improve power density. These high switching frequencies, though, introduce new design challenges to be addressed: firstly, high-frequency magnetics that are cost-effective, efficient, and small are required, for which innovations in PCB integration are proposed and validated. Secondly, a proper topology and control scheme must be selected to achieve soft-switching, low RMSto-average current ratios, controllability, and a wide-input-voltage range, for which we combine the controllability of buck-based converters and the efficiency of soft-switched LLC topologies. Tab. 1.3 shows the impact of each design choice in the general power-module performance. Ultimately, we seek to prove that the design of a next-generation DC/DC power module is only possible by the *combination* of WBG power semiconductors with advanced PCB-integrated magnetics and proper topology/control.

| Goal                 | Means                     |

|----------------------|---------------------------|

| Reliability & safety | Voltage regulation        |

|                      | Hold-up time              |

|                      | Low-complexity system     |

|                      | Galvanic isolation        |

| Low cost             | PCB-integrated magnetics  |

|                      | Low-complexity system     |

| High power density   | High switching frequency  |

|                      | PCB-integrated magnetics  |

| High efficiency      | WBG power semiconductors  |

|                      | Soft switching            |

|                      | Proper topology & control |

**Tab. 1.3:** Key characteristics and technologies that, if combined, will potentially enable reliable, cost-effective, compact and efficient next-generation DC/DC power modules.

#### 1.4 List of Publications

Key insights presented in this thesis have been published in international scientific journals, conference proceedings, or presented at workshops. The publications created as part of this thesis, or in the scope of related projects, are listed below in reverse-chronological order.

#### 1.4.1 Journal Papers

- G. C. Knabben, G. Zulauf, J. Schäfer, J. W. Kolar, M. J. Kasper, J. Azurza Anderson, G. Deboy, "Conceptualization and analysis of a next-generation ultra-compact 1.5-kW PCB-integrated wide-input-voltage-range 12V-output industrial DC/DC converter module," *Electronics* 2021, 10, 2158. DOI: 10.3390/electronics10172158, [PDF].

- D. Neumayr, G. C. Knabben, E. Varescon, D. Bortis and J. W. Kolar, "Comparative evaluation of a full- and partial-power processing active power buffer for ultracompact single-phase DC/AC converter systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 2, pp. 1994-2013, 2021. DOI: 10.1109/JESTPE.2020.2987937, [PDF].

#### 1.4.2 Conference Papers

- G. C. Knabben, J. Schäfer, J. W. Kolar, G. Zulauf, M. J. Kasper and G. Deboy, "Wide-input-voltage-range 3 kW DC-DC converter with hybrid LLC & boundary / discontinuous mode control," in *Proc. of IEEE Applied Power Electronics Conference and Exposition (APEC)*, March 2020. DOI: 10.1109/APEC39645.2020.9124410, [PDF].

- M. J. Kasper, L. Peluso, G. Deboy, G. Knabben, T. Guillod and J. W. Kolar, "Ultra-high power density server supplies employing GaN power semiconductors and PCB-integrated magnetics," in *Proc. of International Conference on Integrated Power Electronics Systems (CIPS)*, March 2020. DOI: not available, [PDF].

- G. C. Knabben, J. Schäfer, L. Peluso, J. W. Kolar, M. J. Kasper and G. Deboy, "New PCB winding "snake-core" matrix transformer for ultra-compact wide DC input voltage range hybrid B+DCM resonant server power supply," in *Proc. of IEEE International Power Electronics and Application Conference and Exposition (PEAC)*, Nov 2018. DOI: 10.1109/PEAC.2018.8590430, [PDF].

Best-Presenter-at-the-Session Award

G. C. Knabben, D. Neumayr and J. W. Kolar, "Constant duty cycle sinusoidal output inverter with sine amplitude modulated high frequency link," in *Proc. of IEEE Applied Power Electronics Conference and Exposition (APEC)*, March 2018. DOI: 10.1109/APEC.2018.8341372, [PDF].

#### 1.4.3 Workshops and Seminars

▶ **G. C. Knabben**, J. Schäfer, J. W. Kolar, M. J. Kasper, and G. Deboy, "Key enablers for ultra-compact server power supplies," presented at *Tech-Talks at Infineon Technologies Austria AG*, Villach, Austria, Oct 2020. DOI: not available, [PDF].

#### 1.5 Thesis Outline

According to the goals and contributions mentioned above, the content of the thesis is divided into five main chapters and conclusions. All the chapters can be read independently, since the interdependencies have been reduced to the strict minimum.

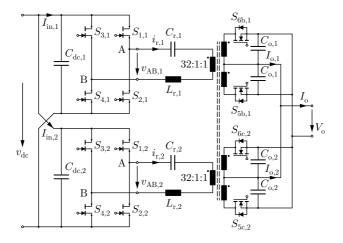

- ► **Chapter 2** identifies a suitable low-complexity circuit topology and control scheme that operates across the wide-input-voltage range with complete soft-switching, implementing a new hybrid wide-input-range LLC control for a topology that includes a full-bridge primary and a matrix transformer for multiple high-current outputs. With this topology, the converter can operate efficiently at higher frequencies and high output currents with PCB-integrated magnetics, significantly improving power density compared to state-of-the-art designs.

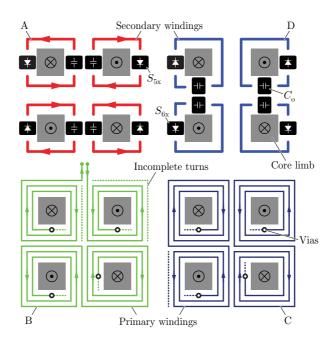

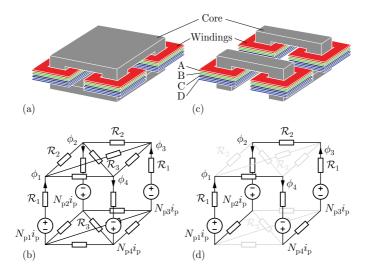

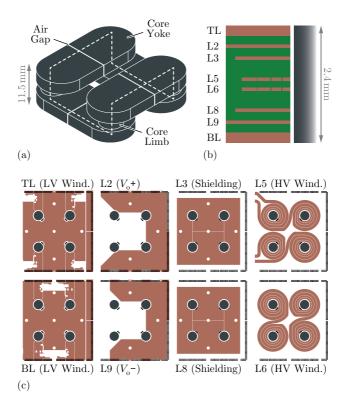

- Chapter 3 introduces the "Snake-Core" Transformer, a PCB-integrated matrix transformer that has a single path for the magnetic flux, ensuring equal flux linkage of parallel-connected secondary windings despite possible geometric PCB-layout asymmetries or reluctance imbalances. This approach avoids the emergence of circulating currents between parallel-connected secondary windings and guarantees, at the same time, equal secondary-side voltages in power supplies with multiple isolated outputs.

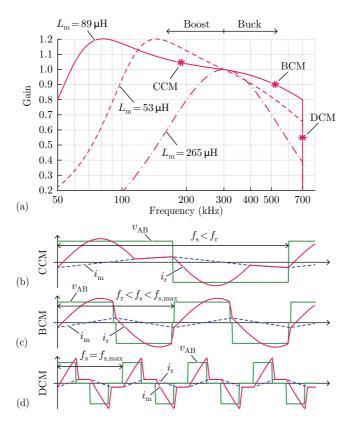

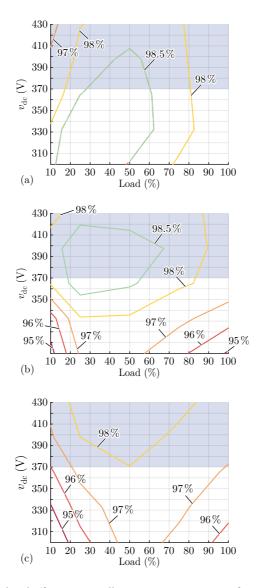

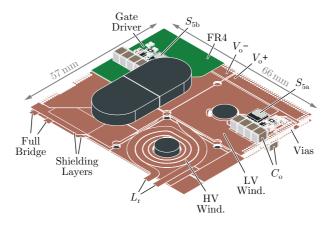

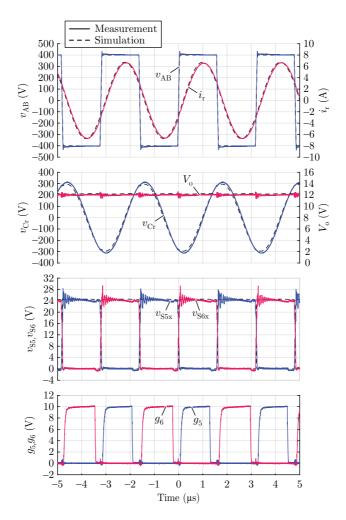

- ▶ **Chapter 4** demonstrates a wide-input-voltage-range, 370 V-430 V-to-12 V, 3 kW DC/DC series-resonant converter that validates the control method and transformer design discussed in Chapter 2 and Chapter 3. The converter achieves 350 W/in<sup>3</sup> (21.4 kW/dm<sup>3</sup>) power density and 94 % peak efficiency while operating from 300 V to 430 V input voltage and from 10 % to full load. An improved design additionally utilizes the magnetizing inductance for boost operation and a performance comparison is finally explored for comparing the improved design with the presented hardware demonstrator and with conventional LLC converters.

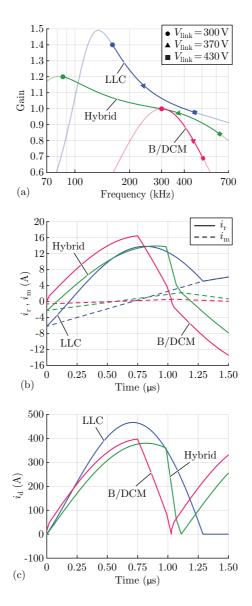

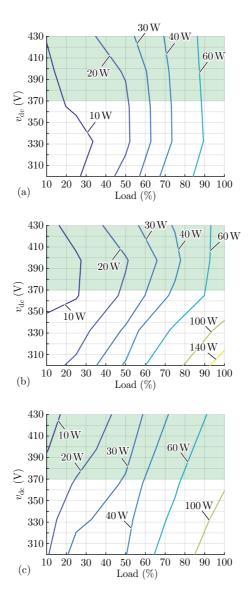

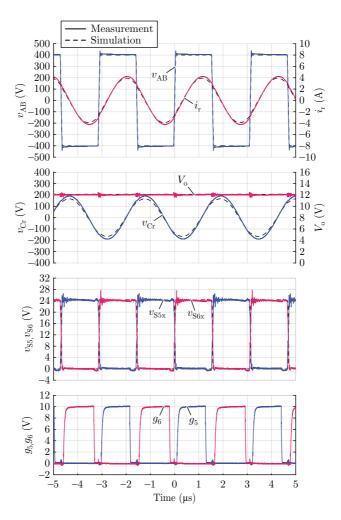

- ▶ **Chapter 5** presents the conceptualization, design, modelling, fabrication, and characterization of a 1.5 kW, 12 V-output DC/DC converter for industrial power supplies that is required to operate across a wide 300 V-430 V input voltage range. The converter achieves close to 96% peak efficiency with a power density of 337 W/in<sup>3</sup> (20.6 kW/dm<sup>3</sup>), excellent matching to the derived loss models, and zero-voltage switching even down to zero load. The loss models are used to identify improvements to further boost efficiency, the most important of which is the minimization of delay times in synchronous rectification.

- Chapter 6 demonstrates a 12 V-output, 300 V-430 V-input DC/DC power module that takes advantage of the the loss models and effi-

ciency analysis developed in Chapter 5 to improve efficiency at all load levels. This 1.5 kW hardware prototype eliminates nearly 25 % of converter losses for a peak efficiency of nearly 97 % with a power density of  $308 \text{ W/in}^3$  ( $18.8 \text{ kW/dm}^3$ ). Two 1.5 kW modules are then paralleled to achieve 3 kW output power at 12 V and  $345 \text{ W/in}^3$  ( $21.1 \text{ kW/dm}^3$ ) with ideal current sharing between the secondary outputs and no drop in efficiency from a single module.

Chapter 7 concludes the thesis and briefly summarizes the main contributions and key findings. In addition, an outlook on possible future research is provided.

## 2

## Topology & Control for Compact and Efficient DC/DC Power Supply Modules

#### Chapter Abstract —

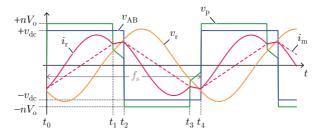

Proper topology and control-scheme selection is crucial for designing high-performance converters. In this chapter, a suitable topology for an isolated, wide-voltage-range-input, high-current-output DC/DC converter is conceptualized. First, state-of-the-art topologies are analysed and compared. Three candidates are considered for the application: the fullbridge converter, the dual-active-bridge converter, and the LLC converter. Because of its soft-switching properties, low-harmonic currents and synchronous rectification, the LLC converter with center-tap rectifier and matrix transformer is chosen as the most promising topology to fulfil the high-demanding requirements. The remainder of the chapter analyses alternative control strategies to overcome the issue of controllability in LLC converters, making them suitable for wide-input-voltage-range applications while still efficient. Two main techniques are described as key to extend the LLC converter gain range and keep high efficiency: a proper selection of the resonant inductor, and the synergetic control of frequency and phase-shift.

#### 2.1 Introduction

A key power conversion stage in a broad range of emerging applications is a kW-scale, high-step-down-ratio DC/DC converter with a 12 V output. In electric vehicles, for example, this stage converts the high-voltage battery output, which typically varies between 250 V and 450 V, to 12 V for chassis electronics [50]. In data centers, the output of a mains-connected PFC rectifier is converted to supply the 12 V distribution bus, with nominal input voltage near 400 V and fault operation required down to 300 V [51]. Similar specifications are also required in industrial automated manufacturing [52]. These diverse applications feature common demands for this 12 V DC/DC converter: exceptional power density, high efficiency and a wide-input-voltage range, beside other key specifications (see Tab. 1.1).

Previous approaches to meet the given requirements are limited by the tradeoff between high efficiency and wide-input-voltage range: LLC-based, soft-switched designs achieve high efficiency within a narrow input-voltage range [30–35] while buck-based topologies are lossy but can achieve the required range [26–29]. A design that combines the best features of both approaches is, however, mandatory in order to comply with the design specifications of Tab. 1.1, where we require high efficiency despite the large full-power output current and a tightly-regulated output voltage throughout the wide-input-voltage range.

#### 2.2 Topology Selection

The topology challenges are driven by the combination of wide-input-voltage range (needed for hold-up time requirements) and high performance, as discussed in Section 1.2. We seek a low-complexity topology and control scheme, which eliminates approaches such as (i) DCX transformers, which require pre-regulation to fix the input voltage to the DC/DC module [21], (ii) additional hold-up time extensions circuits, which require a full additional converter module [22], and (iii) reverse-feeding for hold-up time, which adds significant control complexity to the DC/DC module [23]. Instead, the aim is to use a topology that can be controlled—with minimal complexity—across a wide gain range, and that maintains soft-switching throughout the full load and voltage ranges.

#### 2.2.1 Topology Options

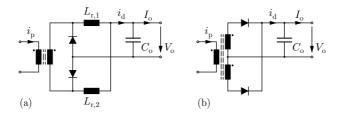

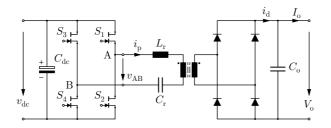

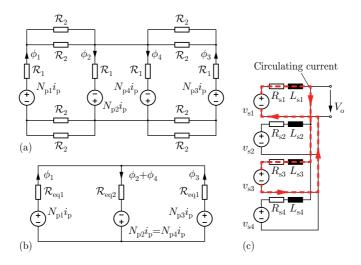

The full-bridge DC/DC converter with phase-shift control (see Fig. 2.1) [33, 39, 41–43, 53–63] is an isolated topology typically selected in applications where controllability throughout wide-voltage ranges is required. This converter consists of a full-bridge arrangement of power semiconductors that switches with high frequency and phase-shift modulation (between the bridge legs), imposing a square-voltage waveform across the primary side of the trans-

former that can have its duty cycle adjusted. The resulting AC-voltage on the transformer's secondary side is rectified and applied to an output LC network that filters the modulated waveform and builds up the output DC voltage. The main advantages of this topology are full transformer usage with positive and negative excitation, output-current-control capability through the output inductor, fixed-frequency operation for optimal component design, and wide-range controllability with phase-shift modulation. These advantages come with the cost of multiple elements in the high-output-current path (particularly the output inductor), square current waveforms with high harmonic content (see Appendix B), and hard-switching. Alternatively, the secondary-side diode bridge could be replaced by the current-doubler topology of Fig. 2.2(a) [64], leading to lower semiconductor count and splitting the high output current into two inductors (for lower conductions losses).

**Fig. 2.1:** Phase-shifted-full-bridge (PSFB) DC/DC converter with galvanic isolation and passive secondary-side rectification. A phase shift between the two bridge legs controls the energy transfer in this topology.

**Fig. 2.2:** Current-doubler (a) and center-tap (b) circuits as alternative output switching stages to, respectively, the full-bridge and the LLC topologies.

Another potential topology is the dual-active-bridge (DAB) converter (see Fig. 2.3) [27, 28, 65-74], which achieves higher efficiencies in high-outputcurrent applications as the inductor is placed on the high-voltage side (where currents are smaller and less conduction losses are expected), and zero-voltage switching (ZVS) is achieved in all semiconductors for at least part of the operating range. It also offers fixed-frequency operation and tight outputvoltage regulation throughout a wide-input-voltage range, with phase-shift control between the active bridges. As a topological disadvantage, the devices' turn-off happens typically with high currents, resulting in larger switching losses when compared to topologies with both zero-voltage and zero-current switching (ZVS and ZCS). Furthermore, the triangular shape of the currents contains harmonics that, though not as large as in the full-bridge topology (see Appendix B), lead to conduction losses-specially in the transformer windings, where losses are frequency-dependent. Due to the two active bridges, a more elaborated gating with signal isolators is also required, adding complexity to the overall system.

**Fig. 2.3:** Dual-active-bridge (DAB) converter with galvanic isolation. This converter is typically controlled by applying a phase-shift between the two active bridges.

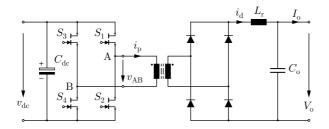

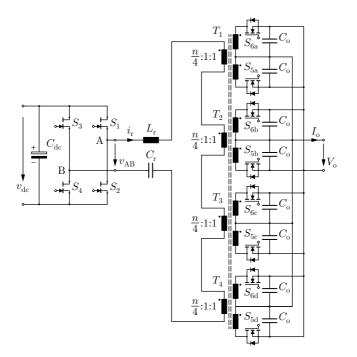

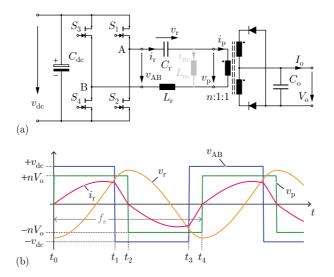

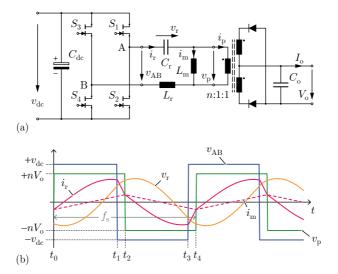

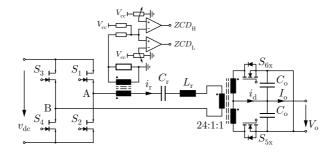

As a third option, LLC topologies (see Fig. 2.4) [30–33,75–83] are capable of converting energy with very low harmonic content (cf. Appendix B) and ZVS throughout the full load range. Moreover, due to the sinusoidal shape of the currents, secondary-side semiconductors switch with ZCS and primaryside devices with very low currents (just the minimum for ZVS), making this topology the most efficient choice for high-output-current applications. Further improvements in efficiency and simplicity can be achieved by replacing the diode-bridge rectifier stage with the center-tap circuit of Fig. 2.2(b) [84] for a lower semiconductor count and lower conduction losses. The main drawback of LLC converters, however, lies in their control method. To keep the desired sinewave shape for ZCS and low-harmonic currents, the energy transfer is controlled by means of frequency modulation, which makes the topology inefficient for wide-voltage-range applications.

**Fig. 2.4:** LLC resonant converter with galvanic isolation and passive secondaryside rectification. The energy transfer in this converter is controlled by frequency modulation of the primary-side full-bridge.

As discussed in Section 1.2, and recalled in Section 2.1, the challenge is to combine the controllability of buck-based converters, which enables a wide-input-voltage range, with the high efficiency of LLC-based resonant topologies, that feature low-harmonic currents and soft-switching (ZVS and ZCS) across the full load and voltage ranges. As a first step toward this goal, we seek to derive a topology that is LLC-based and can handle high output currents, benefiting from the soft-switching properties and low-harmonic currents of LLC converters. Next, alternative control approaches that can handle wide-input-voltage ranges are proposed, culminating in the derivation of an efficient LLC-based topology with wide-voltage-range controllability.

### 2.2.2 Conceptualization

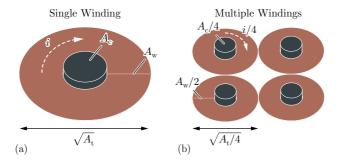

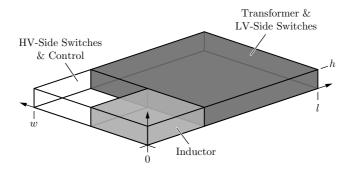

A key component of next-generation DC/DC power supply modules is the PCB-integrated transformer, which must handle high output currents while still being compact and efficient. With the winding-geometry parameters of a generic PCB transformer shown in Fig. 2.5(a), the current density in the secondary winding can be calculated (cf. Appendix C) as:

$$J_{\rm pk} = \frac{\pi N_{\rm s} I_{\rm o}}{2A_{\rm w}},\tag{2.1}$$

while the flux density in the core is:

$$B_{\rm pk} = \frac{V_{\rm o}}{4N_{\rm s}f_{\rm s}A_{\rm c}}.$$

(2.2)

According to Ohm's law and Steinmetz's equation [85], these two parameters can be directly related to winding  $(P_{v,w})$  and core  $(P_{v,c})$  volumetric losses:

$$P_{\rm v,w} = \frac{J_{\rm pk}^2}{2\sigma} \tag{2.3}$$

$$P_{\rm v,c} = k_{\rm c} f_{\rm s}^{\alpha} B_{\rm pk}^{\beta}, \qquad (2.4)$$

showing that winding and core losses are proportional to  $J_{\rm pk}^2$  and  $B_{\rm pk}^{2-1}$ , respectively. It becomes clear from the equations that a high-current, low-voltage output will potentially lead to higher winding losses against core losses. Adding the requirement of PCB integration, with low winding cross-sectional areas ( $A_w$ ), makes the design of such a transformer very challenging. The formulas also reveal that the secondary-winding number of turns ( $N_s$ ) is a key parameter that can be tweaked to rebalance core and winding losses for an optimized overall transformer loss. But with the challenging requirements of this design ( $V_0 = 12$  V,  $I_0 = 250$  A),  $N_s$  must be reduced to the strict minimum of a single turn ( $N_s = 1$ ), not yet being optimal.

**Fig. 2.5:** (a) Illustrative scheme of a PCB-integrated, single-turn secondary-side winding with  $A_w$  window area,  $A_c$  core cross-section area,  $A_t$  total footprint area, and current *i*. (b) Winding-loss minimization at the expense of increased core loss by means of a multi-output (matrix) structure with paralleled windings that reduces the current density for the shown arrangement by a factor of 2 for a fixed total footprint area  $A_t$  and fixed current *i*.

To further improve the balance of core and winding losses, the high output current is divided among multiple windings and rectifiers, with in-

<sup>&</sup>lt;sup>1</sup>Assuming a typical  $\beta = 2$  for core materials in this application.

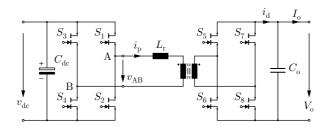

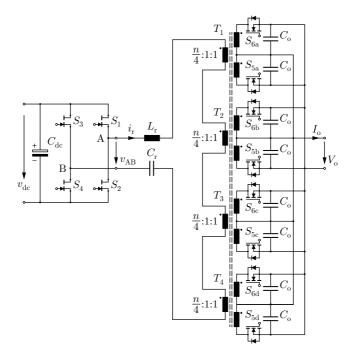

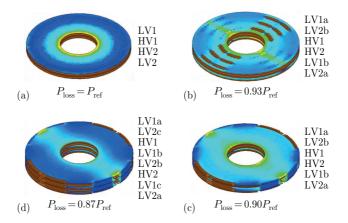

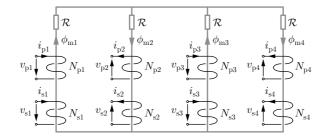

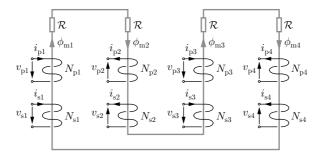

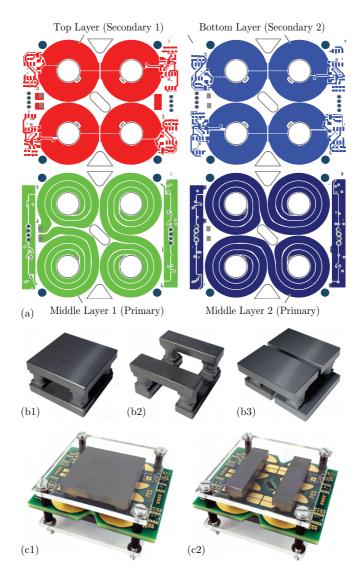

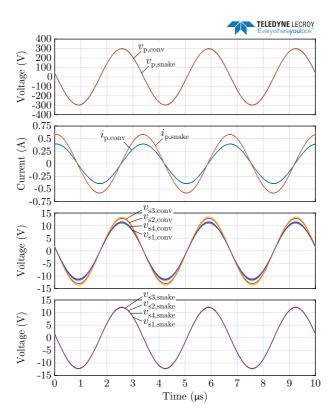

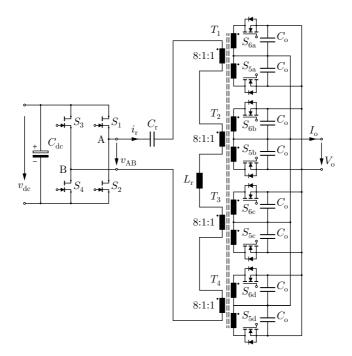

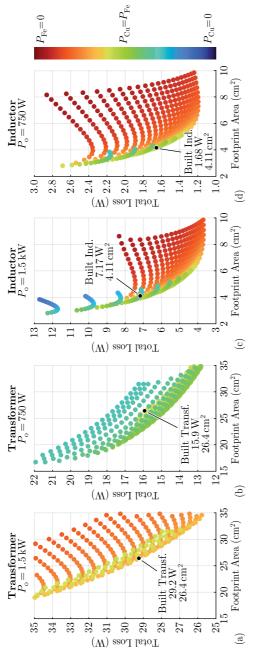

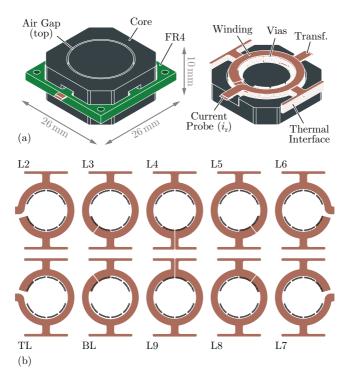

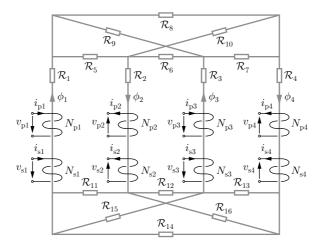

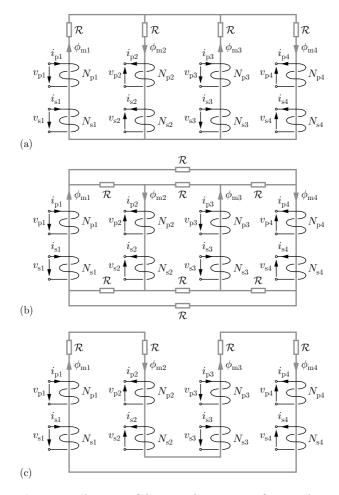

spiration drawn from matrix transformers used in state-of-the-art LLC designs [30-32]. As shown in Fig. 2.6, the utilization of four identical subtransformers  $(T_1 - T_4)$ -with primary windings connected in series and singleturn secondary windings connected in parallel-allows to split the output current among four secondary stages and to have only one primary-side connection to the high-voltage switching stage. The optimal number of subtransformers is selected to balance the copper and core losses. We eliminate the choices with an odd number of secondary windings, which would yield an asymmetrical structure, a complex core shape, or unnecessarily-higher core losses. 1 or 2 sub-transformers does not sufficiently reduce copper losses, while 8 sub-transformers would yield a complicated core structure with potentially higher core losses. Therefore, for the particular constraints of this design-and especially around PCB integration, which limits the available copper thickness-a proper copper-to-core loss ratio is achieved with 4 subtransformers, as validated later with experimental results. This multi-output, matrix structure with 4 paralleled outputs reduces the copper loss by a factor of 4 over a single output with the same footprint area  $(A_t)$ , as the current density reduces by a factor of 2 (see Fig. 2.5(b)). Ultimately, the optimal  $A_{\rm w}$ -to- $A_{\rm c}$ ratio between winding window area and core cross-sectional area must be selected based on a Pareto-optimization from copper and core loss models, which is developed and detailed later in this thesis.

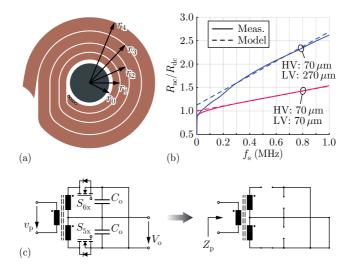

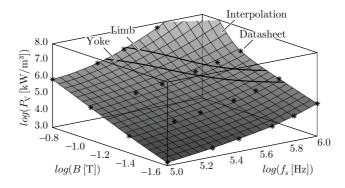

For the remainder elements of the topology in Fig. 2.6, a center-tapped rectifying stage is selected for the secondary side, a circuit that features a low semiconductor count, zero-voltage and zero-current switching, and no high-current output inductor. Attached to each single-turn secondary winding, synchronous rectifiers with power MOSFETs  $(S_{5x} - S_{6x}, x = [a, b, c, d])$ and close-connected output capacitors  $(C_0)$  are chosen to avoid diode voltage drops, reduce commutation loops and minimize termination losses. Since the transformer secondary windings are directly connected to C<sub>o</sub> (voltage source characteristic), the series-connected primary windings must be excited by a current source, whose waveform should be sinusoidal in order to minimize losses from harmonics (see Appendix B). These sinusoidal currents are generated by a resonant-tank network, which is excited with a rectangular voltage from the primary-side full-bridge  $(S_1 - S_4)$ . GaN devices are chosen for the realization of  $S_1 - S_4$ , with excellent specific  $R_{on}$  and low switching losses and/or zero reverse-recovery losses [36, 37]. Relative to the half-bridge topology, the full-bridge has half of the primary-side current for a given power (with a tank excitation of  $\pm v_{dc}$ , rather than  $\pm \frac{1}{2}v_{dc}$  for the half-bridge), and an additional control variable in the phase-shift between the two bridge legs,

**Fig. 2.6:** Power circuit of the proposed DC/DC converter featuring GaN devices for the primary-side full-bridge, power MOSFETs operating as synchronous rectifiers on the secondary-side, and a series-input, paralleled-output, center-tapped matrix transformer.

during which a variable-length voltage of 0 V can be applied to the tank. This added flexibility of two available control variables (frequency and phase-shift) will be leverage to extend the gain range of the converter without increasing largely the switching frequency as in state-of-the-art solutions.

# 2.3 Improving the Controllability of LLC Resonant Converters

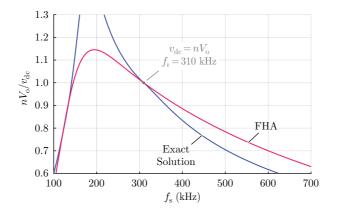

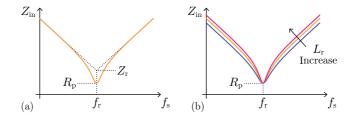

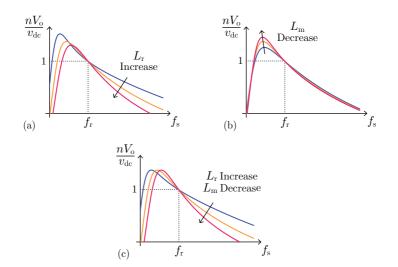

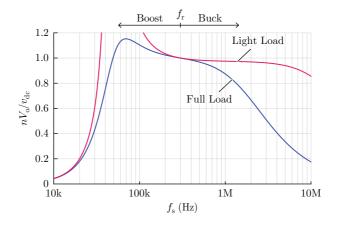

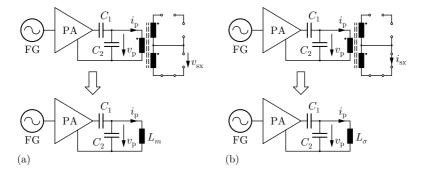

As mentioned earlier in this chapter, the challenge of LLC converters for wideinput-voltage ranges lies in their control method. Hence, some alternatives to extend their gain range will be analysed in this section, in particular (i) the use of an external-to-the-transformer resonant inductor ( $L_r$ ), with higher inductance than in state-of-the-art designs, and (ii) the synergetic control of both full-bridge's frequency and phase-shift.

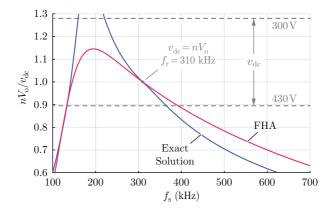

## 2.3.1 Gain Analysis

Before moving to the investigation of alternative control schemes, this subsection briefly discusses the derivation of the topology gain. Knowing the gain characteristic of a converter is essential for designing the control method, as it describes the output-to-input voltage ratio  $\left(\frac{V_o}{v_{dc}}\right)$  as a function of the control variable. In state-of-the-art LLC converters, the control variable that allows gain changing is the switching frequency  $(f_s)$  of the primary-side switching stage. This comes directly from the gain characteristic of such converters, as frequency modulates how much energy the resonant tank can deliver.

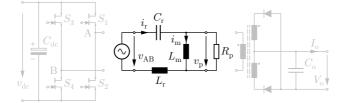

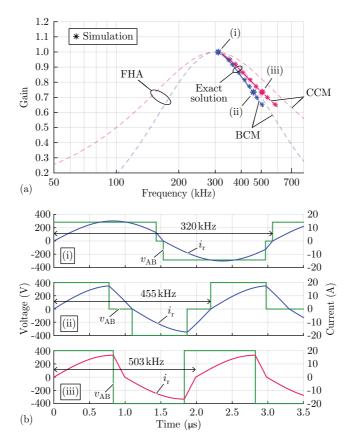

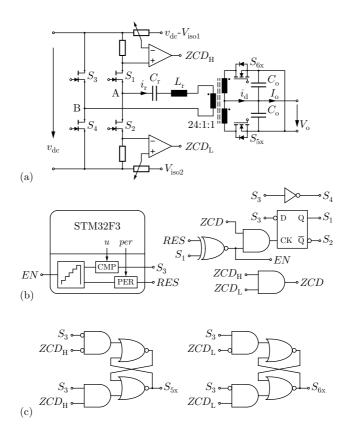

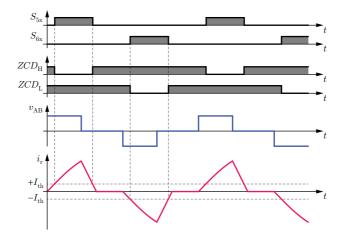

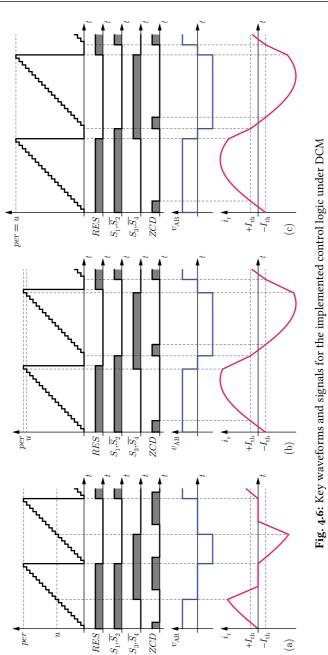

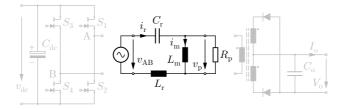

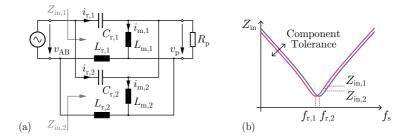

For the selected topology of Fig. 2.6, the simplified circuit of Fig. 2.7 is derived. Here, the full-bridge was replaced by a sinusoidal voltage source with the fundamental frequency of  $v_{AB}$ , and the output stage was replaced by a resistance ( $R_p$ ). This is only possible by means of the fundamental-harmonicapproximation (FHA) [86], an extensively-used tool in LLC converter designs to simplify the gain analysis. The FHA essentially assumes that the resonant tank—which has a high quality factor (Q)—works as a band pass filter and is capable of rejecting all harmonics of the square-voltage excitation except the fundamental component (to which the tank is tuned), allowing a simplified frequency-domain analysis of the circuit. With this method applied to the circuit of Fig. 2.7, straightforward equations can be derived, and the gain (normalized by the transformer turns ratio, n) has a comprehensive analytical solution [84]:

$$\frac{nV_{\rm o}}{v_{\rm dc}} = \frac{(m-1)\left(\frac{f_{\rm s}}{f_{\rm r}}\right)^2}{\sqrt{\left[m\left(\frac{f_{\rm s}}{f_{\rm r}}\right)^2 - 1\right]^2 + Q^2(m-1)^2\left(\frac{f_{\rm s}}{f_{\rm r}}\right)^2 \left[\left(\frac{f_{\rm s}}{f_{\rm r}}\right)^2 - 1\right]^2}}$$

(2.5)

$$f_{\rm r} = \frac{1}{2\pi\sqrt{L_{\rm r}C_{\rm r}}}\tag{2.6}$$

$$m = 1 + \frac{L_{\rm m}}{L_{\rm r}} \tag{2.7}$$

25

$$Q = \frac{Z_{\rm r}}{R_{\rm p}}$$

(2.8)

$$Z_{\rm r} = \sqrt{\frac{L_{\rm r}}{C_{\rm r}}} \tag{2.9}$$

$$R_{\rm p} = \frac{8n^2}{\pi^2} \frac{V_{\rm o}^2}{P_{\rm o}}.$$

(2.10)

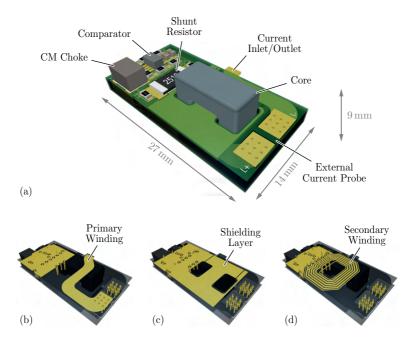

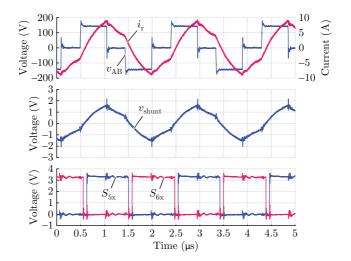

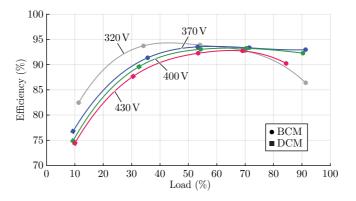

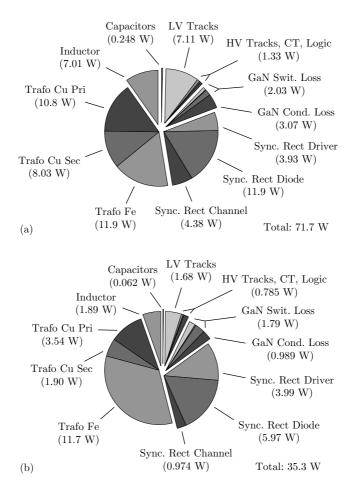

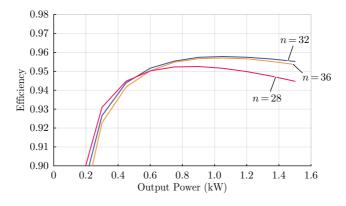

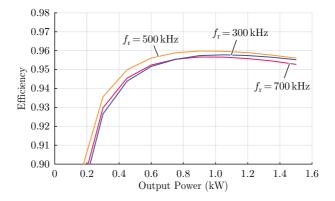

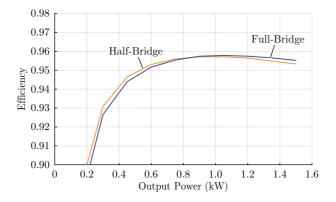

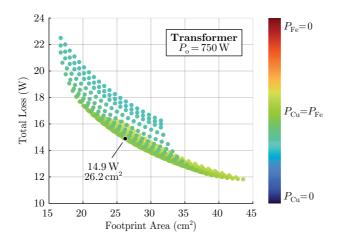

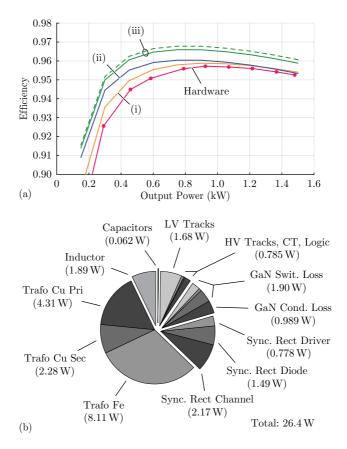

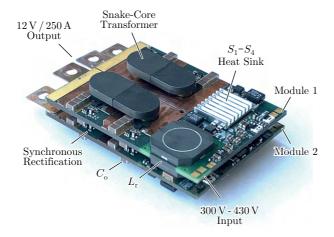

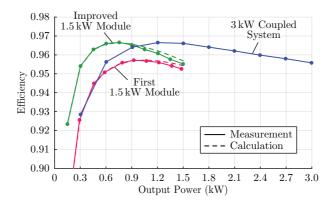

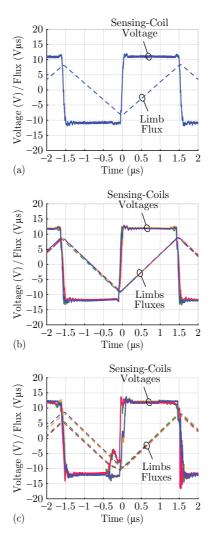

**Fig. 2.7:** Simplified version of the selected topology of Fig. 2.6, using the fundamental-harmonic-approximation (FHA) to capture the fundamental component of switched waveforms.