© 2015 IEEE

Proceedings of the Sixteenth IEEE Workshop on Control and Modeling for Power Electronics (COMPEL 2015), Vancouverl, Canada, Juli 12-15, 2015

# Novel Modulation Concept of the SWISS Rectifier Preventing Input Current Distortions at Sector Boundariess

L. Schrittwieser, J. W. Kolar, T. B. Soeiro

This material is published in order to provide access to research results of the Power Electronic Systems Laboratory / D-ITET / ETH Zurich. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the copyright holder. By choosing to view this document, you agree to all provisions of the copyright laws protecting it.

# Novel Modulation Concept of the SWISS Rectifier Preventing Input Current Distortions at Sector Boundaries

L. Schrittwieser\*, J. W. Kolar\* and T. B. Soeiro<sup>†</sup>

\*Power Electronic Systems Laboratory, ETH Zurich, Switzerland, Email: schrittwieser@lem.ee.ethz.ch <sup>†</sup>ABB Switzerland Ltd., Corporate Research, 5405 Baden-Dättwil, Switzerland

Abstract—This paper describes a new modulation concept for the uni- and bidirectional SWISS rectifier which mitigates input current distortions at the gird voltage sector boundaries. An analytical model is derived and compared to simulations, showing that these distortions are increasing the input current THD significantly. Furthermore, an algorithm is presented which allows the calculation of a temporary pulse width modulation for the SWISS Rectifier's active  $3^{rd}$  harmonic current injection network which mitigates the distortions. Simulations show that the AC input currents' THD can be reduced from 4.2%to 0.8% on a prototype system. The concept is verified by measurement results taken on a bidirectional 7.5 kW SWISS Rectifier prototype.

#### I. INTRODUCTION

The increasing power consumption of data centers and telecommunication equipment has led to a demand for more efficient power supply systems. As data center equipment is an intrinsic DC load, DC distribution systems are expected to provide significant gains in efficiency as rectifier stages of the power supply modules can be omitted. Furthermore, a direct battery buffering of the DC bus voltage allows to omit a dedicated UPS system, which increases efficiency further, improves reliability and reduces capital cost and floor space [1][2]. Accordingly, standards for 380 V DC distribution systems have been created recently [3]. Additionally, similar benefits are expected from DC distribution systems e.g. in office builds and industry [4].

As the DC bus voltage of 380 V is lower than the full-wave rectified voltage of the 400 V AC grid, two-stage systems are normally used. These consist of a power factor correction stage (PFC) connected in series with a DC-DC converter. This is typically also the case for fast chargers of Electric Vehicle batteries which are powered from the three-phase mains [6][7]. In these applications buck-type PFC converters,

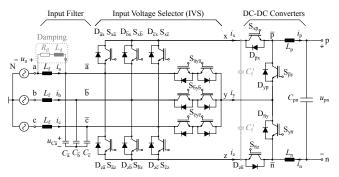

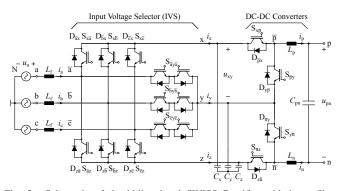

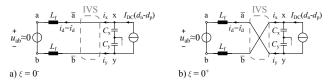

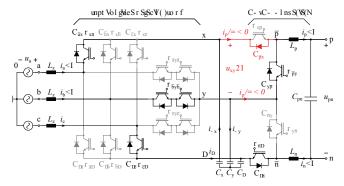

Fig. 1. Schematic of the bidirectional SWISS Rectifier with AC side EMI filter capacitors as introduced in [5]. The input filter damping structures  $(L_d, R_d)$  are not shown for phases b and c for clarity.

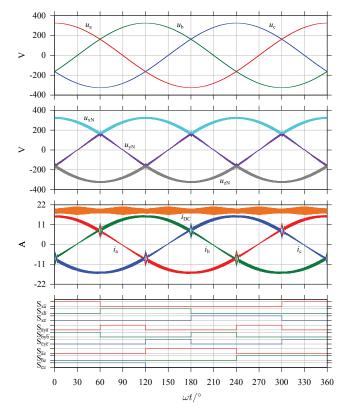

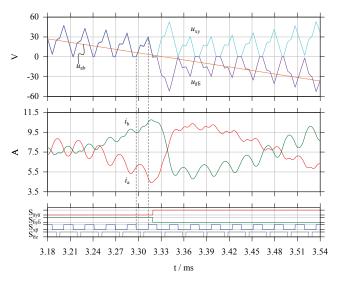

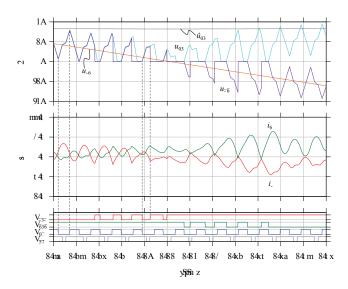

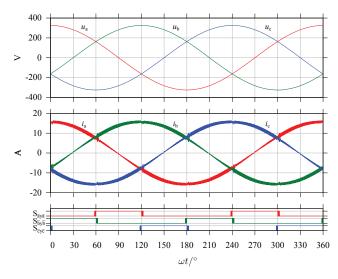

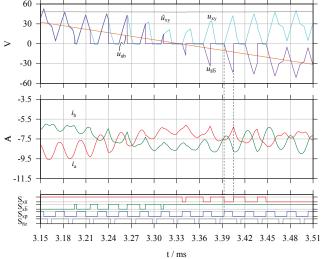

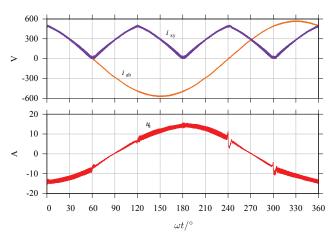

Fig. 2. Simulation results for the SWISS Rectifier specified in **Table I**, in AC-to-DC operation at nominal power.  $u_{\rm xN}$ ,  $u_{\rm yN}$  and  $u_{\rm zN}$  are the DC side voltages of the IVS with reference to the AC grid's neutral N. The distortions of the AC input currents  $i_{\rm a,b,c}$  at intersections of the phase voltages  $u_{\rm a,b,c}$  are visible. A low frequency (< 10 kHz) input current THD of 4.2% results.

like the SWISS Rectifier, are an advantageous alternative, allowing a single-stage conversion between the three-phase mains and a DC bus with lower voltage.

The schematic of the conventional bidirectional SWISS Rectifier, as introduced in [5] and [8], is shown in **Fig. 1**. It consists of an AC side input filter, an Input Voltage Selector (IVS), two DC-DC converters ( $S_{x\bar{p}}$ ,  $S_{\bar{p}y}$ ,  $L_p$  and  $S_{y\bar{n}}$ ,  $S_{z\bar{n}}$ ,  $L_n$ ) and a DC output capacitor  $C_{pn}$ . Additional capacitors  $C'_f$ are used to shorten the commutation paths of the two DC-DC converters. The IVS consists of a three-phase full-wave diode bridge with anti-parallel switches and a third harmonic injection network. Its switches are controlled such that the input phase with highest potential is connected to node x, the one with lowest potential to node z and the remaining phase to node y. Therefore, the injection network's switches  $S_{\bar{a}y\bar{a}}$ ,  $S_{\bar{b}y\bar{b}}$ and  $S_{\bar{c}v\bar{c}}$  operate with twice the mains frequency, while the

TABLE I

Specifications of Simulated SWISS Rectifier

| AC Input Voltage (Line to Neutral) | $U_1 = 230 \mathrm{V_{rms}}$               |

|------------------------------------|--------------------------------------------|

| AC Input Frequency                 | $f = 50 \mathrm{Hz}$                       |

| Switching Frequency                | $f_{\rm s} = 36  \rm kHz$                  |

| Nominal DC Voltage                 | $U_{\rm pn} = 400  \mathrm{V}$             |

| DC Link Capacitance                | $C_{\rm pn} = 470\mu\text{F}$              |

| DC Link Inductance                 | $L_{\rm p,n} = 250\mu{\rm H}$              |

| DC Output Power                    | $P = 7.5 \mathrm{kW}$                      |

| AC Filter Capacitance              | $C_{\bar{a},\bar{b},\bar{c}} = 4.4  \mu F$ |

| DC Filter Capacitance              | $C_{\rm x,v,z} = 4.4 \mu F$                |

| AC Filter Inductance               | $L_{\rm f} = 120  \mu {\rm H}$             |

| AC Filter Damping                  | $L_{\rm d} = 120\mu{\rm H}$                |

| AC Filter Damping                  | $R_{\rm d} = 6.8\Omega$                    |

rectifier switches  $S_{x\bar{a}}$ ,  $S_{x\bar{b}}$ ,  $S_{x\bar{c}}$ ,  $S_{\bar{a}z}$ ,  $S_{\bar{b}z}$  and  $S_{\bar{c}z}$  are operated with mains frequency. This can be seen in **Fig. 2** where the grid voltages and the IVS output voltages  $u_{xN}$ ,  $u_{yN}$  and  $u_{zN}$ are shown.

As described in [5] the two DC-DC converters of the SWISS Rectifier can ideally be controlled in such a way that sinusoidal AC side input currents  $i_a$ ,  $i_b$  and  $i_c$  result. Fig. 2 shows simulation results for the bidirectional 7.5 kW SWISS Rectifier specified in Table I. While the rectifier's input currents are sinusoidal and in phase with the grid voltages, it can be seen that they are distorted at the intersections of the AC mains phase voltages  $u_a$ ,  $u_b$  and  $u_c$ .

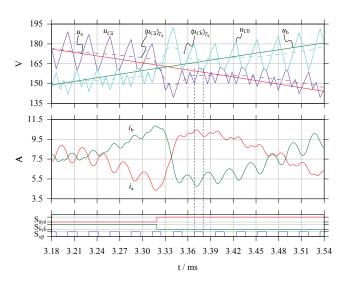

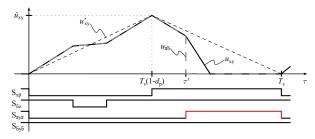

These distortions are caused by the switching frequency voltage ripple across the input filter capacitors  $C_{\bar{a},\bar{b},\bar{c}}$  [9]. This can be seen in Fig. 3 which shows detailed simulation results for the intersection interval of the phase voltages  $u_{\rm a}$  and  $u_{\rm b}$ . Additionally the voltages  $u_{C\bar{a}}$  and  $u_{C\bar{b}}$  across the respective input filter capacitors and their local averages  $\langle u_{C\bar{a}} \rangle_{T_c}$ ,  $\langle u_{C\bar{b}} \rangle_{T_s}$  over one switching period  $T_s$  are shown. Neglecting the voltage drop due to the fundamental of the phase current  $i_{\rm a}$ across  $L_{\rm f}$ , the local average  $\langle u_{\rm C\bar{a}} \rangle_{T_{\rm s}}$  equals the corresponding phase voltage  $u_a$  before the current distortion starts. The same holds for  $\langle u_{C\bar{b}} \rangle_{T_c}$  and  $u_b$ . As the voltages  $u_a$  and  $u_b$  approach each other, the instantaneous voltages  $u_{C\bar{a}}$  and  $u_{C\bar{b}}$  would have to intersect for this to hold true. However, this is not the case as shown in Fig. 3, because the diodes  $D_{\bar{a}x}$  and  $D_{\bar{b}x}$ are starting to conduct once  $u_{ar{a}ar{b}} = u_{Car{a}} - u_{Car{b}}$  reaches zero (cf. Fig. 4). Therefore the local averages  $\langle u_{C\bar{a}} \rangle_{T_a}$  and  $\langle u_{C\bar{b}} \rangle_{T_a}$ no longer matches the corresponding phase voltages  $u_{\rm a}$  and  $u_{\rm b}$ . This impresses a voltage on the input filter inductors  $L_{\rm f}$ , which leads to a distortion of the input currents  $i_{\rm a}$  and  $i_{\rm b}$ , as shown in Fig. 3.

Therefore, in the following a modified circuit topology which reduces the conduction losses in the IVS and decouples the switching operation of the DC-DC converters and the IVS is proposed. For this circuit, an analysis of the current distortion's impact on the converter's THD is given in **Chapter III**. Subsequently, a novel modulation concept, which mitigates the current distortions by temporary pulse width modulation of the IVS switches is introduced in **Chapter IV**. In **Chapter V** measurement results, taken on a 7.5 kW prototype SWISS Rectifier, are presented which verify the theoretical considerations.

## II. DC SIDE FILTER CAPACITORS

As written above, an implementation of the SWISS Rectifier typically requires additional filter capacitors  $C'_{\rm f}$  in order to shorten the commutation paths of the two DC-DC converters

Fig. 3. Detailed simulation results for the first intersection at  $\omega t = 30^{\circ}$  showing the intersecting grid phase voltages  $u_{\rm a}$  and  $u_{\rm b}$  and the corresponding filter capacitor voltages  $u_{\rm C\bar{a}}$  and  $u_{\rm C\bar{b}}$ .  $\langle u_{\rm C\bar{a}} \rangle_{T_{\rm s}}$  is the average of  $u_{\rm C\bar{a}}$  over one switching frequency period  $T_{\rm s}$ . It can be seen that no intersection of  $u_{\rm C\bar{a}}$  and  $u_{\rm C\bar{b}}$  occurs because of  $D_{\rm \bar{a}x}$  and  $D_{\rm \bar{b}x}$  (cf. Fig. 4).

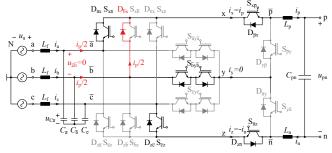

Fig. 4. Schematic of the SWISS Rectifier with  $S_{x\bar{p}}$  turned on, showing the additional conduction path caused by the diode  $D_{\bar{b}x}$  when the voltage  $u_{\bar{a}\bar{b}}$ , i.e. the difference of the voltages of the filter capacitors  $C_{\bar{a}}$  and  $C_{\bar{b}}$  reaches zero. This implies  $u_{\bar{a}\bar{b}} \ge 0$  which means that  $u_{C\bar{a}}$  and  $u_{C\bar{b}}$  cannot intersect (cf. **Fig. 3**).

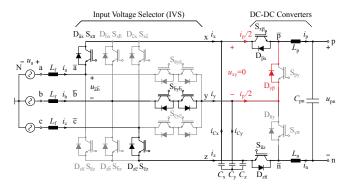

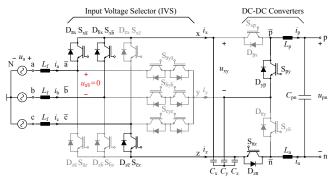

as shown in **Fig. 1**. Therefore, nodes x, y and z form a kind of split DC link which provides the input voltages  $u_{xy}$  and  $u_{yz}$  for the DC-DC converters. However, as the switches of the IVS are operated at mains frequency only, the voltages  $u_{xN}$ ,  $u_{yN}$  and  $u_{zN}$ , are piecewise sinusoidal and hence form a three-phase system (cf. **Fig. 2**). This allows to move the input filter capacitors to the DC side of the IVS as shown in **Fig. 5**.

Throughout this paper a star connection of the filter capacitors ( $C_x$ ,  $C_y$  and  $C_z$ ) is assumed. However, a line-to-line (delta) connection could be used as well. Note that a total of three capacitors of equal capacitance is required in order to load the AC grid symmetrically, even for a delta connection as the voltages at nodes x, y and z are piecewise sinusoidal and form a three phase system within every  $60^{\circ}$  mains sector.

Placing the input filter capacitors on the DC side of the IVS has several advantages: It shortens the commutation paths of the DC-DC converters which means that no additional capacitors  $C'_{\rm f}$  are required. Furthermore, the currents  $i_{\rm x}$ ,  $i_{\rm y}$  and  $i_{\rm z}$  flowing through the IVS are continuous in the case of DC side filter capacitors, as opposed to the original SWISS Rectifier where  $i_{\rm x}$ ,  $i_{\rm y}$  and  $i_{\rm z}$  are discontinuous due to the DC-DC converters. This leads to a reduction of conduction losses

in the IVS switches. Additionally, the DC side capacitors are decoupling the switching operations of the IVS and the DC-DC converters. In the original bidirectional SWISS Rectifier, special commutation sequences are required in the IVS in order not to interrupt the currents  $i_p$  and  $i_n$  in the output inductors [8]. This is not the case with DC side input filter capacitors, as  $C_x$ ,  $C_y$  and  $C_z$  provide a conduction path for the IVS and the DC-DC converter currents at all valid switching states.

This implies that the SWISS Rectifier with DC side filter capacitors can, to some extent, be considered as a system consisting of two individual converters: an IVS stage which performs an AC-to-DC voltage conversion and a DC-DC converter stage which ensures sinusoidal input currents and provides DC output voltage control. Therefore, the IVS and the DC-DC converters can be designed, optimized and operated almost independently of each other. For example, several individual DC-DC converter modules could be fed from a single, larger IVS which provides the xyz (DC) link. In this case, the IVS and the DC-DC converters could even be spatially separated, for example accommodated in different cabinets.

#### **III. INPUT CURRENT DISTORTIONS**

As described **Chapter I** the conventional SWISS Rectifier exhibits AC input current distortions at the intersections of the grid's phase voltages. This is due to the switching frequency voltage ripple at the input filter capacitors which causes additional diodes in the IVS to conduct as shown in **Fig. 4**. Note that the problem persists, even if the input filter capacitors are moved to the DC side of the IVS. In this case the voltage ripple across  $C_x$ ,  $C_y$  and  $C_z$  causes diodes of turned-off DC-DC converter switches to conduct as shown in **Fig. 6**. This results in the same grid current distortions as with AC side filter capacitors, as can be seen from the simulation results shown in **Fig. 7**. An analysis of these current distortions and their impact on the AC currents' THD follows.

In order to derive an analytical model of the current distortions the switching frequency ripple components of the currents in  $L_{\rm f}$  and  $L_{\rm p,n}$  are neglected and  $i_{\rm p} = i_{\rm n} = I_{\rm DC}$  is assumed. The grid voltages and currents are considered to be purely sinusoidal. Due to the phase symmetry it is sufficient to consider only the first intersection of  $u_{\rm a}$  and  $u_{\rm b}$ , i.e.  $\omega t \approx \pi/3$ .

Fig. 5. Schematic of the bidirectional SWISS Rectifier with input filter capacitors placed at the DC side of the IVS. A star connection of filter capacitor is shown here, however a line-to-line (delta) connection could be used as well. The same input filter damping structure as in the original SWISS Rectifier with AC side input filter capacitors can be used.

Fig. 6. Schematic of the SWISS Rectifier with  $S_{x\bar{p}}$  turned on, showing the additional conduction path caused by the diode  $D_{y\bar{p}}$  when the voltage  $u_{xy}$  across the filter capacitors  $C_x$  and  $C_y$  reaches zero. This implies that  $u_{xy} \ge 0$  (cf. Fig. 7).

Fig. 7. Detailed simulation results for the first sector boundary (at  $\omega t \approx 30^{\circ}$ ) with input filter capacitors on the DC side of the IVS ( $C_x$ ,  $C_y$  and  $C_z$ , cf. **Fig. 6**). It can be seen that  $u_{xy}$  cannot become negative because of  $D_{y\bar{p}}$ . This implies that the average over one switching period of the voltage  $u_{\bar{a}\bar{b}}$  at the input of the IVS differs significantly from the corresponding grid voltage  $u_{ab}$ . Accordingly a distortion of the input currents  $i_a$  and  $i_b$  occurs.

The filter capacitors are assumed to have equal capacitance, i.e.  $C_x = C_y = C_z = C_f$ .

As explained above, the switching frequency ripple across the input filter capacitors is the root cause of the current distortions. Therefore, an analytical expression for its peakto-peak value  $\hat{u}_{xy}$  is required. It can be seen from **Fig. 7** that  $u_{xy}$  assumes the peak value at the switching transitions of  $S_{x\bar{p}}$ . It can therefore be calculated as:

$$\hat{u}_{xy} = \frac{1}{C_{f}} \int_{0}^{(1-d_{p})/f_{s}} i_{Cx} - i_{Cy} d\tau$$

$$= \frac{1}{f_{s} C_{f}} \left[ (i_{x} - i_{y}) \left( 1 - d_{p} \right) + I_{DC} \left( d_{n} - d_{p} \right) \right] , \quad (1)$$

where  $d_p$  is the duty cycle of  $S_{x\bar{p}}$  and  $d_n$  is the duty cycle of  $S_{\bar{n}z}$ . Assuming that the SWISS Rectifier is operated such that the AC gird currents are in phase with the gird voltages and that the current distortion is short compared to the grid

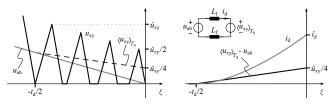

Fig. 8. Drawing (not to scale) of the assumptions made to derive (10). At the beginning of the distortion  $(\xi = -t_d/2)$  the local average  $\langle u_{xy} \rangle_{T_s}$  of  $u_{xy}$  equals the grid voltage  $u_{ab}$ . The difference of  $\langle u_{xy} \rangle_{T_s}$  and  $u_{ab}$  increases linearly until  $\xi = 0$  where it reaches a peak value of  $\dot{u}_{xy}/4$ . This voltage,  $\langle u_{xy} \rangle_{T_s} - u_{ab}$ , drives the distortion current  $i_d$  in the filter inductors of the corresponding phases.

Fig. 9. Simplified schematics of the two phases with intersecting voltages: a) before the IVS changes polarity at  $\xi = 0$  and b) immediately afterwards. The distortion current  $i_d$  flowing in the filter inductors  $L_f$  leads to a rapid change of  $u_{xy}$  after the IVS' switching as  $i_x$  and  $i_y$  change polarity.

voltage period the following simplifications hold:

$$d_{\rm p} = M \cos(\omega t) \approx \frac{M}{2} \qquad \omega t \approx \frac{\pi}{3}$$

(2)

$$d_{\rm n} = M \cos(\omega t - \frac{\pi}{3}) \approx M .$$

(3)

Note that M is the modulation index of the SWISS Rectifier. Neglecting any voltage drops across the switches, diodes and filter inductors, the steady state voltage transfer ratio between AC and DC side is defined as

$$U_{\rm pn} \approx U_{\bar{\rm p}\bar{\rm n}} = \frac{3}{2} M \hat{U}_1 \qquad M = \frac{2 U_{\rm pn}}{3 \hat{U}_1} , \qquad (4)$$

where  $U_1$  is the amplitude of the AC grid's phase voltage [10]. By neglecting the grid frequency component of the filter capacitor current  $i_{Cx,y,z}$  further simplifications can be found:

$$i_{\rm x} = I_{\rm DC} \, d_{\rm p} \approx I_{\rm DC} \frac{M}{2} \tag{5}$$

$$i_{\rm z} = -I_{\rm DC} \, d_{\rm n} \approx -I_{\rm DC} \, M \tag{6}$$

$$i_{\rm y} = -(i_{\rm x} + i_{\rm z}) \tag{7}$$

By combining (1) to (7)  $\hat{u}_{xy}$  can approximated as

$$\hat{u}_{\rm xy} = \frac{I_{\rm DC} M}{2 C_{\rm f} f_{\rm s}} \,. \tag{8}$$

When the line-to-line voltage  $u_{ab}$  becomes smaller than half the voltage ripple  $\hat{u}_{xy}$  calculated in (1) or (8), the current distortion starts. Hence, the time span  $t_d/2$  from the beginning

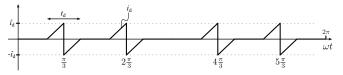

Fig. 10. Simplified distortion current within one mains period assumed for the rms-value calculation used to derive (11).

of the distortion until the zero crossing of the line-to-line voltage  $u_{\rm ab}$  can be derived:

$$u_{\rm ab}\left(\frac{\pi}{3} - \frac{\omega t_{\rm d}}{2}\right) = \sqrt{6} U_1 \sin\left(\frac{\omega t_{\rm d}}{2}\right) \le \frac{\dot{u}_{\rm xy}}{2} ,$$

$$\frac{t_{\rm d}}{2} = \frac{1}{\omega} \arcsin\left(\frac{I_{\rm DC} M}{4\sqrt{6} U_1 C_{\rm f} f_{\rm s}}\right) \approx \frac{1}{\omega} \frac{I_{\rm DC} M}{4\sqrt{6} U_1 C_{\rm f} f_{\rm s}} .$$

(9)

At the beginning of the current distortion  $\langle u_{xy} \rangle_{T_s}$  (the average of  $u_{xy}$  over one switching period  $T_s$ ) is equal to the gird voltage  $u_{ab}$ . As can be seen from **Fig. 7**, in the center of the distortion (at  $u_{ab} = 0$ ), the ripple of  $u_{xy}$  is approximately half the value compared to the point in time where the current distortion starts. This is shown in **Fig. 8** and it enables an estimation of the distortion current's amplitude  $\hat{i}_d$ :

$$\hat{i}_{\rm d} = \frac{1}{2L_{\rm f}} \int_{-t_{\rm d}/2}^{0} u_{\rm xy} \left(\frac{\pi}{3} + \frac{\xi\,\omega}{2}\right) - u_{\rm ab} \left(\frac{\pi}{3} + \frac{\xi\,\omega}{2}\right) d\xi ,$$

$$\approx \frac{1}{2L_{\rm f}} \int_{-t_{\rm d}/2}^{0} \frac{\hat{u}_{\rm xy}}{4} \left(1 + \frac{\xi}{t_{\rm d}/2}\right) d\xi = \frac{\hat{u}_{\rm xy}\,t_{\rm d}}{32L_{\rm f}} . \tag{10}$$

So far only the first half of the distortion, until  $u_{ab}$  reaches zero (at  $\xi = 0$ ) was considered. Once  $u_{ab}$  changes its sign, the IVS commutates in order to reverse the polarity of  $u_{\overline{ab}}$ . This is shown in the simplified schematics in **Fig. 9**. Note, that the polarity reversal of the IVS changes the sign of the IVS' DC side currents  $i_x$  and  $i_y$ . This leads to a considerably higher peak value of  $u_{xy}$  during the first switching period after the polarity reversal. Therefore a higher voltage is applied to the filter inductors  $L_f$  in this cycle which leads to a fast polarity reversal of the distortion current  $i_d$ . This can also be seen in the simulation results shown in **Fig. 7**. The current distortion is therefore approximately symmetric in time around the zero crossing of the line-to-line voltage  $u_{ab}$  (at  $\omega t = \pi/3$ ).

For further analysis the converter's grid currents  $i_{a,b,c}$  are approximated as sum of a fundamental component  $i_{a,b,c(1)}$ which is in phase with the grid voltages and a distortion  $i_d$ . Each phase is distorted four times per gird voltage period. By modeling each distortion as one triangular wave with a period of  $t_d$  and amplitude  $\hat{i}_d$  (cf. **Fig. 10**), the rms value  $I_d$ of  $i_{da,b,c}$  can be calculated as

$$I_{\rm d} = \frac{\hat{i}_{\rm d}}{\sqrt{3}} \sqrt{4 \, t_{\rm d} \, f} \,. \tag{11}$$

In order to generalize (11) for any SWISS Rectifier, the following normalization is applied:

$$C_{\rm f} = \frac{Q_{\rm f}}{3U_1^2 \omega} \quad Q_{\rm f} = P \tan(\phi_1) , \qquad (12)$$

$$L_{\rm f} = L_{\rm f,p.u.} \frac{R_1}{\omega} = L_{\rm f,p.u.} \frac{3U_1^2}{\omega P} \quad R_1 = \frac{3U_1^2}{P} , \quad (13)$$

$$I_{\rm DC} M = \hat{I}_{\rm a,b,c(1)} = \frac{2P}{3\hat{U}_1}$$

(14)

Note that  $\phi_1$  represents the phase shift of the input current's fundamental which results from the reactive power consumption of the input filter capacitors. The reactive power created by the filter inductors is neglected as it is typically much smaller than the  $Q_f$ .

By combining (11) with (8)-(10) and applying the normalizations (12)-(14) the normalized RMS value of the current

Fig. 11. SWISS Rectifier with DC side input filter capacitors and AC-to-DC power transfer during the first intersection of  $u_a$  and  $u_b$ . By turning  $S_{x\bar{a}}$  off and turning on  $S_{\bar{a}y\bar{a}}$  the IVS' output voltage  $u_{\bar{a}\bar{b}}$  is forced to zero.

distortions can be expressed as a function of general system parameters:

$$\frac{I_{\rm d}}{I_{\rm a,b,c(1)}} = \frac{\pi^2}{16 \cdot 3^{5/4}} \frac{1}{L_{\rm f,p.u.}} \left(\frac{f}{f_{\rm s}} \frac{1}{\tan(\phi_1)}\right)^{5/2} , \qquad (15)$$

where  $I_{a,b,c(1)}$  is the RMS value of the AC side input currents' fundamental component at nominal power. This allows an estimation of the current distortions' impact on the rectifier's input current THD. It can be seen that increasing the switching frequency or the input filter capacitors (increasing  $\phi_1$ ) reduces the magnitude of the current distortions with a power of 2.5, while it is inversely proportional to the input filter inductance.

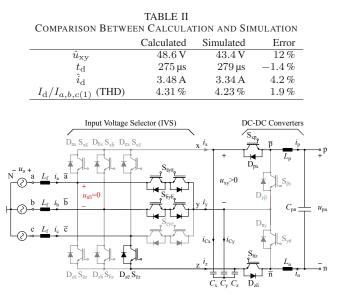

**Table II** shows the numerical results for the equations derived above and compares the values to results obtained from a simulation of the system specified in **Table I**. The calculated values are typically within 10% of the simulation results. Furthermore, it can be seen that the low frequency THD<sup>1</sup> of the rectifier's input currents is 4.2%. A modulation technique eliminating the current distortions is presented in the following.

### IV. MITIGATING DISTORTIONS BY PWM OF THE IVS

As described in the previous chapter, the AC input current distortions can have a significant contribution to the THD of a SWISS Rectifier. For the system specified in **Table I** current distortions with a normalized RMS value of 4.2% result. However, the distortions can be prevented by properly modulating the switches in the IVS as will be shown in the following.

The root cause of the current distortions is the switching frequency voltage ripple across the input filter capacitors and the fact that the voltages  $u_{xy}$  and  $u_{yz}$  cannot be negative (cf. **Fig. 7**). However, if the input filter capacitors are placed on the DC side of the IVS, the IVS can be used to temporarily disconnect the filter capacitors  $C_{x,y,z}$  from the filter inductors  $L_f$  by simultaneously turning on two of the three injection

Fig. 12. Simulation results, showing pulse width modulated injection switches  $S_{\bar{a}y\bar{a}}$  and  $S_{\bar{b}y\bar{b}}$  during the first intersection of  $u_a$  and  $u_b$  which reduces the current distortions. Furthermore, the calculated peak-to-peak ripple of  $u_{xy}$  is shown as  $\hat{u}_{xy}$ .

Fig. 13. Time behavior of the filter capacitor voltage ripple  $u_{xy}$  within one switching period  $T_s$  for DC-to-AC power transfer. The signal  $u'_{xy}$  is used as approximation for  $u_{xy}$  in order to simplify the algebraic calculations.

switches, e.g.  $S_{\bar{a}y\bar{a}}$  and  $S_{\bar{b}y\bar{b}}$ . This short-circuits the corresponding input nodes  $\bar{a}$  and  $\bar{b}$  and results in  $u_{\bar{a}\bar{b}} = 0$ , as shown in **Fig. 11**. Therefore, it is possible to mitigate the current distortions by toggling the second injection switch such that the average over one switching period of  $u_{\bar{a}\bar{b}}$  equals the gird voltage  $u_{ab}$ .

### A. AC-to-DC Power Transfer

The following considerations focus on AC-to-DC power transfer and the intersection of  $u_a$  and  $u_b$  at  $\omega t \approx \pi/3$ , however, they can be generalized for the other five intersections and DC-to-AC power transfer. It can be seen from Fig. 12 that  $u_{xy}$  increases while  $S_{x\bar{p}}$  is not conducting, which implies that  $u_{xy}$  is minimal when  $S_{x\bar{p}}$  is turned off. Therefore, the turn-off of  $S_{x\bar{p}}$  is selected as origin for the auxiliary time axis  $\tau$ .

Fig. 13 shows a diagram of the filter capacitor voltage  $u_{xy}$  during the first half of the first intersection ( $\omega t \le \pi/3$ ,  $u_a > u_b$ ). The additional injection switch  $S_{\bar{a}y\bar{a}}$  is turned on at time  $\tau'$  and is turned off together with  $S_{x\bar{p}}$  in order to allow  $u_{xy}$  to charge. In order to simplify the analytical calculations  $u'_{xy}$  is used as an approximation for  $u_{xy}$ :

$$u_{\rm xy}'(\tau) = \begin{cases} \hat{u}_{xy} \frac{\tau}{(1-d_{\rm p}) T_{\rm s}} & \text{if } \tau \le (1-d_{\rm p}) T_{\rm s} \\ \hat{u}_{xy} \frac{1}{d_{\rm p}} \left( 1 - \frac{\tau}{T_{\rm s}} \right) & \text{if } \tau > (1-d_{\rm p}) T_{\rm s} , \end{cases}$$

(16)

$$u_{\bar{a}\bar{b}}(\tau) = \begin{cases} u_{xy}(\tau) \approx u'_{xy}(\tau) & \text{if } \tau \leq \tau' \\ 0 & \text{if } \tau > \tau' \end{cases}.$$

(17)

<sup>&</sup>lt;sup>1</sup>Spectral components up to 10 kHz, i.e. up to the 200<sup>th</sup> harmonic of the grid frequency, are considered.

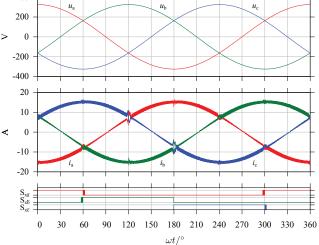

Fig. 14. Simulation results for the SWISS Rectifier specified in **Table I** using the proposed modulation technique for the IVS switches. Compared with the results in **Fig. 2**, the current distortions are significantly reduced, the low frequency (< 10 kHz) THD of  $i_{a,b,c}$  reduces from 4.2% to 0.8%.

Note that either equation (1) or (8) can be used to estimate the peak value  $\hat{u}_{xy}$ . The average  $\langle u_{\bar{a}\bar{b}}(\tau)\rangle_{T_s}$  over one switching frequency period  $T_s$  of the IVS output voltage  $u_{\bar{a}\bar{b}}$  can be found by integration:

$$\langle u_{\bar{a}\bar{b}}(\tau') \rangle_{T_{s}} = \frac{1}{T_{s}} \int_{0}^{\tau'} u_{xy}(\tau) d\tau \approx \frac{1}{T_{s}} \int_{0}^{\tau'} u'_{xy}(\tau) d\tau .$$

(18)

In order to prevent the current distortions  $\tau'$  has to be selected such that  $\langle u_{\bar{a}\bar{b}}(\tau')\rangle_{T_s}$  equals the corresponding AC grid voltage  $u_{ab}$  which is used as reference value  $u_{ref}$ :

$$u_{\rm ref} = u_{\rm a} - u_{\rm b} = u_{\rm ab} \tag{19}$$

By solving (18) an algebraic expression for  $\tau'$  can be found:

$$\begin{aligned} u_{\rm ref} &= \langle u_{\bar{\rm a}\bar{\rm b}}(\tau') \rangle_{T_{\rm s}} \implies \\ \tau' &= T_{\rm s} \begin{cases} \sqrt{2 \, \frac{u_{\rm ref}}{\hat{u}_{\rm xy}} \, (1-d_{\rm p})} & \text{if } u_{\rm ref} \leq \hat{u}_{\rm xy} \, \frac{1-d_{\rm p}}{2} \\ 1 - \sqrt{d_{\rm p} - 2 \, d_{\rm p} \, \frac{u_{\rm ref}}{\hat{u}_{\rm xy}}} & \text{if } u_{\rm ref} > \hat{u}_{\rm xy} \, \frac{1-d_{\rm p}}{2} \end{cases}. \end{aligned}$$

$$(20)$$

This implies that the current distortions can be mitigated by measuring the grid voltages and evaluating equations (1), (19) and (20) every switching frequency cycle. The additional injection switch  $S_{\bar{a}y\bar{a}}$  is then turned on at time  $\tau'$  after the turn-off of  $S_{x\bar{p}}$ .

All considerations and calculations given above hold only for the first half of the first current distortion, i.e. for  $\omega t < \pi/3$ . In the second half ( $\omega t > \pi/3$ ) the grid voltage  $u_{\rm ab}$ becomes negative which implies that the output voltage of the IVS has to be negative as well, while the filter capacitor voltage  $u_{\rm xy}$  remains positive. This is achieved by modulating  $S_{\rm \bar{b}y\bar{b}}$  instead of  $S_{\rm \bar{a}y\bar{a}}$ , as can be seen in **Fig. 12**. By replacing the grid voltages  $u_{\rm a}$  and  $u_{\rm b}$  and the injection switches with the corresponding values, this can be generalized for the other two positive grid voltage intersections ( $\omega t \approx 180^\circ, 300^\circ$ ). Furthermore, the concept can be expanded to the negative side DC-DC converter ( $S_{\rm nz}$ ,  $d_{\rm n}$ ,  $u_{\rm yz}$ ) to mitigate the current distortions at the intersections of negative grid phase voltages

Fig. 15. Schematic of the SWISS Rectifier with DC-to-AC power transfer  $(i_{\rm p} < 0, i_{\rm n} < 0)$  during the first intersection of  $u_{\rm a}$  and  $u_{\rm b}$ . When the filter capacitor voltage  $u_{\rm xy}$  reaches zero the diode  $D_{\rm px}$  is forward biased and starts to conduct, thus preventing  $u_{\rm xy}$  from reversing polarity. Therefore, similar input current distortions as for AC-to-DC power transfer result (cf. Fig. 6).

Fig. 16. SWISS Rectifier with DC-to-AC power transfer  $(i_{\rm p} < 0, i_{\rm n} < 0)$  during the first intersection of  $u_{\rm a}$  and  $u_{\rm b}$ . Two Rectifier switches  $(S_{\rm x\bar{a}}, S_{\rm x\bar{b}})$  are turned on simultaneously  $(S_{\bar{b}u\bar{b}}$  is turned off) in order to achieve  $u_{\bar{a}\bar{b}} = 0$ .

$(\omega t \approx 0^{\circ}, 120^{\circ}, 240^{\circ})$ . The resulting formulas are summarized in **Table III**. Simulation results for AC-to-DC operation of the SWISS Rectifier with the compensation enabled for all intersections are shown in **Fig. 14**.

### B. DC-to-AC Power Transfer

The previous descriptions focus on AC-to-DC power transfer, however, the current distortions exist for DC-to-AC power transfer as well. A similar mitigation strategy can be used as will be shown in the following.

As depicted in **Fig. 15** the diode  $D_{px}$  starts to conduct for DC-to-AC power transfer once the filter capacitor voltage  $u_{xy}$  reaches zero. Therefore, the local average of  $u_{xy}$  starts to deviate from the grid voltage  $u_{ab}$  once the ripple is larger than  $2u_{ab}$  as explained above for AC-to-DC power transfer. Thus similar grid current distortions result.

In order to temporarily disconnect the grid filter inductors  $L_{\rm f}$  from the filter capacitors  $C_{{\rm x},{\rm y},{\rm z}}$  two rectifier switches, e.g.  $S_{{\rm x}\bar{\rm a}}$ ,  $S_{{\rm x}\bar{\rm b}}$  are turned on simultaneously as shown in Fig. 16. Simulation results of a SWISS Rectifier using this modulation technique are shown in Fig. 17. Note that, unlike for AC-to-DC power transfer, it is not possible to modulate the injection switches  $S_{\bar{\rm i}y\bar{\rm i}}$  ( $\bar{i} = \bar{a}, \bar{b}, \bar{c}$ ) because  $u_{{\rm xy}}$  has to be discharged to zero once the additional switch is turned on at  $\tau'$ . It can be shown that this is the case only when the rectifier switches  $S_{{\rm x}\bar{\rm a},\bar{\rm b},\bar{\rm c}}$ ,  $S_{\bar{\rm a},\bar{\rm b},\bar{\rm c}z}$  are modulated.

The equations required to implement the mitigation algorithm for DC-to-AC power transfer are summarized in the right column of **Table III**. Note that the switching transition

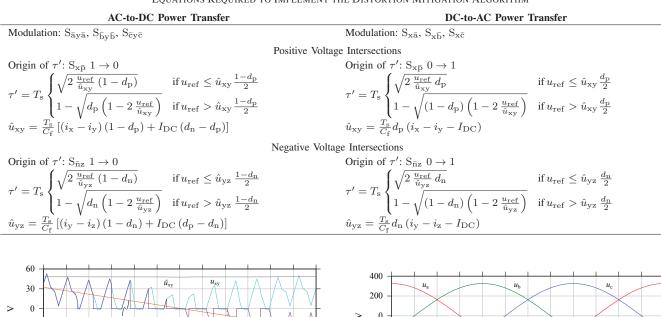

TABLE III

EQUATIONS REQUIRED TO IMPLEMENT THE DISTORTION MITIGATION ALGORITHM

Fig. 17. Detailed simulation results for DC-to-AC power transfer and the first intersection of  $u_a$  and  $u_b$  showing the modulation of a second rectifier switch  $(S_{x\bar{a}}, S_{x\bar{b}})$ . The distortion in  $i_a$  and  $i_b$  is significantly reduced.

which marks the beginning of the time span  $\tau'$  is different than in AC-to-DC power transfer.

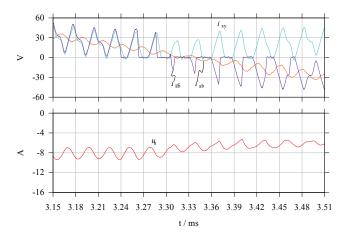

Fig. 18 shows simulation results for the SWISS Rectifier specified in Table I with 7.5 kW DC-to-AC power transfer. For illustration, the distortion compensation is disabled for the intersections at  $\omega t \approx 120^{\circ}$  and  $\omega t \approx 180^{\circ}$ . It can be seen that the current distortions are significantly reduced.

#### V. MEASUREMENT RESULTS

In order to demonstrate the practicability of the algorithm described above, it was implemented on a bidirectional 7.5 kW prototype SWISS Rectifier. The values of all major components used in the system are given in **Table I** and were used for the presented simulation results.

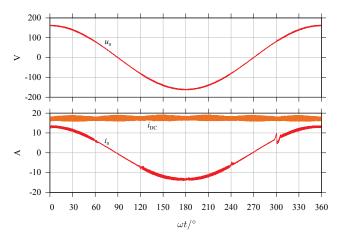

### A. AC-to-DC Power Transfer

Fig. 19 shows measurements taken on the hardware prototype operating with AC-to-DC power transfer. The mitigation algorithm is active during the grid voltage intersections at  $\omega t \approx 60^{\circ}$ ,  $120^{\circ}$  and  $240^{\circ}$ . At  $\omega t \approx 300^{\circ}$  it is disabled in order to demonstrate the effect and magnitude of the current

Fig. 18. Simulation results for the SWISS Rectifier specified in **Table I** with DC-to-AC power transfer. The proposed algorithm is used to mitigate the current distortions. During the intersections at  $\omega t \approx 120^{\circ}, 180^{\circ}$  the mitigation algorithm is turned off for illustrative purposes.

distortions in the grid current  $i_{a}$ . It can be seen that the amplitude of the current distortions is reduced below the switching frequency ripple of the input current.

#### B. DC-to-AC Power Transfer

Measurement results for DC-to-AC power transfer at nominal power are shown in **Fig. 20**. Again, the mitigation algorithm is disabled during the two intersections at  $\omega t \approx 240^{\circ}$ and  $\omega t \approx 300^{\circ}$  for comparison. Furthermore, the input filter capacitor voltage  $u_{xy}$  is shown. Note that it is positive at all times, which is in accordance with **Section IV-B**.

Fig. 21 shows detailed measurements of the first intersection of  $u_a$  and  $u_b$  at  $\omega t \approx 60^\circ$  for the same operating conditions as in Fig. 20. The output voltage  $u_{\bar{a}\bar{b}}$  of the IVS is shown as well. It can be seen that the control algorithm turns on additional rectifier switches in order to reduce the average output voltage  $u_{\bar{a}\bar{b}}$  of the IVS. Therefore, the average of  $u_{\bar{a}\bar{b}}$  closely follows the grid voltage  $u_{ab}$ . Note that the grid voltage  $u_{ab}$  shows a switching frequency ripple due to the output impedance of the AC-source employed to provide the three-phase AC mains supply voltage.

Fig. 19. Measurement results for the SWISS Rectifier prototype operated with  $I_{\rm DC} = 17.4$  A and  $U_1 = 115$  V. The current distortion compensation is turned off during the intersection at  $\omega t \approx 300^{\circ}$  for illustrative purposes.

Fig. 20. Measurement results for the SWISS Rectifier prototype operated with nominal DC-to-AC power transfer. The distortion compensation is turned off during the intersection at  $\omega t \approx 240^{\circ}, 300^{\circ}$  for illustrative purposes.

#### VI. CONCLUSION

This paper analyzes the AC input current distortion in three-phase buck-type SWISS Rectifiers which is caused by the switching frequency voltage ripple across its input filter capacitors. An analytical model is derived which allows the estimation of the distortion current's peak value and its impact on the converter's overall THD. It is shown that the current distortion's magnitude depends on the AC side filter inductance value, the ratio of switching frequency and AC grid frequency and the AC filter capacitance value.

In order to reduce the current distortion, a modification of the original SWISS Rectifier's circuit topology is proposed. By moving the AC side filter capacitors to the DC side of the input voltage selector (IVS), the commutation paths of the DC-DC converters are shortened and the conduction losses in the IVS switches are reduced. Furthermore, the DC-DC converters and the IVS can be operated independently which allows a temporary pulse width modulation of the IVS switches at the phase voltage sector boundaries in order to mitigate the input current distortions.

The modulation concept and the formulas required for its implementation are derived. It can be applied to uni- and bidirectional SWISS Rectifiers and AC-to-DC as well as

Fig. 21. Detailed results of the first grid voltage intersection of phases a and b (at  $\omega t \approx 30^{\circ}$ ) for the same configuration as in **Fig. 20**. Shown are the voltage  $u_{\rm xy}$  of the DC side input filter capacitors, the line-to-line gird voltage  $u_{\rm ab}$  and the output voltage  $u_{\rm ab}$  of the IVS, as well as the grid current  $i_{\rm a}$ .

DC-to-AC power transfer. Furthermore, it does not require additional sensors; the DC link current sensor and the AC grid voltage sensors, which are typically present in a SWISS Rectifier, are sufficient. In total, three multiplications, one division and one square root have to be evaluated once every switching cycle.

Simulations of various operating conditions and measurements taken on a 7.5 kW hardware prototype are proving the principle's feasibility.

#### REFERENCES

- G. AlLee and W. Tschudi, "Edison Redux: 380 Vdc Brings Reliability and Efficiency to Sustainable Data Centers," *IEEE Power and Energy Magazine*, vol. 10, no. 6, pp. 50–59, Nov 2012.

- [2] D. E. Geary, D. P. Mohr, D. Owen, M. Salato, and B. J. Sonnenberg, "380V DC Eco-System Development: Present Status and Future Challenges," in *Proc. of 35th International Telecommunications Energy Conference (INTELEC)*, Oct 2013, pp. 1–6.

- [3] ETSI, "Environmental Engineering (EE); Power Supply Interface at the Input to Telecommunications and Datacom (ICT) Equipment; Part 3: Operated by Rectified Current Source, Alternating Current Source or Direct Current Source up to 400 V; Sub-part 1: Direct Current Source up to 400V," *EN 300 132-3-1*, Feb. 2012.

- [4] D. J. Becker and B. J. Sonnenberg, "DC Microgrids in Buildings and Data Centers," in *Proc. of 33rd International Telecommunications Energy Conference (INTELEC)*, Oct 2011, pp. 1–7.

- [5] J. W. Kolar and T. Friedli, "The Essence of Three-Phase PFC Rectifier Systems - Part I," *IEEE Transactions on Power Electronics*, vol. 28, no. 1, pp. 176–198, Jan. 2013.

- [6] D. Aggeler, F. Canales, H. Zelaya-De La Parra, A. Coccia, N. Butcher and O. Apeldoorn, "Ultra-Fast DC-Charge Infrastructures for EV-Mobility and Future Smart Grids," in *Proc. of Innovative Smart Grid Technologies Conference Europe (ISGT)*, Oct 2010, pp. 1–8.

- [7] A. Kuperman, U. Levy, J. Goren, A. Zafransky and A. Savernin, "Battery Charger for Electric Vehicle Traction Battery Switch Station," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 12, pp. 5391– 5399, Dec 2013.

- [8] M. F. Vancu, T. Soeiro, J. Mühlethaler, J. W. Kolar and D. Aggeler, "Comparative Evaluation of Bidirectional Buck-Type PFC Converter Systems for Interfacing Residential DC Distribution Systems to the Smart Grid," in *Proc. of Industrial Electronics Society Conference* (*IECON*), Oct. 2012, pp. 5153–5160.

- [9] R. Chen, Y. Yao, L. Zhao and M. Xu, "Inhibiting Mains Current Distortion for SWISS Rectifier - A Three-Phase Buck-Type Harmonic Current Injection PFC Converter," in *Proc. of Applied Power Electronics Conference and Exposition (APEC)*, Mar. 2015, pp. 1850–1854.

- [10] T. B. Soeiro, T. Friedli and J. W. Kolar, "SWISS Rectifier A Novel Three-Phase Buck-Type PFC Topology for Electric Vehicle Battery Charging," in *Proc. of Applied Power Electronics Conference and Exposition (APEC)*, Feb. 2012, pp. 2617–2624.