# Design and Experimental Analysis of a Three-Phase Active CM/DM Conducted EMI Noise Separator

Pascal Samuel Niklaus, Dominik Bortis, and Johann Walter Kolar

Abstract—This work investigates three-phase electromagnetic interference (EMI) conducted emission (CE) measurements with the aim to separate the noise voltages in their common-mode (CM) and differential-mode (DM) parts. By doing so, the converter input and/or output filter stages can be individually optimized to improve the CM or DM attenuation depending on the origin of the CE disturbances. An overview of various ways to achieve this separation is provided and an active three-phase noise separator is presented. The main advantage of the presented active solution is the absence of magnetic components in the signal path which drastically facilitates the matching at high frequencies. The influence of asymmetries and mismatches of the component parasitics as well as in the circuit board layout are analyzed. To assess the performance of the proposed system according to widely known metrics such as CM and DM transfer functions and rejection ratios, different test methods are established and the implied limitations regarding maximum measurable performance are considered. Finally, experimental results verifying the calculated separation capabilities are provided.

Index Terms—Common-mode (CM) and differential-mode (DM) noise separation, electromagnetic compatibility (EMC), electromagnetic interference (EMI), EMI measurements, filter optimization, three-phase noise separator.

### I. Introduction

The characterization of electromagnetic interference (EMI) noise is required to verify compliance with international and regional standards such as CISPR 11 [1] and CISPR 14 [2] that limit the generated conducted emissions (CE) in the frequency range between 150 kHz and 30 MHz. With today's research going into the direction of maximum power density, the switching frequencies for the carrier signals are chosen in the range of several 100 kHz or even several MHz [3]. The harmonics, inevitably present in the characteristic triangular or trapezoidal current and voltage waveforms, appear at frequencies within the range of the aforementioned standards, thus care needs to be taken to limit the generated emissions. In addition, the fast switching transitions achievable with modern wide band-gap semiconductors generate a significant amount of high-frequency spectral components [4], which

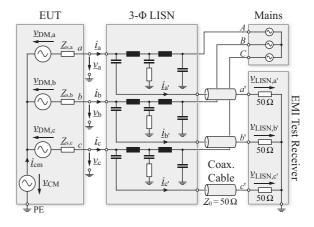

Fig. 1. Typical measurement setup for EMI measurements with a three-phase EUT using a three-phase LISN to connect the EUT to the mains and with coaxial cables to a EMI test receiver.

also need to be considered for EMI compliance. While there exist several techniques to reduce the generated CE by design, e.g., by implementing modulation schemes that allow for a variable switching frequency [5] or by deliberately limiting the transition speed and therefore reducing the high-frequency spectral components [6], it is nevertheless often unavoidable to employ dedicated filtering, implying additional volume, losses and cost. Hence, the aim is to keep the filtering effort as low as possible.

Measurements with a standard EMI test setup as shown in Fig. 1 with a three-phase converter that has to comply to EMI standards as equipment-under-test (EUT), a three-phase line impedance stabilization network (LISN) and a corresponding EMI test receiver allow the quantification of the total CE. The LISN acts as a bridge between the three-phase mains and the converter and serves three purposes. Firstly, it provides a fixed mains impedance of 50  $\Omega$ ||50  $\mu$ H to the EUT for the relevant frequency range as specified above [7], which is crucial for meaningful measurements, since CE voltage noise arises from impressed currents flowing through the inner mains impedance. Secondly, it enables low-frequency (LF) power flow (50/60 Hz) from the mains to the EUT (and vice versa) and thirdly redirects any high-frequency (HF) content emitted from the EUT to the connected EMI test receiver where the measurements are taken and therefore prevents the HF noise from flowing into the mains. At the same time, any LF component is attenuated at the HF output port to prevent saturation of the EMI test receiver input. Even though Fig. 1 shows the measurement path only

Manuscript received January 22, 2020; revised April 16, 2020; accepted May 22, 2020. Date of publication September 30, 2020; date of current version September 5, 2020. (Corresponding author: Pascal Samuel Niklaus)

All authors are with the Power Electronic Systems Laboratory, Swiss Federal Institute of Technology, Zurich 8092, Switzerland (e-mail: niklaus@lem.ee.ethz.ch; bortis@lem.ee.ethz.ch; kolar@lem.ee.ethz.ch).

Digital Object Identifier 10.24295/CPSSTPEA.2020.00023

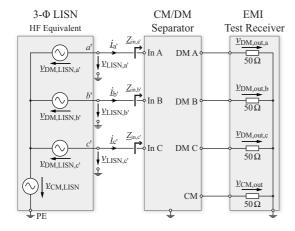

Fig. 2. The same setup as before but now using a three-phase CM/DM noise separator between the three-phase LISN, which is modeled as a three-phase noise source comprised of CM and DM components, and the measurement receiver whose input is modeled with three 50  $\Omega$  resistors. For the sake of simplicity, the coaxial cables actually used to connect the separator with the LISNs as well as the test receiver are omitted.

as first-order high-pass filter, in reality the filtering network attenuates LF components much stronger. In the appendix the equivalent circuit of a commercially available LISN and the resulting attenuation is described.

In order to be compliant with the standards, the spectral envelope of the total conducted noise over the specified frequency range must be below the defined limits. As mentioned above, in modern power converters, compliance is usually only achieved by employing dedicated filter stages. Obviously, overdimensioned filters must be avoided and apart from profound knowledge of the amount of noise generated by the employed converter topology and modulation scheme, it is important to know the share of common-mode (CM) and differential-mode (DM) emissions for an optimal filter design, since the total noise can be composed of only one of the two sources or the combination thereof. Since the LISN only measures the total CE noise, it is very convenient to have a so-called CM/DM noise separator that allows to separately quantify the CM and DM components of the total measured CE and thereby allows to improve only the insufficiently performing filter to reduce the CE. Furthermore, the designer can also determine potential cross-coupling between the filter stages due to component placement and parasitic elements [8]. The CM/DM noise separator can be integrated to the standard EMI test setup, as depicted in Fig. 2. In the standard setup (cf. Fig. 1), the HF outputs of the LISNs are connected to the test receiver using coaxial cables with a characteristic impedance of  $\underline{Z}_0 = 50 \Omega$  and are terminated with the 50  $\Omega$  input resistance of the receiver, at which the HF noise voltages  $\underline{\nu}_{LISN\,a'}$ ,  $\underline{\nu}_{LISN\,b'}$ , and  $\underline{v}_{LISN c'}$  are measured. When adding a three-phase noise separator between LISN and test receiver (cf. Fig. 2), it must be ensured that the input impedances  $\underline{Z}_{in,a'}$ ,  $\underline{Z}_{in,b'}$  and  $\underline{Z}_{\text{in,c'}}$  of the three separator input ports equal 50  $\Omega$ , as otherwise measurement errors due to an impedance mismatch between separator and LISN occur [9].

In this work, Section II presents an overview of singleand three-phase noise separation theory and corresponding circuit realizations. The performance metrics to assess the separation capabilities are introduced and previously reported results found in literature are discussed. Then, an active threephase noise separator as proposed in [10] and realized in [11] is analyzed in detail. Based on these analyses, a hardware demonstrator of the active three-phase CM/DM noise separator is presented and it is highlighted how asymmetries and parasitic elements of the PCB and in the utilized components influence the overall achievable performance. Design guidelines to estimate the impact of imperfections on the resulting separation capabilities are given (Section III and Section IV). Afterwards, measurement methods to evaluate the performance of such a three-phase separator with focus on the limitations in the maximum measurable performance due to the setup are shown in Section V. Finally, the achieved performance of the constructed active separator is presented with transfer functions and by spectral measurements with a three-phase power electronic converter before in Section VI a conclusion of the work and results is given.

#### II. FUNDAMENTALS OF CM/DM EMI NOISE SEPARATION

In practice, EMI test receivers feature only a single input channel and also three-phase LISNs are implemented in such a way that only one phase can be measured at a time (only one HF signal output exists). Hence, to characterize a three-phase EUT, three consecutive measurements, performed for each phase output, are required. To determine the CM and DM components, however, the three measurements need to be performed concurrently, which either requires a custom-made LISN that features three separate HF outputs or a test setup comprising three single-phase LISNs which are connected in such a way to perform three-phase measurements.

The separation of conducted CM and DM emissions is a widely known practice during EMI pre-compliance testing [12] and has been discussed extensively in literature. Especially for single-phase systems, there exist various implementations, either comprising passive components [7], [13]–[19], power splitters [20], active components [21] or using computer-aided design with post-processing [22], [23]. All of the presented implementations rely on the fact, that in a single-phase system, the CM and DM components of the CE can be determined independently using the two voltages  $\underline{v}_{\text{LISN,p}}$  (noise on the phase line with respect to earth) and  $\underline{v}_{\text{LISN,n}}$  (noise on the neutral line with respect to earth) as follows

$$\underline{v}_{\text{CM}} = \frac{\underline{v}_{\text{LISN},p} + \underline{v}_{\text{LISN},n}}{2} \tag{1}$$

$$\underline{v}_{DM} = \frac{\underline{v}_{LISN,p} - \underline{v}_{LISN,n}}{2}.$$

(2)

Due to the coupling between the phases a, b and c, the determination of the CM and DM noise components in a three-phase system is not as straight forward as in the single-phase case. As shown in Fig. 1, the EUT is modeled as a

combination of voltage sources, comprising a CM voltage  $\underline{v}_{\text{CM}}$  common to all three phases and three DM voltage sources  $\underline{v}_{\text{DM},i}$  ( $i = \{a, b, c\}$ ), one for each phase. In addition, the noise source of each phase includes a source impedance  $\underline{Z}_{\text{s,a}}$ ,  $\underline{Z}_{\text{s,b}}$ , and  $\underline{Z}_{\text{s,c}}$  respectively. Hence, each phase voltage at the EUT ports consists of a CM and DM part, such that

$$\underline{v}_{i} = \underline{v}_{\text{CM}} + \underline{v}_{\text{DM}i}, \quad i = \{a, b, c\}.$$

(3)

The same argumentation is also valid for the noise voltages  $\underline{\nu}_{\text{LISN,i'}}$  at the LISN outputs, composed of a CM component  $\underline{\nu}_{\text{CM,LISN}}$  and three DM components  $\underline{\nu}_{\text{DM,LISN,i'}}$ , as depicted in Fig. 2. There, the EUT together with the three-phase LISN is replaced by an equivalent three-phase HF noise source, again composed of one CM and three DM voltages. Opposed to the single-phase case, the determination of the corresponding CM and DM parts cannot be carried out independent of each other. Firstly, the CM component is calculated out of the three LISN output voltages. By definition, the sum of the three DM components in a three-phase system is zero and the CM component equals the average value of the three noise voltages

$$\underline{v}_{\text{CMLISN}} = \frac{\underline{v}_{\text{LISN,a'}} + \underline{v}_{\text{LISN,b'}} + \underline{v}_{\text{LISN,c'}}}{3}.$$

(4)

Secondly, the three individual DM components are then obtained by subtracting the calculated CM component from the three LISN output voltages [10]

$$\underline{v}_{\text{DMLISN},i} = \underline{v}_{\text{LISN},i} - \underline{v}_{\text{CMLISN}}.$$

(5)

It is important to note that the resulting DM voltage system is in fact CM free but not necessarily symmetric. There could still be different amplitudes and phase displacements of the phase quantities. Further decomposition of the DM components into a positive and negative sequence using the method of symmetrical components [24] would be possible and the question arises, whether a further optimization in EMI filter design could be achieved if the positive and negative sequence DM components are treated separately. In a complex plane representation, with help of space-vectors [25], the positive and negative sequence correspond to two vectors  $\underline{v}_{DM+}$  and  $\underline{v}_{DM-}$ that rotate in opposite direction. The instantaneous DM voltage vector  $\underline{v}_{DM}$  is the geometric addition of  $\underline{v}_{DM,+}$  and  $\underline{v}_{DM,-}$ . The projection of the vector  $\underline{v}_{DM}$  on the respective phase axes a, b and c corresponds to the time-domain phase voltages  $v_a$ ,  $v_b$  and  $v_c$  at any point in time. Due to the opposite rotation directions of  $\underline{v}_{DM,+}$  and  $\underline{v}_{DM,-}$ , at some time instance the two vectors will add up constructively, which means that the geometric addition is equal to a linear arithmetic addition. The worst case happens exactly when the two vectors are aligned with one of the phase axes and therefore, the corresponding phase voltage is maximized. An EUT has to comply with the EMI regulations also for this worst-case scenario, which means that no further benefit is gained by separating the DM component into its positive and negative sequence. The decomposition

according to (5) implicitly accounts for the positive and negative sequence with the consequence, that the amplitudes of the three DM voltages are not necessarily identical. Therefore, the DM voltage component of all three phases has to be measured with help of a noise separator and the worst of the three measurements has to be taken as reference for the filter design and/or optimization.

#### A. Performance Metrics

The performance of a noise separator is evaluated by means of transfer and rejection characteristics from each input to the different outputs [21]. For a pure CM excitation ( $\nu_{DM,LISN,i} = 0$ ), no voltage should be present at the DM output ports while at the CM output, the CM input voltage should be measured. The former condition is described by the common-mode rejection ratio (CMRR), defined as

$$CMRR_{i} = \left| \frac{\underline{\nu}_{\text{DM,out,}i}}{\underline{\nu}_{\text{CM,LISN}}} \right|, \tag{6}$$

i.e., the ratio between DM output voltage at DM output port *i* and CM input voltage. Note, that due to the presence of three DM output ports, there are generally three different CMRR characteristics, however, for a well-designed three-phase separator, the three CMRR characteristics are very similar. The latter constraint is described by the common-mode transfer function (CMTF), the ratio between CM output voltage and CM input voltage, defined as

$$CMTF = \left| \frac{\nu_{\text{CM,out}}}{\nu_{\text{CM,LISN}}} \right|. \tag{7}$$

Similar conditions are found for a pure DM input ( $\nu_{CM,LISN} = 0$ ), leading to the definition of the differential-mode transfer function (DMTF) and the differential-mode rejection ratio (DMRR), defined as follows

$$DMTF_{i} = \left| \frac{\underline{v}_{DM, \text{out}, i}}{\underline{v}_{DM, \text{ISN}}} \right| \tag{8}$$

$$DMRR = \left| \frac{\underline{\nu}_{CM,out}}{\underline{\nu}_{DM,LISN}} \right|. \tag{9}$$

Again, it has to be noted that due to the measurement at the three DM output ports for the DMTF three (nominally identical) characteristics exist. In accordance with the standards, only the magnitudes are considered as relevant performance metrics.

Since the goal of noise separators is to determine whether the observed noise spectrum is due to CM or DM noise, the relevant criteria for evaluating the performance of such separators are the so called selectivities of CM noise with respect to DM noise and vice versa. Hence, suitable metrics are the two ratios *DMTF/CMRR* and *CMTF/DMRR* as proposed in [21],

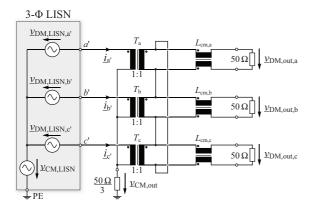

Fig. 3. Schematic drawing of the passive three-phase CM/DM noise separator proposed in [10].

where a high ratio indicates good performance. The first ratio shows the attenuation of a desired DM signal at the DM output with respect to the attenuation of an undesired CM signal at the same output. In a similar manner, the second ratio determines the attenuation of a desired CM signal at the CM output with respect to the attenuation of an undesired DM signal at the same output. These ratios are particularly important when the DMTF and CMTF are not unity, i.e., if there is already a certain attenuation of the desired signal. In this case, specifying solely the CMRR and DMRR can be misleading as it does not show how good the separator performs in terms of selection between CM and/or DM signals from the total noise.

# B. Literature Review of Three-Phase Noise Separators

Different variants for the circuit implementation of the separation of CM and DM noise in a three-phase system according to (4) and (5) have been discussed in literature. The circuit proposed in [10] is shown in Fig. 3. It consists of a three-phase transformer with primary-side star and secondaryside delta  $(Y/\Delta)$  connection. Hence, for a pure CM excitation, the secondary side is shorted and no current flows through the secondary side 50  $\Omega$  resistors and no voltage appears at the DM outputs whereas the CM input voltage is directly measured over the primary side resistor 50  $\Omega/3$ . For a DM input signal, the DM voltages are directly transferred to the secondary side and to the three 50  $\Omega$  resistors, however, since for DM the sum  $\underline{i}_{a'} + \underline{i}_{b'} + \underline{i}_{c'}$  of the three input currents is zero, no voltage is measured across the primary resistor 50  $\Omega/3$ , i.e.,  $\underline{v}_{CM.out} = 0$ . It was shown that the parasitic elements of the transformer as well as asymmetric windings introduce performance degradation in the separation which is mainly seen in reduced CMRR and DMRR. Finally, a CMRR and DMRR of around -30 dB were achieved at 30 MHz. The DMTF shows a flatness (i.e. maximum deviation) of around  $\pm 2$  dB, while the CMTF is flat up to 10 MHz and then starts to drop to roughly -1.5 dB at 30 MHz. Since both, CMTF and DMTF are nominally unity (0 dB), it is sufficient to specify the CMRR and DMRR to assess the separator's performance instead of specifying the selectivities, which in this case are only the inverse of the CMRR and DMRR.

In [26] and [27], a profound theoretical analysis of the characteristics of three-phase noise sources is given together with a generalized approach for multi-port noise separators based on network theory. Similar to [10], the proposed implementation is composed entirely of passive components and relies on the principle of flux cancellation in magnetic cores and therefore requires accurate construction of magnetic components with very high symmetry. Over the specified frequency range the DMTF and CMTF show a maximum deviation of 1.3 dB and 1.2 dB respectively, while the DMRR and CMRR are better than -40 dB and -34 dB respectively. To achieve this reported performance, the magnetic components must have an extremely high coupling factor of k = 0.99995, which is difficult, yet possible to realize in practice if extreme care is taken of the parasitic components.

In [28], the influence of the parasitic components is reduced by employing separate passive CM and DM attenuators, where the CM signal is measured in a similar way as done in [10], while the DM signal is directly extracted on the primary side by adding a three-phase CM low-pass filter in parallel to the transformer. Furthermore, passive attenuators are added to reduce or compensate the influence of the parasitic components on the transfer functions. Hence, the DMTF and CMTF flatness is improved to 0.6 dB and 0.3 dB respectively. The CMRR and DMRR also appear to be better than for example in [26], however, the improved CMRR and DMRR are only achieved by the additional -20 dB attenuation obtained from the used series resistances. Hence, when using the selectivities DMTF/CMRR and CMTF/DMRR as metrics for performance evaluation, the net performance is very similar to the other presented separators in literature, with the advantage that the design of the magnetic components is less critical due to the reduced influence of the parasitic elements. Generally, passive three-phase noise separator realizations rely on the accurate matching of magnetic components, which is very difficult to achieve for the upper frequency range, thereby rendering an active implementation favorable.

In [11], an approach using active components is shown. In fact, the utilized circuit was presented in [10] for the first time but was not realized there due to the increased complexity compared to a passive separator and the need for an external power supply. In contrast to a classical separator used together with a LISN, the authors targeted the CE characterization of motor drives on the load side and therefore added an additional high-impedance high-voltage input stage such that measurements directly on the three phase lines are possible. The reported performance shows a CMTF of -54 dB (due to the strong attenuation in the input stage) with a drop of around 1.5 dB at 10 MHz before reaching again -54 dB at 30 MHz. Similarly, the DMTF is relatively flat at -48 dB and shows a drop of 2 dB at 30 MHz, starting already at around 2 MHz. The DMTF/CMRR is approximately 50 dB up to 1 MHz and then starts to become worse reaching at 30 MHz a value of around 25 dB. The CMTF/DMRR ratio gives 70 dB at 150 kHz and decreases with roughly 20 dB/dec such that at 30 MHz a value of around 30 dB is achieved. It has to be noted that for the rejection ratios,

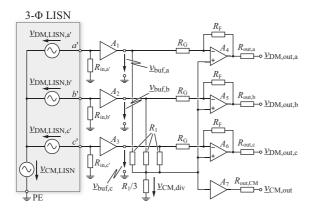

Fig. 4. Schematic drawing of the proposed active three-phase CM/DM noise separator that uses no magnetic components.

especially for the CMRR, a substantial deviation between the three phases was measured. Targeting the same application, in [29] a separation setup based on current probes is presented achieving similar performance. While the importance of a symmetric layout is pointed out, no details for the physical realization were provided and the influence of asymmetries was not investigated.

#### III. THREE-PHASE ACTIVE CM/DM NOISE SEPARATOR

## A. Target Performance

The goal of the presented active separator is to trace down any exceeding of the EMI limits to either the CM or DM filter, such that the one with insufficient attenuation can be improved. Hence, mainly qualitative measurements are of interest and to avoid misinterpretation of the obtained results, the selectivity of the separator should be at least  $-40~\mathrm{dB}$  up to 30 MHz. This means that the error due to cross coupling of a CM signal to the DM outputs or vice versa is less than 1%. At the same time the DMTF and CMTF must be as flat as possible. The standard defines a deviation of no more than  $\pm 2~\mathrm{dB}$  [30], however, much lower values are desired. At the measurement ports an input impedance of 50  $\Omega$  in the whole considered frequency range (150 kHz to 30 MHz) is required.

## B. Implementation

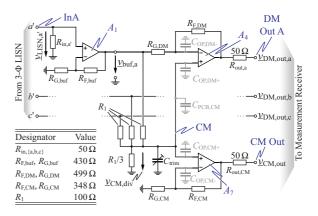

The circuit of the implemented active three-phase noise separator is given in Fig. 4 and is composed of three identical channels, each comprising an input buffer  $(A_1 - A_3, \text{ Analog Devices AD8000 [31]})$  and a difference amplifier  $(A_4 - A_6, \text{ Analog Devices AD8099 [32]})$ . Again, the input coming from a three-phase LISN is modeled with a CM and three DM noise voltage sources. The required 50  $\Omega$  input impedance is solely defined with the three resistors  $R_{\text{in,a'}} \dots R_{\text{in,c'}} = 50 \Omega$ , since the input impedance  $Z_{\text{in,buf}} = 2 \text{ M}\Omega \| 3.6 \text{ pF}$  of the buffer amplifiers can be neglected in the given frequency range  $(Z_{\text{in,buf}})_{f=30 \text{ MHz}} = 1.47 \text{ k}\Omega >> 50 \Omega$ ).

According to (4), at the output of the buffer amplifiers, the

Fig. 5. Detailed view of one DM channel (channel A) and the CM channel. Indicated are the relevant parasitic capacitances that mainly determine the high frequency behavior. In addition, the table shows the resistor values used in the current implementation that are chosen based on the considerations listed below.

CM voltage is obtained with the voltage divider composed of  $R_1$  and  $R_1/3$ . From this voltage the buffered LISN output voltage  $\underline{\nu}_{\text{buf},i}$  is subtracted, such that at the DM output ports the negative DM voltage components  $\underline{\nu}_{\text{DM,out},i} = -\underline{\nu}_{\text{DM,LISN},i}$  remain (cf. (5)). Finally, the amplifier  $A_7$  (Analog Devices ADA4817 [33]) buffers the voltage  $\underline{\nu}_{\text{CM,div}}$  at the CM node and at its output port the pure CM voltage component  $\underline{\nu}_{\text{CM,out}}$  remains. Even though the DM output voltage shows a negative sign compared to the definition in (5), the separation is still valid, since the CE standard only considers the magnitude but not the phase of the emitted noise. Alternatively, a further inverting stage could be added to the circuit.

Fig. 5 shows a more detailed schematic for one of the three channels (channel A), lists the corresponding resistor values and includes the most relevant parasitic capacitances, drawn in light gray. All the observations hold in the same way for the other two channels. The input buffer  $A_1$  is realized as a non-inverting amplifier with a gain of +2, i.e.,  $R_{\rm F,buf} = R_{\rm G,buf}$ , such that

$$\underline{\underline{\nu}}_{\text{buf,a}} = 2 \cdot \underline{\underline{\nu}}_{\text{LISN,a'}} = 2 \cdot (\underline{\underline{\nu}}_{\text{CM,LISN}} + \underline{\underline{\nu}}_{\text{DM,LISN,a'}}).$$

(10)

This additional gain compensates the division of the DM output voltage by a factor of two, due to the 50  $\Omega$  output resistors  $R_{\text{out,a}} \dots R_{\text{out,c}}$  in conjunction with the 50  $\Omega$  input termination of the test receiver.

The CM voltage  $\underline{v}_{CM,div}$  across the resistor  $R_1/3$  in the bottom leg of the CM voltage divider is found based on

$$\underline{v}_{\text{CM,div}} = \left(\sum_{i = \{\text{a,b,c}\}} \underline{v}_{\text{buf},i}\right) \cdot \underbrace{\frac{\left(\frac{R_1}{3} \| R_1 \| R_1\right)}{\left(\frac{R_1}{3} \| R_1 \| R_1\right) + R_1}}_{1/6}.$$

(11)

Using (4) and (10) the above expression can be evaluated as

$$\underline{v}_{\text{CM,div}} = \underline{v}_{\text{CM,LISN}}.$$

(12)

To prevent loading of the CM circuit node CM and to compensate for the -6 dB loss at the CM output port due to the output resistance  $R_{\text{out,CM}}$  and the test receiver input resistance, amplifier  $A_7$  with a gain of +2 ( $R_{\text{GCM}} = R_{\text{ECM}}$ ) is inserted.

In the DM path, the amplifier  $A_4$  is configured as difference amplifier, which subtracts the buffered input voltage  $\underline{v}_{\text{buf,a}}$  from the CM voltage  $\underline{v}_{\text{CM-div}}$  according to

$$\underline{v}_{\text{out},A_4} = \left(1 + \frac{R_{\text{F,DM}}}{R_{\text{G,DM}}}\right) \cdot \underline{v}_{\text{CM,div}} - \frac{R_{\text{F,DM}}}{R_{\text{G,DM}}} \cdot \underline{v}_{\text{buf,a}}.$$

(13)

Setting  $R_{\text{F,DM}} = R_{\text{G,DM}}$  and inserting (10) and (12), the difference amplifier output voltage is directly given by

$$\underline{v}_{\text{out}A_4} = -2 \cdot \underline{v}_{\text{DMLISNa'}} \tag{14}$$

and reduces to

$$\underline{v}_{\text{DM,out,a}} = \underline{v}_{\text{out,}A_4} \cdot \frac{50 \,\Omega}{50 \,\Omega + R_{\text{out,a}}} = -\underline{v}_{\text{DM,LISN,a'}} \tag{15}$$

when considering again the voltage divider formed by the 50  $\Omega$ input resistance of the EMI test receiver together with the 50  $\Omega$ output resistor  $R_{\text{out,a}}$  of the separator. As already mentioned, the signal inversion from input to DM output is not problematic, since the targeted application is the characterization of the dominant noise contributor (CM or DM), hence only the magnitude of the respective voltages are of interest. However, connecting the CM signal at the non-inverting input terminals of the difference amplifiers makes the matching easier, as further explained in the next section. With this configuration, the maximum allowed voltage of  $\pm 1.75$  V (124 dB $\mu$ V) at the separator input is determined by the output voltage range of the operational amplifiers. The reason is the required gain of +2, to drive the double terminated 50  $\Omega$  line. Therefore, to get  $\pm 1.75$  V at the EMI test receiver input, the operational amplifiers must have an output voltage swing of  $\pm 3.5$  V. It has to be noted, that 124 dBµV is orders of magnitude higher than the EMI limiting values and therefore, sufficient margin is provided.

# IV. CRITICAL DESIGN ASPECTS

As already mentioned in [11] and [34], symmetry of the overall structure is very crucial to achieve sufficient performance, especially good rejection ratios at high frequencies and therefore high selectivities. The symmetry requirement can be split into several parts, each treated individually. The critical aspects regarding component selection and printed circuit board (PCB) layout are investigated in this section.

# A. Matching and PCB Layout

From all metrics, the CMRR is most severely affected by any asymmetries, since for a pure CM excitation, the DM output measured with the difference operation according to (13) must stay at zero, which means that both inputs of amplifiers  $A_4 \dots A_6$  must be perfectly equal in magnitude

Fig. 6. Length-matching of the signal paths.

and phase. In [35], it was shown that especially the phase matching of the amplifier input signals has a big influence on the maximum achievable CMRR of a difference amplifier, even if the amplifier itself is assumed ideal. A relative phase error of less than 0.035 % with respect to 180° (absolute phase mismatch of 0.06° or a skew of less than 6 ps at 30 MHz) is required to achieve a CMRR of -60 dB. Apart from reactive elements, a phase shift between two nominally identical signals is also introduced by unequal signal path lengths (PCB tracks), leading to different signal propagation delays  $t_{\rm pd}$ . Mathematically, the phase shift  $\Delta \varphi$  in radians can be calculated as

$$\Delta \varphi(f) = \omega \cdot \Delta t_{\rm pd} = 2\pi \cdot f \cdot \frac{\Delta l}{c}$$

(16)

where  $\Delta l$  denotes the length difference between the two tracks and c the wave propagation speed, which for a 50  $\Omega$  microstrip on the utilized layer stack-up is calculated as approximately  $1.68 \cdot 10^8$  m/s using a standard PCB calculator [36]. It becomes clear, that for a given length mismatch the phase error is proportional to the signal frequency. To keep the absolute phase error below  $0.06^\circ$  over the whole frequency range, i.e., to achieve a CMRR better than -60 dB, the overall length mismatch has to be lower than 0.9 mm, resulting from solving (16) for  $\Delta l$  at the maximum frequency f = 30 MHz.

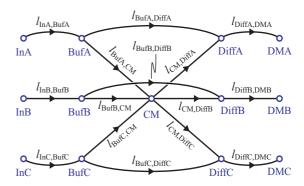

Length matching needs to be fulfilled at several stages in the circuit layout as illustrated in Fig. 6. First and foremost, the tracks from each input port InA, InB, and InC to the respective buffer amplifiers BufA  $(A_1)$ , BufB  $(A_2)$ , and BufC  $(A_3)$  must have equal length. The buffer outputs are connected to the inverting inputs of the difference amplifiers DiffA  $(A_4)$ , DiffB $(A_5)$  and  $DiffC(A_6)$  with tracks of length  $l_{Buff,Diffi}$ ,  $i = \{A, B, C\}$ respectively and to the respective non-inverting inputs via the CM divider network. Hence, for each channel the sum of the lengths  $l_{\text{Bufi,CM}}$  (track length from the buffer output to the CM node) and  $l_{\rm CM,Diffi}$  (track length from the CM node to the noninverting input of the difference amplifier) needs to be equal to the length  $l_{\text{Bufi.Diffi}}$  (track length from the buffer output to the inverting input of the difference amplifier), such that for a pure CM input signal the voltages at the inverting and non-inverting input terminals of the difference amplifier have no phase shift. The connections between difference amplifier output and separator output ports  $(l_{\text{Diffi,DMi}})$  only need to be length-

TABLE I

PCB Track Lengths and Length Mismatch of the Critical Signal Paths.

(All numbers are given in mm)

| Ch. | $l_{ m In, Buf}$ | $l_{ m Buf,CM}$ | $l_{\mathrm{CM,Diff}}$ | $l_{ m Buf, Diff}$ | $\Delta l_{ m Diff}$ |

|-----|------------------|-----------------|------------------------|--------------------|----------------------|

| A   | 14.163           | 12.144          | 14.199                 | 26.341             | -0.002               |

| В   | 14.169           | 12.157          | 14.201                 | 26.354             | -0.004               |

| C   | 14.173           | 12.148          | 14.202                 | 26.350             | 0                    |

matched if the three DM outputs are monitored simultaneously in time-domain. The above requirements can be summarized mathematically with three conditions

$$l_{\text{InA,BufA}} = l_{\text{InB,BufB}} = l_{\text{InC,BufC}}$$

(17)

$$l_{\text{BufA,DiffA}} = l_{\text{BufB,DiffB}} = l_{\text{BufC,DiffC}}$$

(18)

$$l_{\text{Buff,Diffi}} = l_{\text{Buff,CM}} + l_{\text{CM,Diffi}}, \quad i = \{A, B, C\}.$$

(19)

It can be observed, that the last condition is graphically represented with three triangles (cf. Fig. 6) and therefore a semicircular arrangement of the channels with interleaved input and output ports and the CM port located in the center as will be shown in Fig. 9 allows for a very convenient implementation. Table I lists the PCB track lengths of the critical signal paths shown in Fig. 6 including the mismatch  $\Delta l_{\rm Diff} = l_{\rm Buf,Diff} - (l_{\rm Buf,CM} + l_{\rm CM,Diff})$  at the difference amplifier input for each channel. All tracks are realized as 50  $\Omega$  microstrips with a track width of 0.2 mm on a standard FR-4 PCB. Possible tolerances during the PCB manufacturing are very likely to exceed the calculated length mismatch of 4  $\mu$ m between the critical signal paths to the difference amplifier inputs.

## B. Matching and Selection of Passive Components

Apart from the layout, the selection of the passive components also has a substantial influence on the symmetry and therefore the CMRR and DMRR. The general idea is that all resistive dividers of one channel are matched to the respective dividers of the other channels and that there is no phase mismatch between the two inputs of the three difference amplifiers. For the lower frequency range this is accomplished by choosing resistors with the lowest available tolerance of  $\varepsilon_{\rm R} = \pm 0.01$  %, which for an ideal difference amplifier gives a worst-case CMRR of -74 dB [37]. While the network of Fig. 4 features only resistors and amplifiers, parasitic capacitances, as for example the amplifier input capacitance denoted in Fig. 5, introduce a phase shift at frequencies above several MHz, which unfortunately still lay in the considered frequency range. The HF CMRR is trimmed to diminish the phase mismatch of the difference amplifier input signals due to e.g. loosely matched parasitic capacitances. The time constant of the effective node impedances, assumed as first-order RC circuits, must be equal for both inverting and non-inverting input. To achieve this, trimming capacitors need to be placed on the CM voltage divider, whereby three possibilities exist: i) placement of a capacitor in parallel to  $R_1$  in each channel or ii) placement of one single capacitor in parallel to  $R_1/3$ , which

then acts on all three channels together or iii) a combination of both variants. The first variant allows individual channel matching to precisely account for the specific parasitic elements in each channel. Albeit this trimming method promises the highest possible CMRR for all three DM outputs, it unfortunately influences the DMRR as well. To keep the DMRR at an acceptable level, accurate trimming of all three channels against each other is required. This is because the CM divider only performs the voltage addition according to (4) if all three resistors  $R_1$  have equivalent parallel capacitance (equal impedance over the whole frequency range). When trimming each channel for maximum CMRR, this is not necessarily given. The second variant, however, omits any external capacitance in parallel to  $R_1$  thereby providing the best possible accuracy in the determination of the CM voltage component. It is found that the residual parasitic capacitance of the three resistors is very well controlled with a symmetric PCB layout. This results in a very good DMRR. On the contrary, the CMRR can not be trimmed for each channel separately but thanks to the very symmetric layout the performance of all three channels is improved by matching the the nominal time constant using one single trimming capacitor. In practical applications the calibration/compensation effort must be kept to a minimum. Therefore, despite not yielding the absolute highest possible CMRR in all three channels, variant ii) is a very good compromise between usability and performance and is preferred.

In Fig. 5 the dominant parasitic elements for one channel are highlighted, namely the difference amplifier input capacitances  $C_{\mathrm{OP,DM+}}$  and  $C_{\mathrm{OP,DM-}}$  (2 pF each), the common-mode amplifier input capacitances  $C_{\mathrm{OP,CM+}}$  and  $C_{\mathrm{OP,CM-}}$  (1.3 pF each) and the capacitance  $C_{\mathrm{PCB,CM}}$  of the PCB track connecting the obtained common-mode voltage  $\underline{\nu}_{\mathrm{CM,div}}$  to all three difference amplifiers (measured as roughly 8.5 pF). The resulting node impedances at the inputs of the difference amplifiers are given as

$$\underline{Z}_{DM,-} = \left( R_{E,dm} \left\| R_{G,dm} \right\| \frac{1}{j\boldsymbol{\omega} \cdot C_{OP,DM-}} \right)$$

$$= \frac{\left( R_{E,dm} \left\| R_{G,dm} \right. \right)}{1 + j\boldsymbol{\omega} \cdot C_{OP,DM-} \cdot \left( R_{E,dm} \left\| R_{G,dm} \right. \right)} \tag{20}$$

at the inverting input terminal and

$$\underline{Z}_{\text{DM,+}} = \frac{(R_1/3||R_1||R_1||R_1|)}{1 + j\omega \cdot C_{en} \cdot (R_1/3||R_1||R_1||R_1|)}$$

(21)

at the non-inverting input terminal where

$$C_{\text{eq}} = 3 \cdot C_{\text{OP,DM+}} + C_{\text{OP,CM+}} + C_{\text{CM,PCB}} + C_{\text{trim}}.$$

(22)

Therefore, the two cut-off frequencies

$$f_{c,DM-} = \frac{1}{2\pi \cdot C_{OP,DM-} \cdot R_{E,dm}/2}$$

(23)

$$f_{c,DM+} = \frac{1}{2\pi \cdot C_{eq} \cdot R_1/6},$$

(24)

are obtained, where also the condition  $R_{F,DM} = R_{G,DM}$  is used to simplify the expressions. It should be noted that the parasitic shunt capacitance of the resistors is neglected in this step, since for a 0603 surface mount 1 M $\Omega$  resistor a maximum value of 100 fF was measured with a precision impedance analyzer (Agilent 4294A [38]). This is considerably lower than all the other parasitic capacitances. The frequency  $f_{\rm c, DM^+}$  is likely to be lower than  $f_{c,DM-}$ , since  $C_{eq} = 15.8 \text{ pF}$  (without considering  $C_{\text{trim}}$ ) is much larger than  $C_{\text{OP,DM}}$ . Adding the trim capacitor in parallel to  $R_1/3$  according to Fig. 5 adds more capacitance to the CM node and therefore decreases  $f_{\rm DM,+}$  even more. To end up with  $f_{c,DM-}$  being smaller than  $f_{c,DM+}$ , such that adding more capacitance ( $C_{trim}$ ) to the CM node makes the two frequencies equal, either a large  $R_{\rm F,dm}$  and/or a small  $R_1$  must be chosen. According to [32], the value of  $R_{\text{F,DM}}$  should be chosen in the range of 250  $\Omega$  to 499  $\Omega$  where the maximum value is selected here. This directly defines the upper bound  $R_{1 \text{ max}}$  for the CM divider resistance  $R_1$  as

$$R_{1,\text{max}} = \frac{3 \cdot R_{\text{F,DM}} \cdot C_{\text{OP,DM-}}}{C_{\text{eq}}} = 189.5 \ \Omega \geqslant R_1.$$

(25)

For the presented implementation, a lower value of  $R_{\rm l}=100~\Omega$  is chosen such that matching is still possible even when  $C_{\rm OP,DM-}$  is significantly lower and/or  $C_{\rm eq}$  substantially higher than the respective nominal values. Assuming the parasitic capacitances according to the nominal values and given the above specified resistances,  $C_{\rm trim}$  must be set to 14.2 pF to equalize the two cutoff frequencies.

At this point, again the question could arise why to add even more capacitance to the CM node, instead of adding capacitors parallel to the resistor  $R_1$  in each CM divider. This would indeed facilitate the selection of  $R_1$ ,  $R_{\rm F,DM}$  and  $R_{\rm G,DM}$  but as mentioned would also lead to the necessity of trimming all three channels against each other, in order to get a sufficient DMRR and a flat CMTF apart from the good CMRR. Another option would be to reduce  $f_{\rm c,DM-}$  according to (23) by increasing the capacitance  $C_{\rm OP,DM-}$ . This is, however, undesired because the operational amplifier phase margin is reduced by the placement of any capacitance at the inverting input terminal.

While channel to channel trimming is not needed with the selected trimming method, the CMRR of only one channel can be optimized due to the slightly different  $f_{c,\mathrm{DM}}$  in each channel coming from variations in  $R_{\mathrm{F,DM}}$ ,  $R_{\mathrm{G,DM}}$  and component parasitics. Therefore, slight deviation in the CMRR responses of the three channels are to be expected but can be minimized by careful PCB layout and by using components from the same batch to decrease deviations due to manufacturing process variations.

The DMRR is mainly dependent on the matching of the resistors  $R_1$  in each channel because only if the three upper resistors  $R_1$  are exactly identical, the sum of the three resistor currents is zero for a pure DM excitation, resulting in no output signal at the CM output port.

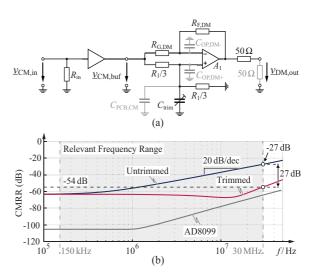

To test the effectiveness of the employed matching method on the CMRR, a reduced version of the circuit from Fig. 4

Fig. 7. (a) Schematic of the configuration used for testing the difference amplifier alone and (b) the resulting CMRR responses for the case where  $C_{\rm trim} = 0$  pF (Untrimmed) and for the case of an optimally trimmed response (Trimmed). In addition, the measured CMRRs are compared to the CMRR of the AD8099 obtained from the datasheet, which equals to the maximum achievable CMRR when all resistors would be perfectly matched and no parasitic components would exist.

was built on a PCB with the exact same layout and parasitic elements as the PCB of the three-phase separator will have. The schematic is shown in Fig. 7(a) and features only one channel with input buffer and difference amplifier. To get the same node impedance at the non-inverting input of the difference amplifier  $A_1$ , the upper resistor is changed from  $R_1$ to  $R_1/3$ , resulting in the same effective resistance as on the three-phase separator for CM excitation. The only difference between the final separator and the given test circuit is the absence of the two other channels as well as the CM buffer amplifier. The transfer characteristic was measured using a network analyzer (Omicron Lab Bode 100 [39]) and the result is shown in Fig. 7(b) where the relevant EMI frequency range between 150 kHz and 30 MHz is highlighted. The LF CMRR is around -63 dB, hence 11 dB worse than the expected value of -74 dB resulting from the resistor tolerances. This can be explained by the fact that the absolute deviation of  $R_1 = 100 \ \Omega \pm 0.01 \ \%$  is only  $\pm 10 \ \text{m}\Omega$ . Therefore, the total error is also strongly influenced by factors such as the solder joint and PCB track resistance. A PCB track with a width of 0.2 mm and a length of 5 mm already has a dc resistance of 12 m $\Omega$  and predominates the error. The LF CMRR could be improved by employing a resistive trimmer (or higher values of the resistors, yet below the limit of (25)), however, the value of -60 dB is sufficient for the targeted application and hence further LF trimming is omitted. At elevated frequencies the untrimmed circuit shows insufficient performance as the CMRR already starts to increase with +20 dB/dec at around 300 kHz, reaching a value of only -27 dB at 30 MHz. After trimming with the aforementioned method, a significant performance improvement is observed and the CMRR of -63 dB is maintained up to around 20 MHz before it increases, reaching a value of -54 dB at 30 MHz. The improvement of 27 dB (factor of 22) compared to the untrimmed circuit proves that the applied trimming method works as intended.

## C. Difference Amplifier

Up to now, an ideal difference amplifier was assumed and the only degradation in the separator performance was addressed to an asymmetry in the layout and/or component mismatch. In reality, a difference amplifier has only a limited CMRR, typically getting worse towards higher frequencies due to internal mismatches. This results in a limited maximum possible CMRR even for perfect matching of the amplitude and phase at the amplifier input ports. The selected difference amplifier (AD8099) features a very good HF CMRR which is also indicated in Fig. 7(b) and it is observed that at low frequencies, the resulting overall performance is limited by a resistive mismatch, while at frequencies above 10 MHz it is very close to the performance of the amplifier itself and therefore is mainly limited by the internal CMRR and not by the parasitics or capacitor trimming [40].

#### D. Distortion and Noise Considerations

Another important aspect is to have low noise and distortion at the output ports. Otherwise, significant spurs in the measured spectrum could occur even without a EUT connected, leading to misinterpretation of the obtained measurements. Noise concerns are less critical due to the fact that the EMI test receiver has a measurement bandwidth of only 9 kHz. Therefore, broadband noise has minor influence on the total displayed noise floor. Other distortions, however, can occur for various reasons, such as switching spurs on the supply rails or harmonic distortion in the amplifiers. To mitigate the former, a two-stage power supply with switched-mode and linear regulators is employed. The switched-mode supplies regulate the input voltage to a value that is just above the minimum required linear regulator input considering the dropout. The linear regulators are selected for a high power supply rejection ratio (PSRR) at the given switching frequencies. Very little distortion on the analog supply rails is therefore expected.

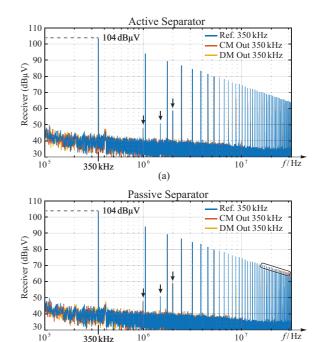

The remaining distortions are reduced by the good harmonic distortion performance of the employed operational amplifiers. Fig. 8 shows the measured output spectra for a 104 dBµV 350 kHz rectangular input voltage for (a) the active and (b) the passive noise separator. The input voltage (blue spectrum) is applied either as CM or DM with the corresponding separator output spectra highlighted in orange (CM) and yellow (DM), respectively. The measurements reveal that there is no added harmonic distortion due to non-linear operation of the amplifier, even though the selected amplitude of the reference input is significantly higher than the EMI standards limiting values. However, three unexpected spectral components occur, which are equally strong in the reference and the output spectra (both active and passive). Therefore, they originate from the arbitrary waveform generator utilized to apply the input signal. The slightly increased output at frequencies above 15 MHz in the passive separator does not occur in the active one. Similar

Fig. 8. Test spectrum of a  $104~dB\mu V$  350 kHz rectangular signal (blue) and the corresponding CM (orange) and DM (yellow) output spectra for (a) the active noise separator in comparison with (b) the passive noise separator. The highlighted non-expected spectral components are due to the signal source (arbitrary waveform generator), since they occur in the reference as well as in the output spectra.

(b)

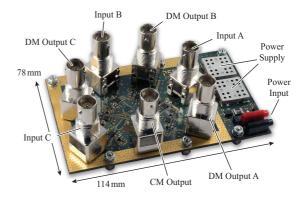

Fig. 9. Picture of the proposed three-phase active CM/DM noise separator showing all input and output connections as well as the auxiliary power supply.

measurements were performed when an additional 123 dB $\mu$ V 50 Hz component is added to the reference input to verify that there are no non-linear distortions due to intermodulation effects with a LF component.

## E. Realized Hardware Prototype

A picture of the realized hardware prototype considering all the above mentioned effects is shown in Fig. 9 with labeled input and output ports as well as auxiliary power supply. The overall dimensions of  $114 \text{ mm} \times 78 \text{ mm}$  result mainly from the employed BNC connectors and also partially from restrictions of the component placement due to the symmetry

Fig. 10. (a) Schematic of the CM adapter which is basically a very well matched power splitter with  $\underline{Z}_{in} = 50~\Omega$ , providing the input signal  $\underline{\nu}_{CM,in}$  on each of its output ports A, B and C with equal magnitude and phase. Picture of (b) the top side and (c) the bottom side of the assembled adapter showing the matched traces from the input to each output port.

requirements. Further miniaturization could be achieved by using smaller coaxial connectors (e.g. SMA or SMC).

A prominent difference compared to a passive noise separator is the requirement for an external power supply. However, the power consumption of measurement equipment is usually not of great importance, since there is not a continuous operation. Therefore, the total power consumption of 1.5 W, which is mainly composed of the quiescent power of the operational amplifiers, is acceptable, in particular in comparison with the several tens of watts that are consumed by the EMI test receiver. The measurement signal is loaded with an entirely resistive 50  $\Omega$  impedance, hence it does not significantly contribute to the losses.

## V. Measurement Procedure and Results

#### A. Signal Injection Adapters

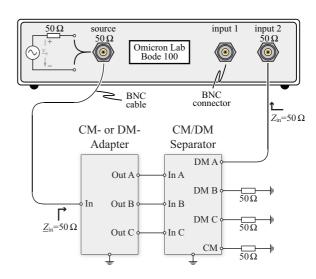

To characterize the overall performance of the three-phase active noise separator, a test setup that allows to apply pure CM or DM input signals to the separator and measure the corresponding outputs is used. The input signal is applied through matched adapter PCBs, one for CM and three for DM, which can be directly plugged on top of the separator. The stringent symmetry and matching requirements from the separator PCB layout equally apply to those adapters.

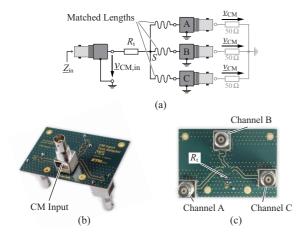

Providing a CM input is straight forward and in Fig. 10(a) the schematic of the utilized CM signal adapter is shown. It is implemented as purely resistive power splitter with one input port, to which a signal generator is connected, and three output ports which are connected to the separator. The CM adapter shows a nominal impedance of 50  $\Omega$  when looking into the input port, provided the three output ports are terminated with 50  $\Omega$ , which is inherently given when the CM adapter is connected to the separator. Such an implementation guarantees

Fig. 11. (a) Magnitude and phase response of the three channels on the CM adapter and (b) the calculated maximum measurable CMRR (*CMRR*<sub>Adapter</sub>) for channels A, B and C, assuming an ideal separator with the only asymmetry arising from the CM adapter.

that the signal source connected to the input is properly terminated and no reflections occur. At the same time it can be realized with only one resistor  $R_t$  and without the need of having an additional series resistor between the star-point S (cf. Fig. 10) and each output port. The resistor  $R_t$  in Fig. 10 is chosen such that in series with the parallel combination of the three 50  $\Omega$  terminations at the output ports an input impedance  $\underline{Z}_{in}$  equal to the nominal coaxial cable impedance of  $\underline{Z}_0 = 50 \Omega$  results, i.e,

$$R_{\rm t} = R_{\rm out} - \frac{R_{\rm out}}{3} = \frac{2}{3} R_{\rm out} \stackrel{R_{\rm out}}{=} 500 \ 33.\overline{3} \ \Omega.$$

(26)

Given the value  $R_t$ , the theoretical insertion loss, i.e., the attenuation  $G_{\text{CM},i,\text{theo}}$  of the CM input signal in the CM adapter, is derived as

$$G_{\text{CM,i,theo}} = \frac{(R_{\text{out}} || R_{\text{out}} || R_{\text{out}})}{R_{\text{i}} + (R_{\text{out}} || R_{\text{out}} || R_{\text{out}})} = \frac{1}{3} = -9.54 \text{ dB.} \quad (27)$$

The implementation with a single resistor is favorable, since the focus of the CM adapter is to guarantee minimum channel-to-channel imbalance between A, B, and C and therefore, any component between the star-point S and the output ports with its inevitable tolerances would change the transfer behavior, especially the phase response as explained above. The three tracks from the star-point towards each of the output ports are length-matched and impedance-matched, resulting in an overall channel-to-channel skew of less than 2 ps, corresponding to a phase shift of around  $0.02^{\circ}$  at 30 MHz.

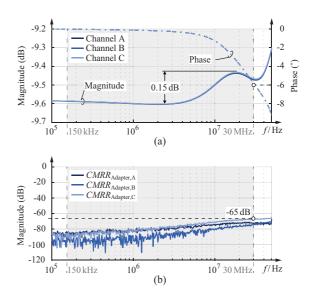

Fig. 10(b) and (c) show pictures of the realized CM adapter while Fig. 11(a) shows the measured amplitude and phase responses of the transfer functions of all three channels of only the CM adapter. Note, that each channel is measured

Fig. 12. (a) Schematic drawing of the DM adapter which by means of a wideband transformer with secondary center-tap configuration converts a single-ended input signal  $\underline{\nu}_{\rm DM,in}$  to differential output voltages  $\underline{\nu}_{\rm DM,+}$  and  $\underline{\nu}_{\rm DM,-}$  being connected to two of the output ports, while the third is connected to ground via a termination resistor. There exist three variants of the DM adapter with either phase A, B or C connected to ground respectively (*DMA*, *DMB*, *DMC*). In (b) and (c) pictures of the top and bottom side of the variant *DMA* are shown, again indicating the matched traces on the board to equalize the propagation delay to ensure maximum symmetry.

separately with the network analyzer while the other two are terminated with 50  $\Omega$ . The measured insertion loss closely matches the nominal value of -9.54 dB calculated in (27) and the magnitude deviation is maximum 0.15 dB within the considered frequency range while the phase turns by  $-6^{\circ}$ . Between the three channels, however, no significant magnitude and phase imbalance is visible. From these measured transfer functions  $\underline{G}_{\text{CM,A}}$ , ...,  $G_{\text{CM,C}}$ , the theoretically maximum measurable CMRR

$$CMRR_{\text{Adapter,i}} = \frac{\underline{G}_{\text{CM,i}} - (\underline{G}_{\text{CM,A}} + \underline{G}_{\text{CM,B}} + \underline{G}_{\text{CM,C}})/3}{(\underline{G}_{\text{CM,A}} + \underline{G}_{\text{CM,B}} + \underline{G}_{\text{CM,C}})/3}$$

(28)

for  $i = \{A, B, C\}$  is calculated under the assumption of an ideal separator based on (4) and (5). This means that the only error contribution to the CMRR is the imbalance of the three CM adapter channels, which must be much lower than the CMRR error contribution of the separator in order to properly quantify the CMRR performance of the separator. The maximum measurable CMRR according to (28) is corrected for the adapter insertion loss.

The results are shown in Fig. 11(b) and at 30 MHz a CMRR of at least –65 dB is achieved for all channels. Considering the results from the previous measurements with the difference amplifier (cf. Fig. 7), this is sufficient to characterize the separator. It has to be emphasized, that the CMRR responses in Fig. 11(b) are created by post-processing based on measurements taken consecutively. Hence, a potential repeatability error of the network analyzer is included in these calculations.

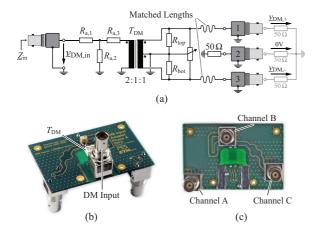

Besides a CM adapter for the DMRR performance evaluation of the separator also a DM adapter is needed, since it is very difficult to generate a perfectly symmetric three-phase

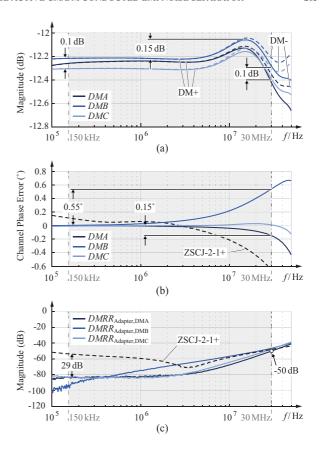

Fig. 13. (a) Amplitude responses for all three DM adapter variants (DMA, DMB and DMC), showing the ratio  $G_{DM,+} = \mathcal{V}_{DM,-}/\mathcal{V}_{DM,in}$  (solid lines) and  $G_{DM,-} = \mathcal{V}_{DM,-}/\mathcal{V}_{DM,in}$  (dashed lines) respectively, (b) the deviation from the nominal phase difference of 180° and (c) the maximum measurable DMRR assuming an ideal separator (corrected for the DM adapter insertion loss). In addition, (b) and (c) show the phase error and maximum measurable DMRR when using a commercial power splitter [42] (dashed line).

CM free DM system. Thus, the DM characteristics were tested using a DM signal adapter that excites only two phases with two signals 180° out of phase and leaves the third phase connected to ground, as shown in Fig. 12(a). The input signal is fed to a wideband signal transformer (Mini-Circuits T1-6T-KK81+ [41]) whose center-tap configured secondary side is connected to two of the separator's input channels, providing two signals with half the magnitude and a phase shift of 180°, denoted as  $\underline{\nu}_{\rm DM^+}$  and  $\underline{\nu}_{\rm DM^-}$ . Imbalances in the transfer ratio from primary side to the two secondary sides can be adjusted with the two resistors  $R_{\text{top}}$  and  $R_{\text{bot}}$ , both set to 50  $\Omega$  nominally. Although the circuit would also work with no connection of the center-tap, measurements showed better performance when it is connected to the ground potential. The third separator input is terminated with 50  $\Omega$  to ground and therefore three variants of the DM adapter exist, hereinafter denoted with DMA, DMB and DMC, where the last letter denotes the phase that is connected to ground. All three adapters fulfill (4) when setting  $\underline{v}_{CM}$  to zero, i.e.,  $\underline{v}_{DM^+} + \underline{v}_{DM^-} = 0$ . The resistive -6 dB attenuator composed of  $R_{a,1...3}$  at the input ensures an input impedance  $\underline{Z}_{in}$  sufficiently close to 50  $\Omega$  despite the frequency dependent transformer impedance transfer ratio.

In Fig. 13(a) the magnitude responses for both DM chan-

nels (DM+ and DM-) of all three DM adapters are shown. The insertion loss is around -12.2 dB for all three adapters and the worst-case channel imbalance occurs for DMC where the two responses DM+ (solid lines) and DM- (dashed lines) deviate by 0.1 dB at 30 MHz. The overall shape is very similar for all adapters and a flatness of 0.15 dB is achieved. Fig. 13(b) shows the phase error between the DM+ and DM- channels in each adapter, i.e., the deviation from the nominal 180° phase shift. Here, it can be seen that *DMC* performs best with almost no phase error whereas DMA shows a deviation of 0.15° and DMB 0.55° respectively, both measured at 30 MHz. As a comparison, the same measurement was performed with a commercially available power splitter (Mini-Circuits ZSCJ-2-1+ [42]), which shows even more phase imbalance (around 0.7°). Based on the complex DM transfer functions  $\underline{G}_{DMi+}$  and  $\underline{G}_{\mathrm{DM},-}$  from the input  $\underline{v}_{\mathrm{DM},\mathrm{in}}$  to the respective outputs  $\underline{v}_{\mathrm{DM},+}$  and  $\underline{v}_{DMi-}$  ( $i = \{A, B, C\}$ ) the maximum measurable DMRR for each adapter

$$DMRR_{\text{Adapter,DM}i} = \frac{(\underline{G}_{\text{DM}i,+} + \underline{G}_{\text{DM}i,-})/3}{\underline{G}_{\text{DM}i,-}}$$

(29)

is calculated in accordance with (4). It corresponds to the ratio of the voltage at the CM output port of an ideal separator with respect to its DM input voltage and it is only affected by asymmetries of the DM signal adapters. The resulting responses are depicted in Fig. 13(c) and for a simpler comparison to the results of the separator (cf. Fig. 15), the DMRR<sub>Adapter,DM,i</sub> responses are corrected for the nominal insertion loss of the corresponding DM signal adapter. Since the magnitude response of both,  $\underline{G}_{\mathrm{DM}i,+}$  and  $\underline{G}_{\mathrm{DM}i,-}$  is almost identical (cf. Fig. 13(a)), it does not matter which of the two is taken for the correction in (29). It can be seen that for frequencies below 3 MHz a DMRR better than -80 dB can be measured. At elevated frequencies, however, the DMRR starts to rise and at 30 MHz the error contribution due to asymmetries in the DM adapters gives a DMRR of -50 dB, which means that even if the separator would achieve a DMRR better than -50 dB, a DMRR worse than -50 dB would be measured, since the adapter board is limiting the maximum measurable DMRR. All three DM adapters achieve approximately the same DMRR at 30 MHz, since e.g. DMB has a considerable phase deviation but a very low amplitude error whereas DMC has almost no phase deviation but the highest amplitude error. It is observed that DMB shows inferior performance compared to the other two adapters, which can be improved with better trimming of  $R_{\text{top}}$  and  $R_{\text{bot}}$  on the secondary side (cf. Fig. 12). Additionally, the same curve is shown for the commercial power splitter and the achievable performance is worse particularly at low frequencies (29 dB worse), which justifies the usage of the custom-made adapters.

*Remark:* Instead of two input signals with 180° phase shift a three-phase DM system with 120° phase shift between the individual signals could be realized with a digital signal processor (DSP) or a field-programmable gate array (FPGA). However, to achieve a phase accuracy of 0.5° as it is reported

Fig. 14. Test setup for measuring the active separator characteristics using the Omicron Lab Bode100 network analyzer. The CM or DM input from the Bode100 source is fed to the separator via the CM- or DM-adapter shown in Fig. 10 and 12 respectively and the corresponding output is directly connected back to the Bode100 receiver input, while all other separator outputs are terminated with 50  $\Omega$ .

for the presented DM signal adapters (cf. Fig. 13(b)), particularly at high signal frequencies, a time resolution in the sub-nanosecond range would be required. This would be very difficult to realize in practice and therefore, the purely passive DM signal adapters are a very convenient method.

#### B. Measurement Setup

The separator transfer and rejection characteristics are captured using the Omicron Lab Bode100 network analyzer with the corresponding test setup shown in Fig. 14. The output of the network analyzer is fed to the separator via the CM or one of the DM adapters. The output port to be measured (DM output A in Fig. 14) is connected to the receiver of the analyzer while all others are terminated with 50  $\Omega$ . All the transfer and rejection characteristics shown hereinafter are corrected with respect to the adapter insertion loss, such that for example a unity gain CMTF means that there is no attenuation between a CM input signal at ports InA, InB and InC of the separator and the corresponding CM output port CM.

## C. Separator Transfer Function and Rejection Ratio Measurements

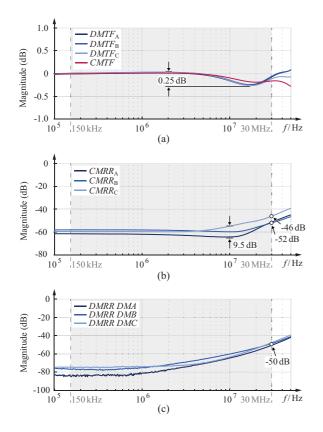

The resulting separator transfer and rejection characteristics are indicated in Fig. 15. The DMTF and CMTF in Fig. 15(a) are very flat, showing an absolute deviation of less than 0.25 dB and practically no relative deviation (< 50 mdB) over the whole considered frequency range with nominal unity gain, i.e., 0 dB. The CMRR in Fig. 15(b) is very similar to the response found for the difference amplifier (cf. Fig. 7), starting at -60 dB and staying at this value until around 10 MHz, before reaching values of -52 dB (channels A and B) and -46 dB (channel C) at 30 MHz. Although there are three channels, the

Fig. 15. Comparison of the transfer characteristics of the active three-phase noise separator, showing (a) the DMTF of all three channels as well as the CMTF, (b) the CMRR (measured at all three DM output ports) and (c) the DMRR (measured with the three different DM signal adapters).

previously mentioned trimming method can only optimize the CMRR of one channel (here channel A which consequently shows the best CMRR). While channels A and B show very similar behavior at high frequencies, channel C shows a slightly worse (9.5 dB worse at 10 MHz), yet still sufficiently good performance, which can be explained with different parasities in amplifier  $A_6$  and/or a mismatch in  $R_{\rm F,DM}$  or  $R_{\rm G,DM}$ compared to the other channels. The difference at lower frequencies is again explained with the influence of parasitic resistances from the PCB tracks, soldering joints etc. which are superimposed to the 0.01 % tolerance of the resistors. The DMRR depicted in Fig. 15(c) starts at around -80 dB at low frequencies and reaches -50 dB at 30 MHz. There are three responses *DMRR DMi*,  $i = \{A, B, C\}$  illustrated, since the CM output port is measured for an excitation with each of the three DM adapters *DMi*. The deviation between these three curves is explained with the slightly different transfer characteristics of the DM adapter (cf. Fig. 13) as well as with the selected trimming method where only one channel can be optimized. Interestingly, comparing Fig. 13(c) with Fig. 15(c), the high-frequency DMRR is mainly determined by the finite symmetry of the DM signal adapters, therefore it is very likely that the separator performs better than the measurements here indicate. Important to note is that due to the unity gain CMTF and DMTFs the selectivities, i.e., DMTF/CMRR and CMTF/ DMRR are simply the inverse of the CMRR and DMRR and are not explicitly shown here.

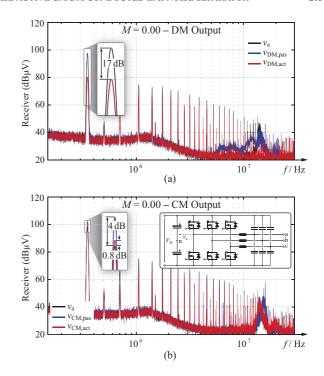

Fig. 16. Noise spectra captured with a three-phase voltage source inverter. (a) DM and (b) CM output spectrum for a converter modulation depth M=0. This corresponds to pure CM switching noise. A comparison measurement using a passive noise separator is performed as well. The overall noise level is deliberately selected considerably higher than the EMI standards to highlight the separator dynamic range.

## D. Separator Converter Measurements

Finally, spectral measurements with a three-phase voltage source inverter are performed using the presented active noise separator to demonstrate its practical applicability. Comparison measurements with a pre-existing passive separator allow a performance comparison between the two variants. The test setup from Fig. 1 is extended by placing the noise separator between the LISN [43] and the EMI test receiver [44]. Fig. 16 shows measured spectra for zero modulation depth (M = 0). This corresponds to the case where the three bridge-legs are switching ( $f_{sw} = 350 \text{ kHz}$ ) but do not generate any output voltage, resulting in pure CM noise. Measurements are taken at (a) the DM output port and (b) the CM output port. The tested inverter is not mains-interfaced and therefore does not need to comply with the EMI regulations. Hence, in all cases the measured values are exceeding the limiting values. This case allows to illustrate the function of the separator also with large input signals. The black curves denote the total phase voltage noise spectrum, whereas the red and blue curves are the measurement results obtained with the active and passive noise separator, respectively. In addition, Fig. 16(b) shows the utilized converter structure. Its output filter is referenced to the dc link and therefore, the filter components are effective for CM and DM noise. It is clearly visible that the separator CMRR is not the limiting factor, since the switching frequency DM component is only 17 dB below the total noise voltage component. This demonstrates, that a reliable decomposition of EMI noise into CM and DM components does not only require a high performance noise separator but also a very symmetric overall test setup. The connection cables and the LISNs must meet the same strict symmetry requirements as the separator itself. The measurements shown here are obtained using a standard commercial test setup and reveal insufficient symmetry of the test setup. For the sake of brevity, a further investigation of the influence of the test setup is omitted here. The underlying considerations, however, would be exactly the same as presented in this work for the design of the noise separator. Cables must be length-matched closer than 1 mm and the magnitude and phase response of the LISNs must be very closely matched.

Overall, the presented spectral measurements proof the practical applicability of the active noise separator even for very large noise voltages. Furthermore, the high frequency behavior is considerably better compared to the passive separator, which particularly suffers from a insufficient CMRR as revealed by the substantial noise components at its DM outputs (cf. Fig. 16(a)). It becomes clear that a practical measurement setup contains many asymmetries, which can only be determined and quantified when a high performance noise separator is used.

#### VI. CONCLUSION

In this paper, an active three-phase EMI CM/DM noise separator is presented. The device is used to distinguish between CM and DM noise in the measured total spectrum of the conducted emissions and therefore allows to optimize the corresponding CM and DM filters accordingly. Relevant performance metrics are introduced, namely the CM and DM transfer functions and rejection ratios as well as the selectivities, before the challenges involved in the design and layout of such a separator to meet the required performance are explained, in particular the influence of parasitic capacitances. A very simple procedure that requires the adjustment of only one variable capacitor is sufficient to achieve a very good performance and in particular, there is no need to match all three phases against each other. In addition, the presented active separator does not contain any magnetic components which are very difficult to match precisely and usually are big in size. The usage of precision resistors and the careful PCB layout allow very reliable measurements and repeatable performance.

A measurement procedure to evaluate the proposed separator is established and it is shown how this already imposes limitations in respect of the maximum measurable performance. The CM and DM transfer characteristics (CMTF and DMTF) show very little deviation from the ideal unity gain behavior over the whole considered frequency range between 150 kHz and 30 MHz. At the lower frequency end the separator achieves –60 dB of both, CMRR and DMRR, limited by the resistive matching, whereas the HF CMRR of roughly –50 dB is defined by the remaining phase mismatch between the three phase signals and the derived CM voltage. The HF DMRR of

Fig. 17. (a) Internal structure for one channel of a commercially available LISN. Indicated are the power and HF signal flow. (b) Measured and simulated transfer function from EUT port ( $\nu_{\text{EUT}}$ ) to HF measurement port ( $\nu_{\text{HF}}$ ).

-50 dB is likely to be limited by the asymmetry of the three DM signal adapters used to excite the separator with a DM signal and not by the separator itself.

The residual channel-to-channel mismatch is attributed to the selected trimming method, involving only one adjustable capacitor and therefore to the limitation that only one channel can be optimized but with the big advantage of a very straightforward and fast trimming procedure.

To use the very high performance of the presented separator in a typical power electronics CE EMI test setup, the described symmetry constraints and matching of the external components such as the LISNs, connecting cables as well as the EUT itself is very important. Otherwise, CM noise from the converter could misleadingly be attributed as DM error or vice versa, resulting in the adjustment of the wrong filter part. Hence, subject to future research is a detailed analysis of the influence of various external components on the overall measurement performance with the aim to provide a guideline for valid measurements and the corresponding interpretation.

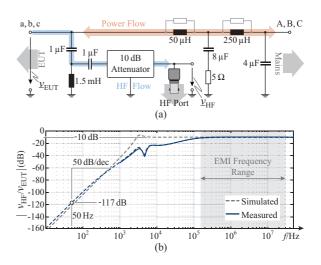

# APPENDIX: INTERNAL LISN STRUCTURE

Fig. 17(a) shows the internal structure of a commercially available LISN [43] according to the CISPR 16-1-2 standard [7]. The EUT is decoupled from the mains with large cylindri-cal aircore inductors (50  $\mu H$  and 250  $\mu H$ ) and capacitors. Resonances are damped with resistors in parallel to the large inductors. The HF signal (highlighted in blue) passes through a high-pass filter composed of two 1  $\mu F$  capacitors and a 1.5 mH inductor. Low frequency signals such as the 50/60 Hz component related to the power flow (highlighted in red) are heavily attenuated. Below the high-pass filter cut-off frequency of around 6 kHz the gain drops with around -50 dB/dec. This is illustrated in Fig. 17(b) with the simulated and measured transfer function  $|\underline{\nu}_{HF}/\underline{\nu}_{EUT}|$  from the EUT input port to the HF measurement port (blue lines). The 50/60 Hz mains voltage component with a peak value of 325 V is attenuated by almost 120 dB, hence only around 0.5 mV appear

at the HF measurement port. This particular LISN model features an additional 10 dB attenuator to protect measurement equipment connected to the HF port from large voltages that can occur if the EMI noise is not attenuated sufficiently by the EMI filter in the EUT. In the relevant frequency range, the transfer function is flat and only the 10 dB attenuation remains.

Remark: The roll-off with roughly -20 dB/dec starting at around 100 kHz is due to the network analyzer's internal  $50~\Omega$  resistor in series with its output port. Together with the EUT port impedance that is lower than  $50~\Omega$  at frequencies below 150~kHz, this leads to an additional apparent filtering behavior. In practice this does not influence the attenution of the 50/60~Hz component as verified with the gray dashed line that corresponds to the simulated transfer function where the effect of the network analyzer's internal  $50~\Omega$  resistor is corrected.

## REFERENCES

- International Electrotechnical Commission (IEC), "CISPR 11: Limits and methods of measurement of electromagnetic disturbance characteristics of industrial, scientific and medical (ISM) radiofrequency equipment," Tech. Rep., 1990.

- [2] International Electrotechnical Commission (IEC), "CISPR 14: Limits and methods of measurement of radio interference characteristics of household electrical appliances, portable tools and similar electrical apparatus," Tech. Rep., 1985.

- [3] M. Hartmann, H. Ertl, and J. W. Kolar, "EMI filter design for a 1 MHz, 10 kW three-phase/level PWM rectifier," in *IEEE Transactions on Power Electronics*, vol. 26, no. 4, pp. 1192–1204, Apr. 2011.

- [4] H. Peng, R. Ramabhadran, R. Thomas, and M. J. Schutten, "Comprehensive switching behavior characterization of high speed gallium nitride E-HEMT with ultra-low loop inductance," in *Proceedings* of the 5th IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Albuquerque, NM, USA, 2017, pp. 116–121.

- [5] F. Lin and D. Chen, "Reduction of power supply EMI emission by switching frequency modulation," in *IEEE Transactions on Power Electronics*, vol. 9, no. 1, pp. 132–137, Jan. 1994.

- [6] N. Oswald, P. Anthony, N. McNeill, and B. H. Stark, "An experimental investigation of the tradeoff between switching losses and EMI generation with hard-switched all-Si, Si-SiC, and all-SiC device combinations," in *IEEE Transactions on Power Electronics*, vol. 29, no. 5, pp. 2393–2407, May 2014.

- [7] International Electrotechnical Commission (IEC), "CISPR 16: Specification for radio disturbance and immunity measuring apparatus and methods part 1-2: Radio disturbance and immunity measuring apparatus coupling devices for conducted disturbance measurements," Tech. Rep., 2015

- [8] M. Schutten, S. Prabhakaran, D. Karipides, J. Nasadoski, and R. Thomas, "High frequency EMI filter parasitic characterization," in *Proceedings* of 2011 IEEE Vehicle Power and Propulsion Conference, Chicago, IL, USA, 2011, pp. 1–8.

- [9] K. S. Kostov, S. Schroth, F. Krismer, M. Priecinsky, H. P. Nee, and J. W. Kolar, "The input impedance of common-mode and differential-mode noise separators," in *IEEE Transactions on Industry Applications*, vol. 51, no. 3, pp. 2352–2360, May–Jun. 2015.

- [10] M. Heldwein, J. Biela, H. Ertl, T. Nussbaumer, and J. W. Kolar, "Novel three-phase CM/DM conducted emission separator," in *IEEE Transactions on Industrial Electronics*, vol. 56, no. 9, pp. 3693–3703, Sep. 2009.

- [11] J. Dobusch, P. Konarski, D. Kuebrich, and T. Duerbaum, "Implementation of voltage based three-phase CM/DM noise separation on the drive side," in *Proceedings of the 20th European Conference on Power Electronics* and Applications (EPE ECCE Europe), Riga, Latvia, 2018, pp. 1–9.

- [12] C. R. Paul, in *Introduction to Electromagnetic Compatibility*, Hoboken, NJ, USA: John Wiley & Sons, Inc., Sep. 2005, vol. 38, no. 7–8.

- [13] M. J. Nave, "A novel differential mode rejection network for conducted

- emissions diagnostics," in *National Symposium on Electromagnetic Compatibility*, Denver, CO, USA, 1989, pp. 223–227.

- [14] C. R. Paul and K. B. Hardin, "Diagnosis and reduction of conducted noise emissions," in *IEEE Transactions on Electromagnetic Compatibility*, vol. 30, no. 4, pp. 553–560, Nov. 1988.

- [15] A. Nagel and R. W. D. Doncker, "Separating common mode and differential mode noise in EMI measurement," in *EPE Journal*, vol. 10, no. 2, pp. 27–30, Aug. 2000.

- [16] K. Y. See, "Network for conducted EMI diagnosis," in *Electronics Letters*, vol. 35, no. 17, pp. 1446–1447, Aug. 1999.

- [17] M. C. Caponet, F. Profumo, L. Ferraris, A. Bertoz, and D. Marzella, "Common and differential mode noise separation: Comparison of two different approaches," in *Proceeding of 2001 IEEE 32nd Annual Power Electronics Specialists Conference*, Vancouver, BC, Canada, 2001, pp. 1383–1388.