# Three-Phase Two-Third-PWM Buck-Boost Current Source Inverter System Employing Dual-Gate Monolithic Bidirectional GaN e-FETs

Mattia Guacci\*, *Student Member, IEEE*, Daifei Zhang\*, Mina Tatic\*, Dominik Bortis\*, *Member, IEEE*, Johann W. Kolar\*, *Fellow, IEEE*, Yusuke Kinoshita§, and Hidetoshi Ishida§, *Member, IEEE*

\* Power Electronic Systems Laboratory, ETH Zurich, Zurich, Switzerland Energy Solution Development Center, Industrial Solutions Company, Panasonic Corporation, Osaka, Japan

Corresponding Author: Mattia Guacci, ETL I12, Physikstrasse 3, 8092 Zurich, Switzerland (CH) E-Mail: guacci@lem.ee.ethz.ch - Telephone: +41 (0)44 632 80 49

Abstract— Latest dual-gate (2G) monolithic bidirectional (MB) gallium nitride (GaN) enhancement-mode field effect transistors (e-FETs) enable a performance breakthrough of current DC-link inverters, e.g. in terms of power conversion efficiency, power density, cost and complexity. In fact, a single 2G MB GaN e-FET can replace the two anti-series connected conventional power semiconductors required in this inverter topology, realizing a four-quadrant (AC) switch with bidirectional voltage blocking capability and allowing controlled bidirectional current flow. Furthermore, as shown in this paper in case of three-phase  $(3-\Phi)$  buckboost (bB) current source inverter (CSI) systems comprising a DC-link current impressing buck-type DC/DC input stage and a subsequent boosttype 3-\Phi current DC-link inverter output stage, a variable DC-link current control strategy, based on a Synergetic Control concept, can be applied to significantly reduce the switching losses occurring in the 3- $\Phi$ inverter. This strategy is denominated Two-Third Pulse-Width Modulation (2/3-PWM), since by properly shaping the DC-link current with the input stage, the desired 3- $\Phi$  sinusoidal load phase currents can be generated by switching, in each switching period, only two out of the three phases of the output stage. Based on comprehensive circuit simulations and analytical calculations, a detailed explanation of the developed modulation and control schemes in different operating conditions is provided, and the reduction of losses enabled by 2/3-PWM is confirmed. Next, the seamless transition of the 3- $\Phi$  bB CSI system from 2/3-PWM to conventional 3/3-PWM is demonstrated. Finally, a 3.3 kW 3- $\Phi$  bB CSI system, applying 2/3-PWM and employing research samples of 2G MB GaN e-FETs in the 3- $\Phi$  inverter, is estimated to achieve an efficiency of 98.4 % and a power density of 18 kW/dm3 (295 W/in3) at a switching frequency of 140 kHz.

Index Terms— Dual-Gate Monolithic Bidirectional Gallium Nitride Enhancement-Mode Field-Effect Transistor, Three-Phase Buck-Boost Current Source Inverter System, Variable DC-Link Current Control.

#### I. INTRODUCTION

The three-phase  $(3-\Phi)$  voltage DC-link inverter is the industry preferred solution to perform compact and efficient DC/AC energy conversion in variable speed drives (VSDs) and/or grid connected power electronic applications. To comply with the electromagnetic (EM) regulations and, in case of VSDs, to avoid excessive losses in the electric machine, insulation stress and bearing wear-out [1], filter circuits are connected at the output of voltage DC-link inverters to generate continuous output voltage waveforms [2]–[4]. To limit the size and/or cost of the output filter, but also to increase the control bandwidth of the system, high frequency, e.g.  $100\,\mathrm{kHz}$ , VSDs are employed. In this context, wide band-gap (WBG) semiconductors, i.e. gallium nitride (GaN) and silicon carbide (SiC), become key technologies to preserve a high power conversion efficiency, even outperforming conventional silicon (Si) based solutions [5]. Additionally, when the supplying DC input voltage varies in a wide range, e.g.

when it is provided by the traction battery of an electric vehicle (EV) [6] or by a string of photovoltaic (PV) panels [7], voltage DC-link inverters are preceded by a boost-type DC/DC converter input stage [8], which regulates the DC input voltage of the 3- $\Phi$  inverter. Hence, the so obtained two-stage converter (including the output filter), i.e. a 3- $\Phi$  boost-buck (Bb) voltage source inverter (VSI) system, can operate in a wide DC input voltage range and generate continuous output voltage waveforms, thus fulfilling the requirements of modern DC/AC power converters [1], [8].

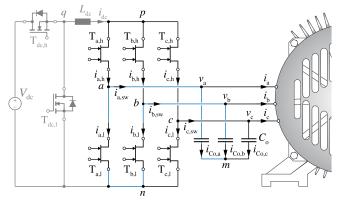

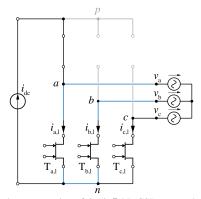

The functionality of a 3- $\Phi$  Bb VSI system can alternatively be achieved with the quasi-dual approach, i.e. the 3- $\Phi$  buck-boost (bB) current source inverter (CSI) system [9]–[11] shown in **Fig. 1**. It comprises a DC-link current impressing buck-type DC/DC input stage (gray) and a subsequent boost-type 3- $\Phi$  current DC-link inverter output stage (black) [12]. Advantageously, the DC-link inductor  $L_{\rm dc}$  forms, in combination with the output capacitors  $C_{\rm o}$ , an integrated output filter; i.e., the 3- $\Phi$  bB CSI system naturally generates continuous output voltage waveforms.

Nevertheless, this quasi-dual solution is rarely adopted, mainly because of the higher count of power devices. In fact, a 3-Φ voltage DC-link inverter only requires six power semiconductors with unidirectional voltage blocking capability allowing controlled

Fig. 1: Schematic of the three-phase  $(3-\Phi)$  buck-boost (bB) current source inverter (CSI) system analyzed in this paper. The boost-type  $3-\Phi$  current DC-link inverter output stage (black) is formed by six 2G MB GaN e-FETs and connected to an electric machine, as in a variable speed drive (VSD) application. The buck-type DC/DC converter input stage (gray), connected to a supplying DC input voltage source, introduces the bB functionality and allows to control and shape the DC-link current  $i_{\rm dc}$ .

bidirectional current flow, such as MOSFETs or IGBTs (with external anti-parallel diodes), which are the most widely used power devices. Consequently, VSI systems are often preferred and, especially when WBG power semiconductors are considered, high power conversion efficiencies and extreme power densities can be achieved at any power level [8], [13].

In contrast, a 3-Φ current DC-link inverter requires six power semiconductors with bidirectional voltage blocking capability, such as, e.g., symmetric GTOs. However, when design constraints demand switching frequencies in the 10-100 kHz range, these switches are preferably realized by anti-series connecting two discrete components, e.g. two power transistors (with external anti-parallel diodes) [14]. This ultimately causes an increase of chip area, cost, driving complexity and conduction losses, which disfavor CSI systems in comparison with VSI systems. However, the unprecedented performance of WBG devices, enabling a significant reduction of switching and conduction losses compared to Si MOSFETs at a given operating point, stimulate further research on current DC-link converters featuring GaN [15] or SiC [16] power semiconductors. Additionally, recent development in the power semiconductor industry culminated in the realization of monolithic bidirectional [17] (MB) GaN enhancementmode field-effect transistor (e-FET) research prototypes [18]-[21] which feature bidirectional voltage blocking capability and allow a controlled current flow in both directions, i.e. excellently fit the requirements of current DC-link inverters. In particular,  $\pm 600\,\mathrm{V}$  $26\,\mathrm{m}\Omega$  research samples of a dual-gate (2G) MB GaN e-FET [22] are available from a major manufacturer of power semiconductors. Preliminary tests on these devices are performed in [23], however, their potential in a 3- $\Phi$  bB CSI system still remains unclear.

Beside these new components, other intrinsic characteristics [15] of  $3-\Phi$  bB CSI systems motivate the research on this circuit topology. In fact, while voltage DC-link inverters switch a constant voltage and a variable current, the opposite is true for current DC-link inverters. Since the switching losses are typically stronger influenced by the switched voltage than by the switched current [24], lower switching losses might occur in the current DC-link approach for the same processed power [25], eventually resulting in overall higher efficiencies [26]. Moreover, although capacitors (voltage DC-links) have a higher energy storage density than inductors (current DC-links), a lower boundary for their volume is given by their current rating [27]. Differently, higher switching frequencies, i.e. WBG semiconductors, always enable the downsizing of magnetic components. Additionally, different costs, operating temperature ranges, critical environmental conditions, failure modes and failure rates are associated to capacitors and inductors. Hence, current DC-link inverters potentially show advantages over voltage DC-link inverters in certain applications.

In this paper, the operating principle of the 3- $\Phi$  bB CSI system is introduced in **Section II**. Ideal waveforms of the 3- $\Phi$  inverter support the explanation of a variable DC-link current control strategy denominated *Two-Third Pulse-Width Modulation* (2/3-PWM) [28]–[31]. Although the basic principle of 2/3-PWM is originally presented in [29], [30], this is as well briefly summarized in **Section III** to provide a common basis for the subsequent analysis, which focuses on its range of applicability, resulting stress on the circuit components, e.g. switching losses, and operation supported by comprehensive simulation results (also in case of non-unity load power factor and load steps). In particular, analytic calculations, performed in **Section IV**, highlight the performance improvement of the 3- $\Phi$  inverter enabled by this concept. The developed *Synergetic Control* scheme, employed for the 3- $\Phi$  bB CSI system, is described in **Section V** and circuit

**TABLE I:** Nominal specifications of the 3- $\Phi$  bB CSI system shown **Fig. 1**.

|                       | Description                        | Value            |

|-----------------------|------------------------------------|------------------|

| $V_{ m dc}$           | supplying DC input voltage         | 400 V            |

| $\hat{i}_{	ext{out}}$ | peak sinusoidal load phase current | 11 A             |

| $\hat{v}_{	ext{out}}$ | peak sinusoidal output voltage     | $196\mathrm{V}$  |

| $f_{ m out}$          | output frequency                   | $50\mathrm{Hz}$  |

| $P_{\text{out}}$      | output power                       | $3.3\mathrm{kW}$ |

simulations prove its functioning in different operating conditions. The considered 2G MB GaN e-FET research prototypes are presented in **Section VI** and compared to state-of-the-art power semiconductors. A prediction of the efficiency and power density achievable by the 3- $\Phi$  bB CSI system precedes **Section VII**, which concludes the paper. Finally, an experimental hardware, designed to evaluate the switching performance of the 2G MB GaN e-FETs, is described and measured switching waveforms are discussed in the **Appendix**.

#### II. POWER CONVERTER OPERATION

As first step of a comprehensive analysis of the  $3-\Phi$  bB CSI system shown in **Fig. 1**, its operating range and operating principle are described in this section.

#### A. Operating Range

The direction of power flow in the 3- $\Phi$  bB CSI system shown in **Fig. 1** is defined by the sign of the DC-link current  $i_{dc}$ . In fact, since the output voltage of the buck converter  $v_{qn}$  is unipolar, i.e. it is limited between  $0 \, \mathrm{V}$  and the supplying DC input voltage  $V_{\mathrm{dc}} > 0 \, \mathrm{V}$ , the average in a switching period of the input voltage of the 3- $\Phi$ inverter  $\bar{v}_{pn}$  must be positive to guarantee the controllability of  $i_{dc}$ , i.e. the stability of the system. However, still both directions of power flow are possible in the 3- $\Phi$  inverter, as only the sign of  $i_{dc}$  (and not the one of  $\bar{v}_{pn}$ , as for a conventional system [32]) must be inverted for feeding power back to the supplying DC input voltage source. Nevertheless, when  $\bar{v}_{pn}$  approaches 0 V, i.e. when the peak value  $\hat{v}_{out}$ of the sinusoidal output voltages or the load power factor  $\cos(\phi)$ of the supplied load are reduced [32], the controllability of  $i_{dc}$ , as well as the possibility to invert it, are limited. For this reason, the selected 3- $\Phi$  bB CSI system is particularly suited for VSDs supplying synchronous machines operated with high power factors or passive loads, e.g. pumps and fans [33], and, in the case of grid connected power electronic applications, for power factor correction (PFC) rectifiers and inverters, e.g. future bidirectional EV battery chargers, and PV inverters, i.e. for systems typically operating with  $\cos(\phi) \approx \pm 1.$

Irrespectively of this limitation, the DC/DC buck-type input stage based  $3-\Phi$  bB CSI system (see **Fig. 1**) is preferred to the back-to-back AC/AC system comprising two DC-side connected  $3-\Phi$  inverters [32] to better suite the requirements of voltage DC-link systems and distributed voltage DC-link architectures, becoming more and more prominent in VSDs [34].

# B. Input-Output Voltage Gain

The two main control variables of the 3- $\!\Phi$  bB CSI system are the duty-cycle of the buck converter

$$\bar{s}_{\mathrm{Tdc,h}} = \frac{\bar{v}_{\mathrm{qn}}}{V_{\mathrm{dc}}} = \frac{\bar{v}_{\mathrm{pn}}}{V_{\mathrm{dc}}},\tag{1}$$

where  $\bar{v}_{\rm qn}$  indicates the average in a switching period of  $v_{\rm qn}$ , and the modulation index of the 3- $\Phi$  inverter

$$m_{\text{dc/ac}} = \frac{\hat{i}_{\text{out}}}{I_{\text{dc}}} = \frac{\bar{v}_{\text{pn}}}{\hat{v}_{\text{out,ll}}} \frac{2}{\sqrt{3}},$$

(2)

if constant  $i_{\rm dc}=I_{\rm dc}$  and  $\cos(\phi)=+1$  are assumed. In (2),  $\hat{i}_{\rm out}$  and  $\hat{v}_{\rm out,ll}$  correspond to the peak values of the sinusoidal load phase currents  $i_{\rm out}$  and sinusoidal line-to-line output voltages  $v_{\rm out,ll}$  generated by the 3- $\Phi$  inverter, respectively. Combining (1) and (2), the voltage gain  $g_{\rm v}$  of the 3- $\Phi$  bB CSI system can be calculated as

$$g_{\rm v} = \frac{\hat{v}_{\rm out,ll}}{V_{\rm dc}} = \frac{\bar{s}_{\rm Tdc,h}}{m_{\rm dc/ac}} \frac{2}{\sqrt{3}}.$$

(3)

Since  $0 \le \bar{s}_{Tdc,h} \le 1$  and  $0 \le m_{dc/ac} \le 1$ ,  $g_v$  can assume any positive value, i.e. the bB capability of the system is confirmed.

Although different combinations of  $\bar{s}_{\mathrm{Tdc,h}}$  and  $m_{\mathrm{dc/ac}}$  result in the same  $g_{\mathrm{v}}$ ,  $\bar{s}_{\mathrm{Tdc,h}}=1$  eliminates the switching losses in the buck converter (since  $\mathrm{T}_{\mathrm{dc,h}}$  is permanently on), while  $m_{\mathrm{dc/ac}}=1$  minimizes the losses of the overall system for a given operating point [35]. Accordingly, these are the preferred values of  $\bar{s}_{\mathrm{Tdc,h}}$  and  $m_{\mathrm{dc/ac}}$  for a given  $g_{\mathrm{v}}$ ; hence, two operating modes, namely the Buck-Mode ( $0 \leq \bar{s}_{\mathrm{Tdc,h}} < 1$ ,  $m_{\mathrm{dc/ac}}=1$ ) and the Boost-Mode ( $\bar{s}_{\mathrm{Tdc,h}}=1$ ,  $0 \leq m_{\mathrm{dc/ac}}<1$ ), can be defined [28]. From (3), the boundary between the Buck-Mode and the Boost-Mode can be calculated as

$$V_{\rm dc} = \frac{\sqrt{3}}{2} \, \hat{v}_{\rm out,ll}.\tag{4}$$

In particular, for  $V_{\rm dc} > \sqrt{3}/2\,\hat{v}_{\rm out,ll}$ , the system is operated in the *Buck-Mode*, whereas, when  $V_{\rm dc} < \sqrt{3}/2\,\hat{v}_{\rm out,ll}$ , the buck converter can no longer control  $i_{\rm dc}$ ; consequently, the *Boost-Mode* is entered.

#### C. Simplified Operating Principle

The 3- $\Phi$  bB CSI system shown in **Fig. 1** is simplified to the circuit shown in Fig. 2 (cf. Fig. 13 in [32]) to explain its operation in the Buck-Mode and with power flowing from the supplying DC input voltage source to the supplied AC output load. For this purpose, the buck converter and  $L_{\rm dc}$  are replaced by a current source  $i_{\rm dc} > 0$ , whereas the  $3-\Phi$  inverter is represented by two three-position switches  $T_h$  and  $T_l$ . The two output terminals tapped by  $T_h$  and  $T_l$  define one state of the 3- $\Phi$  inverter out of overall  $3^2 = 9$  possibilities; e.g., in Fig. 2, a transition from state [ab] to [ac] is illustrated. The three shoot-through states [aa], [bb] and [cc] are denominated zero states in contrast to the remaining six states denominated active states. In the zero states, the 3- $\Phi$  inverter short circuits the DC-link terminals p and n whereas, in the active states, it connects the load between them. Consequently, depending on the selected state,  $v_{\rm pn}$  varies between  $0\,\mathrm{V}$  (zero states) and the six  $v_{\mathrm{out,ll}}$  values, i.e.  $\pm v_{\mathrm{ab}},\,\pm v_{\mathrm{bc}}$  and  $\pm v_{\mathrm{ca}}$ (active states), while the switching stage output currents  $i_{a,sw}$ ,  $i_{b,sw}$ and  $i_{\rm c,sw}$  can either assume the value of 0 A (zero states) or of  $\pm i_{\rm dc}$ (active states). Hence, by appropriately switching Th and Tl, and output filtering (through  $C_0$ ),  $i_{dc}$  can be modulated and transformed into the sinusoidal load phase currents  $i_a$ ,  $i_b$  and  $i_c$ .

#### III. MODULATION SCHEMES

Two different modulation schemes, namely conventional *Pulse-Width Modulation* (3/3-PWM) and *Two-Third Pulse-Width Modulation* (2/3-PWM) [28]–[31] can be applied to the 3- $\Phi$  bB CSI system when operated in the *Buck-Mode*. Both approaches are described in this section with the support of idealized waveforms of the 3- $\Phi$  inverter, relative to its nominal operating point (see **Table I**).

# A. Conventional Pulse-Width Modulation (3/3-PWM)

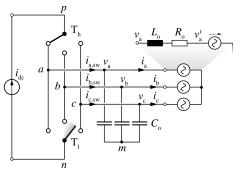

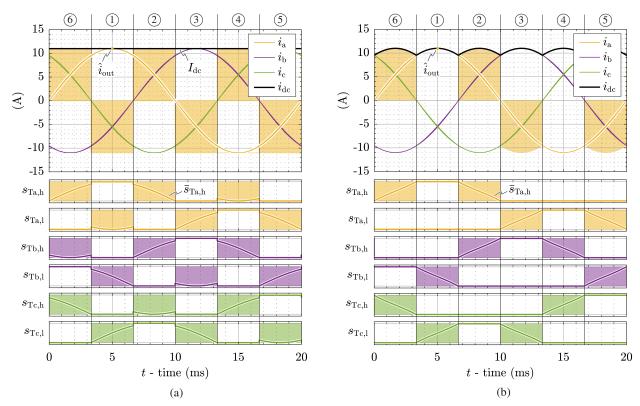

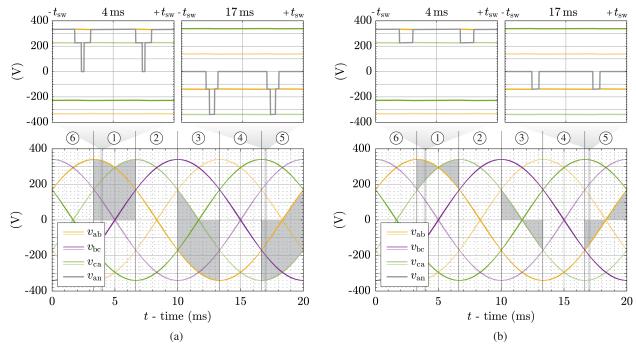

In the *Buck-Mode* (see **Section II-C**), the buck converter controls  $i_{\rm dc}$ , while the 3- $\Phi$  inverter is responsible for generating  $i_{\rm a}$ ,  $i_{\rm b}$  and  $i_{\rm c}$ . In case 3/3-PWM is applied,  $i_{\rm dc}$  is controlled to a constant value  $I_{\rm dc}$ . The most significant waveforms of the 3- $\Phi$  inverter in these conditions are summarized in **Fig. 3(a)**, **4(a)** and **5(a)**, where the encircled numbers

**Fig. 2:** Simplified representation of the 3- $\Phi$  bB CSI system shown **Fig. 1**. The two *three-position* switches  $T_h$  and  $T_l$ , modulating the DC-link current  $i_{dc}>0$  by alternately connecting the output terminals a,b and c to the DC-link terminals p and p, model the operation of the 3- $\Phi$  inverter.

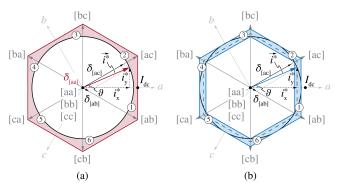

define the six symmetric  $\pi/3$ -wide sectors of an AC output period. In each interval of **Fig. 3(a)**, three of the six 2G MB GaN e-FETs forming the 3- $\Phi$  inverter are operated with PWM, i.e. are switched with switching frequency  $f_{\rm sw}$ . For example in sector (1), characterized by  $i_a > |i_b|$  and  $i_a > |i_c|$ ,  $T_{\rm a,h}$  is permanently on, while  $T_{\rm b,h}$  and  $T_{\rm c,h}$  are permanently off, and all three low-side switches  $T_{\rm i,l}$  are alternately switched within a switching period. In other words, the states [aa], [ab] and [ac] are alternately applied since, as visible in the space vector diagram of **Fig. 6(a)**, these are (in this sector) the closest neighbors of the vector of the reference sinusoidal load phase current  $\vec{i}$ , having  $|\vec{i}| = m_{\rm dc/ac} I_{\rm dc} = \hat{i}_{\rm out}$ . Hence,  $\vec{i}$  can be expressed as

$$\frac{\vec{i^*}}{I_{dc}} = \delta_{[aa]} \cdot [aa] + \delta_{[ab]} \cdot [ab] + \delta_{[ac]} \cdot [ac], \tag{5}$$

where  $\delta_{[xy]}$  indicates the duty-cycle of the state [xy]. Intuitively, all other  $\delta_{[xy]}=0$ .

In **Fig. 3**, the gate control signal  $s_{\text{Ti,j}}$  of each 2G MB GaN e-FET  $T_{\text{i,j}}$  and its average within one switching period  $\bar{s}_{\text{Ti,j}}$  are additionally shown. The conversion from  $\delta_{[xy]}$  to  $\bar{s}_{\text{Ti,j}}$  is immediately deduced from **Fig. 2** and can be expressed as

$$\bar{s}_{\text{Ti,h}} = \sum_{y = a, b, c} \delta_{[iy]}, \quad \bar{s}_{\text{Ti,l}} = \sum_{x = a, b, c} \delta_{[xi]} \quad (i = a, b, c).$$

(6)

Furthermore, from **Fig. 6(a)**, the duty-cycles of the *active states*  $\delta_{[ab]}$  and  $\delta_{[ac]}$  can be derived from the projections of  $\vec{i}^*$  according to

$$\frac{|\vec{i^*}|}{I_{\rm dc}} \begin{bmatrix} \cos \vartheta \\ \sin \vartheta \end{bmatrix} = \begin{bmatrix} 1 & 1 \\ \frac{1}{\sqrt{3}} & -\frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} \delta_{\rm [ac]} \\ \delta_{\rm [ab]} \end{bmatrix} \quad (-\pi/6 < \vartheta < \pi/6), \quad (7)$$

where  $\vartheta$  indicates the instantaneous phase angle of  $\vec{i}$ . The remaining fraction of the switching period is accounted for the *zero state*, whose duty-cycle  $\delta_{[aa]}$  is calculated as

$$\delta_{\text{[aa]}} = 1 - (\delta_{\text{[ac]}} + \delta_{\text{[ab]}}) = 1 - m_{\text{dc/ac}} \cos \vartheta \ge 1 - \cos \vartheta \ge 0.$$

(8)

It should be noticed in (8), that even if  $|\vec{i^*}| = I_{dc}$  as given for the *Buck-Mode* and applying 3/3-PWM,  $\delta_{[aa]} > 0$  results (except for the point in time in the middle of ①, i.e. for  $\vartheta = 0$ , where  $\delta_{[aa]} = 0$ ). Hence, a free-wheeling interval, i.e. an interval during which  $I_{dc}$  bypasses the load flowing through  $T_{a,h}$  and  $T_{a,l}$ , is present during every switching period forming ①. Since (7) and (8) can be extended to the other five sectors (from ② to ⑥) based on symmetry considerations, it can be concluded that *zero states* are always necessary when 3/3-PWM is applied, i.e. the *zero state* and the two *active states* are occurring in each switching period.

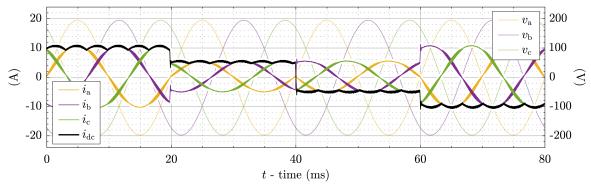

Fig. 3: DC-link current  $i_{dc}$ , sinusoidal load phase currents  $i_a$ ,  $i_b$  and  $i_c$  with peak value  $\hat{i}_{out}$  and gate control signals  $s_{\text{Ti},j}$  within one AC output period, in case (a) 3/3-PWM is applied ( $i_{dc} = I_{dc}$ ) and (b) 2/3-PWM is applied ( $i_{dc} = \max\{|i_a|, |i_b|, |i_c|\}$ ). The waveforms are given for the operating point specified in **Table I**. The encircled numbers, also indicated in **Fig. 4**, 5 and 6, define the six symmetric  $\pi$ /3-wide intervals of an AC output period. The yellow area in the graphs of  $i_{out}$  indicates the switching stage output current of phase a, i.e.  $i_{\text{sw,a}}$ . The colored lines in the graphs of  $s_{\text{Ti},j}$  correspond to their average  $\bar{s}_{\text{Ti},j}$  in a switching period. Further details are shown in **Fig. 4** and 5.

Fig. 4: Sinusoidal line-to-line output voltages  $\pm v_{ab}$ ,  $\pm v_{bc}$  and  $\pm v_{ca}$ , and input voltage of the 3- $\Phi$  inverter  $v_{pn}$  within one AC output period, in case (a) 3/3-PWM is applied and (b) 2/3-PWM is applied. The waveforms are given for the operating point specified in Table I. The red lines correspond to the average input voltage of the 3- $\Phi$  inverter  $\bar{v}_{pn}$  in a switching period. Further details are shown in Fig. 3 and 5.

## B. Two-Third Pulse-Width Modulation (2/3-PWM) [28]-[30]

According to **Section III-A**, a *zero state* free modulation should be preferred to maximize the efficiency of the  $3-\Phi$  bB CSI system. In fact, the transitions into (and out of) the *zero states* cause additional switching losses and, during the *zero states*, conduction losses occur even though no power is transferred to the load. Additionally, *zero states* are responsible for generating the highest common-mode voltage [36].

Hence, rewriting (8) for  $\delta_{[aa]} = 0$ ,

$$i_{\rm dc} = \hat{i}_{\rm out} \cos \vartheta = i_{\rm a} \qquad (-\pi/6 < \vartheta < \pi/6)$$

(9)

is obtained. For symmetry, (9) can be generalized to

$$i_{dc} = \max\{|i_a|, |i_b|, |i_c|\},$$

(10)

which is valid for the entire AC output period, neglecting the currents flowing in  $C_0$ . In other words, if the buck converter controls and shapes  $i_{\rm dc}$  to be equal to the instantaneous largest load phase current

Fig. 5: Sinusoidal line-to-line output voltages  $\pm v_{ab}$ ,  $\pm v_{bc}$  and  $\pm v_{ca}$ , and voltage  $v_{an}$ , within one AC output period, in case (a) 3/3-PWM is applied and (b) 2/3-PWM is applied. The waveforms are given for the operating point specified in **Table I**. The graphs in the upper part offer a zoomed view of  $v_{an}$  during a switching period. Further details are shown in **Fig. 3** and **4**.

Fig. 6: Space vector diagram highlighting the nine states of the 3- $\Phi$  inverter and the vector of the reference sinusoidal load phase current  $i^*$ , in case (a) 3/3-PWM is applied, i.e. the apothem of the hexagon is fixed to  $I_{\rm dc}$  and (b) 2/3-PWM is applied, i.e. the size of the hexagon is scaled according to  $i_{\rm dc}$ . The encircled numbers define the six symmetric  $\pi$ /3-wide intervals of an AC output period, as described in Fig. 3.

absolute value, e.g. to  $i_a$  during (1), the free-wheeling interval is avoided (since, e.g. again during (1),  $i_{dc} - i_a = 0$ ). Adjusting  $i_{dc}$  as described translates, in the space vector plane shown in **Fig. 6(b)**, into a continuous scaling of the dimensions of the hexagon over time such that its perimeter matches the trajectory defined by  $i^{\vec{*}}$ , resulting in  $\delta_{[ac]} + \delta_{[ab]} = 1$ , i.e.  $\delta_{[aa]} = 0$ . Following this approach, only the two *active states* [ab] and [ac] (instead of all three states) must be applied within one switching period; consequently,  $T_{a,l}$  is permanently off and only two  $(T_{b,l}$  and  $T_{c,l})$  instead of three 2G MB GaN e-FETs are alternately switched, as illustrated in **Fig. 3(b)**. Accordingly, this concept is named *Two-Third Pulse-Width Modulation* (2/3-PWM) and, as already speculated and further discussed in **Section IV-B**, it enables a significant reduction of switching losses.

As a consequence of (10),  $\bar{v}_{\rm pn}$  in **Fig. 4(b)** is not constant as in

Fig. 4(a) but still guarantees a constant power  $\bar{v}_{\rm pn}i_{\rm dc}$  at the input of the 3- $\Phi$  inverter. Moreover, since the zero states are avoided,  $v_{\rm pn}$  never assumes the value of 0 V.

In **Fig. 5** the voltage  $v_{\rm an}$  across  $T_{\rm a,l}$  is indicated for completeness. During ① in **Fig. 5(b)**, generated applying 2/3-PWM,  $v_{\rm an}$  varies between  $v_{\rm ab}$  and  $-v_{\rm ca}$ , while in **Fig. 5(a)**, where 3/3-PWM is considered, it also reaches 0 V. The same reasoning can be extended to ⑤, where the three states of interest are [ca], [cb] and [cc] (see **Fig. 6**), yielding to  $v_{\rm an}$  not assuming the value of  $-v_{\rm ca}$  in **Fig. 5(b)**. Repeating the calculations described in **Section II-B** with  $i_{\rm dc}=\hat{i}_{\rm out}\cos\vartheta$ , the range of applicability of 2/3-PWM can be determined as

$$V_{\rm dc} > \frac{\sqrt{3}}{2} \frac{1}{\cos(\vartheta)} \hat{v}_{\rm out,ll} \qquad (-\pi/6 < \vartheta < \pi/6). \tag{11}$$

Since  $\sqrt[3]{2} < \cos(\vartheta) \leq 1$ , (11) indicates that 2/3-PWM can be considered only if  $V_{\rm dc} > \hat{v}_{\rm out,II}$ , i.e. in a subset of the *Buck-Mode* operating region. However, when  $\sqrt[3]{2}\,\hat{v}_{\rm out,II} < V_{\rm dc} < \hat{v}_{\rm out,II}$ , i.e. in the rest of the *Buck-Mode* region, 2/3-PWM and 3/3-PWM can be alternated depending on  $\vartheta$ , as discussed more in detail in **Section V-B**. In practice, the range of applicability of 2/3-PWM should be defined in the design phase of the 3- $\Phi$  bB CSI system, opportunely selecting  $V_{\rm dc}$  as function of  $\hat{v}_{\rm out}$ .

## IV. ANALYSIS OF THE TWO-THIRD PULSE-WIDTH MODULATION

Following the basic analysis of 2/3-PWM provided in **Section III-B**, the enabled reduction of conduction and switching losses in the 3- $\Phi$  inverter are calculated in the following.

# A. Reduction of Conduction Losses

Since  $i_{dc}$  continuously flows through  $L_{dc}$  and two MB GaN e-FETs, the conduction losses occurring in the 3- $\Phi$  inverter are proportional to

the square of the root-mean-square (RMS) value of  $i_{dc}$ . Considering  $i_{dc}$  given by (10),

$$i_{\text{dc,RMS}} = \sqrt{\frac{1}{\pi/3} \int_{-\pi/6}^{+\pi/6} \hat{i}_{\text{out}}^2 \cos^2(\vartheta) \, d\vartheta} = 0.96 \, \hat{i}_{\text{out}}$$

(12)

results. Consequently, for a given operating point, the conduction losses reduce by 8% in case 2/3-PWM is applied. Similarly, the local average value of  $i_{\rm dc}$  given by (10) can be calculated for each sector of an AC output period, obtaining  $\langle i_{\rm dc} \rangle = ^3/\pi \ \hat{i}_{\rm out} = 0.95 \ \hat{i}_{\rm out}$ .

#### B. Reduction of Switching Losses

To analyze the occurring switching losses, the  $3-\Phi$  bB CSI system illustrated in **Fig. 1** is simplified to the circuit schematic shown in **Fig. 7**. This representation is valid during (1) but, according to the symmetry of the phases, similar diagrams can be derived for the rest of the AC output period.

Only the three low-side switches  $T_{i,l}$  are considered in **Fig. 7**, since (during ①) the switching state of the three high-side switches  $T_{i,h}$  is fixed, i.e.  $T_{a,h}$  is permanently on, while  $T_{b,h}$  and  $T_{c,h}$  are permanently off. It can be recognized that the three line-to-line output voltages  $v_{xy}$  are applied across the corresponding pairs of low-side switches  $T_{x,l}$  and  $T_{y,l}$ , and that one switch in turn conducts  $i_{dc}$ . Therefore, the series connection of  $T_{x,l}$  and  $T_{y,l}$  can be considered as a bridge-leg configuration supplied from  $v_{xy}$ , having the negative DC-link terminal n as switch node and  $i_{dc}$  as load current. Consequently, the switching transition between two states, e.g. from [ab] to [ac], is nothing else than the commutation of a bridge-leg, e.g. of the one formed by  $T_{b,l}$  and  $T_{c,l}$ , and supplied by  $v_{bc}$ .

Assuming  $i_{\rm dc} > 0$  and practically constant, on the one hand the sign of  $v_{\rm xy}$  determines whether a switching state change correspond to a zero voltage switching transition or a hard switching transition, while on the other hand the actual value of  $v_{\rm xy}$  determines the occurring switching losses. Moreover, the sequence in which the states of the 3- $\Phi$  inverter, i.e. the three closest neighbors of the vector of the reference sinusoidal load phase current  $\vec{i}^*$  (see **Section III**), are applied within one switching period ultimately defines which  $v_{\rm xy}$  are switched [31]; e.g.,  $v_{\rm ab}$  and  $v_{\rm bc}$  are involved in the state sequence [aa]-[ab]-[ac], whereas  $v_{\rm ab}$  is replaced by  $v_{\rm ca}$  in the state sequence [aa]-[ac]-[ab].

Accordingly, the switching losses occurring in the 3- $\Phi$  inverter can be approximated by calculating the average value of the switched  $v_{xy}$  over the considered  $\pi/3$ -wide interval of an AC output period,

Fig. 7: Simplified representation of the 3- $\Phi$  bB CSI system shown in Fig. 1 for the analysis of the switching losses in the 3- $\Phi$  inverter. Each pair of low-side switches forms a bridge-leg supplied from one of the sinusoidal line-to-line output voltages and having the DC-link current as load current.

i.e.  $\langle v_{\rm sw} \rangle$ , which is dependent on  $\phi$ , on  $\hat{v}_{\rm out}$  and on the selected state sequence [37], [38]. For simplicity, only hard switching losses are considered in this analysis, i.e. zero voltage switching losses are neglected.

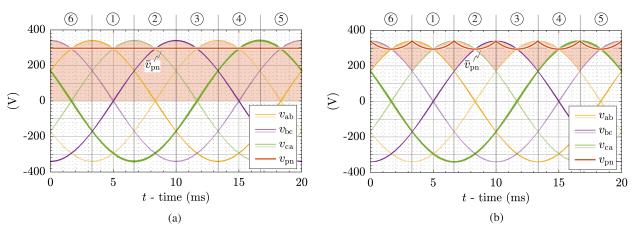

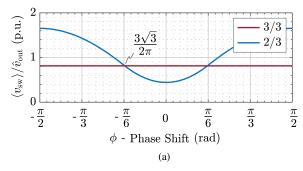

In case of 3/3-PWM, extending the procedure proposed in [38], it can be shown that the state sequence offering minimum switching losses [39] requires two hard switching transitions with an average voltage

$$\langle v_{\text{sw,3/3}} \rangle = \frac{3\sqrt{3}}{2\pi} \, \hat{v}_{\text{out}} \tag{13}$$

per switching period, independent of  $\phi$ . In case of 2/3-PWM, instead, only the two *active states* [ab] and [ac] are applied within one switching period, i.e. the switched voltage, during ①, is always  $v_{\rm bc}$ ; hence,  $\langle v_{\rm sw,2/3} \rangle$  (the counterpart of  $\langle v_{\rm sw,3/3} \rangle$  for 2/3-PWM) can be calculated as the average of  $|v_{\rm bc}|$  over the considered  $\pi$ /3-wide interval of an AC output period [29]–[31], obtaining

$$\frac{\langle v_{\text{sw,2/3}} \rangle}{\hat{v}_{\text{out}}} = \begin{cases}

\frac{3\sqrt{3}}{\pi} \left(2 - \sqrt{3} \cos(\phi)\right) & (-\pi/6 < \phi < +\pi/6) \\

\frac{3\sqrt{3}}{\pi} \sin(\phi) & (+\pi/6 < |\phi| < +\pi/2).

\end{cases} (14)$$

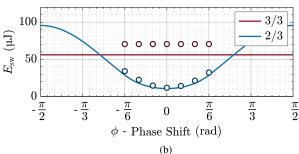

The mathematical expressions (13) and (14) are visualized in **Fig. 8(a)**. The ratio between  $\langle v_{\text{sw},2/3} \rangle$  and  $2 \langle v_{\text{sw},3/3} \rangle$  (where the factor 2 accounts for the fact that two hard switching transitions occur within one switching period in case of 3/3-PWM) is already an indicator of the reduction of switching losses enabled by 2/3-PWM; in particular

$$\frac{\langle v_{\text{sw,2/3}} \rangle}{2 \langle v_{\text{sw,3/3}} \rangle} = 2 - \sqrt{3} \cos(\phi) = 0.27 \tag{15}$$

is obtained for  $\cos(\phi) = +1$ .

More precisely, the hard switching losses  $P_{sw} = E_{sw} f_{sw}$  occurring

Fig. 8: (a) Normalized average (over the considered  $\pi/3$ -wide interval of an AC output period) line-to-line output voltages  $\langle v_{\rm sw} \rangle$  switched in the 3- $\Phi$  inverter, as function of the phase shift  $\phi$ . (b) Switching energy  $E_{\rm sw}$  dissipated in the 3- $\Phi$  inverter in one switching period, as function of  $\phi$  and of the selected modulation scheme. The lines indicate the results of the simplified analytical calculations while the dots are obtained from circuit simulations.

in the  $3-\Phi$  inverter can be calculated according to the conventional VI-overlap switching loss model. Considering only the dependency on the switched voltage given by (13) and (14), since the switched current is practically constant,  $E_{\rm sw}$  can be approximated with

$$E_{\text{sw},3/3} = 2 \left( k_1 \langle v_{\text{sw},3/3} \rangle + k_2 \langle v_{\text{sw},3/3} \rangle^2 \right)$$

(16)

and

$$E_{\text{sw},2/3} = k_1 \left\langle v_{\text{sw},2/3} \right\rangle + k_2 \left\langle v_{\text{sw},2/3} \right\rangle^2 \tag{17}$$

for the case of 3/3-PWM and 2/3-PWM, respectively. The values of  $k_1$  and  $k_2$  in (16) and (17) are determined by the considered operating point (see **Table I**) and by the switching performance of the power semiconductors employed for the realization of the 3- $\Phi$  inverter.  $k_1=60\,\mathrm{A}$  ns and  $k_2=720\,\mathrm{pF}$  [40] are selected as an example in **Fig. 8(b)**, where (16) and (17) are depicted for comparison. It can be observed that 2/3-PWM clearly outperforms 3/3-PWM, as already speculated, especially for low values of  $\phi$ , i.e. in approximately ohmic load conditions. This originates from the fact that 2/3-PWM requires only one hard switching transition per switching period and, in addition, that the switched voltage  $|v_{bc}|$  is the smallest among all  $|v_{xy}|$  for low values of  $\phi$  [31]. In particular

$$\frac{E_{\text{sw},2/3}}{E_{\text{sw},3/3}} = 0.19 \tag{18}$$

is calculated for  $\cos(\phi) = +1$ , i.e. in the typical operating conditions of VSDs supplying synchronous machines or passive loads, of PFC rectifiers and of inverters feeding renewable energy into the grid. The result of (18) is lower (and more accurate) than the one of (15) for the influence of the quadratic term present in (16) and (17).

Only for  $\pi/3 < |\phi| < \pi/2$ ,  $|v_{bc}|$  features a maximum; hence, all state sequences avoiding the transitions from [ab] to [ac] and vice versa result in lower switching losses. However, 2/3-PWM can nevertheless be applied and [aa] used only as a transitory state between [ac] and [ab], just to avoid the most lossy switching transition associated to the direct commutation from [ac] to [ab]. In this way, it is still possible to benefit from the reduction of conduction losses enabled by 2/3-PWM

To prove the correctness of the developed analytic procedure, the switching energy  $E_{\rm sw}$  is additionally calculated in a simulation environment. The same operating conditions (see **Table I**) and switching loss models (cf. (16) and (17)) are selected, but the exact switched voltage and current values are now considered. The so

obtained numerical results are indicated with dots in **Fig. 8(b)**, confirming the accuracy of the analytical results. The discrepancy between calculations and simulations is attributed to the averaging of  $v_{\rm xy}$  over the considered  $\pi/3$ -wide interval of an AC output period and to the neglection of the soft switching losses, as well as of the losses occurring in the switch not involved in the commutation of  $i_{\rm dc}$  [41]. A more detailed (but more complex) analytic derivation of  $E_{\rm sw}$ , offering a better matching with the numerical results, can be found in [31].

In summary, it should be pointed out that, in particular for  $\phi\approx 0$ , typical for VSDs employing synchronous machines and passive loads, and for PFC rectifiers and inverters, the reduction of switching losses in the 3- $\Phi$  inverter enabled by 2/3-PWM amounts up to 83 %.

#### V. CIRCUIT SIMULATION

The detailed operation of the 3- $\Phi$  bB CSI system is discussed in this section through the analysis of circuit simulations, focusing on 2/3-PWM and on the developed *Synergetic Control* scheme.

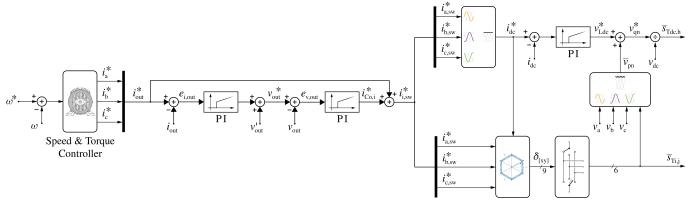

#### A. Synergetic Control

A key requirement for the correct operation of the 3- $\Phi$  bB CSI system, in particular when 2/3-PWM is applied, is a precise control and shaping of  $i_{\rm dc}$ ; for this purpose, the control structure shown in **Fig. 9** is proposed and described in the following.

The input of the controller, indicated on the left, is the reference speed of the driven electric machine  $\omega^*$ , assuming a VSD application. Comparing  $\omega^*$  with the measured speed  $\omega$ , a reference for the torque and hence for the sinusoidal load (motor) phase currents  $i_a^*$ ,  $i_b^*$  and  $i_c^*$  are generated. Since this analysis focuses only on the operation of the 3- $\Phi$  bB CSI system, the speed and torque controller (typically implemented in a rotating dq-coordinate frame) is not discussed further.

The central part of the control structure determines the reference switching stage output currents  $i_{\rm a,sw}^*$ ,  $i_{\rm b,sw}^*$  and  $i_{\rm c,sw}^*$  from  $i_{\rm a}^*$ ,  $i_{\rm b}^*$  and  $i_{\rm c}^*$  and compensates for the currents  $i_{\rm Co,a}$ ,  $i_{\rm Co,b}$  and  $i_{\rm Co,c}$  flowing through  $C_{\rm o}$ . As this part is identical for all the phases, the phase quantities  $i_{\rm a}^*$ ,  $i_{\rm b}^*$  and  $i_{\rm c}^*$  are unified in the generic reference sinusoidal load phase current  $i_{\rm out}^*$ . Comparing  $i_{\rm out}^*$  with the measured  $i_{\rm out}$ , i.e. with the measured  $i_{\rm a}$ ,  $i_{\rm b}$  and  $i_{\rm c}$ , the error on the sinusoidal load phase current  $e_{\rm i,out}$  is calculated. Through a proportional-integral (PI) controller,  $e_{\rm i,out}$  is transformed into the reference sinusoidal output voltage  $v_{\rm out}^*$  to be applied across  $C_{\rm o}$ . Eventually, an estimation of

Fig. 9: Structure of the *Synergetic Control* combining the regulation and shaping of  $i_{\rm dc}$  with the generation of sinusoidal load phase currents. The input of the controller (left) is the reference speed of the driven electric machine  $\omega^*$ , while the outputs (right) are the duty-cycle of the buck converter  $\bar{s}_{\rm Tdc,h}$  and the nine gate control signals (average in a switching period) of the 3- $\Phi$  inverter  $\bar{s}_{\rm Ti,j}$ . The illustrated control structure is applicable in the *Buck-Mode* (both for 2/3-PWM) and for 3/3-PWM) and can be extended to the *Boost-Mode* as described in [28].

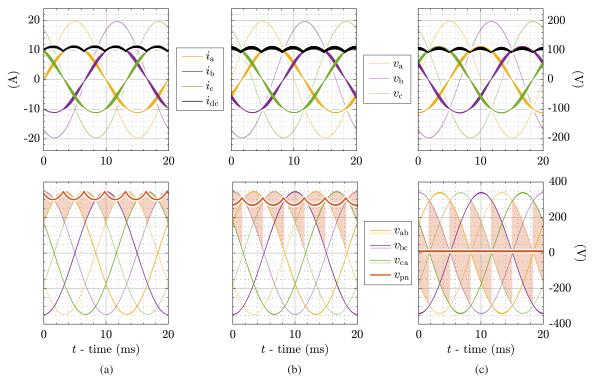

Fig. 10: DC-link current  $i_{dc}$ , sinusoidal load phase currents  $i_a$ ,  $i_b$  and  $i_c$ , sinusoidal output voltages  $v_a$ ,  $v_b$  and  $v_c$ , sinusoidal line-to-line output voltages  $\pm v_{ab}$ ,  $\pm v_{bc}$  and  $\pm v_{ca}$ , and input voltage of the 3- $\Phi$  inverter  $v_{pn}$  within one AC output period, in case 2/3-PWM is applied, for (a) phase shift of the sinusoidal load phase currents and sinusoidal output voltages  $\phi \approx 0$ , (b)  $\phi \approx \pi/6$  and (c)  $\phi \approx \pi/2$ . Independently of the value of the load power factor  $\cos(\phi)$ , a constant peak value  $\hat{i}_{out}$  of the sinusoidal load phase currents is maintained. The red lines in the graphs of  $v_{out,ll}$  correspond to the average input voltage of the 3- $\Phi$  inverter  $\bar{v}_{pn}$  within a switching period.

$v_{\rm out}$ , i.e.  $v_{\rm out}'$ , can be feed-forwarded to improve the performance of the current controller. In case of VSDs,  $v_{\rm out}'$  (see **Fig. 2**), i.e. the back-electromotive force of the electric machine, can be obtained multiplying  $\omega$  with the speed constant of the considered electric machine. Similarly as for the case of  $i_{\rm out}$ , comparing  $v_{\rm out}^*$  with the measured  $v_{\rm out}$ , the error on the sinusoidal output voltage  $e_{\rm v,out}$  is calculated. Again, through a PI controller,  $e_{\rm v,out}$  is transformed into the reference filter capacitor current  $i_{\rm Co,i}^*$ , (i = a, b, c). Summing  $i_{\rm out}^*$  with  $i_{\rm Co,i}^*$ , the reference switching stage output current  $i_{\rm i,sw}^*$  (i = a, b, c) is finally obtained.

Phase quantities are necessary in the right part of the block diagram; hence  $i_{i,\text{sw}}^*$  is transformed back into  $i_{a,\text{sw}}^*$ ,  $i_{b,\text{sw}}^*$  and  $i_{c,\text{sw}}^*$ . This part is divided in two sub-parts: one provides the duty-cycle of the buck converter  $\bar{s}_{\text{Tdc,h}}$ , while the other one determines the average (within one switching period) gate control signals of the 3- $\Phi$  inverter  $\bar{s}_{\text{Ti,j}}$ . In the upper part,  $i_{a,\text{sw}}^*$ ,  $i_{b,\text{sw}}^*$  and  $i_{c,\text{sw}}^*$  are first combined to generate the reference DC-link current  $i_{dc}^*$ , as defined in (10). Comparing  $i_{dc}^*$  with the measured  $i_{dc}$ , the reference voltage to be applied across  $L_{dc}$ , i.e.  $v_{Ldc}^*$ , is determined through the third PI controller. Summing  $v_{Ldc}^*$  with  $\bar{v}_{pn}$ , obtained from the lower part of the block diagram, the reference output voltage of the buck converter  $v_{qn}^*$  is obtained. Finally, dividing  $v_{qn}^*$  with  $v_{dc}$ , also  $\bar{s}_{\text{Tdc,h}}$  is determined.

In the lower part,  $i_{\rm a,sw}^*$ ,  $i_{\rm b,sw}^*$ ,  $i_{\rm c,sw}^*$  and  $i_{\rm dc}^*$  are first inserted in (7) to determine the nine duty-cycles  $\delta_{\rm [xy]}$ . For example, for  $\vartheta=0$  (during 1),  $\delta_{\rm [ac]}=\delta_{\rm [ab]}=0.5$  (and all other  $\delta_{\rm [xy]}=0$ ) results. Thus, the nine  $\delta_{\rm [xy]}$  are converted to the six  $\bar{s}_{\rm Ti,j}$ , as indicated in (6). In the example,  $\delta_{\rm [ac]}=\delta_{\rm [ab]}=0.5$  translates into  $\bar{s}_{\rm Ta,h}=1$ ,  $\bar{s}_{\rm Tb,l}=\bar{s}_{\rm Tc,l}=0.5$  and all other  $\bar{s}_{\rm Ti,j}=0$ . Finally, the six  $\bar{s}_{\rm Ti,j}$  are combined with the measured

$v_{\rm a},\,v_{\rm b}$  and  $v_{\rm c}$  to obtain

$$\bar{v}_{pn} = \sum_{i=a,b,c} (\bar{s}_{Ti,h} - \bar{s}_{Ti,l}) v_i,$$

(19)

required in the upper part of the control. In the example, (19) expands to  $\bar{v}_{\rm pn}=v_{\rm a}-0.5\,(v_{\rm b}+v_{\rm c})$ .

As clarified with this explanation, the control scheme shown in **Fig. 9** is considered as *Synergetic*, since the upper and lower parts mutually contribute to the correct operation of the 3- $\Phi$  bB CSI system, i.e. the buck converter shapes  $i_{\rm dc}$  in support of the generation of sinusoidal load phase currents, finally performed by the 3- $\Phi$  inverter. This control concept is applicable in the *Buck-Mode*, but can be easily extended to the *Boost-Mode* [28].

To conclude, it should be additionally noticed that, the same exact control structure can be considered for 3/3-PWM, except for (10). In case of 3/3-PWM, in fact,  $i_{\rm dc}^*$  is constant and  $i_{\rm dc}^* = I_{\rm dc}^* \geq i_{\rm i,sw}^*$  (i = a, b, c) is necessary. As shown in the next section, this allows a seamless transition between 3/3-PWM and 2/3-PWM and viceversa.

#### B. Simulation Results

The functioning of the *Synergetic Control* scheme described in **Section V-A** is verified in the following analyzing the results of closed-loop circuit simulations of the 3- $\Phi$  bB CSI system, in different operating conditions.

In particular, in the upper part of **Fig. 10(a)**, (b) and (c), the simulated waveforms of  $i_{\rm dc}$  and  $i_{\rm out}$  are shown together with the ones of  $v_{\rm out}$ , for  $\phi \approx 0$ ,  $\pi/6$  and  $\pi/2$ . Differently from the ideal case considered in **Fig. 3(b)**, a small discrepancy between  $i_{\rm out}$  and  $i_{\rm dc}$ , due to  $i_{\rm Co,i}$ , can be observed here. Although the same values of  $\hat{i}_{\rm out}$  (hence  $i_{\rm dc}$ ) and  $\hat{v}_{\rm out}$  are considered in these three plots, the different

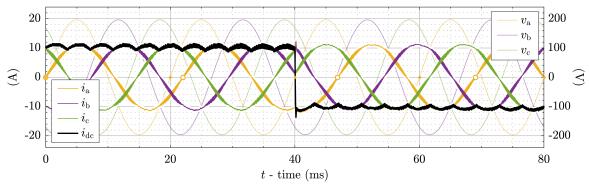

Fig. 11: DC-link current  $i_{\rm dc}$ , sinusoidal load phase currents  $i_{\rm a}$ ,  $i_{\rm b}$  and  $i_{\rm c}$ , sinusoidal output voltages  $v_{\rm a}$ ,  $v_{\rm b}$  and  $v_{\rm c}$  within four AC output periods, in case 2/3-PWM is applied, and for load power factor  $\cos(\phi)$  decreasing linearly from +1 to -1. Independently of the value of  $\cos(\phi)$ , a constant peak value  $\hat{i}_{\rm out}$  of the sinusoidal load phase currents is maintained. At time  $t=40\,{\rm ms}$ ,  $\cos(\phi)$  reaches 0 and subsequently changes sign, i.e. the direction of power flow is swapped and  $i_{\rm dc}$  must be inverted accordingly.

Fig. 12: DC-link current  $i_{dc}$ , sinusoidal load phase currents  $i_a$ ,  $i_b$  and  $i_c$ , sinusoidal output voltages  $v_a$ ,  $v_b$  and  $v_c$  within four AC output periods, in case 2/3-PWM is applied, for load power factor  $\cos(\phi) = +1$  for time  $t < 40 \, \mathrm{ms}$  and  $\cos(\phi) = -1$  for  $t > 40 \, \mathrm{ms}$ , and for different peak values  $\hat{i}_{out}$  of the sinusoidal load phase currents, i.e. for full and half rated output power  $P_{out}$ .

Fig. 13: DC-link current  $i_{dc}$ , sinusoidal load phase currents  $i_a$ ,  $i_b$  and  $i_c$ , sinusoidal output voltages  $v_a$ ,  $v_b$  and  $v_c$ , and supplying DC input voltage  $v_{dc}$  within four AC output periods, for load power factor  $\cos(\phi) = +1$ . By reducing  $v_{dc}$ , a transition from the *Buck-Mode* to the *Boost-Mode* occurs; additionally, both 3/3-PWM and 2/3-PWM are applied in the *Buck-Mode*.

values of  $\cos(\phi)$  result in different values of the output power  $P_{\text{out}}$ . Accordingly, the reduction of  $\bar{v}_{\text{pn}}$ , directly proportional to the one of  $P_{\text{out}}$ , is highlighted in the lower part of **Fig. 10(a)**, **(b)** and **(c)**. For completeness, the simulated waveforms of  $i_{\text{dc}}$ ,  $i_{\text{out}}$  and  $v_{\text{out}}$ , for  $-1 \leq \cos(\phi) \leq +1$ , are shown in **Fig. 11**. The smooth decrease of  $\cos(\phi)$  can be noticed observing how, e.g. the waveforms of  $i_a$  and  $v_a$ , are in phase at time t=0 s and in phase opposition at

$t=80\,\mathrm{ms}$ . To guarantee the controllability of  $i_\mathrm{dc}$ , i.e. to guarantee that  $\bar{v}_\mathrm{pn}$  is sufficiently positive when the direction of power flow is inverted (see **Section V-A**),  $\phi$  instantaneously varies from  $\pi/2-\pi/8$  to  $\pi/2+\pi/8$  at  $t=40\,\mathrm{ms}$ . The same waveforms are summarized in **Fig. 12**, for  $\cos(\phi)=\pm1$ , and for different values of  $\hat{i}_\mathrm{out}$ , to analyze the dynamic response of the *Synergetic Control* scheme. Finally, the two operating modes described in **Section II-B**, i.e. the *Buck-Mode*

and the *Boost-Mode*, and the two modulation schemes presented in **Section III**, i.e. 3/3-PWM and 2/3-PWM, are jointly shown in **Fig. 13**, for  $\cos(\phi)=+1$ . At t=0 s, the supplying DC input voltage  $v_{\rm dc}>\hat{v}_{\rm out,ll}$  allows both 3/3-PWM and 2/3-PWM in the *Buck-Mode*; hence, both modulations are independently applied in the first and second AC output periods, respectively. At  $t\approx 40\,{\rm ms},\,v_{\rm dc}<\hat{v}_{\rm out,ll}$ ; thus, although still in the *Buck-Mode*, 2/3-PWM can be used only in combination with 3/3-PWM, depending on the instantaneous value of  $v_{\rm out}$ . When  $v_{\rm dc}>\sqrt{3}/2\,\hat{v}_{\rm out,ll}$  after  $t\approx 60\,{\rm ms},\,$  the *Boost-Mode* is entered.

To summarize, in all the operating conditions of interest, i.e. for different values of  $\cos(\phi)$  and  $\hat{i}_{\text{out}}$ , the 3- $\Phi$  bB CSI system outputs the desired current and voltage waveforms and can be successfully operated with 2/3-PWM.

#### VI. ASPECTS OF PRACTICAL REALIZATION

In this section, after introducing research samples of 2G MB GaN e-FETs, a prediction of the efficiency and power density achievable by the  $3-\Phi$  bB CSI system is provided.

#### A. Dual-Gate Monolithic Bidirectional GaN e-FET

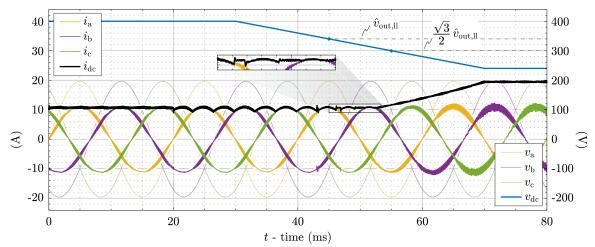

The power devices selected for the realization of the 3- $\Phi$  inverter are  $\pm 600~V~26~m\Omega~2G$  MB GaN e-FETs [23]. The main characteristics of this switch (currently only available as research sample) are compared in **Table II** with the ones of the best-in-the-market conventional GaN power transistor in the same voltage class, i.e. a  $650~V~25~m\Omega$  GaN e-FET [42].

To extend the operation of the conventional devices to *four-quadrants*, while maintaining the same overall on-state resistance  $R_{\rm ss,on}$ , two anti-series and two parallel devices must be connected as shown in **Fig. 14(a)**; this massively increases costs and, as highlighted by **Fig. 14(b)**, the required PCB area with respect to the solution based on the MB switch. Additionally, due to the increased parasitic output capacitance  $C_{\rm oss}$ , the Figure of Merit (FoM) [13] of the so obtained AC-switch becomes almost three times worse than the one of the MB device. To summarize, the considered 2G MB GaN e-FET is expected to allow a performance breakthrough of  $3-\Phi$  bB CSI systems, and

Fig. 14: Conventional realization of a switch with bidirectional voltage blocking capability and allowing controlled bidirectional current flow, i.e. a four-quadrant (AC) switch, with (a) two anti-series/two parallel 650 V 25 m $\Omega$  GaN e-FETs [42] compared with (b) a single  $\pm 600$  V 26 m $\Omega$  2G MB GaN e-FET [23] (geometric proportions of the packages are preserved). Both solutions (a) and (b) achieve approximately the same voltage blocking capability and overall on-state resistance, however (b) enables a massive saving in terms of package size. (c) Perspective view of the 20-pin package of the 2G MB GaN e-FET.

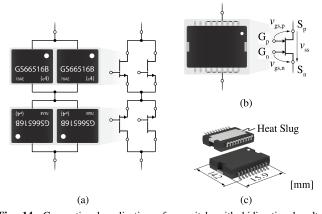

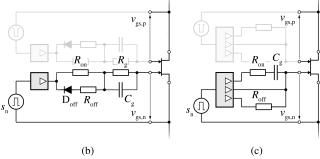

**Fig. 15:** (a) Equivalent circuit of the 2G MB GaN e-FET depending on the applied gate voltages  $v_{\rm gs,n}$  and  $v_{\rm gs,p}$ . (b) Conventional gate driver circuit adapted to GITs [44] based on a commercial IC and (c) gate driver circuit for GITs based on a specialized IC featuring a dedicated pin for the supplying of the constant gate current [45].

potentially of all circuit topologies requiring AC-switches as, e.g., AC/AC matrix converters.

In order to simultaneously control the bidirectional voltage blocking and current flow capabilities of the 2G MB GaN e-FET (see Fig. 15(a)), two gate voltages  $v_{\rm gs,n}$  and  $v_{\rm gs,p}$  must be separately applied to the 2G structure, as indicated in Fig. 14(b). Alternatively, if only one gate is controlled, only unidirectional current flow is possible. The gate voltages  $v_{\rm gs,n}$  and  $v_{\rm gs,p}$  must be isolated from each other because of the common-drain structure (split-source structure) which, based on a single drift layer, yields to lower values of  $R_{\rm ss,on}$  compared with the alternative common-source structure [20]. Additionally, the potential of the substrate must be left floating, while it is typically connected to the only source potential available in conventional GaN power transistors; different switching behaviors of the 2G MB GaN e-FET are observed when the substrate is connected to the one or the other source potentials, and are currently under investigation.

Since the device is of *Gate Injection Transistor* (GIT) type [43], constant currents (in the mA-range) must flow through the gates to modulate the conductivity of the two-dimensional electron gas (2DEG) channel during on-state. As visible in **Fig. 15(b)**, conventional gate driver circuits can be modified to include this feature [44]; alternatively, an *ad hoc* integrated circuit (IC) [45], i.e. featuring a dedicated pin for the supplying of the constant gate current, can be used. Adopting the latter approach, the compact gate driver design illustrated in **Fig. 15(c)**, requiring only three discrete components between the IC and the gate terminal, can be realized.

## B. Performance Estimation of the 3- $\Phi$ bB CSI System

The presented 2G MB GaN e-FETs, whose operation is verified in the **Appendix**, together with the simulation results discussed in **Section V-B**, demonstrate the feasibility of the  $3-\Phi$  bB CSI system operated with 2/3-PWM, and rise the interest in estimating its key

**TABLE II:** Main characteristics of the selected 2G MB GaN e-FET compared to the best-in-the-market conventional GaN power transistor in the same voltage class as a single device (1x) and in the two anti-series/two parallel configuration (4x).

| Power<br>Semiconductor |           | $V_{ m ss,MAX}$                                        | $I_{\rm ss,MAX}$ @ 25 °C | <b>R</b> <sub>ss,on</sub><br>@ 25 - 150 °C | $C_{\text{oss,Q}}$ $C_{\text{rss,Q}}$ @ $400\mathrm{V}$ | FoM = $(R_{ss,on}C_{oss,Q})^{-1}$<br>@ 25 °C - 400 V | Package<br>Size    |

|------------------------|-----------|--------------------------------------------------------|--------------------------|--------------------------------------------|---------------------------------------------------------|------------------------------------------------------|--------------------|

| Panasonic Co.          | EDLS06SMD | ±600 V                                                 | 92 A                     | $26 - 43 \mathrm{m}\Omega$                 | 190 pF 40 pF                                            | $202\mathrm{GHz}$                                    | $2.3\mathrm{cm}^2$ |

| GaN Systems Inc.       | GS66516   | $(1x) \mid 650 \text{ V}  (4x) \mid \pm 650 \text{ V}$ | 60 A<br>120 A            | $25$ - $65\mathrm{m}\Omega$                | 281 pF 8 pF<br>562 pF 16 pF                             | 142 GHz<br>71 GHz                                    |                    |

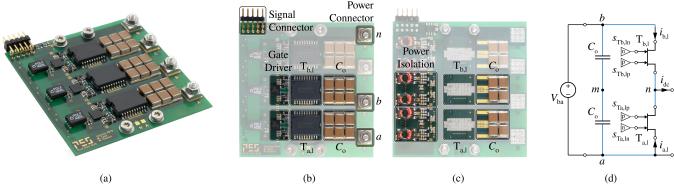

Fig. 16: (a) Perspective view, (b) top view and (c) mirrored bottom view of the test bench PCB comprising the three 2G MB GaN e-FETs  $T_{i,l}$  forming the low-side of the 3- $\Phi$  inverter, their respective gate drivers [45] with isolated signal transmission and isolated power supply, and a fraction of the overall output filter capacitors  $C_0$  [46], in addition to robust power and signal connectors. The PCB is squared, with each edge measuring 7.1 cm (2.8 in). (d) Bridge-leg formed by  $T_{a,l}$  and  $T_{b,l}$  on which the waveforms shown in Fig. 17 are measured. The blue line should help to recognize this bridge-leg structure in Fig. 1 and Fig. 7.

performance indexes, i.e. the achievable efficiency and power density, e.g. for the specifications given in **Table I**.

In particular, the design of the 3- $\Phi$  bB CSI system analyzed in the simulation environment (see Fig. 10) is estimated to achieve an efficiency  $\eta = 98.4\%$ , a volumetric power density  $\rho = 16 \,\mathrm{kW/dm^3}$  $(260 \,\mathrm{W/in^3})$  and a gravimetric power density  $\beta = 6.1 \,\mathrm{kW/kg}$  at a switching frequency  $f_{\text{sw}} = 140 \text{ kHz}$ , if a cooling system performance index CSPI =  $15 \,\mathrm{W/K} \,\mathrm{dm}^3$  is considered [47]. The power density figures are mainly limited by the volume (81 cm<sup>3</sup>) and weight (240 g) of  $L_{\rm dc} = 550 \, \mu \text{H}$  [48]. Accordingly, if the allowed peak-to-peak current ripple on  $i_{dc}$  is increased from 10 %, as selected for Fig. 10 (in order to clearly describe the operation of the 3- $\Phi$  inverter) to 30 %,  $L_{\rm dc}$  can be reduced to 185  $\mu H$ , resulting in a more compact and lighter inductor design, i.e. in a volume of  $50\,\mathrm{cm}^3$  (3.0 in<sup>3</sup>) and in a weight of  $115\,\mathrm{g}$ ; thus, for the same  $\eta=98.4\,\%$ , the power density figures increase to  $\rho = 18 \,\mathrm{kW/dm^3}$  (295 W/in<sup>3</sup>) and  $\beta = 7.7 \,\mathrm{kW/kg}$ . If 3/3-PWM is applied to the same design,  $\eta$  drops below 98 %; an even more significant reduction is observed for higher values of  $f_{sw}$ , when the switching losses dominate the loss breakdown.

In all designs, the buck converter is realized with the best-in-the-market conventional GaN power transistor listed in **Table II**, whose performance are reported in [40]; moreover the same switching frequency is considered for the buck converter and for the  $3-\Phi$  inverter [28].

# VII. CONCLUSION

A 3- $\Phi$  bB CSI system employing a variable DC-link current control strategy denominated *Two-Third Pulse-Width Modulation* (2/3-PWM) and 2G MB GaN e-FETs in its boost-type 3- $\Phi$  current DC-link inverter output stage is analyzed in this paper. Circuit simulations are performed to verify the operation of the 3- $\Phi$  bB CSI system, considering 2/3-PWM and the developed *Synergetic Control* concept. Moreover, analytic calculations quantify a reduction of conduction

losses of 8 % and a massive reduction of switching losses of 83 % (in case of unity load power factor), for 2/3-PWM in comparison with conventional 3/3-PWM. The operation of the 2G MB GaN e-FETs, which are suitable for any topology requiring AC-switches, is verified in a hardware prototype, where voltages up 400 V and currents up to 10 A are continuously switched. These novel devices, in combination with 2/3-PWM, have the potential to significantly enhance the performance of 3- $\Phi$  bB CSI systems, ultimately favoring their usage in place of 3- $\Phi$  Bb VSI systems; in particular, a 3- $\Phi$  bB CSI system, rated for an output power  $P_{\rm out}=3.3\,{\rm kW},$  is estimated to simultaneously achieve an efficiency  $\eta=98.4\,\%$  and a volumetric power density  $\rho=18\,{\rm kW/dm^3}$  (295 W/in³) at a switching frequency  $f_{\rm sw}=140\,{\rm kHz}$  when 2/3-PWM is applied.

#### APPENDIX

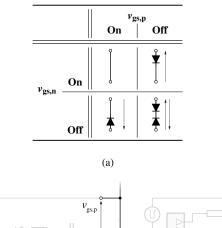

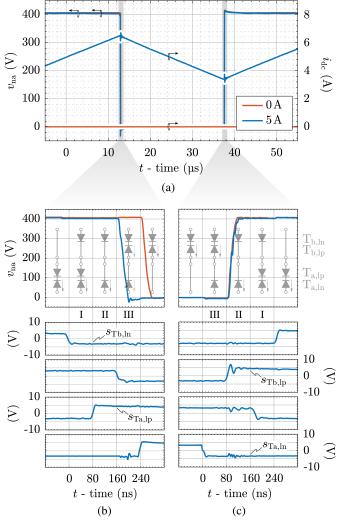

A test bench for the 2G MB GaN e-FETs introduced in Section VI-A is realized as illustrated in Fig. 16(a), (b) and (c). It implements the three switches forming one side (e.g. the low-side) of the  $3-\Phi$  inverter, since, as clarified in Section IV-B, this is sufficient, due to symmetry properties, to quantify the losses occurring in the entire  $3-\Phi$  inverter. In addition to the three T<sub>i,l</sub>, the realized PCB includes the associated gate drivers [45] (see Fig. 15(b)) with isolated signal transmission and isolated power supply, and a fraction of the overall  $C_0$  [46]. In particular, the bridge-leg formed by T<sub>a,l</sub> and T<sub>b,l</sub>, highlighted in Fig. 16 (d), is considered in the following. This bridge-leg is operated connecting a supplying DC input voltage source  $V_{\rm ba}$  between the terminals b and a, and a resistive-inductive load at the switch node n to sink the load current  $i_{dc}$ . Measured waveforms of the switch node voltage  $v_{\rm na}$  and of  $i_{\rm dc}$  are recorded and plotted in Fig. 17(a) for  $V_{\rm ba}=400\,{\rm V}$  and  $\langle i_{\rm dc}\rangle=5\,{\rm A}$  (blue) and  $0\,{\rm A}$  (red) in soft (zero voltage and zero current) switching and hard switching conditions. No significant overvoltage or oscillations are observed on  $v_{na}$ , while turn-off zero current and hard switching transitions are performed at

Fig. 17: (a) Measured waveforms of the switch node voltage  $v_{\rm na}$  and of the load current  $i_{dc}$  during continuous operation of the bridge-leg shown in Fig. 16 (d), for a supplying DC input voltage  $V_{\rm ba} = 400 \, \rm V$  and an average output current  $\langle i_{\rm dc} \rangle = 5\,{\rm A}$  (blue) and  $0\,{\rm A}$  (red). (b)-(c) Zoomed view of  $v_{\rm na}$  during a turn-on zero voltage switching transition (blue in (b)), a turn-on zero current switching transition (red in (b)), a turn-off zero current switching transition (red in (c)), and a turn-off hard switching transition (blue in (c)), associated gate signals  $s_{Ti,lp}$  and  $s_{Ti,ln}$  determined according to the current sign dependent multi-step commutation strategy, and equivalent circuit of the bridge-leg.

switching speeds dv/dt of about 15 V/ns (red and blue in **Fig. 17(c)**, respectively). Moreover, the voltage slope occurring for the turn-on zero voltage switching transition (blue in Fig. 17(b)) confirms the expected  $C_{\text{oss,Q}}$  value according to  $2 C_{\text{oss,Q}} = i_{\text{dc}}/dv/dt$  (cf. **Table II**). For 2G MB GaN e-FETs (and AC-switches in general), particular care must be taken during the switching transition, such that always a path for the switched current is provided while one of the two switches involved in the commutation blocks the bipolar switched voltage (see Fig. 15(a)). Hence, the four gate signals  $s_{Ti,lp}$  and s<sub>Ti,ln</sub> are generated according to a current sign dependent multistep commutation strategy [23], as illustrated in the lower part of **Fig. 17(b)** and (c) for the case of  $i_{dc} > 0$ . Additionally, the zoomed view of the measured  $v_{\rm na}$  is overlapped with the equivalent circuits of the bridge-leg (I, II and III) determined by  $s_{\text{Ti,lp}}$  and  $s_{\text{Ti,ln}}$  (see Fig. 15(a)). These plots highlight how, depending on the

type of switching transition, i.e. zero voltage, zero current or hard, the commutation takes place at different instants of the multi-step sequence.

#### REFERENCES

- [1] C. Vadstrup, X. Wang, and F. Blaabjerg, "LC Filter Design for Wide Band Gap Device Based Adjustable Speed Drives," in *Proc. of the Inter*national Power Electronics and Application Conference and Exposition (PEAC), Shanghai, China, 2014.

- [2] J. Guzinski, H. AbuRub, and P. Strankowski, Variable Speed AC Drives with Inverter Output Filters. John Wiley & Sons, Ltd., 2015.

- [3] F. Maislinger, H. Ertl, G. Stojcic, C. Lagler, and F. Holzner, "Design of a 100 kHz Wide Bandgap Inverter for Motor Applications with Active Damped Sine Wave Filter," *The Journal of Engineering*, vol. 2019, no. 17, pp. 3766–3771, 2019.

- [4] M. Antivachis, D. Bortis, A. Avila, and J. W. Kolar, "New Optimal Common-Mode Modulation for Three-Phase Inverters with DC-Link Referenced Output Filter," CPSS Transactions on Power Electronics and Applications, vol. 2, no. 4, pp. 331-340, 2017.

- [5] K. Shirabe, M. Swamy, J. K. Kang, M. Hisatsune, Y. Wu, D. Kebort, and J. Honea, "Advantages of High Frequency PWM in AC Motor Drive Applications," in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE USA)*, Raleigh, NC, USA, 2012.

- A. Stippich, C. H. Van Der Broeck, A. Sewergin, A. H. Wienhausen, M. Neubert, P. Schülting, S. Taraborrelli, H. Van Hoek, and R. W. De Doncker, "Key Components of Modular Propulsion Systems for Next Generation Electric Vehicles," CPSS Transactions on Power Electronics and Applications, vol. 2, no. 4, pp. 249-258, 2017.

- A. Sangwongwanich, G. Angenendt, S. Zurmuhlen, Y. Yang, D. Sera, D. U. Sauer, and F. Blaabjerg, "Enhancing PV Inverter Reliability With Battery System Control Strategy," CPSS Transactions on Power Electronics and Applications, vol. 3, no. 2, pp. 93–101, 2018.

- [8] M. Antivachis, D. Bortis, D. Menzi, and J. W. Kolar, "Comparative Evaluation of Y-Inverter against Three-Phase Two-Stage Buck-Boost DC-AC Converter Systems," in *Proc. of the International Power Electronics Conference (IPEC - ECCE Asia)*, Niigata, Japan, 2018.

- [9] K. D. T. Ngo, "Topology and Analysis in PWM Inversion, Rectification and Cycloconversion," Ph.D. dissertation, California Institute of Technology, Pasadena, CA, USA, 1984.

- R. Naik and N. Mohan, "A Novel Grid Interface for Photovoltaic, Wind-Electric, and Fuel-Cell Systems with a Controllable Power Factor of Operation," in Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC), Dallas, TX, USA, 1995.

- R. Naik, N. Mohan, M. Rogers, and A. Bulawka, "A Novel Grid Interface, Optimized for Utility-Scale Applications of Photovoltaic, Wind-Electric, and Fuel-Cell Systems," *IEEE Transactions on Power Delivery*, vol. 10, no. 4, pp. 1920–1926, 1995.

- [12] K. P. Phillips, "Current-Source Converter for AC Motor Drives," IEEE

- Transactions on Industry Applications, vol. 8, no. 6, pp. 679–683, 1972.

[13] M. Guacci, D. Bortis, and J. W. Kolar, "High-Efficiency Weight-Optimized Fault-Tolerant Modular Multi-Cell Three-Phase GaN Inverter for Next Generation Aerospace Applications," in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE USA)*, Portland, OR, ŬSA, 2018.

- H. Dai, R. A. Torres, T. M. Jahns, and B. Sarlioglu, "Characterization and Implementation of Hybrid Reverse-Voltage-Blocking and Bidirectional Switches using WBG Devices in Emerging Motor Drive Applications, in Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 2018.

- [15] R. A. Torres, H. Dai, W. Lee, T. M. Jahns, and B. Sarlioglu, "Current-Source Inverters for Integrated Motor Drives Using Wide-Bandgap Power Switches," in *Proc. of the IEEE Transportation Electrification* Conference and Expo (ITEC), Long Beach, CA, USA, 2018.

- T. Friedli, S. D. Round, D. Hassler, and J. W. Kolar, "Design and Performance of a 200 kHz All-SiC JFET Current DC-Link Back-to-Back Converter," *IEEE Transactions on Industry Applications*, vol. 45, no. 5, pp. 1868–1878, 2009.

- [17] F. Heinke and R. Sittig, "The Monolithic Bidirectional Switch (MBS)," in Proc. of the 12th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Toulouse, France, 2000.

- T. Morita, M. Yanagihara, H. Ishida, M. Hikita, K. Kaibara, H. Matsuo, Y. Uemoto, T. Ueda, T. Tanaka, and D. Ueda, "650 V $3.1\,\mathrm{m}\Omega\,\mathrm{cm}^2$  GaN-Based Monolithic Bidirectional Switch Using Normally-Off Gate Injection Transistor," in *Proc. of the IEEE International Electron Devices Meeting (IEDM)*, Washington, DC, USA, 2007.

- J. Waldron and T. P. Chow, "Physics-Based Analytical Model for High-Voltage Bidirectional GaN Transistors Using Lateral GaN Power HEMT," in *Proc. of the 25th International Symposium on Power* Semiconductor Devices and IC's (ISPSD), Kanazawa, Japan, 2013.

- [20] D. Bergogne, O. Ladhari, L. Sterna, C. Gillot, R. Escoffier, and W. Vandendaele, "The Single Reference Bi-Directional GaN HEMT AC Switch," in Proc. of the 17th European Conference on Power Electronics and Applications (EPE - ECCE Europe), Geneva, Switzerland, 2015.

- [21] C. Kuring, O. Hilt, J. Böcker, M. Wolf, S. Dieckerhoff, and J. Würfl, "Novel Monolithically Integrated Bidirectional GaN HEMT," in *Proc.* of the IEEE Energy Conversion Congress and Exposition (ECCE USA), Portland, OR, USA, 2018.

- [22] S. Nagai, Y. Yamada, M. Hiraiwa, H. Ueno, S. Choe, Y. Kawai, O. Tabata, G. Yamada, N. Negoro, and M. Ishida, "A Compact GaN Bi-Directional Switching Diode with a GaN Bi-Directional Power Switch and an Isolated Gate Driver," in *Proc. of the 28th International Symposium on Power Semiconductor Devices and ICs (ISPSD)*, Prague, Czech Republic, 2016.

- [23] H. Uemeda, Y. Yamada, K. Asanuma, F. Kusama, Y. Kinoshita, H. Ueno, H. Ishida, T. Hatsuda, and T. Ueda, "High Power 3-Phase to 3-Phase Matrix Converter Using Dual-Gate GaN Bidirectional Switches," in Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 2018.

- [24] J. Azurza Anderson, G. Deboy, and J. W. Kolar, "Relating the Figure of Merit of Power MOSFETs to the Maximally Achievable Efficiency of Converters," to be published, 2019.

- [25] B. Sahan, S. V. Araujo, C. Nöding, and P. Zacharias, "Comparative Evaluation of Three-Phase Current Source Inverters for Grid Interfacing of Distributed and Renewable Energy Systems," *IEEE Transactions on Power Electronics*, vol. 26, no. 8, pp. 2304–2318, 2011.

- [26] G. J. Su and P. Ning, "Loss Modeling and Comparison of VSI and RB-IGBT Based CSI in Traction Drive Applications," in *Proc. of the IEEE Transportation Electrification Conference and Expo (ITEC)*, Detroit, MI, USA, 2013.

- [27] J. W. Kolar and S. D. Round, "Analytical Calculation of the RMS Current Stress on the DC-Link Capacitor of Voltage-PWM Converter Systems," *IEE Proceedings - Electric Power Applications*, vol. 153, no. 4, pp. 535–542, 2006.

- [28] M. Baumann and J. W. Kolar, "A Novel Control Concept for Reliable Operation of a Three-Phase Three-Switch Buck-Type Unity Power Factor Rectifier with Integrated Boost Output Stage Under Heavily Unbalanced Mains Condition," *IEEE Transactions on Industrial Elec*tronics, vol. 52, no. 2, pp. 399–409, 2005.

- [29] Q. Lei, B. Wang, and F. Zheng Peng, "Unified Space Vector PWM Control for Current Source Inverter," in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE USA)*, Raleigh, NC, USA, 2012

- [30] Q. Lei and F. Zheng Peng, "Space Vector Pulsewidth Amplitude Modulation for a Buck-Boost Voltage/Current Source Inverter," *IEEE Transactions on Power Electronics*, vol. 29, no. 1, pp. 266–274, 2014.

- [31] M. Guacci, M. Tatic, D. Bortis, Y. Kinoshita, I. Hidetoshi, and J. W. Kolar, "Novel Three-Phase Two-Third-Modulated Buck-Boost Current Source Inverter System Employing Dual-Gate Monolithic Bidirectional GaN e-FETs," in Proc. of the 7th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Xi'an, China, 2019.

- [32] J. W. Kolar, T. Friedli, J. Rodriguez, and P. Wheeler, "Review of Three-Phase PWM AC-AC Converter Topologies," *IEEE Transactions* on *Industrial Electronics*, vol. 58, no. 11, pp. 4988–5006, 2011.

- [33] T. M. Jahns and H. Dai, "The Past, Present, and Future of Power Electronics Integration Technology in Motor Drives," CPSS Transactions on Power Electronics and Applications, vol. 2, no. 3, pp. 197–216, 2017.

- [34] D. Meike and I. Rankis, "New Type of Power Converter for Common-Ground DC Bus Sharing to Increase the Energy Efficiency in Drive Systems," in Proc. of the IEEE International Energy Conference and Exhibition (ENERGYCON), Florence, Italy, 2012.

- [35] J. R. Espinoza and G. Joos, "A Current-Source-Inverter-Fed Induction Motor Drive System with Reduced Losses," *IEEE Transactions on Industry Applications*, vol. 34, no. 4, pp. 796–805, 1998.

- [36] N. Zhu, B. Wu, D. Xu, N. R. Zargari, and M. Kazerani, "Common-Mode Voltage Reduction Methods for Medium-Voltage Current Source Inverter-Fed Drives," in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE USA)*, Phoenix, AZ, USA, 2011.

- [37] M. H. Bierhoff and F. W. Fuchs, "Semiconductor Losses in Voltage Source and Current Source IGBT Converters Based on Analytical Derivation," in *Proc. of the 35th IEEE Annual Power Electronics Specialists Conference (PESC)*, Aachen, Germany, 2004.

- [38] T. Halkosaari and H. Tuusa, "Optimal Vector Modulation of a PWM Current Source Converter According to Minimal Switching Losses," in Proc. of the 31st IEEE Annual Power Electronics Specialists Conference (PESC), Galway, Ireland, 2000.

- [39] L. Giuntini, "Adaptive Switching Sequence Selection in Space Vector Modulation of Buck-Type PWM Rectifiers," in Proc. of the International

- Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe), Nuremberg, Germany, 2019.

- [40] E. A. Jones, F. Wang, D. Costinett, Z. Zhang, B. Guo, B. Liu, and R. Ren, "Characterization of an Enhancement-Mode 650 V GaN HFET," in Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE USA), Montreal, QC, Canada, 2015.

- [41] A. Stupar, T. Friedli, J. Miniböck, M. Schweizer, and J. W. Kolar, "Towards a 99% Efficient Three-Phase Buck-Type PFC Rectifier for 400 V DC Distribution Systems," in Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 2011

- [42] GS66516B, GaN Systems Inc., Aug. 2018, Datasheet.

- [43] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagi, T. Ueda, T. Tanaka, and D. Ueda, "Gate Injection Transistor (GIT) A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation," *IEEE Transactions on Electron Devices*, vol. 54, no. 12, pp. 3393–3399, 2007.

- [44] D. Bortis, D. Neumayr, and J. W. Kolar, "ηρ-Pareto Optimization and Comparative Evaluation of Inverter Concepts Considered for the GOOGLE Little Box Challenge," in Proc. of the 17th IEEE Workshop on Control and Modeling for Power Electronics (COMPEL), Trondheim, Norway, 2016.

- [45] AN34092B, Panasonic Co., Jan. 2017, Datasheet.

- [46] C5750X6S2W225K250KA, TDK Co., Jan. 2016, Datasheet.

- [47] U. Drofenik, G. Laimer, and J. W. Kolar, "Theoretical Converter Power Density Limits for Forced Convection Cooling," in *Proc. of the Inter*national Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe), Nuremberg, Germany, 2005.

- [48] P. Papamanolis, F. Krismer, and J. W. Kolar, "Minimum Loss Operation of High-Frequency Inductors," in *Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC)*, San Antonio, TX, USA, 2018.

Mattia Guacci (STM'16) received the B.Sc. degree (summa cum laude) and the M.Sc. degree (summa cum laude) in Electronic Engineering from the University of Udine, Italy in July 2013 and in October 2015, respectively. In 2014 he was with Metasystems SpA in Reggio nell'Emilia, Italy working on on-board battery chargers for electric vehicles. In November 2015 he joined the Power Electronic Systems (PES) Laboratory of the Swiss Federal Institute of Technology (ETH) Zurich, Switzerland as a scientific assistant investigating compact, high-efficiency

DC/AC power converters based on wide band-gap power semiconductors. In September 2016 he started his Ph.D. at PES focusing on advanced power electronics concepts for future aircraft and electric vehicle applications. Mattia Guacci has authored 12 scientific papers in refereed journals and conference proceedings and has filed 6 patents. He has received 1 IEEE Prize Paper Award.

Daifei Zhang received the B.Sc. degree in Electrical Engineering and Automation from Huazhong University of Science and Technology (HUST) in 2017, and the M.Sc. degree in Electrical Engineering and Information Technology from ETH Zurich (with distinction) in 2019. In 2017, he was with the Institute for Power Generation and Storage Systems in RWTH Aachen, Germany, as an exchange student. In July 2019, he joined the Power Electronic Systems Laboratory (PES), ETH Zurich as a Ph.D. student, focusing on advanced three-phase power

electronics inverters and PFC rectifiers.

Mina Tatic received the B.Sc. degree in Electrical Engineering and Computing from the School of Electrical Engineering of the University of Belgrade, Serbia, in 2018. In September 2018 she began her M.Sc. studies in Information Technology and Electrical Engineering at the Swiss Federal Institute of Technology (ETH) Zurich, Switzerland, focusing on power electronics.

Hidetoshi Ishida (M'96) received the B.S. and M.S. degrees from Kyoto Institute of Technology, Kyoto, Japan, in 1989 and 1991, respectively, and the Ph.D. degree from Osaka University, Osaka, Japan, in 2001, all in Electronic Engineering. In 1991, he joined Panasonic Corporation, Osaka, Japan, where he was engaged in the research and development of GaAs HFETs, HBTs, and GaAs MMICs. Since 2003, is involved in the research on GaN-based semiconductor devices. He authored or coauthored more than 60 technical papers in international jour-

nals and conference proceedings. He submitted more than 60 patents on semiconductor devices and on their process technologies. His current interest is on GaN-based bidirectional switches and on their applications.

**Dominik Bortis** (M'08) received the M.Sc. degree in electrical engineering and the Ph.D. degree from the Swiss Federal Institute of Technology (ETH) Zurich, Switzerland, in 2005 and 2008, respectively. In May 2005, he joined the Power Electronic Systems Laboratory (PES), ETH Zurich, as a Ph.D. student. From 2008 to 2011, he has been a Post-doctoral Fellow and from 2011 to 2016 a Research Associate with PES, co-supervising Ph.D. students and leading industry research projects. Since January 2016 Dr. Bortis is heading the newly established

research group Advanced Mechatronic Systems at PES.

Johann W. Kolar (F'10) received his M.Sc. and Ph.D. degree (summa cum laude/promotio sub auspiciis praesidentis rei publicae) from the University of Technology Vienna, Austria, in 1997 and 1999, respectively. Since 1984, he has been working as an independent researcher and international consultant in close collaboration with the University of Technology Vienna, in the fields of power electronics, industrial electronics and high performance drive systems. He has proposed numerous novel PWM converter topologies, modulation and control