© 2019 IEEE

IEEE Journal of Emerging and Selected Topics in Power Electronics, Vol. 7, No. 2, pp. 753-767, June 2019

## 99% Efficient 10kV SiC-Based 7 kV/400V DC-Transformer for Future Data Centers

D. Rothmund, T. Guillod, D. Bortis, J. W. Kolar

Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# 99% Efficient 10kV SiC-Based 7kV/400V DC-Transformer for Future Data Centers

Daniel Rothmund, *Student Member, IEEE*, Thomas Guillod, *Student Member, IEEE*, Dominik Bortis, *Member, IEEE* and Johann W. Kolar, *Fellow, IEEE*

Power Electronic Systems Laboratory, ETH Zurich, 8092 Zurich, Switzerland;

email: rothmund@lem.ee.ethz.ch

Abstract—The power supply chain of data centers from the medium voltage (MV) utility grid down to the chip level voltage consists of many series connected power conversion stages and accordingly shows a relatively low efficiency. Solid-State Transformers (SSTs) could improve the efficiency by substantially reducing the number of power conversion stages and/or directly interfacing the MV AC grid to a 400 V DC bus, from where server racks with a power consumption of several tens of kilowatts could be supplied by individual SSTs. The recent development of SiC MOSFETs with a blocking voltage of  $10 \, \mathrm{kV}$ enables the realization of a simple and hence highly reliable two-stage SST topology, consisting of an AC/DC PFC rectifier and a subsequent isolated DC/DC converter. In this context, an isolated  $25 \,\mathrm{kW}$ ,  $48 \,\mathrm{kHz}$ ,  $7 \,\mathrm{kV}$  to  $400 \,\mathrm{V}$  series resonant DC/DC converter based on 10 kV SiC MOSFETs is realized and tested in this paper. To achieve zero voltage switching (ZVS) of all MOSFETs, a special modulation scheme to actively control the amount of the switched magnetizing current on the MV and LV side is implemented. Furthermore, the design of all main components and especially the electrical insulation of the employed medium frequency (MF) transformer is discussed in detail. Calorimetric efficiency measurements show that a fullload efficiency of 99.0% is achieved, while the power density reaches 3.8 kW/L ( $63 \text{ W/in}^3$ ).

*Index Terms*—Medium-voltage, isolated DC/DC, softswitching, ZVS, 10kV SiC MOSFETs, calorimetric measurement, medium-voltage transformer.

## I. INTRODUCTION

Solid-State Transformer (SST) technology is considered as an interesting concept to increase the efficiency of the power supply chain from the medium voltage (MV) utility grid down to the chip voltage level in data centers, by directly interfacing the MV AC grid to a 400 V DC power distribution bus [1]-[4]. Thereby, the number of cascaded conversion stages is substantially reduced, resulting in a lower complexity, higher reliability, higher power density, and higher efficiency of data center power supplies. For redundancy reasons, it is intended that each server rack (which can reach power demands in the range of  $20 \dots 40 \,\mathrm{kW}$ , [5]–[7]) is supplied from an individual MV AC to 400 V DC SST. The power could then be distributed on MV level (e.g. 6.6 kV phase-to-phase rms, i.e. 3.8 kV rms phase-to-neutral) within the data center with the advantage of substantially lower cable cross sections and/or lower ohmic losses compared to LV distribution. Individual single-phase SSTs (single-phase for a low complexity) could then convert the MV grid voltage into 400 V DC and feed single server racks or clusters of racks, whereby the three phases of the

1

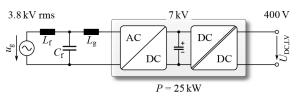

**Fig. 1:** Proposed single-cell two-stage realization of a MV AC to 400 V DC SST consisting of a front-end PFC AC/DC converter stage and an isolated DC/DC converter. To comply with EMI standards and to properly interface the SST to the MV grid via MV cables, an input LCL-filter is added. Given the isolated output voltage, different grounding schemes of the battery buffered DC output voltage can be implemented.

MV utility grid could be symmetrically loaded by connecting the same number of SSTs to each phase.

Up to the present, voltages in the 10 kV-range had to be interfaced by multi-cell converters based on ISOP, i.e. input series output parallel connected modules rated for a fraction of the total MV-side voltage, where each module is comprising an AC/DC [8]-[12] and an isolated DC/DC converter [13]-[15]. However, the recent development of  $10 \dots 15 \,\mathrm{kV}$  SiC MOSFETs with their outstanding switching behavior [16]-[20] enables the construction of single-cell SSTs avoiding the series connection of several modules, and therefore resulting in a simple and reliable converter structure. Due to the reduced complexity, also a higher power density can be expected. Therefore, this paper proposes a 10 kV SiC MOSFET-based single-cell two-stage 25 kW, 3.8 kV single-phase AC to 400 V DC SST (cf. Fig. 1) and provides a detailed analysis and experimental verification of the isolated 7 kV to 400 V DC/DC converter stage. The associated soft-switching 3.8 kV AC to 7 kV DC PFC converter has been presented in [1] and achieves a full-load efficiency of  $99.1\,\%$  and a power density of  $3.28 \, \text{kW/L}$  (54 W/in<sup>3</sup>).

As a part of the National Research Programme "Energy Turnaround" (NRP 70, cf. Acknowledgements), the efficiency goal of the SST is 98%. Therefore, the isolated DC/DC converter has to reach an efficiency of at least 98.9% or 99.0% at full load considering a certain margin. Furthermore, the DC/DC converter should achieve a power density of at least 3 kW/L (50 W/in<sup>3</sup>), comparable to the power density of the PFC rectifier stage [1]. In literature, a 15 kV SiC MOSFETbased isolated DC/DC converter with similar specifications (10 kV to 340 V, 20 kW) has been presented, achieving an extrapolated full-load efficiency of 97.3% and a power density of roughly 1.5 kW/L (25 W/in<sup>3</sup>) [21]. In contrast, considering the defined goals, the DC/DC converter at hand should generate only a third of the relative losses and should reach at least twice the power density.

To achieve such a compact converter, a relatively high switching frequency has to be selected, while to obtain the high efficiency, the switching losses have to be minimized by the operation of all MOSFETs under zero voltage switching (ZVS) conditions. Since the front-end AC/DC PFC stage controls the DC-link voltage, it is sufficient to realize the DC/DC converter with fixed voltage transfer ratio and galvanic isolation. For this reason, a series resonant converter (SRC) operated at resonance frequency and therefore acting as *DC transformer*, tightly coupling its input and output voltages according to the primary and secondary side turns ratio, is selected [22]. Due to the significantly different rise times of the MV and LV-side switch node voltages, a special modulation scheme has to be used for the system to achieve ZVS for all MOSFETs.

Due to the combination of the high switching frequency and the high voltage stress, dielectric losses in the transformer insulation material start playing a role. It has been shown in [23] that a thermal runaway and a destruction of the transformer could occur, if epoxy resin was selected as insulation material. The reasons are the relatively high dissipation factor and the low thermal conductivity of epoxy resins, which makes them unsuitable for the insulation of medium frequency (MF) MV transformers. Therefore, a special two component silicone compound is chosen as insulation material and the vacuum pressure potting (VPP) process used to insulate the winding package is presented in detail in this paper.

Section II describes the DC/DC converter topology and its modulation scheme to achieve ZVS conditions over the complete power range. In Section III, the design of all main converter components is explained in detail, with the focus on the MF transformer and its electric insulation, as well as the MV-side and LV-side power electronic interfaces. Section IV presents the experimental setup and measurement results including the obtained voltage and current waveforms, and the calorimetrically measured efficiency and loss distribution for different power levels. Finally, conclusions are drawn in Section V.

## II. TOPOLOGY AND MODULATION

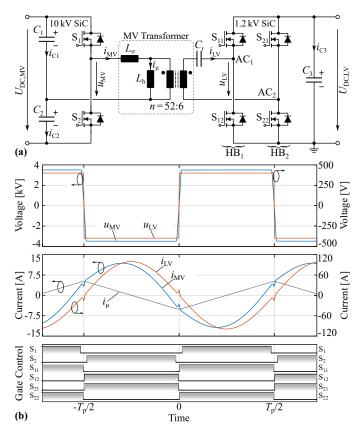

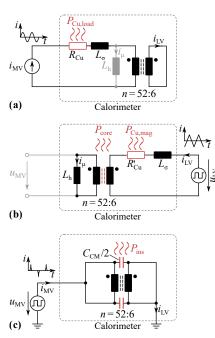

For the isolated DC/DC converter stage, an LLC series resonant converter (SRC) topology is selected, mainly for the reason of clamped switch voltages, the simple operation without closed-loop control, and the possibility to achieve ZVS for all semiconductors. Hence, a high switching frequency of 48 kHz can be selected, which results in a high power density. Furthermore, the SRC features sinusoidal transformer currents, which are beneficial in terms of reduced high-frequency effects in the winding and the core while the currents show a low rms value, which is only  $\pi/(2\sqrt{2}) = 1.11$  times higher than the corresponding DC current (magnetizing current neglected). The circuit diagram of this topology is shown in Fig. 2(a). It consists of a split DC-link and a 10 kV SiC MOSFET-based half-bridge on the MV-side, a 52 : 6 MF transformer providing the galvanic isolation, and a 1200 V SiC MOSFET-based fullbridge on the LV-side. The half-bridge configuration is selected

**Fig. 2:** (a) Circuit diagram of the LLC series resonant converter (SRC) consisting of a 10 kV SiC MOSFET half-bridge, a MF MV transformer for the galvanic isolation and the voltage step-down, a resonance capacitor  $C_{\rm r}$ , and a 1200 V SiC MOSFET full-bridge. (b) Simulated voltage and current waveforms of the SRC together with the corresponding gate control signals. It can be seen that the major part of the magnetizing current  $i_{\mu}$  is switched on the MV-side.

due to its rather simple construction and the associated voltage division by a factor of two, which is beneficial for the MF transformer design [24]. Although the LV-side DC-link voltage is only 400 V and therefore devices with 650 V or 900 V rating could be employed, 1200 V,  $25 \text{ m}\Omega$  SiC MOSFETs are used due to their outstanding performance and to keep the flexibility to adapt the SST for 800 V applications by just changing the transformer turns ratio.

## A. Modulation Scheme of the Dual-Active SRC

As already mentioned, the main task of the DC/DC converter is to provide the galvanic isolation and the constant 7 kV/400 V voltage transfer ratio, as the DC-link voltage level is controlled to a constant value by the AC/DC front end of the SST. Therefore, the SRC is operated at its resonance frequency, where it provides a quasi load-independent voltage transfer ratio and acts as a "DC transformer" [22]. Furthermore, incorporating a certain transformer magnetizing current  $i_{\mu}$  allows the ZVS operation of all MOSFETs and hence, due to the typically low soft-switching losses (SSL), a downsizing of passive components such as the MF transformer and the DC-link capacitors is enabled by increasing the switching frequency, which is fixed to 48 kHz.

**Fig. 3:** Magnified view of the MV-side and LV-side voltages and currents  $u_{\rm MV}$ ,  $i_{\rm MV}$  and  $u_{\rm LV}$ ,  $i_{\rm LV}$  during (a) the rising and (b) the falling voltage edge together with the gate control signals. Due to the much larger  $Q_{\rm OSS}$  of the MV-side MOSFETs (relative to the corresponding current), the voltage on the MV-side  $u_{\rm MV}$  rises/falls much slower than the LV-side voltage  $u_{\rm LV}$ . With the phase shift  $t_{\rm d}$  between the MV and LV-side gate control signals, the switching transitions can be center-aligned, whereby the different rise/fall times create a current spike in the transformer which is utilized as ZVS current for the LV-side MOSFETs. The magnetizing current is used as ZVS current for the MV-side MOSFETs.

Fig. 2(b) shows the simulated voltage and current waveforms together with the gate signals of all MOSFETs. For the "DC transformer" operating mode of the SRC, both the MV and the LV-side MOSFET bridges apply rectangular voltages with 50 % duty cycle to the resonant tank, i.e. the transformer's leakage inductance  $L_{\sigma}$  and the resonance capacitor  $C_{\rm r}$ , resulting in sinusoidal currents on both sides of the transformer. However, in order to achieve soft-switching, the MOSFETs must turn off a certain remaining inductive current

$$I_{\rm ZVS} = Q_{\rm OSS} / T_{\rm dt},\tag{1}$$

which depends on the effective output charge  $Q_{\text{OSS}}$  of the switching MOSFETs and the maximum duration of the resonant switching transition, i.e. the dead time duration  $T_{\text{dt}}$ .

Since the effective output charge  $Q_{OSS}$  of the 10 kV SiC MOSFETs on the MV-side is much larger than the effective output charge of the 1200 V SiC MOSFETs on the LV-side (considering the turns ratio of the transformer and/or the corresponding current), the available transformer magnetizing current should mainly flow on the MV-side to guarantee ZVS of all MOSFETs. This can be achieved by introducing a comparably small phase shift  $t_{\rm d}$  between the MV-side and the LV-side gate control signals. Fig. 3 shows a magnified view of the voltages and currents during the rising and the falling voltage edge, respectively. As can be seen, the phase shift  $t_{\rm d}$  is chosen such, that the MV-side bridge switches the major part of the magnetizing current  $i_{\mu}$ . Furthermore, due to the phase shift  $t_{\rm d}$ , the voltage transitions of the MV-side and the LV-side are aligned symmetrically, i.e. the much faster LV voltage transition is located in the middle of the MV voltage transition. Consequently, this leads to a certain voltage-time-

**TABLE I:** Specifications and characteristics of the isolated DC/DC converter. MOSFET on-state resistances given for  $T_{\rm j}=75\,^{\circ}{\rm C}$  (MV-side) and  $T_{\rm j}=100\,^{\circ}{\rm C}$  (LV-side).

| Parameter                                                                                                                                                                        | Symbol                                                                                                                | Value                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Nominal power<br>Switching frequency<br>MV-side DC-link voltage<br>LV-side DC-link voltage                                                                                       | $P_{ m N}$<br>$f_{ m sw}$<br>$U_{ m DC,MV}$<br>$U_{ m DC,LV}$                                                         | 25 kW<br>48 kHz<br>7 kV<br>400 V                                                                                                                 |

| MV-side DC-link capacitance<br>LV-side DC-link capacitance<br>Resonance capacitance                                                                                              | $\begin{array}{c} C_1, C_2 \\ C_3 \\ C_r \end{array}$                                                                 | 500 nF<br>70 μF<br>3.8 μF                                                                                                                        |

| Transformer leakage inductance<br>Transformer magnetizing inductance<br>Transformer turns ratio<br>MV-side transformer rms current<br>LV-side transformer rms current            | $L_{\sigma} \ L_{ m h} \ n \ I_{ m MV,rms} \ I_{ m LV,rms}$                                                           | 195 µH<br>4.1 mH<br>52 : 6<br>8.6 A<br>70.6 A                                                                                                    |

| Nominal phase shift<br>MV-side ZVS current<br>LV-side ZVS current                                                                                                                | $t_{ m d}$<br>$I_{ m ZVS,MV}$<br>$I_{ m ZVS,LV}$                                                                      | $\begin{array}{c} 300\mathrm{ns}\\ 4\mathrm{A}\\ 16\mathrm{A} \end{array}$                                                                       |

| MV-side DC-link rms current<br>LV-side DC-link rms current<br>MV-side switch rms current<br>LV-side switch rms current<br>MV-side switch resistance<br>LV-side switch resistance | $I_{\rm C1,C2,rms} \\ I_{\rm C3,rms} \\ I_{\rm S,MV,rms} \\ I_{\rm S,LV,rms} \\ R_{\rm DS,on,MV} \\ R_{\rm DS,on,LV}$ | $\begin{array}{c} 4.8 \text{ A} \\ 30.9 \text{ A} \\ 6.0 \text{ A} \\ 50.0 \text{ A} \\ 400 \text{ m}\Omega \\ 11.3 \text{ m}\Omega \end{array}$ |

area which is applied to the leakage inductance  $L_{\sigma}$  of the transformer, resulting in small current spikes on both sides of the transformer. As can be seen in Fig. 3, these current spikes lead to a reduction of the ZVS current on the MV-side, whereas on the LV-side the absolute value of the current  $i_{\rm LV}$ is increased. Due to the proper selection of the phase shift  $t_{\rm d}$ , now the LV-side switches exactly at the peak of these current spikes and hence, ZVS is also enabled for the LV-side. In practice, a compromise between the amount of magnetizing current switched on either side has to be found in dependency of the  $Q_{OSS}$  mismatch of the MV-side and the LV-side by selecting a suitable phase shift  $t_{d}$ . In the system at hand, it has been observed that this modulation works very well over the whole load range (0 kW to 25 kW) and is highly robust against changes in the switching frequency, the voltage level and even the phase shift  $t_{\rm d}$ . For the experimental analysis  $t_{\rm d} = 300 \, \rm ns$ has been selected (cf. TABLE I).

## **III. SYSTEM DESIGN**

In the following, the design of the individual main components of the DC/DC converter is described. **TABLE I** shows the specifications of the SRC, together with the values of the switched currents, and the rms current stresses of the individual components as a basis for the converter design.

## A. MV-Side 10 kV SiC MOSFET-Based Half-Bridge

On the MV-side, a 10 kV SiC MOSFET-based half-bridge comprising *Wolfspeed CPM3-10000-0350* devices in combination with a split DC-link is used. For the determination of the semiconductor losses, the conduction and the switching losses are calculated in the following. With the on-state resistance and the rms current given in **TABLE I**, the total

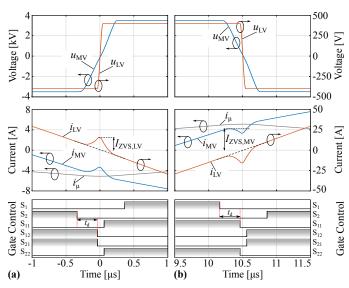

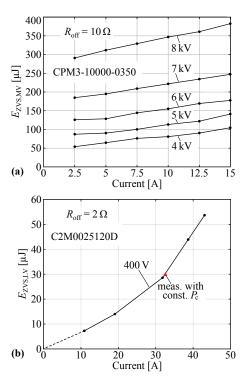

Fig. 4: (a) Calorimetrically measured soft-switching losses (SSL) of the 10 kV SiC MOSFETs for different DC-link voltages and currents (taken from [16]). (b) Calorimetrically measured SSL of one *C2M0025120D* 1200 V SiC MOSFET for different currents and a DC-link voltage of 400 V. To verify the applied calorimetric SSL measurement method, the indicated point is measured with constant conduction losses  $P_c$  and two different switching frequencies.

conduction losses of both MOSFETs are  $P_{c,MV} = 28.8$  W during full-load operation. Furthermore, although the MOSFETs are operated under ZVS, certain soft-switching losses (SSL) arise, but are not available as datasheet values. Therefore, the calorimetrically measured SSL in **Fig. 4(a)**, taken from [16], are used to determine the switching losses. For a DClink voltage of  $U_{DC,MV} = 7$  kV and a switched current of  $I_{ZVS,MV} = 4$  A, the energy loss per switching cycle and per MOSFET is  $E_{ZVS,MV} = 191 \mu$ J. Therefore, the MV-side switching losses at a switching frequency of  $f_{sw} = 48$  kHz are  $P_{sw,MV} = 18.3$  W and together with the conduction losses, the total MV-side semiconductor losses are 47.1 W at full load.

For the realization of the MV-bridge, the goal is to achieve a highly compact design, despite the fact that large distances for the electrical isolation are necessary for voltages in the MV range. According to the IEC 60950-1 International Standard [25], for a sustainable operation, the required creepage distance for 7 kV is  $d_{\rm cr} = 32$  mm, and the minimum clearance distance is  $d_{\rm cl} = 17.5$  mm. Therefore, during the design of the PCB-based MV-bridge, possible creepage paths have to be identified and interrupted by creepage slots, which increase the breakdown voltage since  $d_{\rm cl} < d_{\rm cr}$ .

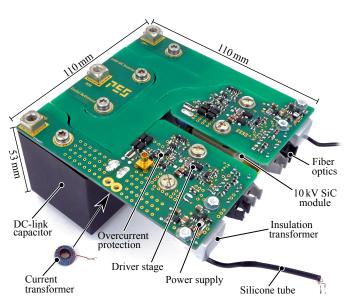

**Fig. 5** shows the realized MV bridge. The PCB interconnects the DC-link capacitor with the low-side and the high-side MOSFETs, whereby busbars (not visible) are used for the connection of the drain terminals (i.e. the base plates) of the MOSFETs. Since both MOSFETs are mounted on one PCB, the full (switched) DC-link voltage of  $U_{\rm DC,MV} = 7 \,\text{kV}$  occurs

Fig. 5: 10 kV SiC MOSFET-based half-bridge with DC-link capacitors and gate driving circuitry including an ultrafast overcurrent protection, and 20 kV isolation voltage rated (and tested) gate driver power supplies.

between the low-side and the high-side circuits on the PCB. In order to still achieve a highly compact design despite the large required creepage distances, a creepage slot separates the high-side from the low-side circuits. Furthermore, highly compact isolation transformers for the power supply of the gate drivers are on-board and feature an isolation voltage rating of 20 kV. These transformers are fed from driver circuits which are separated from the MV, whereby the required creepage distance is provided by silicone tubes that are enclosed in the insulation material of the transformer. In order to protect the 10 kV SiC MOSFETs against harmful overcurrents in case of e.g. an isolation breakdown or an operational fault, the gate drivers are equipped with an ultrafast overcurrent protection circuit (based on monitoring the source current with an airgapped current transformer), which reacts within 22 ns and safely turns off all MOSFETs, even in case of a flashover. More details on the gate driver isolation transformers and the overcurrent protection circuit is given in [26].

The 10 kV SiC modules are directly mounted on separate heat sinks without any electrical insulation. However, since the base plates of the modules are non-isolated (i.e. the base plates act as drain terminals), the heat sinks (not shown) are floating on the respective drain potential such that the fans have to be separated from them by a clearance distance of at least  $d_{\rm cl} =$ 17.5 mm, as similarly done in [1]. Although a certain part of the air flow is bypassing the heat sinks, a thermal resistance of  $R_{\rm th,MV} = 0.125 \,\rm K/W$  per heat sink is achieved and the expected heat sink temperature increase is less than 5 K, which is beneficial in terms of a low  $R_{\rm DS,on}$  and consequently low conduction losses of the 10 kV SiC MOSFETs.

## B. LV-Side 1200 V SiC MOSFET-Based Full-Bridge

The LV-side of the isolated DC/DC converter is realized with 1200 V,  $25 \text{ m}\Omega$  SiC MOSFETs *C2M0025120D* from *Wolfspeed*, since they offer a low on-state resistance and a

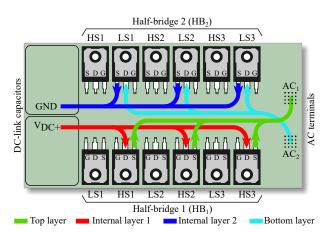

**Fig. 6:** Bottom-view of the full-bridge layout for symmetrical current path lengths through the individual MOSFETs in the parallel connection. PCB current path only indicated for high-side MOSFETs of half-bridge 1 (HB<sub>1</sub>), cf. S<sub>11</sub> in Fig. 2(a), and low-side MOSFETs of half-bridge 2 (HB<sub>2</sub>), i.e. S<sub>22</sub> in Fig. 2(a). Each switch is composed of three parallel-connected TO247 devices.

certain flexibility for future, e.g. 800 V, applications. However, in order to handle the high current on the LV-side and to reduce the conduction losses, each switch of the LV-side fullbridge consists of three parallel C2M0025120D MOSFETs. With the intention of a symmetric current distribution among the three parallel MOSFETs per switch, the current path from the DC-link capacitor through the bridge-legs to the ACterminals must be symmetric for all MOSFETs. Fig. 6 shows the realized layout of the full-bridge. The MOSFETs of each half-bridge are lined up between the DC-link capacitors on the left side and the AC terminals on the right side. This ensures an equal current path length through all MOSFETs and guarantees a symmetric current distribution. Furthermore, the high-side MOSFETs (HS1...HS3) and the low-side MOS-FETs (LS1...LS3) in each half-bridge are placed alternately in order to minimize the commutation loop inductance. Inductive switching tests show that currents of up to 100 A can be switched without oscillations or an asymmetric current distribution, as the homogeneous temperature distribution observed on thermal images of the MOSFET cooling pads prove.

For an estimation of the LV-side semiconductor losses, the conduction and the switching losses of the LV-side full bridge are calculated. With the LV-side MOSFET rms current  $I_{\rm S,LV,rms}$  and the equivalent on-state resistance  $R_{\rm DS,on,LV}$  of the parallel connection of three *C2M0025120D* MOSFETs given in **TABLE I** (specified for  $T_{\rm j} = 100$  °C), the conduction losses are  $P_{\rm c,LV} = 113$  W.

1) LV-Side Soft-Switching Loss (SSL) Measurements: Similar to the MV-side MOSFETs, also the SSL of the 1200 V SiC MOSFETs are not given in the datasheet. Therefore, calorimetric SSL measurements with C2M0025120D MOSFETs are carried out for a drain-source voltage of 400 V and different switched currents. Thereby, an inductor is connected to the AC terminals of the full-bridge, which is soft-switched with a duty cycle of 50 %, leading to symmetrical triangular current in the inductor. The switched current can be varied via the switching frequency or the inductance value, where the MOSFETs always turn off the peak value of the triangular

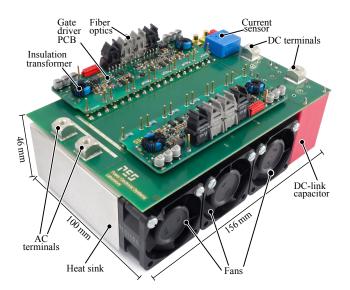

**Fig. 7:** Picture of the LV-side 1200 V SiC-based full-bridge with three parallel *C2M0025120D* MOSFETs per switch.

current under ZVS conditions [16], [18]. Besides the conduction losses during the on-state of the MOSFETs, each turn-off event generates a certain amount of SSL in the MOSFETs. The total LV-side semiconductor losses are measured via the temperature increase of the heat sink and its thermal resistance  $R_{\rm th}$  (similar as shown in [1]), which is known from calibration measurements with constant DC power. In order extract the SSL out of the total losses, at the same time the conduction losses are determined by measuring the current and the onstate voltage of the MOSFETs with a special on-state voltage measurement circuit (OVMC) [27] during operation. For these SSL measurements, the full-bridge is equipped with only one C2M0025120D MOSFET per switch. Fig. 4(b) shows the resulting SSL per switching cycle for a DC-link voltage of 400 V and different switched currents, measured with a turn-off gate resistor of  $R_{\rm off} = 2\,\Omega$ . As can be seen, the SSL increase approximately linearly with the current for low currents and start increasing disproportionately for currents beyond 20 A.

To verify the measured SSL, a different measurement method is applied. Thereby, the intention is to keep the conduction losses  $P_{\rm c}$  constant (by keeping the peak of the triangular current and therewith the switched current  $I_{\rm sw}$  constant) and to measure the total semiconductor losses  $P_{\rm semi1}$  and  $P_{\rm semi2}$  (again thermally via the temperature increase and the  $R_{\rm th}$  of the heat sink) at different switching frequencies  $f_{\rm sw1}$  and  $f_{\rm sw2}$  [28]. Consequently, to keep the peak current constant when the switching frequency is changed, the inductance value has to be adapted accordingly. By taking the difference between the two measured loss values, the conduction losses cancel out and the SSL for the switched current  $I_{\rm sw}$  can be calculated as

$$E_{\rm ZVS,LV}\left(I_{\rm sw}\right) = \frac{P_{\rm semi2} - P_{\rm semi1}}{f_{\rm sw2} - f_{\rm sw1}}.$$

(2)

This method has been applied for a switched current of  $I_{sw} = 32.5 \text{ A}$  and as can be seen in **Fig. 4(b)**, the obtained SSL

match very well with the curve obtained with the OVMC, which proves a high accuracy of the measurement method.

With the measured SSL of the LV-side MOSFETs, the SSL during operation of the DC/DC converter can now be determined. Assuming a symmetric current distribution among the three parallel MOSFETs per switch of the full-bridge and a ZVS current of  $I_{\rm ZVS,LV} = 16$  A (cf. **TABLE I**), each MOSFET turns off a current of  $I_{\rm ZVS,LV}/3 = 5.33$  A. Consequently, the total LV-side switching losses of the four power switches each consisting of 3 parallel MOSFETs are

$$P_{\rm sw,LV} = 4f_{\rm sw} \cdot 3E_{\rm ZVS} \left( I_{\rm ZVS,LV} / 3 \right) = 1.56 \,\mathrm{W},$$

(3)

whereby the the switching loss curve in **Fig. 4(b)** is extrapolated towards lower currents in order to obtain the SSL value for a switched current of 5.33 A. As can be noted, the SSL of the LV-side are very small, considering the system power rating of 25 kW. However, in e.g. a phase shifted dual-active bridge topology, where the MOSFETs would be turned off at the peak of the current [29], [30], the SSL would become significant.

2) LV-side Full-Bridge Hardware: Fig. 7 shows a picture of the realized 1200 V SiC-based LV-side full-bridge. It consists of a 4-layer power PCB (140  $\mu$ m outer and 105  $\mu$ m inner copper thickness), which holds the MOSFETs, the DC-link capacitors, the heat sink as well as the fans, and two gate drive PCBs with isolated auxiliary supplies, each driving one half-bridge. The gate signals are received via optical fibers from a central DSP-board. Furthermore, current and voltage measurement circuits are implemented for control and monitoring purposes. As can be seen, the bridge is highly compact with dimensions of only  $156 \times 100 \times 46$  mm.

## C. Resonance Capacitor

As shown in Fig. 2(a), the resonance capacitor  $C_r$  is connected in series to the LV-side winding of the transformer and it not only acts as resonance capacitor but also as DCblocking capacitor in case the voltage applied from the LV-side full-bridge contains a small DC offset, e.g. due to incorrect switching times resulting from discretization errors in the DSP. Further reasons not to place the resonance capacitor on the MV-side are the split DC-link on the MV-side, which already takes care of the DC-blocking, and the fact that no MV-insulation of the resonance capacitor is required on the LV-side. The capacitance of  $C_{\rm r}$  can be calculated via the leakage inductance of the transformer (as well as the additional stray inductance of the busbars) and the desired resonance frequency, which is equal to the switching frequency  $f_{\rm sw}$  and results in  $C_{\rm r} = 3.8\,\mu{\rm F}$ . Care must be taken when the DClink capacitors are comparably small and start influencing the resonance [31]. Due to the high transformer LV-side current of 70.6 A (cf. TABLE I), which also flows through the resonance capacitor  $C_{\rm r}$ , a low-loss capacitor with a high current rating is required. Therefore, and with the purpose of offering a high flexibility regarding the value of  $C_{\rm r}$ , a parallel connection of 38 COG ceramic capacitors in a 2220 package  $(5.7 \times 5.0 \times 2.8 \text{ mm})$ with  $100 \,\mathrm{nF}$  each and a voltage rating of  $450 \,\mathrm{V}$  is selected. With the dissipation factor of  $\tan \delta = 0.05 \,\%$ , the capacitor

losses can be determined as  $P_{\rm Cr} = 2.17 \,\rm W$  at full-load operation. The capacitor array is soldered between two copper plates for the connection to the transformer and the PCB terminal. At full-load operation of the converter, the capacitor temperature under natural convection is only 45 °C, which means that no additional cooling is required.

## D. MF MV Transformer

One of the key components of the isolated DC/DC converter at hand is the MF MV transformer, which is responsible for the voltage step-down and the galvanic isolation between the MV-side and the LV-side. Although it is well known in power electronics how to design MF transformers (for voltages below 1 kV) and it is well known from power systems how to design the electrical insulation of MV or even highvoltage  $50/60 \,\mathrm{Hz}$  transformers, the combination of MF and MV in a transformer is very challenging in many aspects. Only the recent development of SiC MOSFETs with blocking voltages of 10...15 kV and their outstanding soft-switching capabilities allow for the combination of switching frequencies around 50 kHz and switched voltages in the  $5 \dots 10 \text{ kV}$  range. With these conditions and the aim for a highly compact design (which directly excludes oil as insulation and cooling medium for this power level due to the required oil-expansion tank and dehydration breather), two major problems arise. Due to the MV, the insulation material layer, which encapsulates the MV winding and isolates it from the LV-winding and the core, has to be chosen rather thick. However, the losses of the MV winding have to be extracted by heat conduction through the insulation material, which typically features only a very low thermal conductivity. Furthermore, in a highly compact transformer, the surface area for the heat extraction is small and consequently, the cooling of the MV-winding is very challenging. Secondly, due to the combination of the high switching frequency and the high switched voltage, dielectric losses inside the insulation material can lead to local hotspots, to thermal degradation and even to a thermal runaway [23]. Consequently, it is important to select a suitable insulation material and to consider the dielectric losses during the design process of the MF MV transformer.

1) Transformer Pareto Optimization: With the purpose of achieving a highly compact and efficient transformer, it is optimized with respect to power density and losses. For the high targeted efficiency and power density, only ferrite core material, litz wire and shell-type windings are considered. While the magnetizing inductance, the core material (BFM8) and the isolation distances are fixed, a sweep over the following parameters is carried out and the winding, the core, and the dielectric losses within the transformer operated at nominal power are determined by coupled FEM simulations:

- operating frequency;

- core shape (U-core or E-core);

- core dimensions;

- number of layers and chambers on the MV-side;

- number of turns on the MV and the LV-side;

- litz wire diameter and number of strands;

- strand diameter.

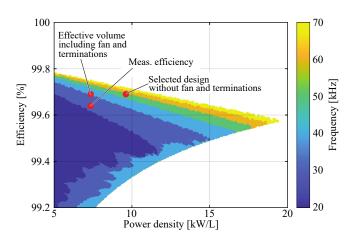

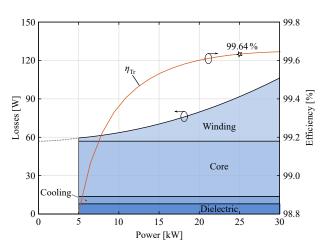

Fig. 8: Volume/loss Pareto optimization of the MF MV transformer for different operating frequencies (color-coded). The optimization does not include the volume of the fan and the terminations. Therefore, these volumes are added separately and the effective volume is indicated in the figure. Additionally, the measured efficiency, which is slightly lower than the simulated efficiency (99.64 % compared to 99.69 %, i.e. 0.05 % difference), is shown.

The simulations include high-frequency effects in the litz wire [32]–[34], the fringing field of the air gap [35], and the effects of the non-sinusoidal magnetic flux by calculating the core losses via iGSE [36]. During the simulation, transformer designs which exceed a certain current density in the windings, a certain core loss density, or a certain dielectric loss density in the insulation material, are discarded in order to avoid designs which would cause a thermal runaway of the transformer. Fig. 8 shows the results of the Pareto optimization of the transformer for different operating frequencies. As can be seen, there is a trend towards higher possible efficiencies and power densities for an increasing operating frequency. However, the efficiency gain between 50 kHz and 70 kHz is rather insignificant and a selection of a high switching frequency would also lead to an increase of the soft-switching losses and hence to a decrease of the total converter efficiency. In order to reach the DC/DC converter's full-load efficiency goal of 99.0%, the maximum allowed transformer losses are 75 W, given the fact that the MV-side and the LV-side bridges, the resonance capacitor, the auxiliary supplies, and the fans together generate around 175 W of losses. Therefore, a design with a calculated efficiency of 99.69% and an operating frequency of 48 kHz is selected. The chosen transformer is a U-core design, which features a larger exposed area of the winding package for the forced convective cooling and an easier construction of the litz wire terminations compared to E-core designs. The chosen transformer is pointed out in Fig. 8 and as indicated, if the volumes of the fan and the litz wire terminations are included, the power density slightly decreases. Furthermore, the design point of the realized transformer with its calorimetrically measured efficiency (cf. Section III-D5) is shown in the Pareto plot and as can be noted, the simulated and the measured efficiencies (99.69% and 99.64%, respectively)are very close, which indicates an accurate simulation as well as an accurate measurement of the transformer losses.

TABLE II lists the key parameters of the realized transformer design and as can be noted, a two-chamber winding

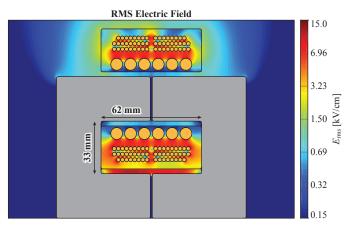

Fig. 9: FEM simulation of the electric field distribution (rms values) of the transformer for a  $\pm 3.5\,kV/400\,V$  excitation.

TABLE II: Key parameters of the realized MF MV transformer.

| Parameter                                                 | Value                                                                                                                                                                    |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nominal power<br>Operating frequency<br>Terminal voltages | $\begin{array}{c} 25{\rm kW} \\ 48{\rm kHz} \\ \pm 3.5{\rm kV}/\pm400{\rm V} \end{array}$                                                                                |

| Winding<br>MV litz winding<br>LV litz winding             | $\begin{array}{c} 52:6 \text{ turns, litz wire, shell-type} \\ 630\times71\mu\text{m, three layers, two chambers} \\ 2500\times100\mu\text{m, single layer} \end{array}$ |

| Core type<br>Air gap<br>Insulation                        | U-core, BFM8 ferrite, $2500 \text{ mm}^2$<br>$2 \times 1.1 \text{ mm}$<br>4.0  mm thickness, designed for $15  kV$                                                       |

is selected on the MV-side in order to reduce the electric field stress between the three layers of the MV-winding, which increases the reliability of the electric insulation. For a deeper analysis of the electric field strength inside the transformer winding package and the surrounding air, the result of a 2D FEM simulation is shown in **Fig. 9**, whereby the insulation material has been modeled with its permittivity given in **TABLE III**. As can be seen, the maximum rms electric field is  $15 \,\mathrm{kV/cm}$  and the peak value is more than 10 times below the electric breakdown field strength of the utilized insulation material. It has to be noted that a higher electric field would lead to quadratically higher dielectric losses

$$P_{\rm ins} \propto E^2 \cdot f_{\rm sw} \cdot \tan \delta, \tag{4}$$

and possibly to partial discharges, which both would enhance the material's ageing process due to local hot spots and degradation. As will be shown by calorimetric measurements in Section III-D5, the dielectric losses account for a significant part of the total transformer losses and cannot be neglected as in case of MF LV transformers.

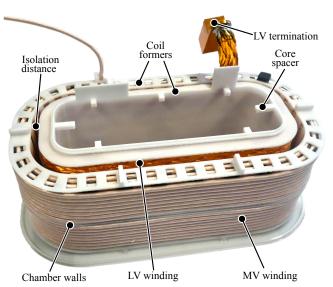

2) Construction of the Transformer Windings: Due to their different electric potentials, the MV and LV windings have to be isolated from each other by an electric insulation material. In order to guarantee that the insulation material thickness between the MV and the LV-winding is constant at a value of 4.0 mm, the MV and the LV-winding are wound on individual 3D-printed coil formers (material: polycarbonate) and assembled concentrically, as shown in **Fig. 10**. With this

Fig. 10: Picture of the MV and LV transformer windings on their 3D-printed coil formers. The isolation distance between the MV and the LV windings, as well as the chamber walls separating the two MV winding chambers can be seen.

arrangement, the LV-winding acts as an electric field shield between the MV-winding and the core and therefore, no MVinsulation is required on the surface of the LV-winding which faces the core. For the cooling of the windings, the LV coil former is equipped with core spacers (cf. Fig. 10), which separate the core from the winding package by a certain distance and allow an air flow to pass in between. Furthermore, polypropylene spacers are used between the three layers of the MV winding in order to keep a distance of 0.8 mm between the individual layers, such that the insulation material can flow into the interspaces during the subsequent potting process. Additionally, for the monitoring of the winding temperature, several NTC temperature sensors are placed close to the LVwindings. Once the windings are assembled, the HF litz wires are soldered into the intended copper terminations to guarantee a low contact resistance.

3) Vacuum Pressure Potting of the Transformer Windings: For the potting of the windings, the coil formers are closed with another 3D-printed part, resulting in a sealed winding package which is then filled up with the insulation material. As already mentioned, standard insulation materials such as Epoxy resins are unsuitable for MF MV applications due to their typically low thermal conductivity and/or high dielectric losses. Therefore, a two-component silicone compound (containing thermally conductive particles) of type *TC-4605 HLV* from Dow Corning is used. The properties of this material are listed in **TABLE III**. An additional advantage compared to

TABLE III: Properties of the utilized silicone Dow Corning TC-4605 HLV.

| Property                            | Value                         |

|-------------------------------------|-------------------------------|

| Dielectric strength                 | $24\mathrm{kV/mm}$            |

| Dielectric constant $\varepsilon_r$ | $< 4.1$ for $f > 50  \rm kHz$ |

| Dissipation factor $\tan\delta$     | $< 0.8\%$ for $f > 50\rm kHz$ |

| Thermal conductivity                | $1\mathrm{W}/(\mathrm{mK})$   |

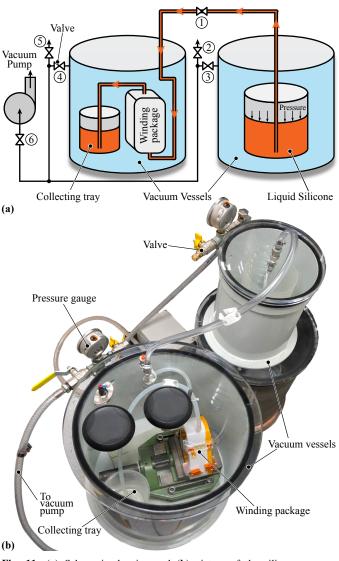

Fig. 11: (a) Schematic drawing and (b) picture of the silicone vacuum pressure potting (VPP) process of the transformer winding package. Both vessels are evacuated (30 mbar) to devolatilize the liquid silicone. Then, the pressure in the right vessel is increased, pressing the silicone through the tubes into the sealed winding package, from where the excessive silicone flows into a collecting tray. After the filling process, the pressure is increased to atomspheric pressure again, in order to compress possible vacuum cavities. Finally, the silicone is cured at  $120 \,^{\circ}$ C.

epoxy resin is the mechanical flexibility of the silicone, which prevents it from cracking during the curing.

The utilized silicone shows outstanding dielectric and thermal properties but reacts highly sensitively to amines, amides, nitriles, and alcohols etc. during the curing process. These substances might be contained e.g. in adhesives used for the mechanical fixing of the turns during the construction of the windings. When the still liquid silicone comes in contact with one of these substances, it might not cure properly, preventing it from developing its dielectric properties [37]. Therefore, the compatibility of the silicone to any adhesives or in general to any materials contained in the winding package has to be verified. It has been found that e.g. cyanoacrylate-based instant adhesives and UV adhesives are unsuitable, whereas two-component instant adhesives, such as *LOCTITE 3090*, for example, have been used successfully.

To guarantee a high reliability of the MV-insulation, the insulation material must be free of cavities or other imperfections, which can lead to partial discharges. To achieve this, a vacuum pressure potting (VPP) process, as shown in Fig. 11(a), is used. Thereby, the already mixed liquid twocomponent silicone and the winding package are placed in two separate vessels. With a vacuum pump, both vessels are evacuated down to a pressure of 30 mbar while values (1), (3), (4) and (6) are open. Since there is no silicone yet in the collecting tray, the tubings and the sealed winding package are evacuated as well. After a certain time, when the liquid silicone is devolatilized, valves (4) and (6) are closed. The pressure in the right vessel is then slightly increased by shortly opening value (2), which presses the liquid silicone into the tubings and from bottom to top through the winding package. To remove possible cavities inside the winding package, this process is not stopped before approximately 300 mL of the liquid silicone have flown through the winding package into the collecting tray. For the further steps, it is important that both ends of the tubings are located below the surface of the liquid silicone, such that no air can enter. Now, value (1) is closed and both vessels are pressurized again to atmospheric pressure, compressing possible vacuum cavities inside the winding package. Finally, the tubes entering and leaving the winding package are clamped to avoid any further flow of the silicone and the winding package is cured for several hours at a temperature of 120 °C in order to activate the adhesion of the silicone to other materials. The best results regarding adhesion are achieved when the temperature is applied directly after the VPP process, although the curing itself does not require an increased temperature. However, if the temperature is only applied after the curing at room temperature, the silicone might detach from the coil former, leading to undesired vacuum or air cavities between the coil former and the silicone. Fig. 11(b) shows a picture of the VPP setup with the two vacuum vessels and the sealed winding package. The covers of the vacuum vessels are made out of acrylic glass and each vessel is equipped with a pressure gauge to enable the monitoring of the process by eye.

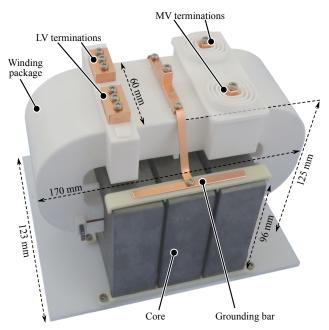

4) Transformer Prototype: The assembled transformer consisting of the winding package and the ferrite cores is shown in **Fig. 12**. As can be seen, the core spacers of the winding package separate it from the core by a certain distance, forming an air channel for the forced convective cooling of both, the core and the windings. However, since the insulation between the LV-winding and the inner wall of the winding package is not designed for MV but only for LV (cf. **Fig. 9**) and the core spacers represent a direct creepage path between the winding package and the cores, the cores must be tied to ground potential. For this reason, a grounding bar is attached to the ferrite cores with the help of a conductive silver adhesive.

For the verification of the electrical insulation of the transformer, a DC voltage of 20 kV has been successfully applied to the MV-winding for one hour.

In operation, the transformer is cooled by a fan (not shown), which provides an air flow onto the cores, the winding package and through the air channel in between. The dimensions of the

Fig. 12: Picture of the realized  $25 \,\mathrm{kW}$  MF transformer consisting of three BFM8-ferrite U-core sets and the winding package with the mounted MV-side and LV-side terminations.

transformer are indicated in **Fig. 12** and the boxed volume of the transformer itself is 2.6 L and the volume is 3.4 L when also the terminations and the fan are included. Therefore, the 25 kW MF MV transformer achieves a power density of 7.35 kW/L (including the fan and the terminations).

5) Transformer Measurements: To characterize the efficiency of the transformer as one of the key components of the isolated DC/DC converter at hand, electrical or calorimetric measurement methods can be applied. However, literature has shown that electrical efficiency measurements of highly efficient systems (either converters or individual power components) are inaccurate, even in case the input and output voltages and currents are DC or 50 Hz AC [1]. Consequently, even larger measurement errors can be expected in case of an electric efficiency measurement of an MF MV transformer operated with switched voltages due to skews between the voltage and current measurements and the limited bandwidth of the measurement devices. Therefore, instead of electrically measuring the input and output power of the transformer to determine its efficiency, its losses are directly measured calorimetrically. With the aim of not only determining the total losses of the transformer but also the loss distribution among the windings, the core, and the insulation material, these loss components are measured independently in a highly accurate two-chamber calorimeter [38].

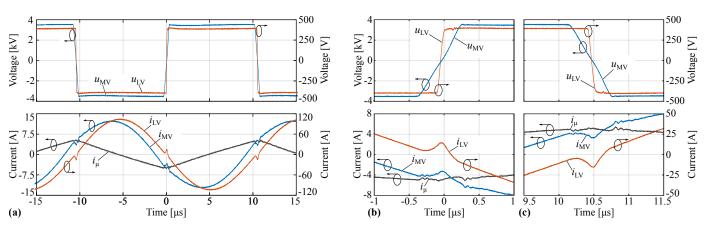

Fig. 13(a) shows the measurement setup for the determination of the winding losses. For this purpose, the LV-winding of the transformer is shorted, and since the currents during the operation of the DC/DC converter are quasi-sinusoidal, a sinusoidal current with a frequency of 48 kHz (which is the operation frequency of the DC/DC converter) is impressed into the MV-winding. Due to the short-circuit on the LVside, the magnetic flux in the core is nearly zero and no core

Fig. 13: Calorimetric measurement setups for (a) the winding losses, (b) the core losses, and (c) the dielectric losses  $P_{ins}$  in the insulation material of the transformer.

losses but only the winding losses  $P_{\text{Cu,load}}$  in the equivalent resistance  $R_{\text{Cu}}$  of both windings caused by the sinusoidal load current occur and can be measured calorimetrically for different amplitudes (i.e. different loads).

Furthermore, the circuit for the measurement of the core losses is shown in Fig. 13(b). Thereby, the MV-side of the transformer is left open, while a rectangular voltage is applied to the LV-winding, creating a triangular magnetizing current and magnetic flux with equal values as during real operation of the DC/DC converter. Besides the actual core losses  $P_{\rm core}$ , also the small part of the ohmic and air-gap fringing-field-related winding losses  $P_{Cu,mag}$  generated by the magnetizing current during DC/DC operation is measured, but together with the losses from the winding loss measurement with the sinusoidal load current (cf. Fig. 13(a)) adds up to the correct total winding losses, i.e.  $P_{Cu} = P_{Cu,load} + P_{Cu,mag}$ . Furthermore, in this arrangement, the dielectric losses in the insulation material are present as well. However, the dielectric losses are measured individually (as shown below) to separate them from the core losses.

Since the losses of ferrite material is typically strongly temperature dependent, the core temperature during the core loss measurement must be equal to the core temperature during the operation of the DC/DC converter. Due to the airchannel between the winding package and the ferrite cores of the transformer, their thermal coupling is extremely low. Accordingly, the core temperature and hence the core losses are not significantly influenced by the winding temperature during the converter operation. For this reason, the core temperature and therewith the core losses can be assumed as constant over the whole power range, since always the same voltage time area is applied to the transformer independently of the transferred power.

Fig. 14: Calorimetrically measured distribution of the transformer losses together with the transformer efficiency curve. At the rated converter power of 25 kW, the transformer efficiency reaches 99.64 %.

As already mentioned, due to the combination of the high voltage and the high frequency, dielectric losses occur in the insulation material. To determine these losses by measurement, the circuit in Fig. 13(c) is used. As can be seen, the transformer is shorted on both sides and grounded on the LV-side. The MV-side is excited by a rectangular voltage generated by the MV-side bridge-leg (cf. Section III-A) with the same frequency (48 kHz), rise time (600 ns), and amplitude ( $\pm 3.5$  kV) as during real converter operation. Thereby, the parasitic commonmode (CM) capacitances  $C_{\rm CM}$  between the MV and the LVwinding are charged and discharged, which in combination with a certain dissipation factor  $tan \delta$  causes dielectric losses that are measured calorimetrically. As can be noticed, with this pure CM excitation, only the CM-component of the dielectric losses are included. However, in converter operation, there is also a differential-mode (DM) voltage across the MV-winding, which causes dielectric losses in the inter-layer insulation as well. To also include these losses, the electric field FEM simulation (cf. Fig. 9) is calibrated in such a way that the pure CM insulation losses match with the measurement, before the simulation is extended to also include the DM losses.

The distribution of the calorimetrically measured transformer losses is shown in **Fig. 14** together with the efficiency curve over the load range from 5 kW to 30 kW. Besides the winding, core and dielectric losses, the losses caused by the fan for the cooling of the transformer are also included. As can be seen, at full load (25 kW), the measured efficiency reaches 99.64%. Furthermore, with a loss distribution of  $P_{\rm Cu} = 34.8 \,\mathrm{W}$  (winding losses),  $P_{\rm core} = 43.2 \,\mathrm{W}$  (core losses),  $P_{\rm ins} = 8.0 \,\mathrm{W}$  (dielectric losses), and  $P_{\rm cooling} = 5.8 \,\mathrm{W}$  (cooling losses), it can be noted that the dielectric losses account for 9% of the total transformer losses and indeed have to be considered in MF MV transformer designs, especially regarding a possible thermal runaway.

If for the calorimetric transformer loss measurement the following measurement errors are assumed (core losses 25% (due to the strong temperature dependency), winding losses 20%, dielectric losses 40% (since only the CM part is measured and the DM part is determined by a re-calibrated simulation),

Fig. 15: (a) Measured voltage and current waveforms during 25 kW operation of the converter. The magnetizing current  $i_{\mu}$  is determined as the difference between the MV-side current  $i_{MV}$  and the transformed LV-side current  $i_{LV}$ . (b) & (c) Magnified views of the voltages and currents during the rising and falling voltage transition, respectively. Practically the total magnetizing current  $i_{\mu}$  is available for ZVS on the MV-side, whereas the current spikes are utilized for achieving ZVS on the LV-side.

and cooling power 2%), a total efficiency measurement error of  $\pm 0.08\%$  results for the transformer, i.e. its efficiency is in the range of  $99.64\% \pm 0.08\% = (99.56\% \dots 99.72\%)$ .

## IV. EXPERIMENTAL SETUP AND RESULTS

For the experimental verification and the efficiency evaluation of the realized DC/DC converter, an appropriate test setup is required. Due to its bidirectionality, the converter can either be supplied from the LV-side or the MV-side, whereby the transferred power is dissipated in a variable load resistor in order to be able to operate the converter at different power levels. In this case, the converter is supplied from the 400 Vside by two paralleled 0...500 V, 0...40 A power supplies (*Regatron TopCon Quadro TC.P.16.500.400.S*). During converter operation, the voltages and currents at the transformer terminals are measured especially in order to see whether or not the converter is operated under ZVS conditions on both sides. For this purpose, a *LeCroy HDO4054A* oscilloscope in combination with *Pearson* current transformers and differential voltage probes (*LeCroy HVD3605*) is used.

For the measurement of the complete system efficiency, the losses of all main power components have to be measured. As already mentioned, calorimetric measurement methods achieve a much higher accuracy compared to electrical measurement methods. Since the efficiency curve of the transformer is already characterized calorimetrically (cf. Fig. 14), the remaining main sources of losses are the 10 kV SiC MOSFETs on the MV-side and the 1200 V SiC MOSFETs on the LV-side. The power demand of the auxiliary supplies for the gate drivers and the cooling system can easily be measured electrically, whereby the relatively small losses of the resonance capacitor  $C_{\rm r}$  are taken from the calculation in Section III-C.

For the accurate measurement of the semiconductor losses, the steady state temperature increase of their heat sinks is measured and together with the thermal resistances of the heat sinks, which are known from calibration measurements with constant power, the semiconductor losses can be determined accurately [1]. While high precision NTCs are used for the measurement of the heat sink temperature on the LV-side, a fiber-optic measurement system (Optocon FOTEMPMK-19), which measures the temperature at the tips of up to 10 nonconductive optical fibers, is used to determine the temperature of the floating heat sinks on the MV-side. Due to the relatively small temperature increase of the MV-side heat sinks of  $\Delta \vartheta_{\rm ss} = 4 \,{\rm K}$  at full-load and a resolution of  $0.2 \,{\rm K}$  of the fiber optic temperature measurement, the measurement error is 10%. Together with an assumed deviation of the thermal resistance of 5 %, the maximum expected error (for the fullload operating point) is  $e_{\rm HS,MV} = 15\%$  (with the propagation of uncertainty theory, i.e. the geometric sum of the errors, the total error would only be 11.2%). On the LV-side, however, the resolution of the NTCs used for the temperature measurement is 0.1 K and leads together with a steady state temperature increase of 16.5K at full-load to a measurement error of 1.2%. With an assumed deviation of the thermal resistance of 5%, the worst case error of the LV-side semiconductor loss measurement is  $e_{\mathrm{HS,LV}} = 6.2\,\%$  (or  $5.1\,\%$  when the propagation of uncertainty theory is considered).

## A. Measured Waveforms

Fig. 15(a) shows the measured voltage and current waveforms at the MV-side and the LV-side transformer terminals during full-load operation (25 kW) of the DC/DC converter, together with the magnetizing current obtained by taking the difference between the MV-side and the transformed LV-side current. As can be seen, the waveforms are smooth and are free of any oscillations, which verifies the careful design of the converter. In Fig. 15(b) & (c), a magnified view of the waveforms in the vicinity of the rising and falling voltage transitions is shown. It can be seen that the MV-side switches almost the entire magnetizing current, whereby the LV-side switches the current peak generated by the different rise/fall times of the MV-side and the LV-side voltage transitions. This means that both, the MV and the LV-side are operated under ZVS conditions and since the magnetizing current is load-independent, ZVS is achieved over the complete load range without the need for adjusting any parameters such as e.g. the phase shift or the switching frequency. During the

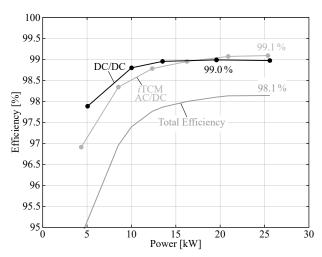

Fig. 16: Calorimetrically measured efficiency of the realized DC/DC converter. An efficiency of 99.0% is achieved above 13 kW. Together with the *i*TCM AC/DC converter presented in [1], a full-load efficiency of the complete SST-system (cf. Fig. 1) of 98.1% is reached.

measurements at different power levels, the robustness of the SRC against small changes in the switching frequency and the phase shift has been tested, especially regarding whether or not all semiconductors operate under ZVS conditions. Thereby, it has been found that the modulation is extremely robust and that ZVS is maintained even for changes in these parameters of up to  $\pm 10$  %. Comparing the measured waveforms in Fig. 15 to the simulated waveforms in Figs. 2 & 3, an almost perfect matching can be noticed.

## **B.** Efficiency Measurements

One of the most important key features of a power electronic converter is its efficiency, since the related energy losses are closely coupled to the operating costs of the converter during its lifetime. Therefore, the efficiency of the DC/DC converter is characterized for different loads between 5 kW and 25.6 kW. The calorimetrically measured efficiency curve is shown in Fig. 16. As can be seen, an efficiency of 99.0% in the power range between 13 kW and 25 kW is achieved. This means that, in contrast to similar converters [21], [39], [40], the realized DC/DC converter not only achieves three times less (relative) full-load losses, but is also well suited for partial load operation, e.g. in a redundant system, where two converters in parallel supply a critical load and are therefore operated at 50% of their rated power [41]. Furthermore, in Fig. 16, also the efficiency curves of the *i*TCM PFC AC/DC converter described in [1] and of the complete SST are shown. Together with the full-load efficiency of 99.1% of the AC/DC converter, the full-load efficiency of the 3.8 kV AC to 400 V DC SST reaches a value of 98.1%. With the given accuracy of the individual calorimetric measurements, the accuracy of the total DC/DC efficiency is  $\pm 0.08$  %, i.e. the efficiency is between 98.92% and 99.08%.

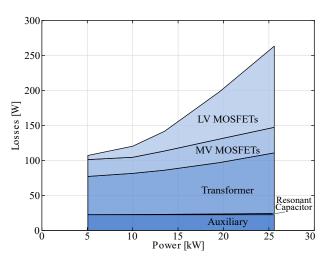

For a deeper analysis of the individual loss components of the DC/DC converter, **Fig. 17** shows the calorimetrically measured loss distribution. As can be seen, the LV-side MOS-FETs and the transformer are responsible for the largest share

Fig. 17: Measured loss distribution of the DC/DC converter's main components over the power range from  $5 \, kW$  to  $25.6 \, kW$ .

of the losses, whereby the MV-side MOSFETs, the auxiliary supply power, and the resonance capacitor losses account for only a minor loss contribution. Whereas the transformer losses cannot be improved significantly any more (due to the given material properties), the LV-side MOSFET losses of 116 W (which match very well with the calculated losses of 113.8 W) could easily be decreased by a factor of two by replacing the 2nd generation  $1200 \,\mathrm{V}, \, 25 \,\mathrm{m}\Omega$  SiC MOSFETs with the latest 3rd generation 900 V,  $11.5 \text{ m}\Omega$  SiC MOSFETs. However, even then the LV-side MOSFET conduction losses would still be significantly higher compared to the MV-side MOSFET conduction losses. To obtain equal conduction losses in both, the MV and the LV-side MOSFETs, the following conditions would have to be fulfilled, whereby the factor of two arises from the half-bridge/full-bridge configuration (magnetizing current neglected):

$$2R_{\rm DS,on,LV} \cdot \left(\frac{P}{U_{\rm DC,LV}}\right)^2 = R_{\rm DS,on,MV} \cdot \left(\frac{2P}{U_{\rm DC,MV}}\right)^2,$$

(5)

$$R_{\rm DS,on,LV} = 2R_{\rm DS,on,MV} \cdot \left(\frac{U_{\rm DC,LV}}{U_{\rm DC,MV}}\right)^2 = \frac{R_{\rm DS,on,MV}}{153}.$$

(6)

Consequently, based on an MV-side on-state resistance of  $R_{\rm DS,on,MV} = 400 \,\mathrm{m}\Omega$ , the LV-side on-state resistance would have to be  $R_{\rm DS,on,LV} = 2.6 \,\mathrm{m}\Omega$  according to (6) for equal MV and LV-side conduction losses. Such a low on-state resistance could be achieved by using e.g. 5 parallel 900 V,  $11.5 \text{ m}\Omega$ SiC MOSFETs per switch. However the total SiC chip area on the LV-side would be 4.8 times higher than the total SiC chip area on the MV-side in this case. This underpins the extremely good performance of the 10 kV SiC MOSFET technology, or in other words, as long as the  $R_{\rm DS,on}$  does not scale better than quadratically with the blocking voltage for the same chip area (cf. (6)), the MV-MOSFETs will always outperform the LV-MOSFETs. This can be explained by the fact that the SiC MOSFET channel resistance becomes much less significant compared to the SiC bulk resistance with increasing blocking voltage, therefore the total  $R_{DS,on}$  is closer to its theoretical limit for MOSFETs with higher breakdown voltage [42].

Furthermore, comparing the measured full-load MV-side MOSFET losses of 36.5 W to the calculated losses of 47.1 W, a significant difference can be noticed. This can be explained by the antiparallel SiC JBS diode chip (CPW3-10000-Z020B) contained in the 10 kV modules. With a forward voltage threshold of 1 V and a differential resistance of  $300 \text{ m}\Omega$ , circuit simulations show that the JBS diode conducts a significant part of the load current during full-load converter operation with a power flow from the LV-side to the MV-side. This results in an equivalent  $R_{\rm DS,on}$  of  $232\,{\rm m}\Omega$  and total MVside conduction losses of 16.7 W instead of 28.8 W calculated with the  $R_{\text{DS.on,MV}}$  of  $400 \,\mathrm{m}\Omega$  of the MOSFET chip itself. Thus, together with the MV-side switching losses of  $P_{\rm sw,MV} = 18.3 \,\rm W$ , the total MV-side semiconductor losses sum up to 35 W, which is very close to the measured value. For a power flow from the MV-side to the LV-side, where the antiparallel JBS diodes do not conduct any current, conduction losses of 28.8 W would appear and would lead to a slight decrease (< 0.05%) of the converter efficiency compared to a power flow from the LV-side to the MV-side.

#### V. CONCLUSION

In this paper, a bidirectional isolated 25 kW, 48 kHz, 7 kV to 400 V DC/DC converter employing 10 kV SiC MOSFETs on the MV-side is presented. Due to its tight coupling of the input and output voltages and the ability to achieve zero voltage switching (ZVS) in all semiconductors, a series resonant converter (SRC) topology operated at resonance frequency and therefore implementing a "DC transformer" is selected. Due to the significantly higher parasitic output capacitances  $C_{OSS}$  of the 10 kV MV-side SiC MOSFETs and the consequently much slower voltage transitions compared to the LV-side, a special modulation scheme is required. A small phase shift between the MV-side and the LV-side gate control signals is introduced, which allows an active sharing of the magnetizing current between the MV and the LV-side and therefore enables ZVS on both sides.

The design of all main power components of the DC/DC converter is presented in detail with a focus on the MF MV transformer and its electrical insulation. It is highlighted that the proper selection of the insulation material is extremely important, since a material with a low dissipation factor and a high thermal conductivity is required to not cause a thermal runaway and hence the destruction of the transformer insulation material. Therefore, a thermally highly conductive silicone compound is chosen and the vacuum potting process (VPP) of the winding package is described in detail. For a deeper analysis, the distribution of the transformer losses among the core, the winding, and the insulation material is measured calorimetrically and it is found that the dielectric losses account for 9% of the total transformer losses and have to be considered in MF MV transformer designs. The transformer reaches a measured efficiency of 99.64% at  $25\,\mathrm{kW}$ transferred power.

Measurements at different power levels show that all switches are operated under ZVS and that the modulation scheme is highly robust against changes in e.g. the switching frequency and/or the phase shift. Finally, the converter efficiency is measured calorimetrically in the power range between 5 kW and 25.6 kW, achieving an efficiency of 99.0 % between 13 kW and 25.6 kW, at a power density of 3.8 kW/L( $63 \text{ W/in}^3$ , referenced to 25 kW). Due to the extremely flat efficiency curve, the realized DC/DC converter is also well suited for partial load operation. Furthermore, from the calorimetrically measured loss distribution, it can be seen that the LV-side conduction losses account for the largest part of the converter losses. Accordingly, by simply replacing the 1200 V LV-side SiC MOSFETs with latest generation 900 V SiC MOSFETs, the LV-side conduction losses could be decreased by a factor of two, resulting in a total DC/DC efficiency beyond 99.2 %.

#### ACKNOWLEDGEMENT

This research project is part of the National Research Programme Energy Turnaround (NRP 70) of the Swiss National Science Foundation (SNSF). Further information on the National Research Programme can be found at www.nrp70.ch.

Furthermore, the authors would like to thank Piotr Czyz, Daifei Zhang, and Dominik Neumayr for conducting the 1200 V SiC soft-switching loss measurements and for the construction of the LV-side full-bridge.

#### REFERENCES

- D. Rothmund, T. Guillod, D. Bortis, and J. W. Kolar, "99.1% Efficient 10kV SiC-Based Medium Voltage ZVS Bidirectional Single-Phase PFC AC/DC Stage," Special Issue of the IEEE J. Emerg. Sel. Topics Power Electron. on Resonant and Soft-Switching Techniques with Wide Bandgap Devices (Accepted for publication), 2018.

D. Rothmund, G. Ortiz, and J. W. Kolar, "SiC-Based Unidirectional

- [2] D. Rothmund, G. Ortiz, and J. W. Kolar, "SiC-Based Unidirectional Solid-State Transformer Concepts for Directly Interfacing 400V DC to Medium-Voltage AC Distribution Systems," in *Proc. Int. Telco. Energy Conf. (INTELEC)*, Vancouver, 2014.

- [3] B. Hafez, H. S. Krishnamoorthy, P. Enjeti, S. Ahmed, and I. J. Pitel, "Medium Voltage Power Distribution Architecture with Medium Frequency Isolation Transformer for Data Centers," in *Proc. IEEE Appl. Power Electron. Conf. and Expo. (APEC)*, Fort Worth, 2014, pp. 3485– 3489.

- [4] S. Zhao, Q. Li, and F. C. Lee, "High Frequency Transformer Design for Modular Power Conversion from Medium Voltage AC to 400V DC," in *Proc. IEEE Appl. Power Electron. Conf. and Expo. (APEC)*, Tampa, FL, USA, 2017, pp. 2894–2901.

- [5] Siemens, "Application Models for Power Distribution in Data Centers," *Planning handbook*, 2013.

- [6] N. Rasmussen, "Guidelines for Specification of Data Center Power Density," APC White Paper #120, pp. 1–21, 2005.

- [7] P. T. Krein, "Data Center Challenges and Their Power Electronics," CPSS Trans. Power Electron. and Appl., vol. 2, no. 1, pp. 39–46, 2017.

- [8] J. W. Kolar and G. Ortiz, "Solid-State-Transformers: Key Components of Future Traction and Smart Grid Systems," in *Proc. Int. Power Electron. Conf. (IPEC-ECCE Asia)*, Hiroshima, 2014.

- [9] Y. Kashihara, Y. Nemoto, W. Qichen, S. Fujita, R. Yamada, and Y. Okuma, "An Isolated Medium-Voltage AC/DC Power Supply Based on Multi-Cell Converter Topology," in *Proc. IEEE Appl. Power Electron. Conf. and Expo. (APEC)*, 2017, pp. 2187–2192.

- [10] J. E. Huber and J. W. Kolar, "Optimum Number of Cascaded Cells for High-Power Medium-Voltage AC-DC Converters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 1, pp. 213–232, 2017.

- [11] S. Srdic, C. Zhang, X. Liang, W. Yu, and S. Lukic, "A SiC-based Power Converter Module for Medium-Voltage Fast Charger for Plug-in Electric Vehicles," in *Proc. IEEE Appl. Power Electron. Conf. and Expo. (APEC)*, Long Beach, CA, USA, 2016, pp. 2714–2719.

- [12] S. Srdic, X. Liang, C. Zhang, W. Yu, and S. Lukic, "A SiC-Based High-Performance Medium-Voltage Fast Charger for Plug-In Electric Vehicles," *Proc. IEEE Energy Conv. Congress and Expo. (ECCE)*, pp. 1–6, 2016.

- [13] T. Jimichi, M. Kaymak, and R. W. De Doncker, "Design and Loss Analysis of a Medium-Voltage DC-DC Converter Intended for Offshoe Wind Farms," in *Proc. Int. Conf. Renew. Energy Research and Appl.*, Birmingham, 2016, pp. 137–142.

- [14] Y. K. Tran and D. Dujic, "A Multiport Medium Voltage Isolated DC-DC Converter," in *Proc. Annual Conf. of the IEEE Ind. Electron. Society* (*IECON*), Florence, Italy, 2016, pp. 6983–6988.

- [15] M. Stojadinovic and J. Biela, "Modelling and Design of a Medium Frequency Transformer for High Power DC-DC Converters," in *Proc. Int. Power Electron. Conf. (IPEC-ECCE Asia)*, Niigata, Japan, 2018, pp. 1103–1110.

- [16] D. Rothmund, D. Bortis, and J. W. Kolar, "Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10kV SiC MOSFETs and Diodes," *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 5240–5250, 2018.

- [17] A. N. Lemmon and R. C. Graves, "Comprehensive Characterization of 10-kV Silicon Carbide Half-Bridge Modules," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 4, pp. 1462–1473, 2016.

[18] D. Rothmund, D. Bortis, and J. W. Kolar, "Accurate Transient Calori-

- [18] D. Rothmund, D. Bortis, and J. W. Kolar, "Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10kV SiC MOSFETs," in *Proc. Int. Symposium on Power Electron. for Distributed Generation Systems (PEDG)*, Vancouver, 2016.

- [19] K. Vechalapu, S. Bhattacharya, E. Van Brunt, S. H. Ryu, D. Grider, and J. W. Palmour, "Comparative Evaluation of 15-kV SiC MOSFET and 15-kV SiC IGBT for Medium-Voltage Converter Under the Same dv/dt Conditions," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 1, pp. 469–489, 2017.

- [20] A. N. Lemmon, R. C. Graves, R. L. Kini, M. R. Hontz, and R. Khanna, "Characterization and Modeling of 10-kV Silicon Carbide Modules for Naval Applications," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 1, pp. 309–322, 2017.

- [21] Q. Zhu, L. Wang, L. Zhang, and A. Q. Huang, "A 10 kV DC Transformer (DCX) Based on Current Fed SRC and 15 kV SiC MOSFETs," in *Proc. IEEE Appl. Power Electron. Conf. and Expo. (APEC)*, San Antonio, USA, 2018, pp. 149–155.

- [22] J. E. Huber, J. Miniböck, and J. W. Kolar, "Generic Derivation of Dynamic Model for Half-Cycle DCM Series Resonant Converters," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 4–7, 2018.

- [23] T. Guillod, R. Färber, F. Krismer, C. M. Franck, and J. W. Kolar, "Computation and Analysis of Dielectric Losses in MV Power Electronic Converter Insulation," in *Proc. IEEE Energy Conv. Congress and Expo.* (ECCE USA), Milwaukee, USA, 2016, pp. 1–8.

- [24] D. Rothmund, G. Ortiz, T. Guillod, and J. W. Kolar, "10kV SiC-Based Isolated DC-DC Converter for Medium Voltage-Connected Solid-State Transformers," in *Proc. IEEE Appl. Power Electronics Conf. (APEC)*, Charlotte, USA, 2015.

- [25] IEC, "International Standard IEC 60950-1," 2005.

- [26] D. Rothmund, D. Bortis, and J. W. Kolar, "Highly Compact Isolated Gate Driver with Ultrafast Overcurrent Protection for 10kV SiC MOSFETs," Special Issue of the CPSS Trans. Power Electron. and Appl. on Appl. of Wide Bandgap Devices (under review), 2018.

- [27] M. Guacci, D. Bortis, and J. W. Kolar, "On-State Voltage Measurement of Fast Switching Power Semiconductors," CPSS Trans. Power Electron. and Appl. (Accepted for Publication), 2018.

- [28] A. Tüysüz, R. Bosshard, and J. W. Kolar, "Performance Comparison of a GaN GIT and a Si IGBT for High-Speed Drive Applications," in *Proc. Int. Power Electron. Conf. (IPEC-ECCE Asia)*, Hiroshima, 2014, pp. 1904–1911.

- [29] L. Zhu, A. Taylor, G. Liu, and K. H. Bai, "A Multiple-Phase-Shift Control for A SiC-Based EV Charger To Optimize the Light-load Efficiency, Current Stress and Power Quality," *IEEE J. Emerg. Sel. Topics Power Electron. (Early Access)*, 2018.

- [30] S. Luo and F. Wu, "Hybrid Modulation Strategy for IGBT Based Isolated Dual Active Bridge DC-DC Converter," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 6, no. 3, pp. 1336–1344, 2018.

- [31] D. Rothmund, J. E. Huber, and J. W. Kolar, "Operating Behavior and Design of the Half-Cycle Discontinuous-Conduction-Mode Series-Resonant-Converter with Small DC Link Capacitors," in *Proc. IEEE Workshop on Control and Model. of Power Electron. (COMPEL)*, Salt Lake City, 2013.

- [32] R. Sullivan, "Optimal Choice for Number of Strands in a Litz-Wire Transformer Winding," *IEEE Trans. Power Electron.*, vol. 14, no. 2, pp. 283–291, 1997.

- [33] D. Dujic and M. Mogorovic, "High Power MFT Design Optimization," *Tutorial at the IEEE Int. Conf. on Ind. Tech. (ICIT)*, 2018.

- [34] M. Leibl, G. Ortiz, and J. W. Kolar, "Design and Experimental Analysis of a Medium-Frequency Transformer for Solid-State Transformer

Applications," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, no. 1, pp. 110–123, 2017.

- [35] A. F. Hoke and C. R. Sullivan, "An Improved Two-Dimensional Numerical Modeling Method for E-Core Transformers," in *Proc. IEEE Appl. Power Electron. Conf. and Expo. (APEC)*, Dallas, USA, 2002, pp. 151– 157.

- [36] K. Venkatachalani, C. R. Sullivan, T. Abdallah, and H. Tacca, "Accurate Prediction of Ferrite Core Loss with Nonsinusoidal Waveforms Using Only Steinmetz Parameters," in *Proc. IEEE Workshop on Computers in Power Electron.*, 2002, pp. 36–41.

- [37] Quantum Silicones, "Addition Cure Silicones Guide: Identifying Chemicals that Cause Inhibition."

- [38] D. Christen, U. Badstuebner, J. Biela, and J. W. Kolar, "Calorimetric Power Loss Measurement for Highly Efficient Converters," in *Proc. Int. Power Electron. Conf. (IPEC-ECCE Asia)*, Sapporo, Japan, 2010, pp. 1438–1445.

- [39] L. Wang, Q. Zhu, W. Yu, and A. Q. Huang, "A Medium-Voltage Medium-Frequency Isolated DC-DC Converter Based on 15-kV SiC MOSFETs," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 5, no. 1, pp. 100–109, 2017.

- [40] S. Baek and S. Bhattacharya, "Analytical Modeling and Implementation of a Coaxially Wound Transformer with Integrated Filter Inductance for Isolated Soft-Switching DC-DC Converters," *IEEE Trans. on Ind. Electron.*, vol. 65, no. 3, pp. 2245–2255, 2018.

- [41] W. Zhang, D. Xu, and H. Wang, "Fault Analysis and Fault-Tolerant Design for Parallel Redundant Inverter Systems," *IEEE J. Emerg. Sel. Topics Power Electron. (Early Access)*, 2018.

- [42] J. W. Palmour, L. Cheng, V. Pala, E. V. Brunt, D. J. Lichtenwalner, G. Y. Wang, J. Richmond, M. O'Loughlin, S. Ryu, S. T. Allen, A. A. Burk, and C. Scozzie, "Silicon Carbide Power MOSFETs: Breakthrough Performance from 900V up to 15kV," in *Proc. Int. Symp. on Power Semicond. Devices and ICs (ISPSD)*, Waikoloa, Hawaii, 2014, pp. 79– 82.