© 2020 IEEE

Proceedings of the 46th Annual Conference of the IEEE Industrial Electronics Society (IECON 2020), Singapore, October 18-21, 2020

# Three-Phase Bidirectional Ultra-Wide Output Voltage Range Current DC-Link AC/DC Buck-Boost Converter

D. Zhang, M. Guacci, J. W. Kolar, J. Everts

Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

## Three-Phase Bidirectional Ultra-Wide Output Voltage Range Current DC-Link AC/DC Buck-Boost Converter

Daifei Zhang\*, Student Member, IEEE, Mattia Guacci\*, Student Member, IEEE,

Johann W. Kolar\*, *Fellow, IEEE*, Jordi Everts<sup>§</sup>

\*Power Electronic Systems Laboratory, ETH Zurich, Switzerland

<sup>§</sup>Prodrive Technologies B.V., Son, The Netherlands

Abstract—High power EV chargers connected to AC power distribution architectures employ a three-phase  $(3-\Phi)$  PFC rectifier front-end and a series-connected isolated DC/DC converter to cover a wide range of traction battery voltages and efficiently supply the required charging current. In this paper, the operating principle of a two-stage 3- $\Phi$  buck-boost current DC-link PFC rectifier system is first introduced. Its optimal operating modes, minimizing conduction losses, switching losses, and CM noise emissions for every DC output voltage level, are identified. Adequate modulation strategies are proposed and explained through detailed switching patterns. Importantly, the two stages of the PFC rectifier system, i.e. the 3- $\Phi$  buck-type current source rectifier input stage and the subsequent three-level boost DC/DC stage, are controlled synergetically which ensures an automatic selection and seamless transition between the optimal combinations of operating modes of both stages. Simulation results verify the operation of the described power converter for different output voltage and output power levels. Furthermore, a new common-mode (CM) filtering method, requiring a CM DClink inductor and a capacitive connection between an artificial 3- $\Phi$  neutral point and the DC output mid-point, is analyzed with the support of a derived CM equivalent circuit. Finally, a complete guideline for the design of the CM filter, based on analytical calculations of the CM voltage-time area, is presented.

Index Terms—Three-Phase Buck-Boost Current DC-Link PFC rectifier system, Three-Phase Buck-Type Current Source Rectifier, CM Equivalent Circuit, CM Filter Design.

#### I. INTRODUCTION

**T**IGH power and high efficiency on- and off-board battery  $\Pi$  chargers, which facilitate a significant reduction of the charging times of electric vehicles (EVs), are of crucial importance for the implementation of sustainable mobility concepts. Today, two types of fast (or Level 3) EV charging architectures, i.e. systems supplied from a local threephase  $(3-\Phi)$  power distribution AC-bus and, alternatively, DC-bus based systems, are discussed in literature [1].  $3-\Phi$ AC-bus based charging stations are benefiting from standard and mature AC protection and metering technologies, and are realized as cascaded converter structures, comprising an AC/DC front-end and a series-connected isolated DC/DC converter [2]. Besides ensuring  $3-\Phi$  sinusoidal input currents and galvanic isolation between the AC-bus and the EV, the employed converter system must cover a wide output voltage range to adapt to different vehicle battery voltages, e.g. to 360 V [3] and 800 V [4]. The required voltage regulation can be performed by the AC/DC front-end, or the isolated

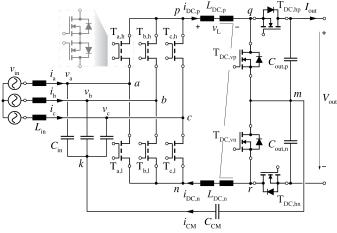

Fig. 1: Power circuit schematic of the proposed three-phase  $(3-\Phi)$  buckboost (bB) current DC-link PFC rectifier system (EV charger AC/DC frontend) employing a three-level (3-L) boost DC/DC stage. The system specifications and circuit parameters are indicated in **Tab. I**. To filter the common-mode (CM) noise at the DC output port, the artificial 3- $\Phi$  neutral point *k* and the DC mid-point *m* are connected through a CM filter capacitor *C*<sub>CM</sub>, and a CM filter inductor is employed in the current DC-link.

DC/DC converter, or shared between both converters. However, if the isolated DC/DC converter is realized as series resonant converter, which offers high efficiency but limited output voltage controllability [5], the AC/DC front-end must provide the complete voltage adaption. Moreover, according to the developing vehicle-to-grid (V2G) trend [6], EVs are planned to serve as distributed energy storage elements to support the grid operation. Therefore, future EV chargers must allow bidirectional power conversion, resulting in an according requirement for the AC/DC front-end.

In this context, the 3- $\Phi$  buck-boost (bB) current DC-link PFC rectifier system shown in **Fig. 1**, formed by a 3- $\Phi$  buck-type current source rectifier (CSR)-stage [7] and a subsequent three-level (3-L) boost DC/DC-stage, offers several advantages compared to a conventional boost-type PFC rectifier approach, i.e. a reduced number of magnetic components, direct start-up capability, and a sinusoidally varying switched voltage which potentially reduces the occurring switching losses [8]. Moreover, a 3- $\Phi$  bB current DC-link PFC rectifier system can also be applied in non-isolated on-board chargers protected by an on-board ground fault circuit interrupter [9]. There, the

TABLE I: System specifications and simulation parameters.

|                  | Description              | Value                                        |  |  |  |  |  |  |

|------------------|--------------------------|----------------------------------------------|--|--|--|--|--|--|

| Vin              | AC-bus RMS phase voltage | 230 V                                        |  |  |  |  |  |  |

| $\cos(\phi)$     | power factor             | 1.0                                          |  |  |  |  |  |  |

| $f_{ m in}$      | AC-bus frequency         | $50\mathrm{Hz}$                              |  |  |  |  |  |  |

| $f_{ m sw}$      | switching frequency      | 100 kHz (both stages)                        |  |  |  |  |  |  |

| $C_{in}$         | input capacitance        | $3 \times 10  \mu { m F}$                    |  |  |  |  |  |  |

| $L_{\rm DC,DM}$  | DM DC-link inductance    | 270 µH                                       |  |  |  |  |  |  |

| $L_{\rm DC,CM}$  | CM DC-link inductance    | $1\mathrm{mH}$                               |  |  |  |  |  |  |

| $C_{\rm CM}$     | CM filter capacitance    | 1.1μF                                        |  |  |  |  |  |  |

| $C_{\text{out}}$ | output capacitance       | $2\times50\mu\mathrm{F}$                     |  |  |  |  |  |  |

| Vout             | DC output voltage        | 200 V 400 V 1000 V                           |  |  |  |  |  |  |

| Iout             | output current           | $25\mathrm{A} 25\mathrm{A} 10\mathrm{A}$     |  |  |  |  |  |  |

| $P_{\text{out}}$ | output power             | $5\mathrm{kW}  10\mathrm{kW}  10\mathrm{kW}$ |  |  |  |  |  |  |

switches of the traction inverter and the stator coils of the motor, which are already present on-board the EV, can be used as DC/DC-stage and DC-link inductor, resulting in a compact and low-cost solution [10].

Different operating modes of the proposed  $3-\Phi$  bB current DC-link PFC rectifier system can be employed depending on the instantaneous output voltage level. In particular, in order to fully exploit the potential of this topology, i.e. to minimize conduction losses, switching losses, and CM noise emissions,

- the number of switching instants can be reduced by deactivating the DC/DC-stage when only buck functionality is required, and by applying a variable DC-link current control strategy [11], [12];

- the DC-link current can be kept at the minimum value, such that the CSR-stage is always modulated with the maximum possible modulation index;

- the CM noise can be reduced by appropriately selecting (different from conventional PWM schemes [13], [14]) the zero state of the CSR-stage.

Additionally, a new CM filtering concept, i.e. a CM DC-link inductor in combination with a capacitive connection between an artificial  $3-\Phi$  neutral point and the DC output mid-point, can be used for suppressing high-frequency CM noise at the DC output port.

These considerations motivate a comprehensive analysis of the 3- $\Phi$  bB current DC-link PFC rectifier system illustrated in **Fig. 1**, which is the subject of this paper. First, the different operating modes and the CM/DM voltage generation of the proposed converter are analyzed in **Section II** with the help of simulations and a CM/DM equivalent circuit, assuming operation in a 3- $\Phi$  400 V RMS (line-to-line) grid, a wide DC output voltage range of 200 V - 1000 V, and a rated power of 10 kW (cf. **Tab. I**). Next, **Section III** provides a guideline for the design of the main high-frequency magnetic component of the converter, i.e. the CM/DM DC-link inductor, and of the proposed CM filter. Finally, **Section IV** concludes this paper.

#### II. OPERATING BEHAVIOR

The operating principle of the proposed  $3-\Phi$  bB current DC-link AC/DC PFC rectifier system is described in this section.

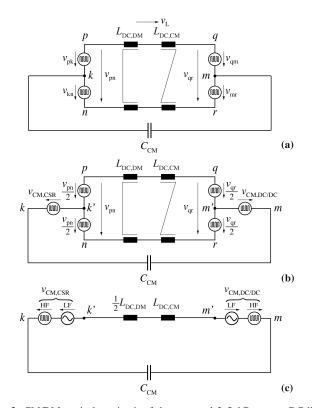

Fig. 2: CM/DM equivalent circuit of the proposed  $3-\Phi$  bB current DC-link PFC rectifier system (cf. Fig. 1). In particular, the CSR-stage and the DC/DC-stage are replaced by (a) switched voltage sources and (b) equivalent CM/DM voltage sources. In (c), only high-frequency (HF) and low-frequency (LF) CM voltage sources are shown together with the new CM filter structure under the assumption that the two windings of the CM inductor are perfectly coupled.

In particular, the different operating modes, selected depending on the output voltage level (see **Tab. II**), which minimize the occurring conduction losses, switching losses, and CM noise emissions, are analyzed with the support of simulation results.

#### A. CM/DM Equivalent Circuit

In order to provide a basis for the understanding and analysis of the CM/DM behavior of the proposed converter system, a CM/DM equivalent circuit is derived in the following. First, mixed CM/DM voltage sources are introduced, i.e. the CSRstage is replaced with two switched voltage sources  $v_{pk}$  and  $v_{kn}$ , and the DC/DC-stage is replaced with two switched voltage sources  $v_{qm}$  and  $v_{mr}$ , as shown in **Fig. 2(a)**. Hence, the fictitious CM voltage  $v_{CM0}$  of the overall converter, i.e. the potential difference between the DC mid-point *m* and the artificial 3- $\Phi$  neutral point *k* in case no capacitive connection via  $C_{CM}$  is present (open-circuit/inner CM voltage source), is calculated as

$$\begin{aligned} v_{\rm CM0} &= v_{\rm pk} - v_{\rm L} - v_{\rm qm} \\ &= v_{\rm pk} - \frac{1}{2}(v_{\rm pn} - v_{\rm qr}) - v_{\rm qm} \\ &= v_{\rm pk} - \frac{1}{2}(v_{\rm pk} - v_{\rm nk} - v_{\rm qm} + v_{\rm rm}) - v_{\rm qm} \\ &= \frac{1}{2}(v_{\rm pk} + v_{\rm nk}) - \frac{1}{2}(v_{\rm qm} + v_{\rm rm}) \\ &= v_{\rm CM,CSR} - v_{\rm CM,DC/DC}, \end{aligned}$$

(1)

where the CM voltage of the CSR-stage,  $v_{\text{CM,CSR}} = \frac{1}{2}(v_{\text{pk}} + v_{\text{nk}})$ , and the CM voltage of the DC/DC-stage,  $v_{\text{CM,DC/DC}} =$

**TABLE II:** Operating regions and corresponding operating modes of the proposed  $3-\Phi$  bB current DC-link PFC rectifier system. In particular, the modulation scheme of the CSR-stage and the input voltage of DC/DC-stage,  $v_{qr}$ , are indicated. Due to the operating range of the considered application (see **Tab. I**), *Boost-Mode #3* is not analyzed in this paper.

| $g_{\mathbf{v}} = V_{\mathbf{out}} / \hat{V}_{\mathbf{in}}$ | Operating Mode | CSR-stage          | DC/DC-stage v <sub>qr</sub>                                                                                                            |

|-------------------------------------------------------------|----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| $g_{ m v}~<rac{3}{2}$                                      | Buck           | 3/3-PWM            | Vout                                                                                                                                   |

| $\frac{3}{2} < g_{\rm v} < \sqrt{3}$                        | Transition     | 3/3-PWM<br>2/3-PWM | $V_{\text{out}}$<br>$\frac{1}{2}V_{\text{out}}$ - $V_{\text{out}}$ - $\frac{1}{2}V_{\text{out}}$                                       |

| $\sqrt{3} < g_{ m v} < 3$                                   | Boost #1       | 2/3-PWM            | $\frac{1}{2}V_{\text{out}}$ - $V_{\text{out}}$ - $\frac{1}{2}V_{\text{out}}$                                                           |

| $3 < g_{\rm v} < 2\sqrt{3}$                                 | Boost #2       | 2/3-PWM            | $\frac{\frac{1}{2}V_{\text{out}} - V_{\text{out}} - \frac{1}{2}V_{\text{out}}}{0 \text{ V} - \frac{1}{2}V_{\text{out}} - 0 \text{ V}}$ |

| $g_{\rm v} > 2\sqrt{3}$                                     | Boost #3       | 2/3-PWM            | $0 \mathrm{V}$ - $\frac{1}{2} V_{\mathrm{out}}$ - $0 \mathrm{V}$                                                                       |

$\frac{1}{2}(v_{\rm qm} + v_{\rm rm})$ , are introduced. Eq. (1) highlights how  $v_{\rm CM0}$  results from the superposition of the CM voltages of the two stages.

Next, an equivalent circuit explicitly showing the CM/DM voltage sources is obtained separating the CM voltages from the generic switched voltage sources (cf. **Fig. 2(a)** and **(b)**). Thus, the DM voltages are calculated as

$$v_{\rm pk'} = v_{\rm pk} - v_{\rm CM,CSR} = \frac{1}{2}v_{\rm pn} = v_{\rm k'n},$$

(2)

$$v_{\rm qm'} = v_{\rm qm} - v_{\rm CM,DC/DC} = \frac{1}{2} v_{\rm qr} = v_{\rm m'r}.$$

(3)

This analysis facilitates the understanding of the CM behavior, hence, the implementation of a new CM filtering concept, comprising a capacitive connection (through  $C_{\rm CM}$ ) between m and k, and a CM DC-link filter inductor  $L_{\text{DC,CM}}$ . The introduced CM filter (see Fig. 2(c)), in series with the equivalent CM voltage source  $v_{\rm CM0}$ , basically acts as a frequency dependent voltage divider, i.e. the HF components  $v_{CM,L}$  are largely applied across  $L_{\text{DC,CM}}$ , while the remaining LF components  $v_{\rm mk}$  largely appear across  $C_{\rm CM}$ , significantly minimizing the HF CM noise emissions at the DC output port, under the assumption that Cin and Cout, with relatively large capacitance values, are ignored compared to  $C_{\rm CM}$ . Furthermore, since the DC-link current  $i_{DC}$  is mainly driven by the difference between the CSR-stage output voltage  $v_{pn}$  and the DC/DC-stage input voltage  $v_{\rm ar}$ ,  $i_{\rm CM}$  has almost no influence on  $i_{\rm DC}$ , given the comparatively large impedance of  $L_{\rm DC,CM}$ .

#### B. System Simulation

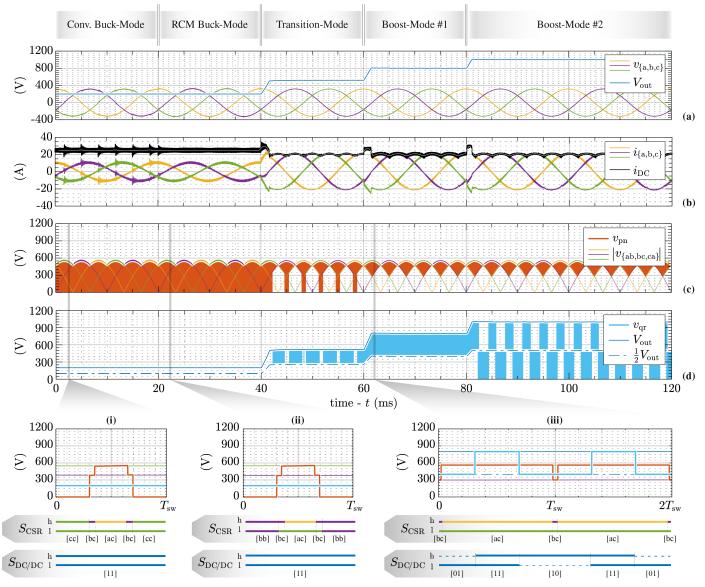

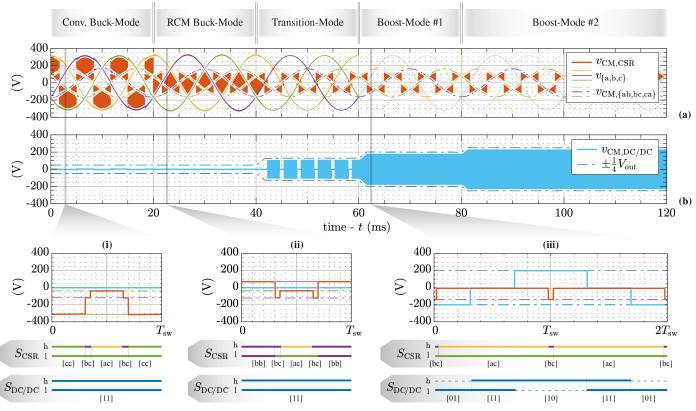

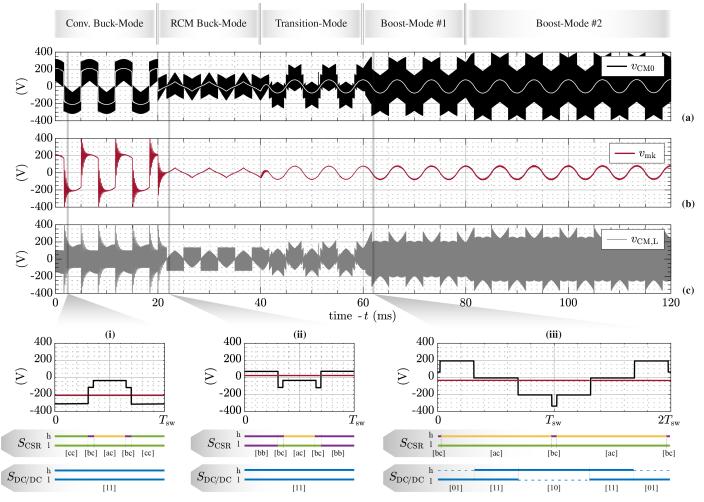

Simulated waveforms of the proposed converter are shown in **Fig. 3**, highlighting the 3- $\Phi$  mains voltages  $v_{\{a,b,c\}}$ , the output voltage  $V_{out}$ , the 3- $\Phi$  mains currents  $i_{\{a,b,c\}}$ , and the DC-link current  $i_{DC}$ , as well as the voltages  $v_{pn}$  and  $v_{qr}$ . Characteristic waveforms describing the formation of  $v_{CM,CSR}$ and  $v_{CM,DC/DC}$ , i.e. the CM behavior, are presented, subsequently, in **Fig. 4**. The CM voltage  $v_{CM0}$ , obtained as in (1), is indicated in **Fig. 5(a)**. Finally, the voltage  $v_{mk}$  across the CM filter capacitor  $C_{CM}$  and the voltage  $v_{CM,L}$  across the CM inductor  $L_{DC,CM}$  are illustrated in **Figs. 5(b)** and (c) to explain the functionality of the proposed CM filter structure.

**TABLE III:** Switching states of the CSR-stage and associated DM voltages  $v_{pn}$  and CM voltages  $v_{CM,CSR}$ .

| $S_{\rm CSR}$        | on-s             | state            | v <sub>pk</sub> | v <sub>kn</sub> | v <sub>pn</sub> | <sup>v</sup> CM,CSR                                                                     |                                                                                                         |

|----------------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| [aa]                 | T <sub>a,h</sub> | T <sub>a,l</sub> | va              | $-v_{a}$        | $0\mathrm{V}$   | $\frac{v_a+v_a}{2}$                                                                     | = <i>v</i> <sub>a</sub>                                                                                 |

| [bb]                 | T <sub>b,h</sub> | T <sub>b,l</sub> | $v_{b}$         | $-v_{b}$        | $0\mathrm{V}$   | $\frac{v_b+v_b}{2}$                                                                     | $= v_{\rm b}$                                                                                           |

| [cc]                 | T <sub>c,h</sub> | $T_{c,l}$        | $v_{\rm c}$     | $-v_{\rm c}$    | $0\mathrm{V}$   | $\frac{\frac{v_{a}+v_{a}}{2}}{\frac{v_{b}+v_{b}}{2}}$ $\frac{\frac{v_{c}+v_{c}}{2}}{2}$ | $= v_{\rm c}$                                                                                           |

| [ab]<br>[ba]         | T <sub>a,h</sub> | T <sub>b,l</sub> | va              | $-v_{b}$        | $v_{\rm ab}$    | $\frac{v_{a}+v_{b}}{2}$                                                                 | $  \label{eq:cmasses} \left. \begin{array}{l} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ |

| [ba]                 | T <sub>b,h</sub> | T <sub>a,l</sub> | $v_{b}$         | $-v_{a}$        | $-v_{\rm ab}$   | $\frac{v_b+v_a}{2}$                                                                     | $\int - v_{CM,ab}$                                                                                      |

| [bc]                 | T <sub>b,h</sub> | T <sub>c,l</sub> | $v_{b}$         | $-v_{\rm c}$    | $v_{\rm bc}$    | $\frac{v_{b}+v_{c}}{2}$                                                                 | ]                                                                                                       |

| [cb]                 | T <sub>c,h</sub> | T <sub>b,l</sub> | $v_{\rm c}$     | $-v_{b}$        | $-v_{bc}$       | $\frac{v_{\rm c}+v_{\rm b}}{2}$                                                         | $\int - v_{CM,bc}$                                                                                      |

| [ca]                 | T <sub>c,h</sub> | T <sub>a,l</sub> | $v_{\rm c}$     | $-v_{a}$        | $v_{ca}$        | $\frac{v_{\rm c}+v_{\rm a}}{2}$                                                         | ]                                                                                                       |

| [cb]<br>[ca]<br>[ac] | T <sub>a,h</sub> | T <sub>c,l</sub> | va              | $-v_{\rm c}$    | $-v_{ca}$       | $\frac{v_{a}+v_{c}}{2}$                                                                 | $\int = v_{\rm CM,ca}$                                                                                  |

**TABLE IV:** Switching states of the DC/DC-stage and associated DM voltages  $v_{qr}$  and CM voltages  $v_{CM,DC/DC}$ .

| $S_{\mathrm{DC/DC}}$ | T <sub>DC,hp</sub> | T <sub>DC,vp</sub> | T <sub>DC,vn</sub> | T <sub>DC,hn</sub> | vqr                         | VCM,DC/DC                                                      |

|----------------------|--------------------|--------------------|--------------------|--------------------|-----------------------------|----------------------------------------------------------------|

| [00]                 | 0                  | 1                  | 1                  | 0                  | 0 V                         | 0 V                                                            |

| [10]                 | 1                  | 0                  | 1                  | 0                  | $\frac{1}{2}V_{\text{out}}$ | $\frac{1}{4}V_{out}$                                           |

| [01]                 | 0                  | 1                  | 0                  | 1                  | $\frac{1}{2}V_{\text{out}}$ | $\frac{\frac{1}{4}V_{\text{out}}}{-\frac{1}{4}V_{\text{out}}}$ |

| [11]                 | 0                  | 1                  | 0                  | 1                  | Vout                        | 0 V                                                            |

All the zoomed plots in **Figs. 3-5** offer a detailed view of the switched voltage waveforms and of the corresponding switching patterns of the CSR-stage ( $S_{CSR}$ , see **Tab. III**), and of the DC/DC-stage ( $S_{DC/DC}$ , see **Tab. IV**). The system specifications and the considered simulation parameters are summarized in **Tab. I**.

C. Buck-Mode Operation ( $V_{\rm out} < \frac{3}{2}\hat{V}_{\rm in}$ )

In **Buck-Mode** operation, only the CSR-stage operates with 3/3-PWM (switching operation of all three bridge legs within a pulse period, [11]) to step down the 3- $\Phi$  mains voltages to a DC output voltage lower than  $\frac{3}{2}\hat{V}_{in}$ , and the two switches  $T_{DC,hp}$  and  $T_{DC,hn}$  of the DC/DC-stage are permanently on. This minimizes the overall conduction losses and avoids any switching losses in the DC/DC-stage.

Two types of 3/3-PWM, different with respect to the zero state utilized in the CSR-stage, are considered in *Buck-Mode* operation, i.e. the conventional 3/3-PWM [7] and the reduced CM (RCM) 3/3-PWM [13]. In the conventional 3/3-PWM, the phase with the maximum current is shorted during the zero state (see **Fig. 3(i)**); differently, with RCM 3/3-PWM, the phase with the minimum absolute current value is used (see **Fig. 3(ii**)). Both types of 3/3-PWM have identical DM performance, but the associated waveforms of  $v_{CM,CSR}$  are different, as shown in **Fig. 4(a)**. In fact, during the zero states,  $v_{CM,CSR}$  coincides with the phase voltage associated to the shorted bridge-legs, which differs in these two variants of 3/3-PWM (see **Tab. III**).

**Fig. 3:** Simulated DM waveforms of the proposed converter for different output voltage levels and operating modes. Corresponding CM waveforms are shown in **Fig. 4.** (a) 3- $\Phi$  mains voltages  $v_{\{a,b,c\}}$  and output voltage  $V_{\text{out}}$ ; (b) 3- $\Phi$  mains currents  $i_{\{a,b,c\}}$  and DC-link current  $i_{DC}$ ; (c) output voltage of the CSR-stage  $v_{\text{pn}}$  alternately assuming the absolute values of the line-to-line voltages  $v_{\{a,b,c,a\}}$  during the active states and 0 V during the zero state; (d) input voltage of the DC/DC-stage  $v_{\text{qr}}$  switching between 0 V and  $\frac{1}{2}V_{\text{out}}$  or  $\frac{1}{2}V_{\text{out}}$  and  $V_{\text{out}}$ . This simulation covers a wide output voltage range forcing the converter to operate in all the modes indicated on top of (a). The graphs at the bottom offer a zoomed view of the switched voltage waveforms and indicate the corresponding switching patterns of the CSR-stage ( $S_{\text{CSR}}$ ) and of the DC/DC-stage ( $S_{\text{DC/DC}}$ ).

The implementation of the mentioned CM filtering method requires the continuity of the local average value (average value over one switching period) of  $v_{\rm CM0}$ , especially at the boundary between different sectors, i.e.  $60^{\circ}$ -wide intervals of a mains period. In fact, a step change of  $v_{\rm CM0}$  excites the resonance of the CM filter and distorts the DC-link current and the 3- $\Phi$ mains currents. This phenomenon is visible in **Fig. 3(b)** for 0 < t < 20 ms, and is attributed to the CSR-stage, which employs conventional 3/3-PWM, since  $v_{\rm CM0} = v_{\rm CM,CSR}$  in **Buck-Mode** operation. RCM 3/3-PWM, instead, meets the continuity requirement, and reduces the CM noise generated by the CSR-stage (see **Fig. 5**), hence, it is preferred in the following.

#### D. Boost-Mode Operation ( $V_{\rm out} > \sqrt{3}\hat{V}_{\rm in}$ )

The boost functionality of the analyzed converter, which is achieved by operating both the CSR-stage and the DC/DCstage simultaneously, is required when  $V_{\text{out}} > \sqrt{3}\hat{V}_{\text{in}}$ . Here, the CSR-stage operates with 2/3-PWM (only two out of three phases are switched in a switching period, as shown in **Fig. 3(iii)**) to reduce the switching losses, and with the maximum modulation index to reduce  $i_{\text{DC}}$ , and thus, the conduction losses of the whole converter [11] and [12]. Accordingly,  $i_{\text{DC}}$  is controlled to a specific profile with six times mains frequency variation (see **Fig. 3(b)** for 60 ms < t < 120 ms).

Fig. 4: Simulated CM waveforms highlighting the formation of the CM voltages of the two stages for different output voltage levels and operating modes. Corresponding DM waveforms are shown in Fig. 3. (a) CM voltage generated by the CSR-stage  $v_{CM,CSR}$  alternately assuming the values of the CM voltage associated to the active states  $v_{CM,\{ab,bc,ca\}}$  and to the zero state  $v_{\{a,b,c\}}$  (see Tab. III); (b) CM voltage generated by the DC/DC-stage  $v_{CM,CDC}$  alternately assuming the values of 0 V and  $\pm \frac{1}{4}V_{out}$  (see Tab. IV). This simulation covers a wide output voltage range forcing the converter to operate in all the modes indicated on top of (a). The graphs at the bottom offer a zoomed view of the switched voltage waveforms and indicate the corresponding switching patterns of the CSR-stage ( $S_{CSR}$ ) and of the DC/DC-stage ( $S_{DC/DC}$ ).

In **Boost-Mode** operation, the waveforms of the CSR-stage (see, e.g.,  $v_{pn}$  in Fig. 3(c) and  $v_{CM,CSR}$  in Fig. 4(a)) are independent of the output voltage level, since the DC/DC-stage adjusts  $v_{qr}$  to balance the voltage-time area generated by the CSR-stage and provides the required voltage gain. The 3-L behavior of the DC/DC-stage is visible on  $v_{qr}$ , alternatively assuming the values of 0 V,  $\frac{1}{2}V_{out}$ , and  $V_{out}$ , as shown in Tab. IV. Depending on this, three sub-modes exist, i.e. **Boost-Mode #1**, #2, and #3 (see Tab. II):

1) Boost-Mode #1 Operation ( $\sqrt{3}\hat{V}_{in} < V_{out} < 3\hat{V}_{in}$ )

$\bar{v}_{pn}$  (the local average value of  $v_{pn}$ ) is always larger than  $\frac{1}{2}V_{out}$ , and  $v_{qr}$  switches between  $\frac{1}{2}V_{out}$  and  $V_{out}$ , as shown in **Fig. 3(d)** for 60 ms < t < 80 ms.

2) Boost-Mode #2 Operation  $(3\hat{V}_{in} < V_{out} < 2\sqrt{3}\hat{V}_{in})$ Due to the increased  $V_{out}$ ,  $\bar{v}_{pn}$  is alternatively larger or smaller (in each 60°-wide sector of a mains period) than  $\frac{1}{2}V_{out}$ . Hence, when  $\bar{v}_{pn} < \frac{1}{2}V_{out}$ ,  $v_{qr}$  additionally switches between 0 V and  $\frac{1}{2}V_{out}$ , as shown in **Fig. 3(d)** for 80 ms < t < 120 ms.

3) Boost-Mode #3 Operation  $(2\sqrt{3}\hat{V}_{in} < V_{out})$

$\bar{v}_{pn}$  is always smaller than  $\frac{1}{2}V_{out}$ , thus  $v_{qr}$  always switches between 0 V and  $\frac{1}{2}V_{out}$ .

Importantly, when  $v_{qr} = \frac{1}{2}V_{out}$ , either  $C_{out,p}$  or  $C_{out,n}$  can be connected at the input port of the DC/DC-stage. This degree of freedom is used to balance the output mid-point m, by alternating between  $C_{out,p}$  and  $C_{out,n}$ , as shown in **Fig. 3(iii**). In this mode,  $v_{CM0}$  (see **Fig. 5(a)**) is obtained with the superposition of  $v_{CM,CSR}$  and  $v_{CM,DC/DC}$ , as described by (1).  $v_{CM,CSR}$ alternately assumes the values of the CM voltage associated to the active states  $v_{CM, \{ab, bc, ca\}}$ , as shown in **Fig. 4(a)**.  $v_{CM,DC/DC}$ , instead, depends on the actual switching pattern of the DC/DCstage (see **Fig. 4(iii**)), and features only HF components, with the main component at  $\frac{1}{2}f_{sw}$ . Hence, with an appropriate filter design, the LF components of  $v_{CM,CSR}$ .

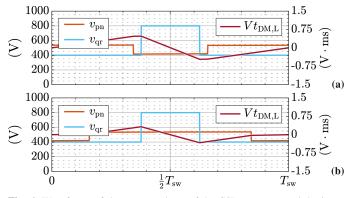

For completeness, to conclude the analysis of the **Boost-Mode** operation, the effect of the phase shift between the PWM carriers of the CSR-stage and of the DC/DC-stage is analyzed. Two scenarios, with or without phase shift, are compared in **Fig. 6**, under the assumption that one switching period starts with a switching state featuring a smaller DM voltage and the one with a larger DM voltage is centered with the carrier peak (see  $v_{qr}$  in **Fig. 6** (a)). The configuration without phase shift is preferred due to the relatively small voltage-time area  $Vt_{DM,L}$  applied across the DM DC-link inductor, which leads to a

Fig. 5: Simulated CM waveforms highlighting the formation and filtering of the CM voltage of the proposed converter for different output voltage levels and operating modes. (a) Fictitious CM voltage  $v_{CM0}$  where the white line indicates the local average value of the switched voltage waveform; (b) voltage  $v_{mk}$  across the CM capacitor  $C_{CM}$ ; (c) voltage  $v_{CM,L}$  across the CM inductor  $L_{DC,CM}$ . This simulation covers a wide output voltage range forcing the converter to operate in different modes indicated on top of (a). The graphs at the bottom offer a zoomed view of the switched voltage waveforms and indicate the corresponding switching patterns of the CSR-stage ( $S_{CSR}$ ) and of the DC/DC-stage ( $S_{DC/DC}$ ).

**Fig. 6:** Waveforms of the output voltage of the CSR-stage  $v_{pn}$  and the input voltage of the DC/DC-stage  $v_{qr}$ , and corresponding DM voltage-time area  $Vt_{DM,L}$  applied across the DM DC-link inductor (a) with and (b) without phase shift between the carriers of the CSR-stage and of the DC/DC-stage.

smaller inductor design. The carrier arrangement has a negligible influence on the CM DC-link inductor design, because, (i) the CM voltage-time area generated by the DC/DC-stage

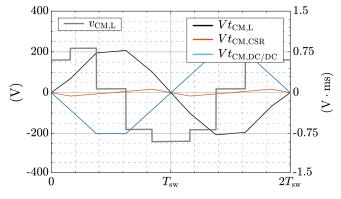

Fig. 7: Waveform of the voltage  $v_{CM,L}$  across the CM inductor  $L_{DC,CM}$  and corresponding CM voltage-time area  $Vt_{CM,L}$  obtained with the superposition of the voltage-time areas generated by the CSR-stage  $Vt_{CM,CSR}$  and by the DC/DC-stage  $Vt_{CM,DC/DC}$ .

$Vt_{CM,DC/DC}$  is much larger than the HF CM voltage-time area generated by the CSR-stage  $Vt_{CM,CSR}$ , and (*ii*) a trapezoidal shape of  $Vt_{CM,DCDC}$  at  $\frac{1}{2}f_{sw}$  is hardly influenced by  $Vt_{CM,CSR}$ ,

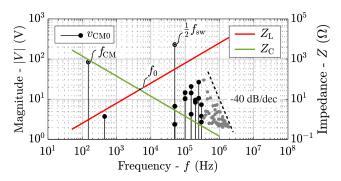

**Fig. 8:** Frequency spectrum of the fictitious CM voltage  $v_{\rm CM0}$  when the converter operates in **Boost-Mode #1** ( $V_{\rm out} = 800$  V). In particular, LF components mainly exist at  $f_{\rm CM}$  and its odd multiples, while HF components are at  $\frac{1}{2} f_{\rm sw}$  and its multiples. The amplitudes of the components decreasing with -40 dB/dec are neglected. The CM filter, formed by  $L_{\rm DC,CM}$  and  $C_{\rm CM}$ , is designed based on the selected natural frequency  $f_0$ .

i.e. a triangular shape at  $f_{sw}$ , as shown in **Fig.** 7.

### E. Transition-Mode Operation $(\frac{3}{2}\hat{V}_{in} < V_{out} < \sqrt{3}\hat{V}_{in})$

In *Transition-Mode* operation (40 ms < t < 60 ms), the converter alternatively operates in *Buck-Mode* and *Boost-Mode*, depending on the instantaneous value of  $\bar{v}_{pn}$ , i.e. if  $\bar{v}_{pn} > V_{out}$ , 3/3-PWM is applied in the CSR-stage and the DC/DC-stage is deactivated, whereas, if  $\bar{v}_{pn} < V_{out}$ , 2/3-PWM is applied in the CSR-stage and the DC/DC-stage the required output level. The seamless transition between the operating modes is realized by the synergetic control structure described in [15], which simultaneously ensures minimum switching losses and conduction losses.

#### **III. CM/DM DC-LINK INDUCTORS DESIGN**

In this section, first, a design guideline for the proposed CM filtering method is presented based on the analysis of the frequency spectrum of  $v_{\text{CM0}}$ . Furthermore, analytical formulas of the voltage-time areas applied to the CM/DM DC-link inductors are derived.

To effectively filter the HF components of the fictitious CM voltage  $v_{\rm CM0}$ , the natural frequency  $f_0$  of the CM filter should be selected between the third harmonic of the CM fundamental frequency  $3f_{\rm CM}$  (= 3 × 150 Hz, ensuring a sufficient attenuation of the LF odd harmonics of  $f_{\rm CM}$ , e.g. 3rd, 5th, 7th, etc, visible in **Fig. 5(a)** in *Buck-Mode*), and half of the switching frequency  $\frac{1}{2}f_{\rm sw}$  (=  $\frac{1}{2} \times 100$  kHz, see **Fig. 5(iii)**), as shown in **Fig. 8**. Therefore,

$$f_0 = \frac{1}{2\pi} \frac{1}{\sqrt{L_{\rm DC,CM} C_{\rm CM}}} = \sqrt{3f_{\rm CM} \cdot \frac{1}{2}f_{\rm sw}},$$

(4)

where  $f_{\rm CM}$  is three times the mains frequency  $f_{\rm in}$ , is selected. Furthermore, the CM inductance  $L_{\rm DC,CM}$  is designed to limit the current ripple  $\Delta i_{\rm CM}$  flowing through  $C_{\rm CM}$ , which is determined by

$$\Delta i_{\rm CM} = \frac{V t_{\rm CM,L}}{L_{\rm DC,CM}},\tag{5}$$

where  $Vt_{CM,L}$  is the voltage-time area applied to the CM DClink inductor. In case a CM/DM integrated DC-link inductor structure would be employed, the interactions between the

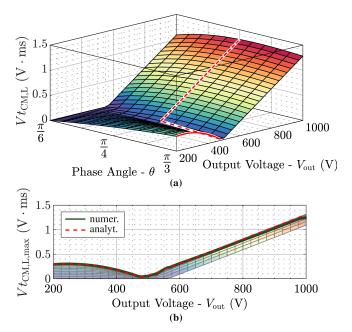

Fig. 9: (a) CM voltage-time area  $Vt_{CM,L}$  over half of one  $60^{\circ}$ -wide sector (angle  $\theta$ ) defined by the 3- $\Phi$  mains currents and in dependency of the output voltage  $V_{out}$ . In the considered sector phase c shows the minimum current value. The dotted line specifies the maximum voltage-time area  $Vt_{CM,L,max}$ for a given  $V_{out}$ . (b) Comparison of  $Vt_{CM,L,max}$  calculated numerically and obtained with the derived formulas.

CM/DM inductors, e.g. the limited winding window and the shared magnetic path, should be considered [16]. A separate CM/DM DC-link inductor design could be advantageous to fully utilize the magnetic material characteristics, as e.g. nanocrystalline materials, which features higher permeability and saturation flux density compared to ferrites, allow a downsizing of the CM inductor.

To derive analytical expressions for  $Vt_{CM,L}$ , different  $v_{CM,L}$ , waveforms are first grouped depending on their shape. Hence, analytical expressions of  $Vt_{CM,L}$  are obtained as function of the phase angle  $\theta$  within one mains period and of  $V_{out}$ , as shown in **Fig. 9(a)**. Afterwards, the value of  $\theta$  corresponding to the maximum voltage-time area for a given  $V_{out}$  is identified, and considered to calculate  $Vt_{CM,L,max}$ . In 3/3-PWM,

$$Vt_{\text{CM,L,max,3/3}} = \frac{T_{\text{sw}}V_{\text{out}}}{12\hat{V}_{\text{in}}} \cdot (3\hat{V}_{\text{in}} - 2V_{\text{out}}) \tag{6}$$

occurs at  $\theta = \pi/3$ , while in 2/3-PWM,

$$Vt_{\rm CM,L,max,2/3} = \frac{T_{\rm sw}}{8} \cdot (2V_{\rm out} - 9\sqrt{2}\hat{V}_{\rm in} + 4\sqrt{6}\hat{V}_{\rm in})$$

(7)

occurs at  $\theta = \pi/4$ .

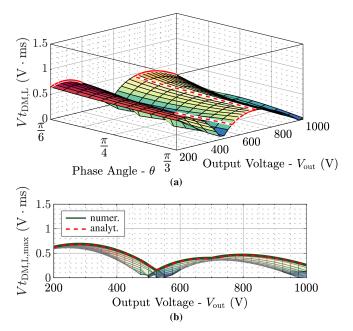

Also analytical expressions for  $Vt_{DM,L}$ , i.e. the counterpart of  $Vt_{CM,L}$  in DM (see Fig. 10(a)), are derived as function of  $\theta$  and  $V_{out}$  in the same manner, to evaluate the DC-link current ripple. Thus, in 3/3-PWM,

$$Vt_{\text{DM,L,max,3/3}} = \frac{T_{\text{sw}}V_{\text{out}}}{6\hat{V}_{\text{in}}} \cdot \left(3\hat{V}_{\text{in}} - \sqrt{3}V_{\text{out}}\right)$$

(8)

occurs at  $\theta = \pi/6$ , while in 2/3-PWM,

$$Vt_{\text{DM,L,max},2/3} = \frac{T_{\text{sw}}}{4V_{\text{out}}} \cdot (3\hat{V}_{\text{in}} - 2V_{\text{out}}) \cdot (V_{\text{out}} - 3\hat{V}_{\text{in}}) \quad (9)$$

Fig. 10: (a) DM voltage-time area  $Vt_{\text{DM,L}}$  over half of one  $60^{\circ}$ -wide sector (angle  $\theta$ ) defined by the 3- $\Phi$  mains currents and in dependency of the output voltage  $V_{\text{out}}$ . In the considered sector, phase *c* shows the minimum current value. The dotted line specifies the maximum voltage-time area  $Vt_{\text{DM,L,max}}$  for a given  $V_{\text{out}}$ . (b) Comparison of  $Vt_{\text{DM,L,max}}$  calculated numerically and obtained with the derived formulas.

is valid for

$$\theta = \pi/3$$

if  $V_{\text{out}} < \frac{3}{\sqrt{2}}V_{\text{in}}$ , and

$Vt_{\text{DM,L,max,2/3}} = \frac{T_{\text{sw}}}{2V_{\text{out}}} \cdot (2\sqrt{3}\hat{V}_{\text{in}} - V_{\text{out}}) \cdot (V_{\text{out}} - \sqrt{3}\hat{V}_{\text{in}})$  (10)

occurs for  $\theta = \pi/6$  if  $V_{\text{out}} > \frac{3}{\sqrt{2}}\hat{V}_{\text{in}}$ . Only the HF voltage-time area is considered here, but the DC components of the DC-link current should be included when designing the DM DC-link inductor.

For both CM and DM, the obtained analytical formulas are compared with the results of the numerical method, and their excellent accuracy is verified in **Fig. 9(b)** and **Fig. 10(b)**.

Finally, a CM DC-link inductor  $L_{DC,CM}$  of 1 mH (see **Tab. I**) is selected to limit the maximum peak CM current ripple (the maximum CM voltage-time area is identified in **Fig. 9**) to 1.5 A according to (7). The natural frequency of the CM filter is selected according to (4) as  $f_0 = 4.7$  kHz, thus,  $C_{CM} = 1.1 \,\mu\text{F}$ , resulting in a HF (at  $\frac{1}{2} f_{sw}$ ) CM voltage at the DC output mid-point of 5 V<sub>pk</sub>. The DM DC-link inductor  $L_{DC,DM}$  is designed to limit the maximum peak-to-peak DClink current ripple (see **Fig. 10**) to 25%. Considering a 20% margin,  $L_{DC,CM} = 270 \,\mu\text{H}$  is selected based on (8). The above mentioned component values are listed in **Tab. I** and have already been used for the simulations throughout the papers.

#### **IV. CONCLUSION**

The widespread adoption of EVs requires a high efficiency, reliable, and distributed battery charging infrastructure. Hence, a three-phase  $(3-\Phi)$  buck-boost current DC-link AC/DC PFC rectifier system, suitable to perform AC/DC energy conversion in fast EV charging architectures connected to a local AC power distribution system, is introduced in this paper. The pro-

posed topology ensures low conduction and switching losses as well as reduced CM noise emissions free of high-frequency components, while operating as AC/DC front-end in a wide DC output voltage range. First, the CM voltage generation is analyzed with the support of CM/DM equivalent circuits. Furthermore, optimal operating modes are proposed to reduce the required DC-link current, to avoid unnecessary switching actions, and to minimize the CM noise emissions at different output voltage levels. All the mentioned functionalities are verified by circuit simulations, focusing on the effectiveness of the presented CM filtering concept, which consists of a CM DC-link inductor in combination with a capacitive connection between the artificial  $3-\Phi$  neutral point and the DC output mid-point, and limits the CM voltage of the DC output port to a low-frequency variation. Finally, the selection of the natural frequency of the CM filter and the analytical equations of the voltage-time area applied across the CM/DM DC-link inductor are provided in order to support the filter design.

#### REFERENCES

- H. Tu, F. Feng, S. Srdic, and S. Lukic, "Extreme Fast Charging of Electric Vehicles: A Technology Overview," *IEEE Transactions on Transportation Electrification*, vol. 5, no. 4, pp. 861–878, 2019.

- [2] D. Zhang, M. Guacci, M. Haider, D. Bortis, J. W. Kolar, and J. Everts, "Three-Phase Bidirectional Buck-Boost Current DC-Link EV Battery Charger Featuring a Wide Output Voltage Range of 200 to 1000 V," in Proc. of the 12th Annual IEEE Energy Conversion Congress & Exposition (ECCE USA), Detroit, Michigan, USA, 2020.

- [3] "Tesla Model 3 Owner's Manual," Tesla, Tech. Rep., 2019.

- [4] "Porsche Taycan Models," www.porsche.com, accessed: 2019-11-13.

- [5] D. Rothmund, T. Guillod, D. Bortis, and J. W. Kolar, "99% Efficient 10 kV SiC-Based 7 kV/400 V DC-Transformer for Future Data Centers," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 7, no. 2, pp. 753–767, 2019.

- [6] C. J. Cleveland and C. Morris, Dictionary of Energy. Elsevier, 2006.

- [7] K. P. Phillips, "Current-Source Converter for AC Motor Drives," *IEEE Transactions on Industry Applications*, vol. 8, no. 6, pp. 679–683, 1972.

- [8] R. A. Torres, H. Dai, W. Lee, T. M. Jahns, and B. Sarlioglu, "Current-Source Inverters for Integrated Motor Drives Using Wide-Bandgap Power Switches," in *Proc. of the IEEE Transportation Electrification Conference and Expo (ITEC)*, Long Beach, CA, USA, 2018.

[9] C. A. Bendall and W. A. Peterson, "An EV On-Board Battery Charger,"

- [9] C. A. Bendall and W. A. Peterson, "An EV On-Board Battery Charger," in Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC), San Jose, CA, USA, 1996.

- [10] S. Loudot, B. Briane, O. Ploix, and A. Villeneuve, "Fast Charging Device for an Electric Vehicle," US Patent 2012/0286740, 2012.

- [11] M. Guacci, D. Zhang, M. Tatic, D. Bortis, J. W. Kolar, Y. Kinoshita, and I. Hidetoshi, "Three-Phase Two-Third-PWM Buck-Boost Current Source Inverter System Employing Dual-Gate Monolithic Bidirectional GaN e-FETs," CPSS Transactions on Power Electronics and Applications, vol. 4, no. 4, pp. 339–354, 2019.

- [12] Q. Lei, B. Wang, and F. Z. Peng, "Unified Space Vector PWM Control for Current Source Inverter," in *Proc. of the IEEE Energy Conversion Congress and Exposition (ECCE USA)*, Raleigh, NC, USA, 2012.

- [13] T. Friedli, M. Hartmann, and J. W. Kolar, "The Essence of Three-Phase PFC Rectifier Systems Part II," *IEEE Transactions on Power Electronics*, vol. 29, no. 2, pp. 543–560, 2014.

[14] L. Ding, Y. Li, and K. Sun, "Discontinuous Bi-Tri Logic SPWM for

- [14] L. Ding, Y. Li, and K. Sun, "Discontinuous Bi-Tri Logic SPWM for Current Source Converter with Optimized Zero-State Replacement," in *Proc. of the IEEE Applied Power Electronics Conference and Exposition* (APEC), New Orleans, LA, USA, 2020.

- [15] D. Zhang, M. Guacci, J. W. Kolar, and J. Everts, "Synergetic Control of a 3-Φ Buck-Boost Current DC Link EV Charger Considering Wide Output Range and Irregular Mains Conditions," in Proc. of the 9th IEEE International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Nanjing, China, 2020.

- [16] B. Wu, S. Rizzo, N. Zargari, and Y. Xiao, "An Integrated DC Link Choke for Elimination of Motor Common-Mode Voltage in Medium Voltage Drives," in *Proc. of the IEEE Industry Applications Conference*, Chicago, IL, USA, 2001.