#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2022/038288 A1

(43) International Publication Date 24 February 2022 (24.02.2022)

(51) International Patent Classification: *H02M 1/10* (2006.01) *H02J 7/20* (2006.01) *H02M 7/81* (2006.01)

(21) International Application Number:

PCT/EP2021/073198

(22) International Filing Date:

20 August 2021 (20.08.2021)

(25) Filing Language:

English

(26) Publication Language:

**English**

(30) Priority Data:

2026324

21 August 2020 (21.08.2020) NL

(71) Applicants: PRODRIVE TECHNOLOGIES B.V. [NL/NL]; Science Park Eindhoven 5501, 5692 EM Son en Breugel (NL). ETH ZURICH [CH/CH]; Raemistrasse 101 / ETH Transfer, 8092 Zurich (CH).

- (72) Inventors: KOLAR, Johann Walter; Forsterstrasse 75, 8044 Zürich (CH). MENZI, David; Fliederweg 4, 3400 Burgdorf (CH). EVERTS, Jordi; Prodrive Technologies B.V., Science Park Eindhoven 5501, 5692 EM Son en Breugel (NL).

- (74) Agent: AWA BENELUX; Av. Josse Goffin 158, 1082 Brussels (BE).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, IT, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, WS, ZA, ZM, ZW.

(57) **Abstract:** An electrical converter (10) comprises a plurality of AC terminals, a first and a second DC terminal, and a plurality of converter modules (11). Each of the plurality of converter modules comprises an AC node. The second DC terminal forms a common node of the plurality of converter modules. A connection between the AC nodes of the plurality of converter modules and the plurality of AC terminals is reconfigurable allowing the electrical converter to operate according to a first mode of operation converting between a first AC signal having a first plurality of phase voltages and the DC signal, in which the converter modules are grouped in first groups (101, 102, 103), and according to a second mode of operation converting between a second AC signal having a single-phase voltage and the DC signal, in which the converter modules are rearranged in second groups. The electrical converter is configured to operate multiple converter modules assigned to a same group of the first groups and the second groups in parallel.

#

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

# **Declarations under Rule 4.17:**

— of inventorship (Rule 4.17(iv))

#### **Published:**

— with international search report (Art. 21(3))

## Modular reconfigurable electrical AC/DC converter

1

#### Technical field

[0001] The present invention is related to an electrical AC/DC converter, allowing both single phase and three phase AC to DC operation. In particular, the present invention is related to such electrical converters allowing buck and boost capability.

## Background

10

15

20

25

In order to support further proliferation of Electric Vehicles (EVs), battery charger systems should allow for nominal power operation both in the case when attached to the European three-phase grid (e.g. 400 Vrms line-to-line voltage), as well as the US American split single-phase grid (e.g. 240 Vrms Vrms line-to-line voltage for a split single phase connection of 2x120 Vrms line-to-neutral voltage). Furthermore, charging systems are required to cover a wide DC output voltage range of typically 400 V – 750 V in order to allow compatibility with various EV battery nominal voltages, such that buck-boost capability is required.

[0003] A typical three-phase rectifier system can operate on the single-phase grid by attaching one phase terminal to the (first) line conductor and a second phase terminal to the neutral/second line conductor, where one phase terminal is not connected. As a result, only approximately 1/3 of the nominal output power can be provided in single-phase operation without overdimensioning of the employed components.

[0004] WO 2020/079019 discloses an AC/DC converter topology allowing both three-phase and single-phase operation. In single-phase operation, the three phases of the rectifier are operated in parallel and connected to the line conductor, while the neutral conductor is connected to a low-frequency unfolder bridge-leg. A four phase common mode choke is required to avoid core saturation in single phase operation. This topology hence allows full power conversion both in three-phase and in single-phase operation. However, this topology comprises a single-stage Power Factor Correction (PFC) rectifier, which is limited to buck or boost operation and hence requires an additional DC/DC converter stage to comply with a wide DC output voltage range.

30 **[0005]** Antivachis M. et al., Three-Phase Buck-Boost Y-Inverter with Wide DC Input Voltage Range, *Proc. of the IEEE Applied Power Electronics Conference and Exposition (APEC*), pp. 1492–1499, March 2018 discloses a phase-modular three-module Y-Inverter allowing three-phase boost and buck operation without the need for

an additional DC/DC converter stage, leading to an ultra-compact and highly efficient converter realization. However, the Y-inverter only allows for three-phase operation.

## Summary

15

20

25

30

35

[0006] It is therefore an aim of the present disclosure to provide an electrical AC/DC converter allowing both three-phase and single-phase AC/DC conversion with improved system performance compared to prior art AC/DC converters, and possibly a reduced hardware count and/or without the need of component overdimensioning. It is an aim of the present disclosure to provide an electrical converter of the above type which allows to maintain modularity in three-phase as well as single-phase operation.

[0007] According to a first aspect of the invention, there is therefore provided an electrical converter as set out in the appended claims. Electrical converters as described herein are operable for converting between an AC signal and a DC signal, and are advantageously used for rectifier operation, inverter operation, or both, i.e. for bidirectional power flow.

[8000] An electrical converter according to the present disclosure comprises a plurality of AC terminals, a first and a second DC terminal and a plurality of converter modules. Each of the plurality of converter modules comprises an AC node, a first converter stage comprising a first switch node, a second converter stage comprising a second switch node, a first inductor, and a first capacitor. The first and second switch nodes are connected to opposite terminals of the first inductor. The AC node and the second DC terminal are connected to opposite terminals of the first capacitor, such that the second DC terminal forms a common node of the first capacitors of the plurality of converter modules. A connection between the AC nodes of the plurality of converter modules and the plurality of AC terminals is reconfigurable allowing the electrical converter to operate according to a first mode of operation and according to a second mode of operation. The first mode of operation is configured to convert between a first AC signal having a first plurality  $p_1 \ge 2$  of phase voltages and the DC signal. The second mode of operation is configured to convert between a second AC signal having a singlephase voltage or a second plurality p<sub>2</sub> of phase voltages and the DC signal, such that the plurality of converter modules contributing to converting between the first AC signal and the DC signal in the first mode of operation contribute to conversion between the second AC signal and the DC signal or to an active capacitive energy storage in the second mode of operation.

[0009] Electrical converters according to the present disclosure feature a modular structure comprising a plurality of converter modules which are configured to

operate in parallel groups between the AC terminals and the DC terminals. The AC grid currents are shared amongst the converter modules allowing each converter module to be controlled individually, in a modular fashion. One advantage of electrical converters of the present invention is that the converter can be reconfigured by rearranging the groups of parallel converter modules when switching between three-phase and single-phase operation, without loss of modularity. This modular approach further allows to reduce switching losses and eliminate the need of component overdimensioning.

**[0010]** According to a further aspect of the present disclosure, there is provided an electric battery charging system, as set out in the appended claims.

[0011] According to a further aspect of the present disclosure, a method for converting between an AC signal and a DC signal is described herein. In a first mode of operation, the method comprises configuring a plurality of converter modules and convert between an AC signal having a first plurality  $p_1 \ge 2$  of phase voltages, advantageously  $p_1 \ge 3$  phase voltages and a DC signal. In a second mode of operation, the method comprises reconfiguring the plurality of converter modules and convert between an AC signal having a single phase voltage or a second plurality  $p_2$  of phase voltages and the DC signal.

[0012] Advantageously, the plurality of converter modules are at least  $p_1k$  converter modules, k being a positive integer equal to or larger than two. In the first mode of operation, the  $p_1k$  converter modules are grouped in  $p_1$  first groups to convert between a first AC signal having a first plurality  $p_1 \ge 2$  of phase voltages and the DC signal. In the second mode of operation, the  $p_1k$  converter modules are rearranged in at least two second groups. Converter modules assigned to a same group of the first groups and the second groups are operated in parallel.

## 25 Brief description of the figures

10

20

30

[0013] Aspects of the invention will now be described in more detail with reference to the appended drawings, wherein same reference numerals illustrate same features.

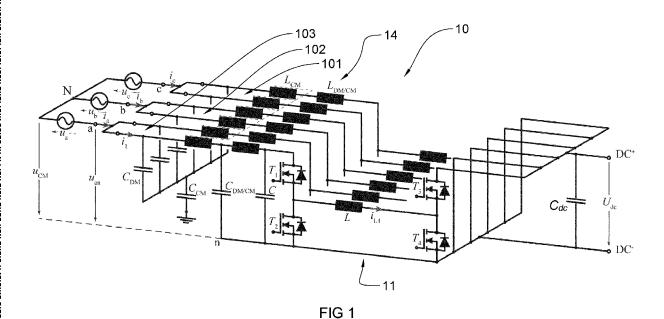

[0014] Figure 1 represents a perspective view of a six-module Y-converter (rectifier) according to the present invention connected to a three-phase AC grid with three groups of two paralleled modules connected to respective three phase terminals.

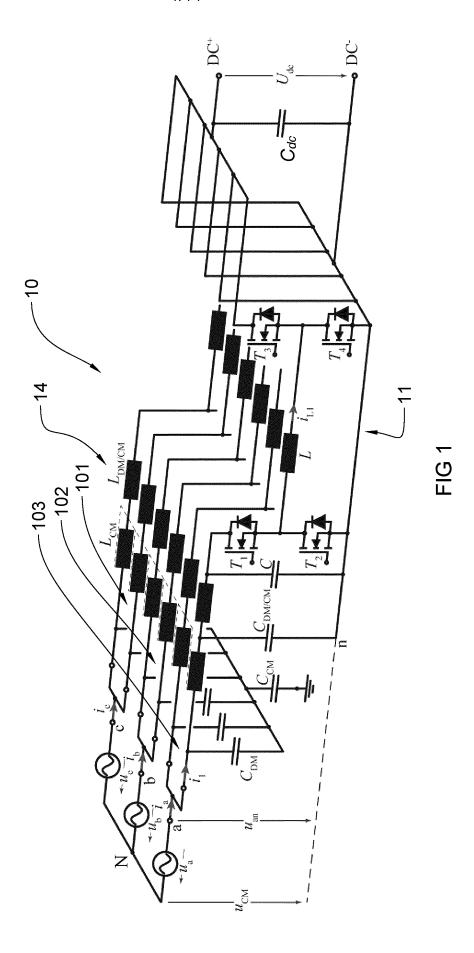

[0015] Figure 2 represents the six-module Y-converter of Fig. 1 connected to a single-phase AC grid with two groups of three paralleled modules connected to the line and neutral conductors.

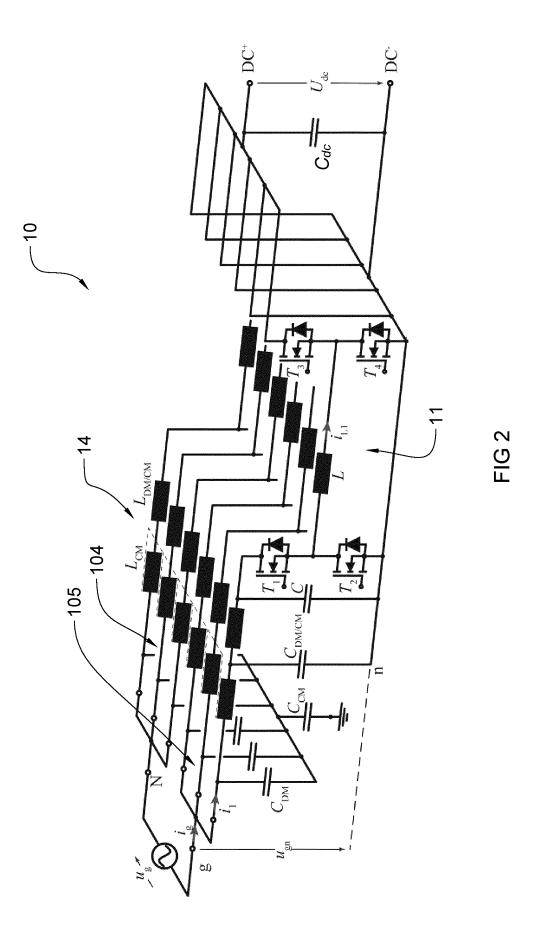

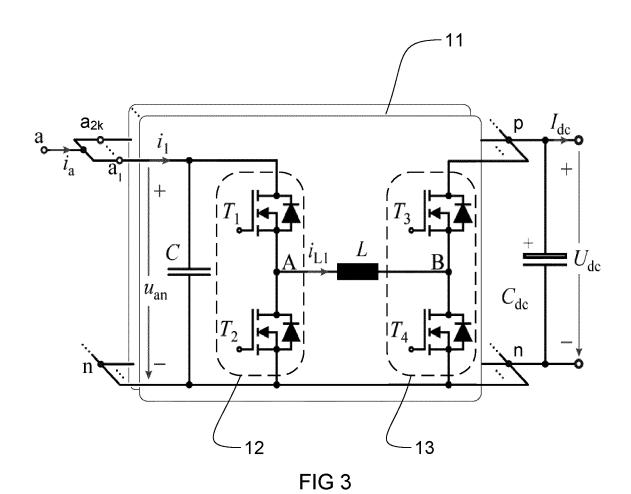

35 **[0016]** Figure 3 represents a converter module used as building block for the converter of Fig. 1 and Fig. 2.

10

15

20

30

35

[0017] Figure 4 represents the resulting duty cycles of the buck and the boost stage of the converter module of Fig. 3 depending on the instantaneous input-output voltage ratio.

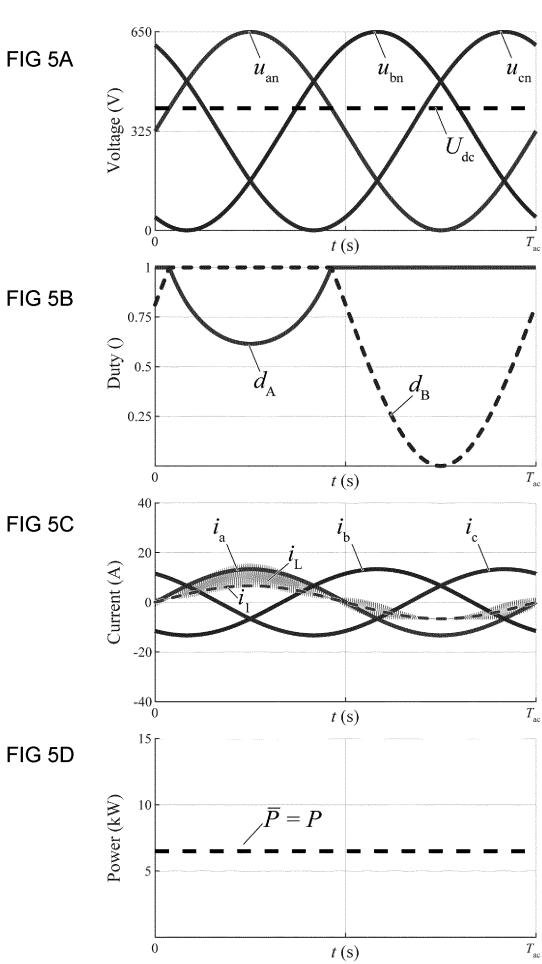

[0018] Figures 5A-D represent the main waveforms of the electrical converter of Fig. 1 in three-phase operation for an average system output power  $\bar{P}=6.6$  kW and a DC voltage of 400 V. Fig. 5A represents the AC and DC terminal voltages. Fig. 5B represents the duty cycles of the buck stage (*A*) and the boost stage (*B*) of a single converter module of Fig. 3. Fig. 5C represents the phase terminal and converter module currents when two paralleled converter modules equally share the phase current. Fig. 5D represents the system instantaneous and average power.

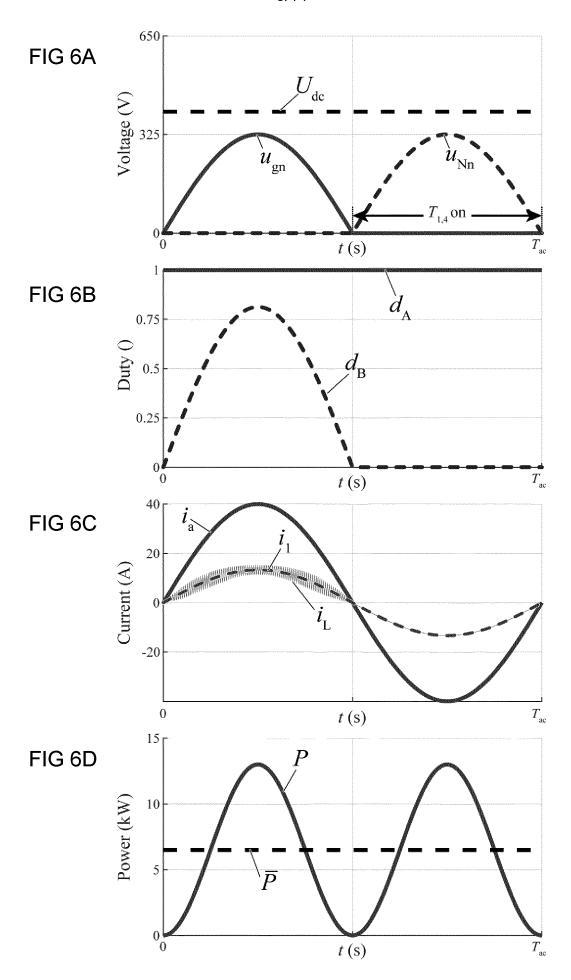

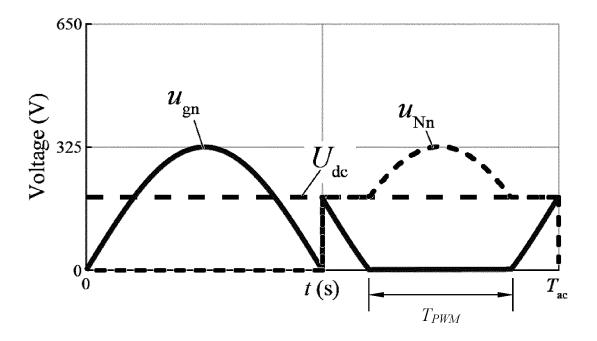

[0019] Figures 6A-D represent the main waveforms of the electrical converter of Fig. 2 in single-phase operation for an average system output power  $\bar{P}=6.6$  kW and a DC voltage of 400 V. Fig. 6A represents the AC and DC terminal voltages. Fig. 6B represents the duty cycles of the buck stage (*A*) and the boost stage (*B*) of a single converter module of Fig. 3 connected to the line terminal *g*. Fig. 6C represents the phase terminal and currents of a converter module connected to line terminal *g* when three paralleled converter modules equally share the line current. Fig. 6D represents the system instantaneous and average power.

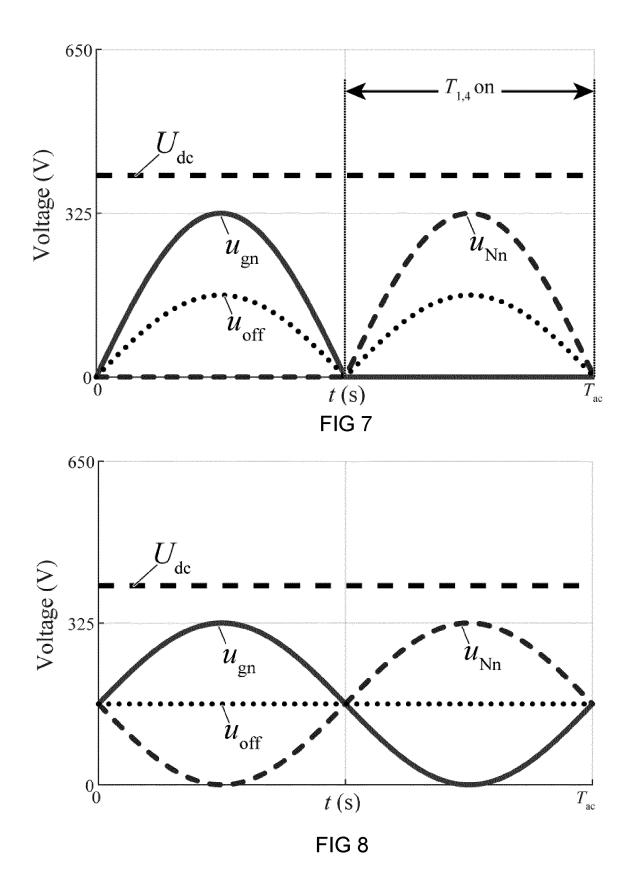

[0020] Figure 7 represents the AC and DC terminal voltage waveforms of the electrical converter of Fig. 2 in single-phase operation with DC voltage of 400 V and with a time-varying offset voltage for the AC-side terminal voltages.

[0021] Figure 8 represents the AC and DC terminal voltage waveforms of the electrical converter of Fig. 2 in single-phase operation with DC voltage of 400 V and with a minimum constant offset voltage for the AC-side terminal voltages.

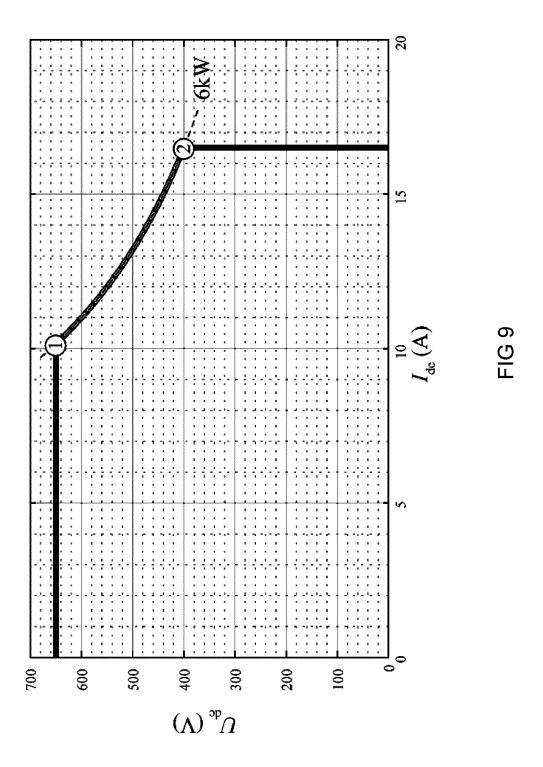

25 **[0022]** Figure 9 represents DC output voltage and current range for a constant system power of 6.6 kW within a wide DC voltage range of 400 V – 650 V.

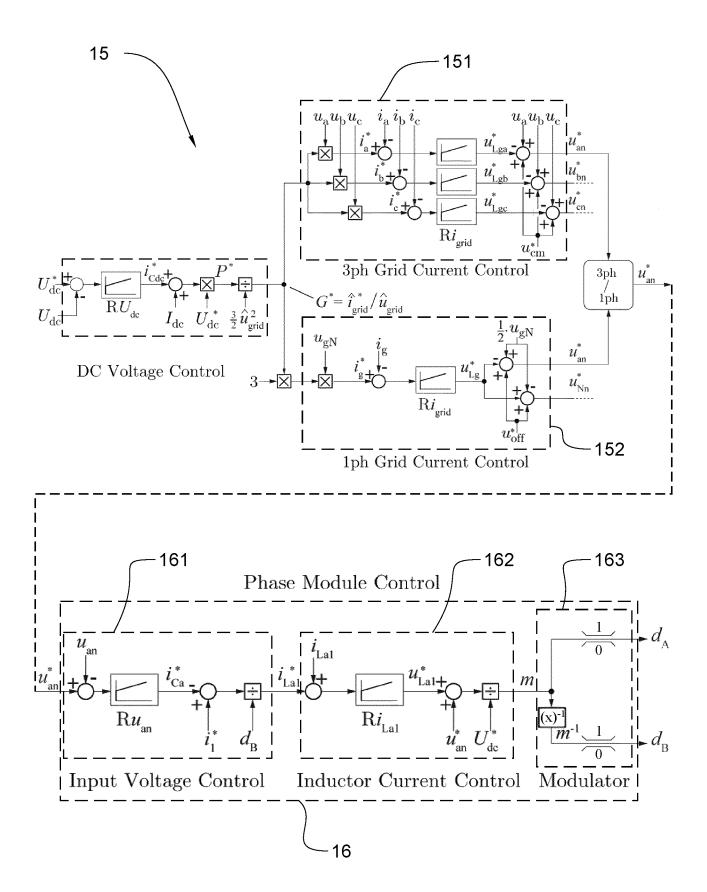

[0023] Figure 10 represents an exemplary embodiment of a control unit for operating the electrical converter of Fig. 1 and 2, both in three-phase and in single-phase operation. The control unit implements a cascaded control structure, and possible measurements are indicated.

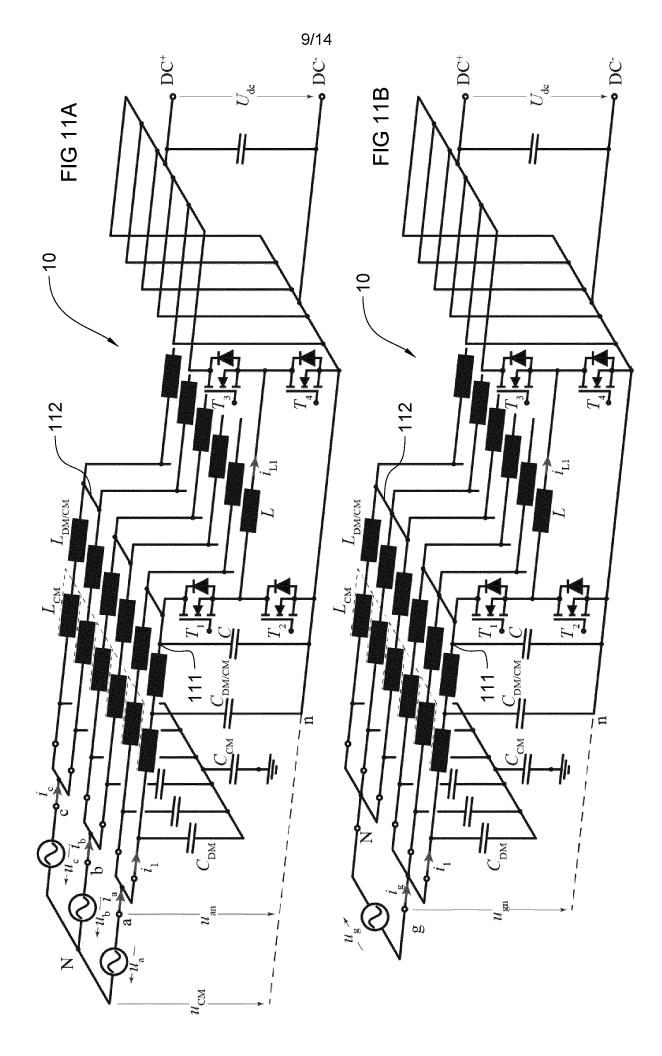

[0024] Figure 11A represents the electrical converter of Fig. 1 in which the AC-sided terminal of the input capacitors of the converter modules within each group are interconnected in three-phase operation. Figure 11 B represents the electrical converter of Fig. 2 in which the AC-sided terminal of the input capacitors of the converter modules within each group are interconnected in single-phase operation.

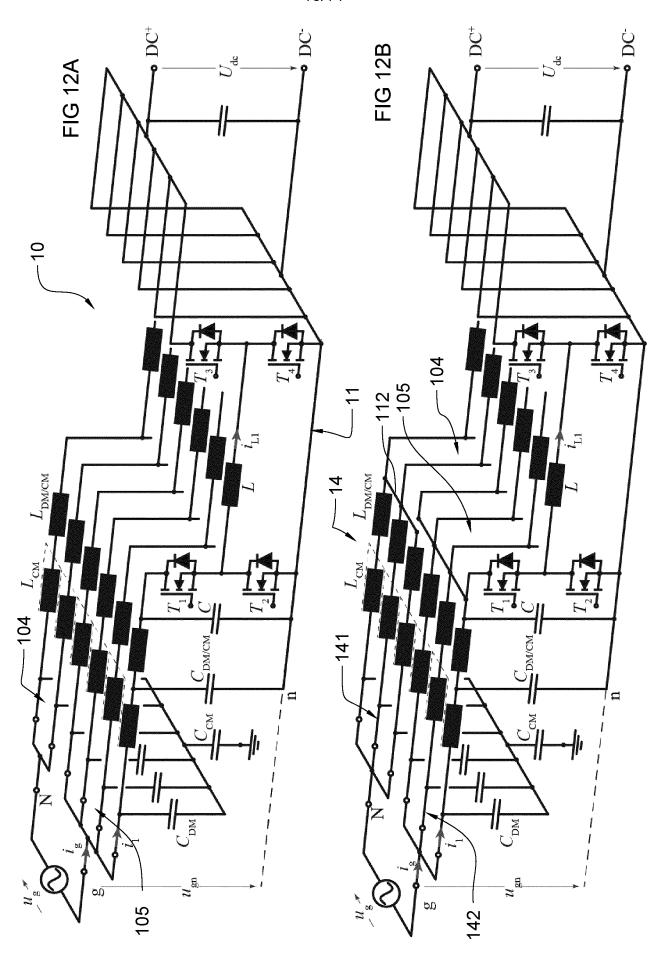

[0025] Figure 12A represents the electrical converter of Fig. 2 in which the converter modules are grouped in groups of unequal number of converter modules in single-phase operation. Figure 12B represents the electrical converter of Fig. 2 in which the groups of converter modules are configured as in Fig. 12A while the AC filter structure is configured as in Fig. 2.

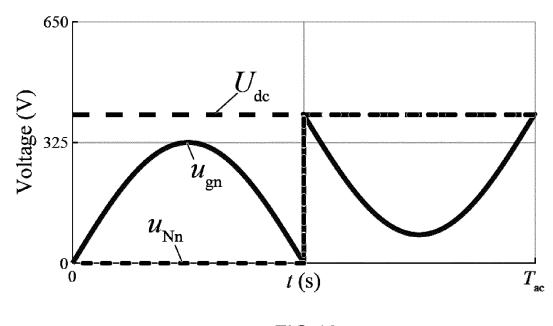

[0026] Figure 13 represents the terminal voltage waveforms for boost operation of the electrical converter of Fig. 12A in single-phase operation.

[0027] Figure 14 represents the terminal voltage waveforms for buck and boost operation of the electrical converter of Fig. 12A in single-phase operation.

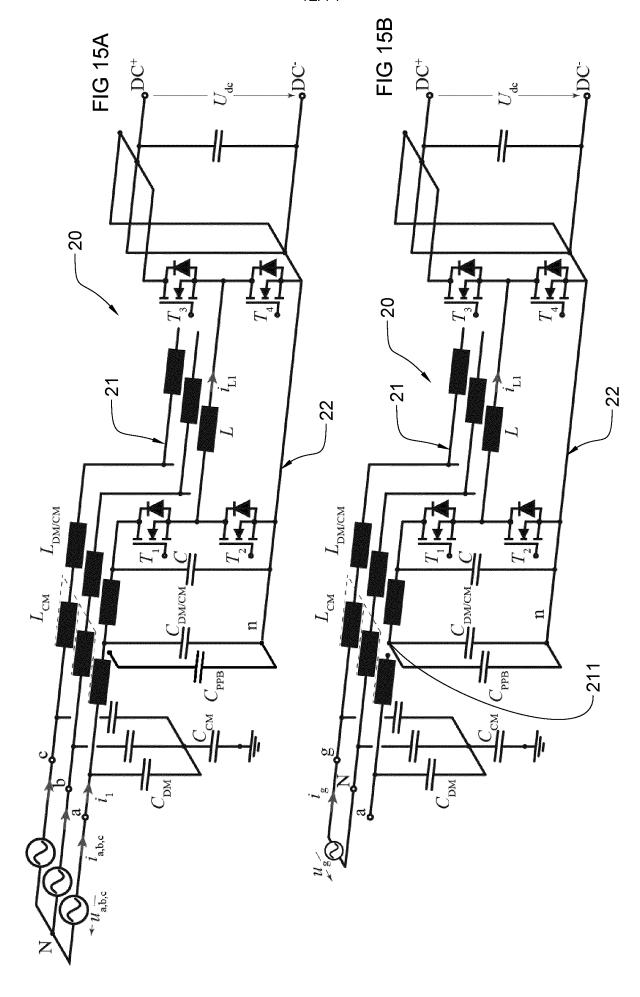

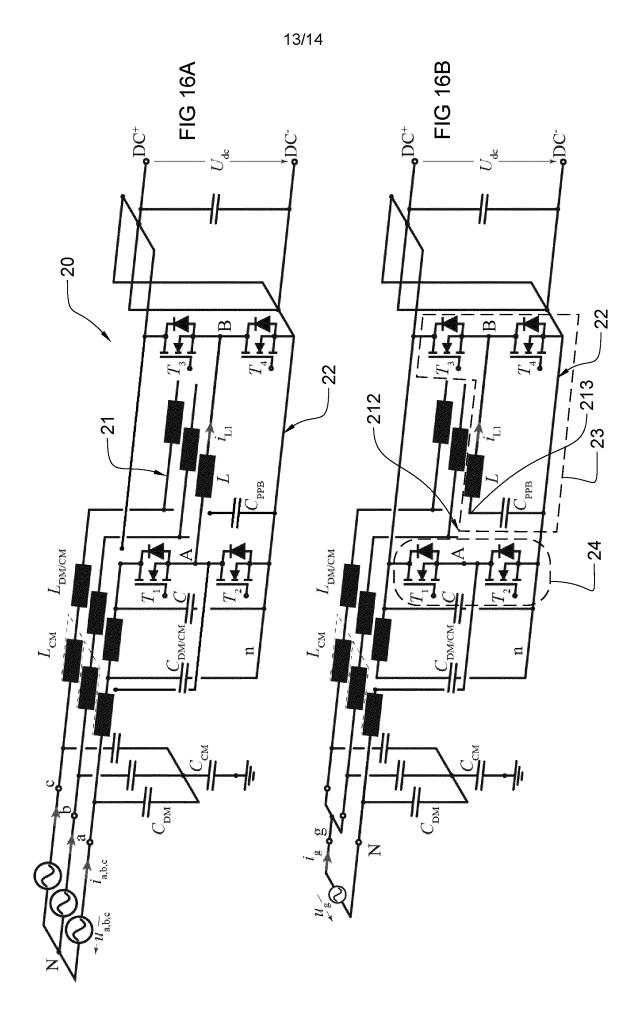

10 **[0028]** Figure 15A represents another electrical converter as described herein connected to a three-phase grid, wherein one converter module is capable of acting as a power pulsation buffer. Figure 15 B represents the electrical converter of Fig. 15A connected to a single-phase grid, with two converter modules connected to respective phase terminals and a third converter module disconnected from the grid and acting as a power pulsation buffer.

[0029] Figure 16A represents the electrical converter of Fig. 15A, with an alternative configuration of the converter module acting as a power pulsation buffer. Figure 16B represents the electrical converter of Fig. 16A connected to a single-phase grid and showing the switchable connections of the converter module acting as the power pulsation buffer.

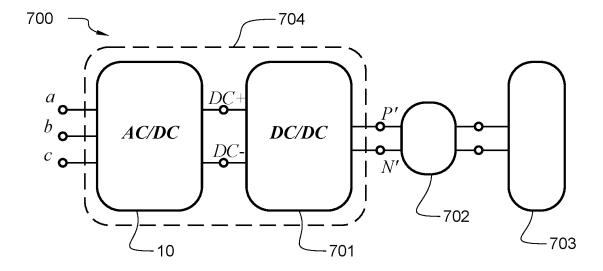

**[0030]** Figure 17 represents a battery charging system comprising an electrical converter as described herein.

## **Detailed Description**

20

25

30

35

[0031] Referring to Figs. 1 and 2, an electrical converter 10 according to aspects of the present disclosure comprises a plurality of possibly identical converter modules 11 arranged between an AC interface with phase terminals referenced as a, b, c in case of three-phase operation (Fig. 1) or g, N in case of single-phase operation (Fig. 2), with g representing the line and N the neutral connection terminals. The electrical converter 10 is hence capable of operating both in three-phase AC to DC conversion and in single-phase AC to DC conversion.

[0032] The electrical converter 10 as shown in Figs. 1 and 2 comprises six converter modules 11 which are all referenced to the negative DC link rail *n* which in turn is connected to the negative DC terminal DC<sup>-</sup>. In three-phase operation as shown in Fig. 1, two converter modules 11 are connected in parallel to each phase terminal *a*, *b*, *c*, hence forming three groups 101, 102, 103 of two parallel converter modules each. The neutral terminal N is advantageously not connected to any of the converter modules, nor

WO 2022/038288

10

15

20

25

30

35

to the negative DC terminal. The two converter modules of each group 101, 102, 103 advantageously equally share the respective phase current  $i_a$ ,  $i_b$ ,  $i_c$ , i.e. for the converter modules of group 103 connected to phase a:  $i_1 = i_a/2$ . In single-phase operation as depicted in Fig. 2, the electrical converter 10 is reconfigured such that three converter modules 11 are connected in parallel to each terminal g (grid line) and N (neutral), hence forming two groups 104, 105 of three parallel converter modules 11 each. The single-phase grid current  $i_g$  is advantageously equally shared among them and  $i_1 = i_g/3$ .

[0033] More generally, it can be stated that the electrical converter comprises  $p_1 \times k$  modules, advantageously  $p_1 \times p_2 \times k$  modules, with  $p_1$ ,  $p_2$  and k being positive integers  $(\in \mathbb{N}_1)$ , advantageously  $p_1 > p_2$ , and the electrical converter is reconfigurable between a first state of operation for converting between a first AC signal having p<sub>1</sub> phase voltages and a DC signal and between a second state of operation for converting between a second AC signal having p<sub>2</sub> phase voltages and the DC signal. In the example of Figs. 1 and 2, k=1,  $p_1=3$  and  $p_2=2$ . The reconfiguration between these two states of operation is effected by arranging the converter modules in p<sub>1</sub> groups of  $p_2k$  parallel operated converter modules in the first state of operation and in  $p_2$  groups of  $p_1k$  parallel operated converter modules in the second state of operation. The presence of p<sub>1</sub> x p<sub>2</sub> x k modules states a degree of freedom for the converter configuration, such that the converter modules are regrouped depending on whether p<sub>1</sub>- or p<sub>2</sub>-phase operation is performed, allowing in both cases utilization of all modules for power conversion. Reconfiguration can be effected manually or automatically, such as through mechanical contact switches or relays.

[0034] The converter modules of all groups (both in single-phase and three-phase operation) are parallel connected to the DC link capacitor  $C_{dc}$  which has terminals connected to the positive DC terminal DC<sup>+</sup> and to the negative DC terminal DC<sup>-</sup> respectively.

[0035] A suitable filter structure 14 can be provided at the AC side of the electrical converter in order to comply with electromagnetic interference (EMI) emission standards in both three-phase and single-phase operation. Filter structure 14 advantageously comprises a common mode (CM) filter. The common mode filter can comprise or consist of a common mode choke  $L_{CM}$  advantageously having a number of windings equal to the number of converter modules, e.g. for the six-converter module electrical converter 10,  $L_{CM}$  is a six-winding choke. In addition, or alternatively, a differential mode filter can be provided as known in the art. Hence the filter structure 14 can comprise one or more of: common mode capacitors  $C_{CM}$ , differential mode capacitors  $C_{DM}$ , differential mode inductors  $L_{DM}$  and common mode inductors  $L_{CM}$ .

[0036] One such converter module 11 is represented in isolated view in Fig. 3. Converter module 11 comprises two stages 12 and 13. The first stage 12 is connected across the AC-side capacitor C and comprises a switch node A. The AC-side capacitor C is connected between the AC node  $a_1$  and the negative DC link rail n. The first stage 12 comprises a suitable conversion circuitry, such as a half-bridge with active switches  $T_1$  and  $T_2$  respectively connecting opposite terminals of capacitor C (i.e., the AC node  $a_1$  and the negative DC-link rail n) to the switch node A. In Fig. 3, the respective branch of filter structure 14 (Fig. 1) of electrical converter 10 is omitted. However, it will be evident that any suitable filter branch may be connected between phase terminal a and the AC node  $a_1$  of the converter module.

[0037] The second stage 13 is connected between the positive DC link node p and the negative DC link rail n, and comprises a switch node B. The second stage 13 comprises a suitable conversion circuitry, such as a half-bridge with active switches  $T_3$  and  $T_4$  respectively connecting the positive DC link rail (node p) and the negative DC link rail n to the switch node B.

10

15

20

25

30

35

**[0038]** Switch nodes A and B are connected to opposite terminals of a physical inductor *L*.

[0039] The above topology allows each converter module 11 to independently perform buck-boost AC/DC conversion between an AC signal at node  $a_1$  and a DC signal between nodes p and n. As will be explained in detail below, the first stage 12 is operated when buck converter operation is required, whereas the second stage 13 is operated when boost converter operation is required. The buck and boost stages are advantageously operated in a mutually exclusive fashion, meaning that only one of the two stages 12, 13 are pulse width modulated at a point of time, while the other stage has its switch node A, B clamped to the respective AC node  $a_1$ , and the positive DC link node p, respectively. By so doing, single-stage high-frequency energy conversion can be obtained, leading to improved performance.

It will be convenient to note that the half bridges of the first stage 12 and/or the second stage 13 can be replaced with any other suitable conversion circuitry allowing to obtain single stage buck or boost AC/DC conversion. One example of a suitable conversion circuitry is a (multi-level) flying capacitor circuit such as described in Dutch patent application No. 2026176 filed on 30 July 2020, the contents of which are incorporated herein by reference.

[0041] Referring to Fig. 3, in order to achieve single-stage high-frequency energy conversion, the converter module 11 is working depending on the instantaneous

10

15

20

25

30

35

modulation depth  $m(t) = u_{an}(t)/U_{dc}$  (i.e. the input-output voltage ratio) in one of the two possible operation modes: boost operation, and buck operation.

Boost operation mode (of converter module 11 linked to AC terminal a) is selected when the respective phase input voltage  $u_{an}$  is lower than  $U_{dc}$ . The upper switch  $T_1$  of the buck bridge-leg (stage 12) is permanently turned on and hence the switch node A of stage 12 is clamped to the AC terminal voltage. The boost stage 13 is controlled through pulse width modulation (PWM) such that the voltage of switch node B has a local average value (i.e. averaged over one pulse period) equal to the AC terminal voltage. In this mode of operation, a second order input filter is advantageously formed by the phase inductor L and the AC-side capacitor C.

Buck operation mode is selected when  $u_{an}$  exceeds  $U_{dc}$ . The upper switch  $T_3$  of the boost bridge-leg (stage 13) is permanently turned on and the switch node B of the boost stage 13 is clamped to the positive DC link rail (node p). Stage 12 is now PWM operated in order to step down the AC terminal voltage, such that the voltage of switch node A has a local average value equal to the DC voltage  $U_{dc}$ . In this operation mode, solely the AC-side capacitor C is acting as an input filter and the inductor current  $i_{L1}$  shows an elevated fundamental (local average) current  $\langle i_{L1} \rangle \geq i_1$ .

[0044] The active switches  $T_1$ ,  $T_2$  of the buck stage 12 and  $T_3$ ,  $T_4$  of the boost stage 13 are advantageously semiconductor switching devices, e.g. Field Effect Transistors (FETs), in particular MOSFET devices.

**[0045]** Accordingly, the stages 12, 13 of converter module 11 are operated with time varying duty cycles  $d_A$  of the buck stage 12 and  $d_B$  of the boost stage 13 which can be defined by:

$$d_A(t) = \min\left(1, \frac{1}{m(t)}\right)$$

$d_R(t) = \min(1, m(t)).$

The duty cycles are graphically represented in Fig. 4. These duty cycles ensure the mutually exclusive high-frequency operation of buck and boost stages 12, 13 respectively. Also, as can be seen from Fig. 4, both duty cycles  $d_A$  and  $d_B$  are advantageously continuous, allowing a simple control structure, avoiding transient oscillations during the changeover of the modulation regions.

[0046] Referring again to Fig. 1, in three-phase operation, the electrical converter 10 is configured such that the six converter modules 11 are grouped in three groups 101-103 of each two converter modules operating in parallel and connected to a respective one of the three phase terminals *a*, *b*, *c*. The two converter modules 11 of each group 101-103 are identical and hence equally share the respective phase current,

15

20

25

30

35

e.g. for phase a:  $i_1 = \frac{i_a}{2}$ . In rectifier operation, the converter modules are operated independently as indicated above with half the phase current. A constant instantaneous power P, equal to the desired average output power  $\bar{P}$ , is drawn from the grid. Advantageously, the two paralleled converter modules are provided with  $360^{\circ}/2k = 180^{\circ}$  phase-shifted PWM carriers to enable interleaved operation of the active switches of the stages 12 and 13 and reduced high-frequency EMI emissions.

Referring to Figs. 5A-D, the voltages between the AC terminals and the negative DC link rail n, i.e. the voltages across the capacitor C, denoted  $u_{\rm an}$ , (and for the two other phases b, c:  $u_{\rm bn}$ , and  $u_{\rm cn}$ ) are strictly positive allowing the converter modules to be operated as DC/DC converters. Since the common-mode offset  $u_{\rm CM} = 1/3$  ( $u_{\rm an} + u_{\rm bn} + u_{\rm cn}$ ) has no corresponding current path, sinusoidal grid currents  $i_{\rm a}$ ,  $i_{\rm b}$ ,  $i_{\rm c}$  can be regulated.  $u_{\rm CM}$  is only constrained by the requirement of strictly positive terminal voltages and can be used to enable e.g. Discontinuous Pulse Width Modulation (DPWM), advantageously allowing for reducing the number of switching actions by 33% and featuring hence a substantial decrease in semiconductor switching losses. The main converter waveforms are shown in Figs. 5A-D for an average system output power  $\bar{P} = 6.6$  kW and a DC voltage of 400 V.

[0048] Referring again to Fig. 2, in single-phase operation, the electrical converter 10 is configured such that the six converter modules 11 are grouped in two groups 104, 105 of three parallel converter modules. The converter modules of group 105 are connected to the line g and those of group 104 to the neutral terminal N of the grid.

Referring to Figs. 6A-D, the voltages between the AC terminals g, N and the negative DC link rail n, i.e. the voltages across the capacitor C, denoted  $u_{\rm gn}$  and  $u_{\rm Nn}$  are strictly positive, allowing the converter modules to be operated as DC/DC converters. The input current of the converter modules connected to line g is given by  $i_1 = i_g/3$ . Advantageously, each group 104, 105 of converter modules is clamped, i.e.  $T_1$  and  $T_4$  are permanently on, during one half of the grid fundamental period  $T_{\rm ac}$  in which the respective phase has the lowest voltage, allowing for reducing the number of switching actions by 50%. The other group of 104, 105 having the highest phase voltage during the half of the grid fundamental period is operated normally as described above (i.e. boost or buck operation with PWM). The main converter waveforms are shown in Figs. 6A-D for an average system output power  $\bar{P} = 6.6$  kW and a DC voltage of 400 V. As  $u_{\rm gn}$  and  $u_{\rm Nn}$  are permanently below the DC link voltage  $U_{\rm dc} = 400$  V, all converter modules are operated in boost mode when active, as can be observed in the duty cycle waveforms displayed in Fig. 6B. Also in this mode of operation, the paralleled converter

modules can advantageously be supplied with  $360^{\circ}/3k = 120^{\circ}$  phase-shifted PWM carriers to enable interleaved operation of the boost stages and allowing reduced high-frequency EMI emissions.

In single-phase operation, a terminal voltage offset  $u_{\rm off} = (u_{\rm gn} + u_{\rm Nn})/2$  with respect to the negative DC link rail n cancels out and states a degree of freedom for the single-phase operation allowing to redistribute conduction and switching stresses among the power semiconductors of the converter modules. Fig. 7 shows a first possible terminal voltage waveform. Here the terminal voltage offset  $u_{\rm off}$  is time varying allowing each group 104 and 105 of converter modules to be PWM operated only during 50 % of the fundamental period  $T_{\rm ac}$ . Fig. 8 shows a second possible terminal voltage waveform with a constant terminal voltage offset. In the latter case, both groups 104 and 105 of converter modules need to be PWM operated continuously.

[0051] A current stress analysis was performed for the electrical converter as shown in Fig. 1 and Fig. 2, both for three-phase and for single-phase operation. To this end, two operating points ① and ② were selected as indicated in Fig. 9. Operating point ① refers to a DC voltage of 400 V and output power  $\bar{P} = 6.6$  kW. Operating point ② refers to a DC voltage of 650 V and output power  $\bar{P} = 6.6$  kW. The resulting component RMS and peak current stresses of one converter module in three-phase and single-phase operation for the two operating points ① and ② are shown in Table 1. It will be convenient to note that the line current (i.e.  $i_g$  or  $i_a$ ) is elevated by a factor of three in single-phase operation (compared to three-phase operation), but as it is shared among 3k paralleled converter modules, the line current has no direct influence on the component stresses and hence on the component dimensioning.

**[0052]** From Table 1 it can be derived that the converter module input current  $i_1$  represents the predominant loss driver in the inductive components of the EMI filter (i.e.  $L_{CM}$ ,  $L_{DM}/C_{CM}$  in Figs. 1 and 2) and is elevated by a factor of two in single-phase operation. Hence, a filter component overdimensioning would be advantageous.

For the inductor current  $i_L$  and semiconductor currents  $i_{T1}$ ,  $i_{T2}$ ,  $i_{T3}$  the stress increase for single-phase operation is less pronounced, as also the high-frequency current ripple impacts the resulting current RMS and peak values. Only semiconductor switch  $T_4$  faces a substantial current stress increase up to a factor of 2.5 given by the constant boost operation, as well as the clamping according to Fig. 6A. At the same time the clamping reduces the number of switching actions and hence the switching losses in  $T_4$ .

10

15

20

25

30

10

15

20

25

Table 1: module component RMS and peak current stresses for the two operating points ① and ② highlighted in Fig. 9 (i.e. with a DC output voltage of 400 V and 650 V) in three-phase and single-phase configuration for a grid line-to-neutral voltage of 325  $V_{pk}$ . The component designators refer to Figs. 1 and 2, where  $i_a$  and  $i_g$  correspond to the line current, in three-phase and single-phase operation, respectively and  $i_{T1}$ ,  $i_{T2}$ ,  $i_{T3}$ ,  $i_{T4}$  are the currents through the semiconductor switches  $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$ , respectively. The line current is split equally among the parallel modules within a group, where the maximally occurring stresses of each component within the considered operating points are highlighted in bold and compared for three-phase (2 paralleled converter modules) and single-phase (three paralleled converter modules) operation, respectively.

|                                  | Three-Phase      |                 |                  | Single-Phase    |                  |                 | 1phase/3phase    |                 |                                    |                                  |

|----------------------------------|------------------|-----------------|------------------|-----------------|------------------|-----------------|------------------|-----------------|------------------------------------|----------------------------------|

|                                  | 400V             | OC .            | 650V             | С               | 400V             | OC              | 650V             | C               | Max. Stres                         | ss                               |

|                                  | A <sub>rms</sub> | A <sub>pk</sub> | A <sub>rms</sub> /A <sub>rms</sub> | A <sub>pk</sub> /A <sub>pk</sub> |

| i <sub>a</sub> (i <sub>g</sub> ) | 9.4              | 13.3            | 9.4              | 13.3            | 28.3             | 40              | 28.3             | 40              | 3.0                                | 3.0                              |

| İ <sub>1</sub>                   | 4.7              | 6.7             | 4.7              | 6.7             | 9.4              | 13.3            | 9.4              | 13.3            | 2.0                                | 2.0                              |

| İL                               | 6.3              | 15.6            | 5                | 7.3             | 9.5              | 15.2            | 9.6              | 18.4            | 1.5                                | 1.2                              |

| i <sub>T1</sub>                  | 5.5              | 15.6            | 5                | 7.3             | 9.5              | 15.2            | 9.6              | 18.4            | 1.7                                | 1.2                              |

| i <sub>T2</sub>                  | 3                | 15.6            | 0                | 0               | 0                | 0               | 0                | 0               | 0.0                                | 0.0                              |

| i <sub>T3</sub>                  | 5.4              | 15.6            | 3.6              | 7.3             | 5.6              | 15.2            | 4.5              | 18.4            | 1.0                                | 1.2                              |

| İ <sub>T4</sub>                  | 3.2              | 7.1             | 3.6              | 7.3             | 7.7              | 15.2            | 8.5              | 18.4            | 2.4                                | 2.5                              |

The current stresses of  $T_4$  can be reduced by selecting a higher offset voltage  $u_{\text{off}}$  and/or by advantageously turning on  $T_2$  (with low current stresses in single-phase operation) during the clamping interval of  $T_1$  and  $T_4$  indicated in Fig. 6A, allowing current sharing between  $T_2$  and  $T_4$  and reduced overall conduction losses.

[0055] Referring to Fig. 10, the converter 10 comprises a control unit 15 configured to operate the electrical converter, both in three-phase operation and in single-phase operation. The control unit 15 can comprise individual control modules for operating the different converter modules 11 in a modular / independent fashion. One such individual control module 16 for operating a single converter module 11, e.g. one of the converter modules of group 103 linked to AC terminal *a*, is shown schematically in Fig. 10.

[0056] The control unit 15 is advantageously configured to perform power factor correction (PFC) rectifier control with a cascaded control structure as known in the art. Measurement means are advantageously provided for measuring the three-phase AC grid voltages  $u_a$ ,  $u_b$ ,  $u_c$ , single-phase AC grid voltage  $u_g$  and three-phase grid currents

5

10

15

20

25

30

35

$i_a$ ,  $i_b$ ,  $i_c$ , single-phase grid current  $i_g$  and the inductor current  $i_L$ . On the DC side, measurement means are advantageously provided for measuring the DC terminal voltage  $U_{dc}$  and advantageously the DC terminal current  $I_{dc}$ . These measurements are advantageously input to control unit 15.

[0057] In three-phase operation, current control is performed through three-phase current control block 151. Sinusoidal grid current references  $i_a^*$ ,  $i_b^*$ ,  $i_c^*$  are derived based on the DC voltage error and the measured AC voltages  $u_a$ ,  $u_b$ ,  $u_c$ . Then, the AC terminal voltage references  $u_{an}^*$ ,  $u_{bn}^*$ ,  $u_{cn}^*$  are set in order to enforce the required grid currents. These AC terminal voltage references are fed to the respective control modules 16 for operating each converter module individually.

[0058] For single-phase operation, current control is performed through single-phase current control block 152. The grid input power P is fluctuating with twice the mains frequency, and accordingly the measured DC voltage is advantageously processed with a notch filter (not shown) before comparing to its reference value. A grid current reference  $i_g^*$  elevated by a factor of 3 (compared to three-phase operation) and again in phase with the measured grid voltage  $u_{gN}$  is set in order to provide the desired average output power. Subsequently, based on the grid current error, the measured grid voltage  $u_{gN}$  and possibly the offset voltage reference  $u_{off}^*$ , the input terminal voltage references  $u_{an}^*$ ,  $u_{Nn}^*$  are derived. As stated earlier, the offset voltage reference can be set to a constant value, or a time varying value, e.g. such that the lower terminal voltage reference is equal to zero.

[0059] The underlying control of the converter modules, through control modules 16 (of which only one is shown in Fig. 10), operates independently of the selected single- or three-phase configuration, where the line current reference is advantageously shared equally among the paralleled modules for each phase, i.e.  $i_1^* = i_a^*/2$  for three-phase and  $i_1^* = i_g^*/2$  for single-phase.

[0060] The control module 16 comprises an AC voltage control block 161, an inductor current control block 162, and a modulator 163. The output signal of the inductor current control block 162 is fed into the modulator 163, generating duty cycles for the mutually exclusive operation of buck stage 12 and boost stage 13. The control signals for the active switches  $T_1$ ,  $T_2$ ,  $T_3$  and  $T_4$  are then generated using PWM from the generated duty cycles as known in the art.

[0061] Referring to Figs. 11A-B, the electrical converter 10 can be provided with additional switching means 112 (e.g. mechanical contact switches or relays) to interconnect the AC-sided terminals 111 of the AC-side capacitors C of all converter modules within one group. The interconnection allows the interleaved currents to at least

WO 2022/038288

10

20

25

30

35

partially cancel out when interleaved PWM operation between the converter modules of one group is performed, advantageously reducing the required filter attenuation to comply with EMI regulations. The interconnections between terminals 111 can be provided either for three-phase operation (Fig. 11A), for single-phase operation (Fig. 11B), or both for three-phase and single-phase operation. The interconnections 112 are advantageously switchable allowing for possibly automatic reconfiguration when reconfiguring between three-phase and single-phase operation modes.

[0062] While in the above embodiments, all groups 101-103 and 104-105 of converter modules comprised an equal number of converter modules, this need not be so, in particular for single-phase operation. Referring to Fig. 12A, it is possible to configure the electrical converter 10 in single-phase operation such that group 105 of converter modules connected to AC line terminal g comprises four converter modules 11 arranged in parallel, whereas group 104 connected to the neutral terminal N comprises only two converter modules 11. In this case, the converter modules of group 104 would be operated as unfolder circuits, i.e. merely configured to provide a return path of the line current. With unfolder operation of the converter modules of group 104, the semiconductors T<sub>1</sub> are permanently turned on and T<sub>3</sub> and T<sub>2</sub>/T<sub>4</sub> are alternatingly clamped to p and n, respectively at half the grid fundamental period. In unfolder operation, the converter modules of group 104 therefore would have elevated semiconductor conduction stresses, but practically no switching losses. Therefore fewer converter modules can be used for this purpose, e.g. two converter modules would be sufficient for this task, and the remaining (third) converter module can be additionally assigned to group 105 connected to the line terminal g. The converter modules of group 105 will be PWM operated as described above and therefore the semiconductor switches T<sub>1</sub>-T<sub>4</sub> are high-frequency (HF) operated hence facing both conduction and switching losses. With the added converter module, the four converter modules of group 105 equally share 1/4 of the grid current compared to 1/3 of the grid current for the configuration of Fig. 2. Thereby the current stresses on the semiconductors can be reduced while semiconductor utilization can be improved.

[0063] The terminal voltage waveforms for the converter configuration according to Fig. 12A in single-phase operation are shown in Fig. 13 for boost operation and Fig. 14 for buck and boost operation. Referring to Fig. 13, when the DC link voltage  $U_{dc}$  is higher than  $u_{gn}$ , the group 104 converter modules are permanently in unfolder operation. In this case,  $u_{Nn}$  is block shaped on a fundamental frequency level, while  $u_{gN}$  needs to be sinusoidal. The group 105 converter modules are hence permanently in

boost operation and can be individually controlled through the control module 16. It will be convenient to note that the voltage offset  $u_{off}$ =0.5( $u_{an}$ + $u_{Nn}$ ) is time varying.

[0064] The terminal voltage waveforms in buck operation (e.g. for extremely low DC voltages, where typically only reduced power has to be provided at the output) are shown in Fig. 14. In buck operation, the group 104 converter modules, i.e. assigned to terminal N, are operated as unfolder circuits except for a short period  $T_{PWM}$  when  $u_{Nn}$  exceeds  $U_{dc}$ . During  $T_{PWM}$ , the group 104 converter modules are PWM operated, e.g. based on the control strategy described above in relation to Fig. 10. The group 105 converter modules are advantageously clamped, i.e.  $T_1$  and  $T_4$  are permanently on.

10

15

20

25

30

35

[0065] In a yet alternative embodiment, referring to Fig. 12B, the converter module configuration of Fig. 12A for single-phase operation, i.e. two converter modules arranged in group 104 connected to N and four converter modules arranged in group 105 connected to g is kept, while the AC side filter structure 14 is equally shared between the two AC terminals g and N, i.e. in a 3-3 configuration. In other words, the AC filter 14 is connected to the AC terminals such that the windings of the differential mode and/or common mode inductors  $L_{DM/CM}$  and  $L_{CM}$  are equally shared between the terminals g and N, just like the configuration of Fig. 11B, thereby obtaining two filter groups 141 and 142 with equal number of windings (branches), while the 4/2 converter module configuration of Fig. 12A is maintained. Hence, filter group 141 is connected between terminal N and the group 104 converter modules, and filter group 142 is connected between terminal g and the group 105 converter modules. This can be obtained by suitably switching the additional switching means 112 which interconnect the AC-sided terminals 111 of the AC-side capacitors C of converter modules within one group, as shown in Fig. 12B. Advantageously, at least one of the switching means 112 should allow to disconnect a converter module from its respective AC filter branch, as shown in Fig. 12B. This allows to evenly distribute the fundamental frequency current stresses within the AC filter 14 while retaining the advantage of the 4/2 configuration of the converter modules.

In single-phase rectifier operation, a time-varying power P pulsating at twice the line frequency is drawn from the grid as shown in Fig. 6D. The output power ripple can be reduced by providing a DC link capacitor  $C_{dc}$  of appropriate size. Alternatively, an active power pulsation buffer (PPB) can be provided for use in single-phase operation, eliminating the need of a large DC link capacitor. The active PPB can comprise a buffer capacitor and a converter circuit, such as a half-bridge converter, interfacing between the DC link and the buffer capacitor. Advantageously, the converter circuit can be provided as being identical to the converter module 11. The buck-boost

capability of the converter module used as PPB advantageously allows to vary the buffer capacitor voltage in a wide range both above and below the desired DC link voltage.

[0067] Referring to Figs. 15A-B, one or more of the converter modules 21 of the electrical converter 20, e.g. converter module 22, can be provided with a respective buffer capacitor C<sub>PPB</sub> for use as PPB in single-phase operation. Converter modules 21, 22 can be identical to the converter modules 11 described hereinabove. In three-phase operation, as shown in Fig. 15A, C<sub>PPB</sub> is disconnected from the AC terminal a allowing converter module 22 to operate along with the other converter modules 21 in modular groups connected to the respective AC terminals a, b, c as described in relation to Fig. 10 1. In single-phase operation, as shown in Fig. 15 B, the converter module 22 is disconnected from the AC grid and the buffer capacitor CPPB is parallel connected to the filter capacitors C and/or C<sub>DM/CM</sub> to operate as a PPB. The voltage across C<sub>PPB</sub> can be both above and below the DC link voltage U<sub>dc</sub>. Although in Fig. 15B it is shown that the common mode choke  $L_{CM}$  is disconnected at node 211 from the buffer capacitors / converter module 22, this is not a requirement and the common mode choke can be left attached. It will be convenient to note that the buffer capacitor C<sub>PPB</sub> is optional, e.g. when the capacitors C and/or C<sub>DM/CM</sub> provide sufficient energy storage capability. The PPB converter modules reduce the minimum DC link capacitance value for single-phase operation.

Referring to Figs. 16A-B, the converter module 22 acting as PPB is modified by providing a suitable switching circuitry 212 allowing in single-phase operation to disconnect switch node B from switch node A while operably connecting the buffer capacitor  $C_{PPB}$  to switch node B. In particular, the switching circuitry 212 is configured to disconnect switch node A from the respective terminal 213 of inductor L while connecting terminal 213 to  $C_{PPB}$ . The switching circuitry 212 is advantageously further configured to connect the bridge-leg  $T_1/T_2$  across the positive and negative DC link rails p and n, while the switch node A is connected to the neutral terminal N. By so doing, converter module 22 is split such that only the boost stage 13 acts as a PPB 23 (now with a PPB voltage strictly below the DC link voltage). Advantageously, the bridge-leg  $T_1/T_2$  acts as an unfolder circuit 24, allowing to parallel the converter modules 21 parallel connected to terminal g, and which are hence equally sharing the grid current.

20

25

30

35

[0069] It will be convenient to note that the converter modules 21 and possibly 22 referenced in Figs. 15A-B and 16A-B can refer to single converter modules as the converter modules 11 described previously, or alternatively can refer to groups 101-103 and 104-105 of converter modules as described in any of the above embodiments. In a particularly advantageous embodiment, the 4/2 converter module

16

configuration as described in relation to Figs. 12A and 12B can be adapted such that one of the four group 105 converter modules 11 is used as a PPB. Hence, a configuration with three group 105 converter modules, two group 104 converter modules and one PPB module is obtained in single-phase operation, while all six converter modules 11 would be available for being assigned to groups 101-103 in three-phase operation.

**[0070]** It will be convenient to note that in both single- and three-phase operation the resulting grid currents do not necessarily need to be in phase with the respective grid voltages and the electrical converter according to aspects of the invention can also be employed in Static VAR Compensator (SVC) applications.

[0071] The electrical converter as described herein can be operated as inverter, both for three-phase and single-phase operation, with a similar control structure as described above. Furthermore, bidirectional power flow through the electrical converter is possible, allowing it to be used for power injection into the AC grid.

Referring to FIG. 17, a battery charging system 700 comprises a power supply unit 704. The power supply unit 704 is coupled on one side to the AC grid through terminals a, b, c and on the other side (at terminals P', N') to an interface 702, e.g. comprising a switch device, which allows to connect the power supply unit 704 to a battery 703. The power supply unit 704 comprises any one of the electrical converters, e.g. converter 10, as described hereinabove and can comprise a further converter stage 701, which in the present system is a DC-DC converter. The power supply unit 704, e.g. the converter stage 701, can comprise a pair of coils which are inductively coupled through air (not shown), such as in the case of wireless power transfer. Alternatively, the DC-DC converters tage 701 can comprise or consist of one or more possibly isolated DC-DC converters. In some cases, the interface 702 can comprise a plug and socket, e.g. in wired power transfer. Alternatively, the plug and socket can be provided at the input (e.g., at nodes a, b, c).

[0073] Another possible application of electrical converters according to the present disclosure is as a traction inverter of an electric motor drive system.

10

20

25

17

## **CLAIMS**

**1.** Electrical converter (10, 20) for converting between an AC signal and a DC signal, comprising:

a plurality of AC terminals (a, b, c, g, N), a first and a second DC terminal (DC<sup>+</sup>, DC<sup>-</sup>),

a plurality of converter modules (11, 21, 22), wherein each of the plurality of converter modules comprises:

an AC node (a<sub>1</sub>, 111),

10

15

20

25

30

35

node (B),

a first converter stage (12) comprising a first switch node (A), a second converter stage (13) comprising a second switch

a first inductor (L), wherein the first and second switch nodes are connected to opposite terminals of the first inductor,

a first capacitor (C), wherein the AC node  $(a_1, 111)$  and the second DC terminal (DC $^-$ ) are connected to opposite terminals of the first capacitor, such that the second DC terminal forms a common node of the first capacitors (C) of the plurality of converter modules,

wherein a connection between the AC nodes ( $a_1$ , 111) of the plurality of converter modules and the plurality of AC terminals is reconfigurable allowing the electrical converter to operate according to a first mode of operation configured to convert between a first AC signal having a first plurality  $p_1 \ge 2$  of phase voltages and the DC signal and according to a second mode of operation configured to convert between a second AC signal having a single-phase voltage or a second plurality  $p_2$  of phase voltages and the DC signal, such that the plurality of converter modules (11, 21, 22) contributing to converting between the first AC signal and the DC signal in the first mode of operation contribute to conversion between the second AC signal and the DC signal or to an active capacitive energy storage ( $C_{PPB}$ ) in the second mode of operation,

wherein the plurality of converter modules are at least  $p_1k$  converter modules, k being a positive integer equal to or larger than two, wherein in the first mode of operation, the  $p_1k$  converter modules are grouped in  $p_1$  first groups (101, 102, 103), and wherein in the second mode of operation, the  $p_1k$  converter modules are rearranged in at least two second groups (104, 105) and wherein the electrical converter is configured to operate multiple converter modules assigned to a same group of the first groups and the second groups in parallel.

**2.** Electrical converter of claim 1, wherein  $p_1 \ge 3$ .

- **3.** Electrical converter of claim 2, wherein the second AC signal has a single-phase voltage.

- 4. Electrical converter of any one of the preceding claims, wherein the first groups (101, 102, 103) have equal number of converter modules (11, 5 21).

- 5. Electrical converter of any one of the preceding claims, wherein the second groups have equal number or disparate number of converter modules (11, 21).

- 6. Electrical converter of any one of the preceding claims, wherein the second AC signal has a single-phase voltage, and wherein the second groups are two (104, 105).

- **7.** Electrical converter of any one of the preceding claims, comprising a second capacitor ( $C_{dc}$ ) connected across the first and second DC terminals, wherein the second converter stages of the plurality of converter modules are parallel connected to the second capacitor.

15

25

30

- **8.** Electrical converter of any one of the preceding claims, comprising an AC filter (14) connected between the plurality of AC terminals (a, b, c, g, N) and the AC nodes (111), wherein the AC filter comprises a common mode filter comprising a common mode choke  $(L_{CM})$ .

- 9. Electrical converter of claim 8, wherein the common mode choke ( $L_{CM}$ ) comprises a branch for each of the plurality of converter modules, wherein the branch is connected or connectable to the AC node (111) of the respective one of the plurality of converter modules.

- 10. Electrical converter of any one of the preceding claims, comprising first switching means (112) for interconnecting terminals of the first capacitors(C) at a side of the AC node (111) in a reconfigurable manner.

- 11. Electrical converter of claim 10 in conjunction with any one of the claims 1 to 6, wherein the first switching means (112) are configured to interconnect the terminals of the first capacitors (C) of the converter modules assigned to a same group of the first groups and/or the second groups.

- 12. Electrical converter of claim 10 or 11 in conjunction with claim 9, wherein the first switching means (112) is configured to connect a first number of the branches to a second number of the plurality of converter modules, the first number and the second number being unequal.

- 35 **13.** Electrical converter of any one of the preceding claims, comprising a control unit (15), wherein the control unit is configured to operate each of

5

10

15

20

25

the plurality converter modules (11) according to a third mode of operation, wherein a DC voltage ( $U_{dc}$ ) across the first and second DC terminals is smaller than or equal to a first voltage ( $u_{an}$ ,  $u_{gn}$ ) across the respective first capacitor (C), and according to a fourth mode of operation, wherein the DC voltage ( $U_{dc}$ ) is larger than the first voltage ( $u_{an}$ ,  $u_{gn}$ ).

- **14.** Electrical converter of any one of the preceding claims, comprising a control unit (15), wherein the first converter stage (12) and the second converter stage (13) comprise active semiconductor switches (T<sub>1</sub>, T<sub>2</sub>, T<sub>3</sub>, T<sub>4</sub>) operably connected to the respective first and second switch node (A, B), wherein the control unit is configured to operate the active semiconductor switches of the first and second converter stages mutually exclusively via pulse width modulation.

- 15. Electrical converter of claim 14, wherein the second AC signal has a single-phase voltage, wherein the control unit (15) is configured to operate the active semiconductor switches ( $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$ ) of one or more first converter modules of the plurality of converter modules connected to one of the plurality of AC terminals (N) for unfolding operation in the second mode of operation, preferably wherein the control unit is configured to operate the one or more first converter modules via pulse width modulation in the first mode of operation.

- **16.** Electrical converter of any one of the preceding claims, comprising a control unit (15), wherein the control unit is configured to determine a duty cycle ( $d_A$ ,  $d_B$ ) for each of the plurality of converter modules independently based on a first reference voltage ( $u^*_{an}$ ,  $u^*_{gn}$ ) across the respective first capacitor (C).

- **17.** Electrical converter of any one of the preceding claims, wherein at least one of the plurality of converter modules (22) is configured to be operated as a power pulsation buffer in the second mode of operation.

- 18. Electrical converter of claim 17, wherein the at least one converter module (21) configured to be operated as a power pulsation buffer is configured to charge and discharge the first capacitor (C) in the second mode of operation.

- 19. Electrical converter of claim 17 or 18, wherein the at least one converter module (21) configured to be operated as a power pulsation buffer further comprises a buffer capacitor (C<sub>PPB</sub>) and second switching means configured to operably connect the buffer capacitor (C<sub>PPB</sub>) to the at least one converter module (21) in the second mode of operation for charging and discharging the buffer capacitor.

- **20.** Electrical converter of claim 19, wherein the second switching means is configured to connect the buffer capacitor (C<sub>PPB</sub>) parallel to the first capacitor (C).

5

- **21.** Electrical converter of claim 19, wherein the second switching means (212) is configured to switch connection of a terminal (213) of the first inductor (L) between the first switch node (A) and a terminal of the buffer capacitor ( $C_{PPB}$ ), such that the second converter stage (13) is operable for charging and discharging the buffer capacitor in the second mode of operation.

- 22. Electrical converter of claim 21, wherein the second switching means (212) is further configured to connect a bridge-leg (24) of the first converter stage (12) between the first and second DC terminals and the first switch node (A) to a respective AC terminal in the second mode of operation.

- 23. Battery charging system, in particular for charging electric vehicle drive batteries, wherein the battery charging system comprises a power supply, the power supply comprising the electrical converter (10) of any one of the preceding claims.

Boost Buck

0.75

0.5

0.25  $m = u_{an}/U_{dc}$   $m = u_{an}/U_{dc}$

FIG 4

FIG 10

FIG 13

FIG 14

FIG 17

#### INTERNATIONAL SEARCH REPORT

International application No PCT/EP2021/073198

A. CLASSIFICATION OF SUBJECT MATTER INV. H02M1/10 H02M7/81 H02J7/20 ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H02M H02J

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

| C. DOCUM | EUEDIOP | ERELEVANI |

|----------|---------|-----------|

|          |         |           |

|          |         |           |

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                     | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| А         | WO 2020/007767 A1 (HELLA GMBH & CO KGAA [DE]) 9 January 2020 (2020-01-09) figures 1,4a,5,6 page 9, last paragraph - page 10 page 6 page 1, paragraph 1 | 1-23                  |

| A         | US 2011/261591 A1 (KRAUSE AXEL [CH]) 27 October 2011 (2011-10-27) figures 1,7 paragraph [0004] - paragraph [0007] paragraph [0079]                     | 10-12,<br>17-23       |

|   | X Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | X See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | * Special categories of cited documents:  "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier application or patent but published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filing date but later than the priority date claimed | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art  "&" document member of the same patent family |

|   | Date of the actual completion of the international search  22 November 2021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Date of mailing of the international search report $30/11/2021$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ı | Name and mailing address of the ISA/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Authorized officer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

1

European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016

van der Weiden, Ad

# **INTERNATIONAL SEARCH REPORT**

International application No

PCT/EP2021/073198

| 0(01:      | tion). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                | PC1/EP2021/0/3198     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| C(Continua | ·                                                                                                                                                         |                       |

| Category*  | Citation of document, with indication, where appropriate, of the relevant passages                                                                        | Relevant to claim No. |

| Υ          | US 2010/091529 A1 (JAKEMAN NIGEL [GB] ET<br>AL) 15 April 2010 (2010-04-15)<br>figures 1a-1e,3<br>paragraph [0058]<br>paragraph [0062]<br>paragraph [0098] | 1-23                  |

| Α          | WO 2015/193003 A1 (BOSCH GMBH ROBERT [DE])<br>23 December 2015 (2015-12-23)<br>figures 1,2,5                                                              | 1-23                  |

| Υ          | WO 2019/057771 A1 (ETH ZUERICH [CH])<br>28 March 2019 (2019-03-28)<br>figure 2<br>page 2                                                                  | 1-23                  |

| Α          | WO 2020/079019 A1 (PRODRIVE TECH BV [NL]) 23 April 2020 (2020-04-23) the whole document                                                                   | 8,9,15                |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

|            |                                                                                                                                                           |                       |

1

# **INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/EP2021/073198

| Patent document<br>cited in search report | Publication<br>date | Patent family<br>member(s)                                                                                                                                                                                                  | Publication<br>date                                                                                                                                                                              |  |

|-------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| WO 2020007767 A1                          | 09-01-2020          | CN 112368897 A DE 102018116486 A1 EP 3818604 A1 US 2021159784 A1 WO 2020007767 A1                                                                                                                                           | 12-02-2021<br>09-01-2020<br>12-05-2021<br>27-05-2021<br>09-01-2020                                                                                                                               |  |

| US 2011261591 A1                          | 27-10-2011          | CN 102301576 A CN 102301577 A EP 2391521 A2 EP 2391522 A2 JP 4910078 B1 JP 5480296 B2 JP 2012516670 A JP 2012516671 A KR 20110110783 A KR 20110110783 A US 2010220501 A1 US 2011261591 A1 WO 2010086788 A2 WO 2010086823 A2 | 28-12-2011<br>28-12-2011<br>07-12-2011<br>07-12-2011<br>04-04-2012<br>23-04-2014<br>19-07-2012<br>19-07-2012<br>07-10-2011<br>07-10-2011<br>02-09-2010<br>27-10-2011<br>05-08-2010<br>05-08-2010 |  |

| US 2010091529 A1                          | 15-04-2010          | CN 101652912 A<br>EP 2118983 A1<br>GB 2459050 A<br>US 2010091529 A1<br>WO 2008074996 A1                                                                                                                                     | 17-02-2010<br>18-11-2009<br>14-10-2009<br>15-04-2010<br>26-06-2008                                                                                                                               |  |

| WO 2015193003 A1                          | 23-12-2015          | DE 102014211853 A1<br>WO 2015193003 A1                                                                                                                                                                                      | 24-12-2015<br>23-12-2015                                                                                                                                                                         |  |

| WO 2019057771 A1                          | 28-03-2019          | CH 714180 A2<br>WO 2019057771 A1                                                                                                                                                                                            | 29-03-2019<br>28-03-2019                                                                                                                                                                         |  |

| WO 2020079019 A1                          | 23-04-2020          | CH 715448 A2<br>CN 113056865 A<br>EP 3868010 A1<br>KR 20210076062 A<br>WO 2020079019 A1                                                                                                                                     | 15-04-2020<br>29-06-2021<br>25-08-2021<br>23-06-2021<br>23-04-2020                                                                                                                               |  |