#### US010404171B2

# (12) United States Patent

Neumayr et al.

(54) POWER CONVERTER CIRCUIT WITH A SWITCHED MODE POWER CONVERTER THAT IS SWITCHED BASED UPON A MEASURED INDUCTOR CURRENT AND DYNAMICALLY-DETERMINED FIRST AND SECOND THRESHOLDS

(71) Applicant: Infineon Technologies Austria AG, Villach (AT)

(72) Inventors: Dominik Neumayr, Zurich (CH);

Dominik Bortis, Zurich (CH); Gerald

Deboy, Klagenfurt (AT); Marc

Fahlenkamp, Geretsried (DE); Johann

Kolar, Zurich (CH); Martin Krueger,

Oberschleissheim (DE); Anthony

Sanders, Weissenfeld (DE)

(73) Assignee: Infineon Technologies Austria AG, Villach (AT)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/983,980

(22) Filed: May 18, 2018

(65) Prior Publication Data

US 2018/0337600 A1 Nov. 22, 2018

(30) Foreign Application Priority Data

May 19, 2017 (DE) ...... 10 2017 111 006

(51) Int. Cl. H02M 1/00 (2006.01) H02M 1/08 (2006.01) H02M 1/32 (2007.01)

(52) U.S. Cl. CPC ...... *H02M 3/158* (2013.01); *H02M 1/08* (2013.01); *H02M 1/32* (2013.01); *H02M*  (10) Patent No.: US 10,404,171 B2

(45) **Date of Patent: Sep. 3, 2019**

(56) References Cited

### U.S. PATENT DOCUMENTS

9,819,264 B1\* 11/2017 Boezen ...... H02M 1/08 2007/0043269 A1\* 2/2007 Mannheimer ..... A61B 5/14551 600/323

(Continued)

### FOREIGN PATENT DOCUMENTS

CN 102097934 A 6/2011

### OTHER PUBLICATIONS

Ramesh, Vaddi et al., "An Adaptive Hysteresis Band Current Controlled Shunt Active Power Filter", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, vol. 3, Issue 3, Mar. 2014, pp. 8031-8040.

(Continued)

Primary Examiner — Kyle J Moody

Assistant Examiner — Trinh Q Dang

(74) Attorney, Agent, or Firm — Murphy, Bilak &

Homiller, PLLC

# (57) ABSTRACT

Disclosed is a power converter circuit and a method for operating the power converter circuit. The power converter circuit includes at least one converter stage and a control circuit. The at least one converter stage includes an input configured to receive an input power, an output configured to supply an output power, a first electronic switch, and a first inductor coupled to the first electronic switch. The control circuit includes a hysteresis controller configured to drive the first electronic switch based on a current measurement signal representing a current through the inductor, a first threshold signal, and a second threshold signal, and an operating point controller configured to detect an operating (Continued)

# US 10,404,171 B2

Page 2

| point of the converter stage to generate the    | first threshold |

|-------------------------------------------------|-----------------|

| signal and the second threshold signal based of | on the detected |

| operating point.                                |                 |

# 28 Claims, 15 Drawing Sheets

| (51) | Int. Cl.  | H02M 1/40  |

|------|-----------|------------|

| , ,  | (2007.01) | H02M 3/156 |

|      | (2006.01) | H02M 3/158 |

|      | (2006.01) |            |

# (56) References Cited

U.S. PATENT DOCUMENTS

| 2008/0067993 | A1 | 3/2008 | Coleman          |

|--------------|----|--------|------------------|

| 2012/0223691 | A1 | 9/2012 | Weinstein et al. |

| 2014/0006808 A1  | 1/2014  | Sizikov et al     |

|------------------|---------|-------------------|

|                  |         | Peker H02M 3/1582 |

| 2014/021/990 AT  | 8/2014  |                   |

|                  |         | 323/271           |

| 2014/0253181 A1  | 9/2014  | Mukherjee         |

| 2015/0162830 A1* | 6/2015  | Dong H02M 1/36    |

|                  |         | 323/271           |

| 2016/0301303 A1* | 10/2016 | Bari H02M 3/156   |

### OTHER PUBLICATIONS

Wu, Xiaohui et al., "Adaptive Hysteresis Window Control (AHWC) Technique for Hysteretic DC-DC Buck Converter with Constant Switching Frequency", 2010 Asia-Pacific Power and Energy Engineering Conference (APPEEC), Mar. 28-31, 2010, pp. 1-4.

<sup>\*</sup> cited by examiner

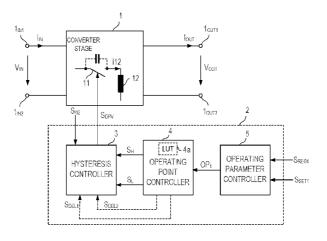

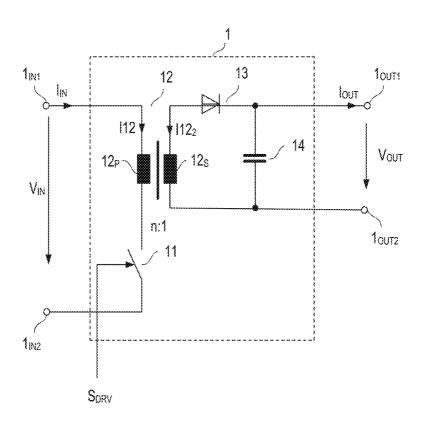

FIG 1

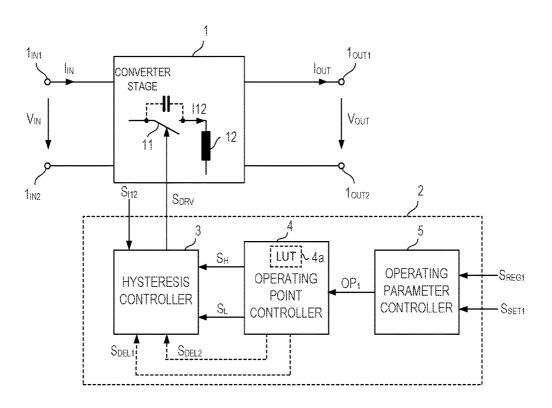

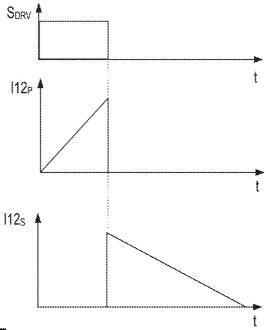

FIG 2

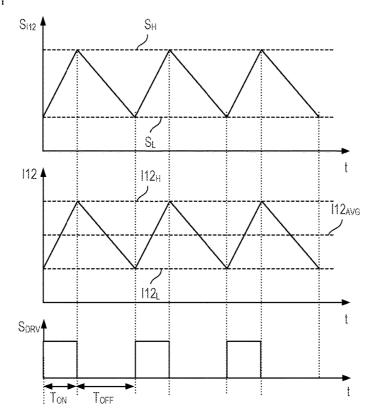

FIG 3

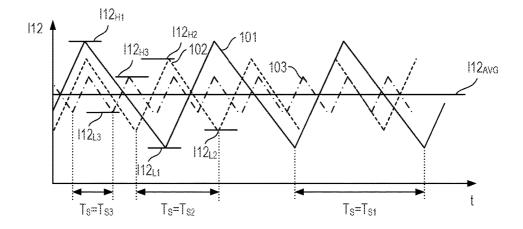

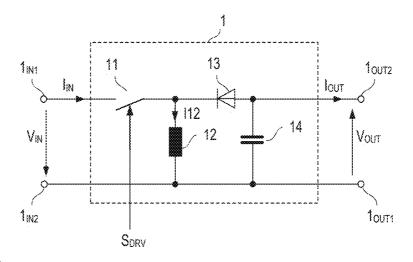

FIG 4

FIG 5

FIG 7

FIG 8

FIG 9

FIG 10

FIG 11

FIG 12

FIG 13C

FIG 14

FIG 15

FIG 19

FIG 22

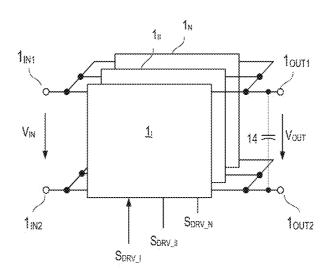

FIG 24

FIG 25

FIG 26

FIG 27

FIG 28

FIG 29

### POWER CONVERTER CIRCUIT WITH A SWITCHED MODE POWER CONVERTER THAT IS SWITCHED BASED UPON A MEASURED INDUCTOR CURRENT AND DYNAMICALLY-DETERMINED FIRST AND SECOND THRESHOLDS

This disclosure in general relates to a power converter circuit, particularly a power converter circuit with a switched mode power converter.

Switched mode power converters (which are often also referred to as switched mode power supplies (SMPS)) are widely used in various types of automotive, industrial, household or consumer electronic applications. A switched mode power converter includes at least one electronic switch 15 coupled to at least one inductor. A switched mode power converter is configured to receive an input power which is given by an input current multiplied with an input voltage at an input and supply an output power which is given by an output voltage multiplied with an output current to a load 20 coupled to an output. By regulating the input power received at the input the switched mode power converter may regulate at least one operating parameter, for example, the output voltage, the output current, or the input current. The input power is regulated by regulating a current through the at 25 least one inductor, whereas the inductor current is regulated by a switched mode operation of the at least one electronic switch.

The switched mode operation of the at least one electronic switch may include operating the electronic switch in a 30 plurality of successive drive cycles, with each drive cycle including an on-time in which the at least one electronic switch is switched on and an off-time in which the at least one electronic switch is switched off. Inevitably, converting power by the switched mode power converter is associated 35 with power losses. These power losses are given by a difference between an overall input power, which also includes a power supply of the switched mode power converter itself, and an output power available at the output. These power losses include, for example, conduction losses, 40 switching losses, or hysteresis losses in the inductor. Conduction losses are losses due to ohmic resistances in conductors and electronic devices of the power converter. Switching losses are losses associated with the switched mode operation of the at least one electronic switch such as 45 losses associated with charging and discharging (parasitic) capacitances of the at least one electronic switch. And, hysteresis losses are losses associated with magnetizing and demagnetizing the inductor. It is desirable to reduce those power losses.

One example relates to a power converter circuit. The power converter circuit includes at least one converter stage and a control circuit. The at least one converter stage includes an input configured to receive an input power, an output configured to supply an output power, a first electronic switch, and a first inductor coupled to the first electronic switch. The control circuit includes a hysteresis controller configured to drive the first electronic switch based on a current measurement signal representing a current through the inductor, a first threshold signal, and a 60 second threshold signal, and an operating point controller configured to detect an operating point of the converter stage to generate the first threshold signal and the second threshold signal based on the detected operating point.

Another example relates to a method. The method 65 includes detecting an operating point of at least one converter stage including an electronic switch and an inductor

2

coupled to the electronic switch in a power converter circuit, selecting a first threshold and a second threshold based on the detected operating point, and driving the electronic switch based on the first threshold and the second threshold and a current measurement signal representing a current through the inductor.

Yet another example relates to a method. The method includes finding an optimum switching frequency of an electronic switch in a power converter stage of a power converter circuit at each of a plurality of different operating points; sensing a current through an inductor connected in series with the electronic switch; and in each operating point, at the optimum frequency, detecting a maximum current through the inductor and a minimum current through the inductor.

Examples are explained below with reference to the drawings. The drawings serve to illustrate certain principles, so that only aspects necessary for understanding these principles are illustrated. The drawings are not to scale. In the drawings the same reference characters denote like features.

FIG. 1 shows a block diagram that illustrates one example of a power converter circuit that includes a converter stage with an electronic switch and an inductor, and a control circuit with a hysteresis controller and an operating point controller:

FIG. 2 shows examples of signal waveforms of a drive signal of the electronic switch, a current through the inductor, and a current measurement signal:

FIG. 3 shows examples of different current waveforms of the inductor current that have the same average current level:

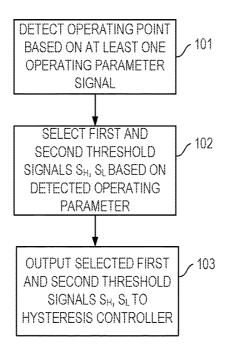

FIG. 4 shows a flowchart that illustrates a function of the operating point controller;

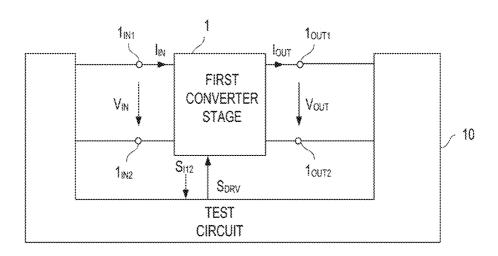

FIG. 5 illustrates a test setup for detecting optimum first and second current thresholds of the hysteresis controller in different operating points of the converter stage;

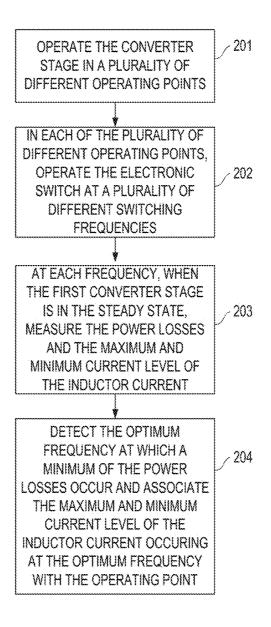

FIG. 6 shows a flowchart that illustrates one example of a testing routine;

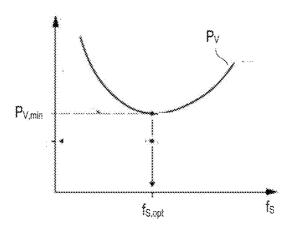

FIG. 7 illustrates how an optimum switching frequency associated with one operating point may be obtained based on the results obtained in the testing procedure.

FIG. 8 shows diagrams that illustrate a switching frequency and first and second current thresholds associated with different operating points obtained by the testing routine;

FIG. 9 shows one example of a converter stage implemented with a buck topology;

FIG. 10 shows one example of a converter stage imple-50 mented with a boost topology;

FIG. 11 shows one example of the hysteresis controller; FIG. 12 shows one example of an active rectifier element with an electronic switch that may be used in the converter stage:

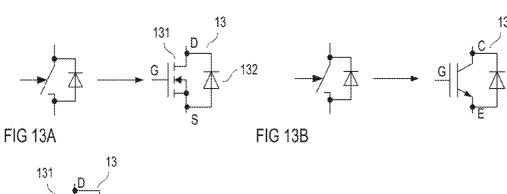

FIGS. 13A to 13C illustrate possible implementations of the rectifier element shown in FIG. 12;

FIG. 14 shows a modification of the hysteresis controller shown in FIG. 11;

FIG. 15 shows one example of an operating parameter controller that may be implemented in the control circuit;

FIG. 16 shows an example of a power converter circuit that includes a second converter stage connected upstream the converter stage and an unfolding circuit connected downstream the converter stage:

FIGS. 17A to 17C show timing diagrams that illustrate signal waveforms of signals occurring in the power converter circuit shown in FIG. 16;

FIG. 18 shows one example of the unfolding circuit shown in FIG. 16:

FIG. 19 shows one example of an operating parameter controller that may be implemented in the control circuit shown in FIG. 16:

FIG. 20 shows an example of a power converter circuit that includes a rectifier circuit connected upstream the converter stage and a second converter stage connected downstream the converter stage;

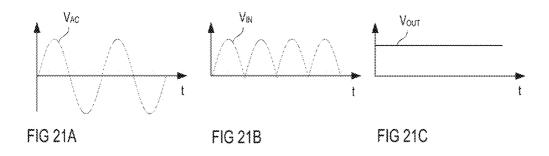

FIGS. **21**A to **21**C show timing diagrams that illustrate 10 signal waveforms of signals occurring in the power converter circuit shown in FIG. **20**;

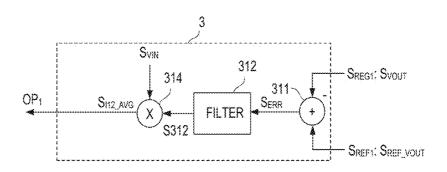

FIG. 22 shows one example of an operating parameter controller that may be implemented in the control circuit shown in FIG. 14:

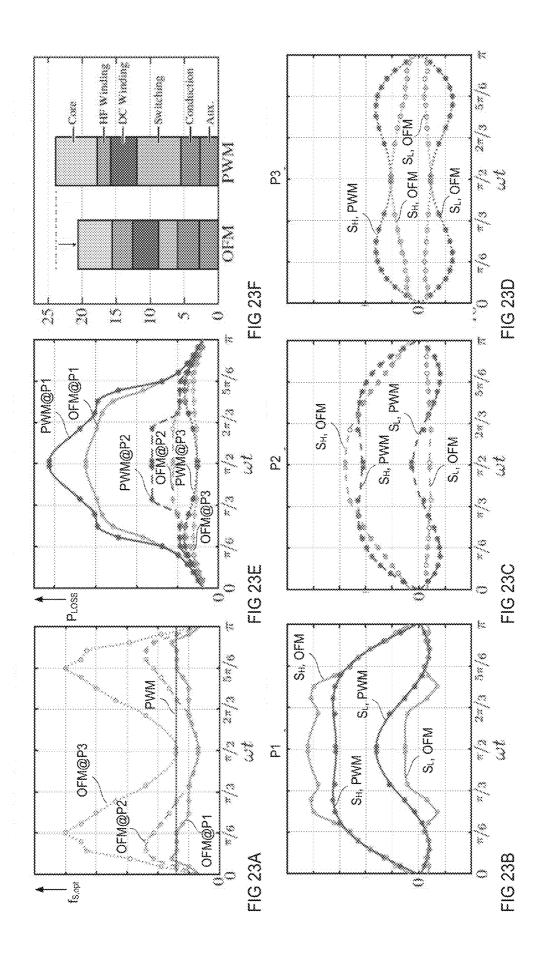

FIGS. 23A to 23F illustrate optimum switching frequencies, first and second current thresholds and power losses in a power converter circuit operated at an optimum switching frequency as compared to a power converter operated at fixed switching frequency;

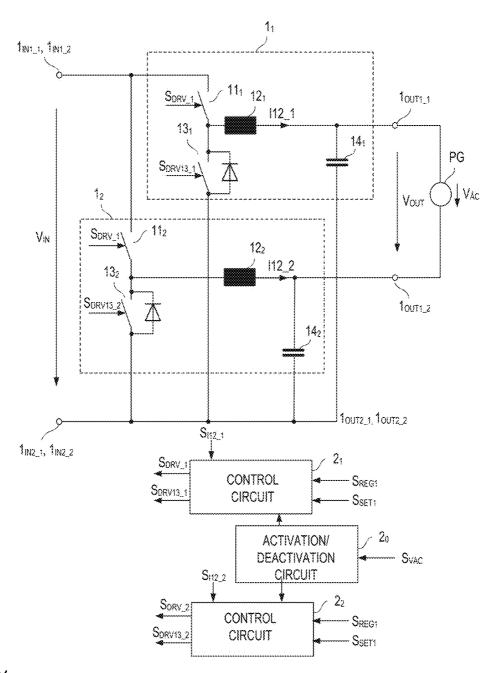

FIG. 24 shows one example of a power converter circuit with two converter stages and associated control circuits;

FIG. 25 shows signal waveforms that illustrate operation of the hysteresis controller in consideration of delays that may occur in the hysteresis controller;

FIG. **26** shows one example of a converter stage with a flyback (converter) topology;

FIG. 27 shows timing diagrams of signals occurring in the flyback converter shown in FIG. 26;

FIG. 28 shows one example of a converter stage with an 30 inverting buck-boost topology; and

FIG. 29 shows one example of a power converter circuit with several converter stages connected in parallel.

In the following detailed description, reference is made to the accompanying drawings. The drawings form a part of the 35 description and by way of illustration show specific embodiments in which the invention may be practiced. It is to be understood that the features of the various embodiments described herein may be combined with each other, unless specifically noted otherwise.

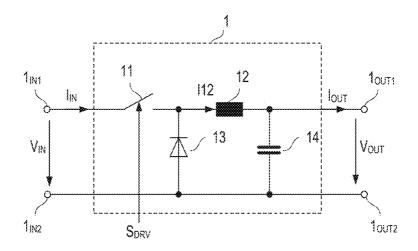

FIG. 1 shows a power converter circuit in particular a switched mode power converter circuit (switched mode power supply, SMPS) according to one example. Referring to FIG. 1, the power converter circuit includes a converter stage 1 with an input configured to receive an input power 45 and an output configured to supply an output power. The input may include a first input node  $\mathbf{1}_{I\!N\!1}$  and a second input node  $1_{IN2}$ , and the output may include a first output node  $\mathbf{1}_{OUT1}$  and a second output node  $\mathbf{1}_{OUT1}$ . The input power received by the converter stage 1 is given by an input current 50  $I_{I\!N}$  multiplied with an input voltage  $V_{I\!N}$  and the output power is given by an output current  $I_{OUT}$  multiplied with an output voltage  $V_{\it OUT}$ . The converter stage 1 includes an electronic switch 11 (which is also referred to as first electronic switch herein further below) connected in series 55 with an inductor 12. The switch 11 is only schematically illustrated in FIG. 1. Any type of electronic switch may be used to implement the switch 11. Examples of the electronic switch 11 include, but are not restricted to, a MOSFET (Metal Oxide Semiconductor Field-Effect Transistor), an 60 IGBT (Insulated Gate Bipolar Transistor), a HEMT (High Electron Mobility Transistor), in particular a Gallium-Nitride (GaN)-HEMT, a BJT (Bipolar Junction Transistor), or the like.

Operation of the converter stage 1 is controlled by a 65 control circuit 2. Controlling operation of the converter stage 1 by the control circuit 2 includes controlling operation

4

of the switch 11 by generating a drive signal  $S_{DRV}$  received by the switch 11, wherein the switch 11 switches on and off in accordance with this drive signal  $S_{DRV}$ . The arrangement with the converter stage 1 and the control circuit 2 is also referred to as (first) power converter in the following.

Referring to FIG. 1, the control circuit 2 includes a hysteresis controller 5, and an operating point controller 4. The hysteresis controller 5 is configured to drive the switch 11, that is, to generate the drive signal  $S_{DRV}$ , based on a current measurement signal S112 representing a current I12 through the inductor 12, a first threshold signal  $S_H$ , and a second threshold signal  $S_L$ . The first threshold signal  $S_H$ represents a first threshold, which is also referred to as upper threshold in the following, and the second threshold signal S<sub>L</sub> represents a second threshold, which is also referred to as lower threshold in the following. In the following,  $S_H$  is used to denote both the first threshold signal and the first (upper) threshold it represents, and  $S_L$  is used to denote both the second threshold signal and the second (lower) threshold it 20 represents. According to one example, the current measurement signal  $S_{I12}$ , which represents the current I12 through the inductor 12, is proportional to the current through the inductor 12. The current measurement signal  $S_{I12}$  can be generated using any type of current measurement circuit (not shown in the drawings) configured to measure the current through the inductor 12. Examples of such current measurement circuits include a current measurement circuit with a shunt resistor, a current measurement circuit with a Hall sensor, a current measurement circuit with an inductive current sensor, or the like.

The operating point controller 4 is configured to detect an operating point of the first converter stage and generate the first threshold signal  $S_H$  and the second threshold signal  $S_L$ based on the detected operating point. According to one example, the operating point is defined by at least one operating point signal OP1, which is referred to as first operating point signal OP<sub>1</sub> in the following. In the example shown in FIG. 1, the operating point controller 4 receives the operating point signal OP<sub>1</sub> from an operating parameter 40 controller 3. The operating parameter controller 3 is configured to receive at least a first operating parameter signal  $S_{REG1}$  that represents a first operating parameter of the converter stage and a first setpoint signal  $S_{SET1}$  associated with the first operating parameter. The setpoint signal  $S_{SET1}$ defines a desired signal level of the first operating parameter. Further, the operating parameter controller 3 is configured to generate the first operating point signal OP1 based on the first operating parameter  $S_{REG1}$  signal and the first setpoint signal S<sub>SET1</sub>.

The control circuit 2 is configured to drive the electronic switch 11 such that at least the first operating parameter represented by the first operating parameter signal  $S_{REG1}$  is regulated in such a way that a level of the first operating parameter essentially equals a level that is represented by the first setpoint signal  $S_{SET1}$ . The first operating parameter may be the output voltage  $V_{OUT}$ . In this case, the first operating parameter signal represents a signal level of the output voltage  $V_{OUT}$  and the first setpoint signal  $S_{SET1}$  represents a desired signal level of the output voltage  $V_{OUT}$ . Regulating the output voltage  $V_{OUT}$ , however, is only an example. Other examples are explained herein further below.

According to one example, the control circuit 2 is configured to regulate the first operating parameter by regulating the input power of the converter stage 1. Regulating the input power is equivalent to regulating the output power, wherein the output power equals the input power minus inevitable power losses occurring in the converter stage 1.

The control circuit 2 regulates the input power by controlling the current I12 through the inductor 12. The inductor current I12, in turn, is controlled by a switched mode operation of the electronic switch 11. The switched mode operation of the electronic switch 11 includes operating the electronic switch 11 based on the drive signal  $S_{DRV}$  in a plurality of successive drive cycles, with each drive cycle including an on-period  $T_{ON}$  in which the at least one electronic switch 11 is switched on and an off-period Tow in which the electronic switch 11 is switched off.

FIG. 2 schematically shows a signal waveform of the drive signal  $S_{DRV}$  in order to illustrate operation of the electronic switch 11 in several successive drive cycles each including an on-period  $T_{ON}$  and an off-period  $T_{OFF}$ . The drive signal  $S_{DRV}$  has an on-level during the on-period and an off-level during the off-period. Just for the purpose of illustration, the on-level is a high signal level and the off-level is a low signal level in the example shown in FIG. 2. The duration of one drive cycle is referred to as cycle 20 period  $T_s$  in the following, and the reciprocal of the cycle period  $T_S$  is referred to as switching frequency  $f_S$ , which is the frequency at which the electronic switch 11 switches on. In the converter stage 1, the electronic switch 11 and the inductor 12 are coupled between the input  $1_{IN1}$ ,  $1_{IN2}$  and the 25 output  $\mathbf{1}_{OUT1},~\mathbf{1}_{OUT2}$  such that the current through the inductor 12 increases during the on-period  $T_{ON}$  and decreases during the off-period Tow. This is also illustrated in FIG. 2 that shows a signal waveform of the current measurement signal  $S_{I12}$  representing the inductor current 30 I12. According to one example, the current measurement signal  $S_{I12}$  is proportional to the inductor current I12. Examples of how the electronic switch 1 and the inductor 12 can be connected between the input  $\mathbf{1}_{I\!N\!1},\,\mathbf{1}_{I\!N\!2}$  and the output  $\mathbf{1}_{OUT1}, \mathbf{1}_{OUT2}$  in order to have an increasing inductor current 35 I12 during the on-period and a decreasing inductor current during the off-period are explained herein further below. A slope of the inductor current I12 during the on-period is referred to as m<sub>ON</sub> in the following, and a slope of the inductor current I12 during the off-period is referred to as 40 mow in the following. These slopes may be dependent on the voltage level of at least one of the input voltage  $V_{IN}$  and the output voltage  $V_{\scriptsize OUT}$

Referring to FIG. 2, the hysteresis controller 5 generates the drive signal  $S_{DRV}$  such that the electronic switch 11 45 switches off when the current measurement signal  $S_{I12}$ , during the on-period  $T_{ON}$ , reaches the upper threshold  $S_H$ and that the electronic switch 11 switches on when the current measurement signal  $S_{I12}$ , during the off-period  $T_{OFF}$ , reaches the lower threshold  $S_L$ . The upper threshold  $S_H$  is 50 associated with a maximum current level  $I12_H$  of the inductor current I12 during one drive cycle, and the lower threshold  $S_L$  is associated with a minimum current level I12<sub>L</sub> of the inductor current I12 during one drive cycle. The maximum current level  $I12_H$  and the minimum current level 55  $\mathrm{I}\mathbf{12}_{L}$  define an average current level  $\mathrm{I}\mathbf{12}_{AVG}$  of the inductor current I12 during one drive cycle and during a plurality of successive drive cycles in which the same lower threshold  $S_L$  and upper threshold  $S_H$  are used to control operation of the electronic switch 11. According to one example, and as 60 shown in FIG. 2, the inductor current I12 increases essentially linearly during the on-period T<sub>ON</sub> and decrease essentially linearly during the off-period. In this case, the average inductor current  $I12_{AVG}$  is given by the arithmetic average of the maximum current level  $I12_H$  as represented by the upper threshold  $S_H$  and the minimum current level  $I12_L$  as represented by the lower threshold  $S_{t}$ , that is,

6

$$I12_{AVG} = \frac{I12_H + I12_L}{2}. (1)$$

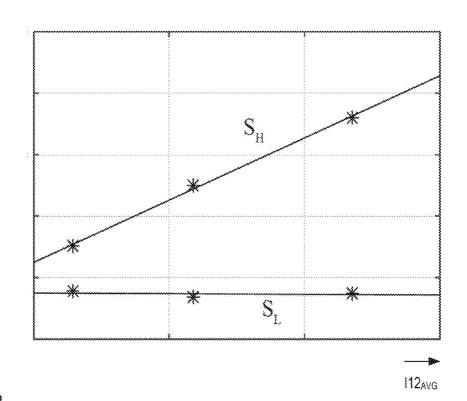

According to one example, the first operating point signal  $\mathrm{OP}_1$  generated by the operating parameter controller 3 and received by the operating point controller 4 represents the (desired) average inductor current  $\mathrm{I12}_{AVG}$ . In this case, the operating point controller 4 generates the first and the second threshold  $\mathrm{S}_L$ ,  $\mathrm{S}_H$  such that the average inductor current  $\mathrm{I12}_{AVG}$  is in accordance with the first operating point signal  $\mathrm{OP}_1$ . As can be seen from equation (1), for each level of the average inductor current  $\mathrm{I12}_{AVG}$  a plurality of pairs of values each including a maximum current level  $\mathrm{I12}_H$  and an associated minimum current level  $\mathrm{I12}_L$  can be found that meet equation (1). This is illustrated in FIG. 3.

FIG. 3 shows three examples of current waveforms of the inductor current I12 that have the same average current level  $I12_{AVG}$ . A first waveform 101 is obtained by selecting the upper and lower threshold  $S_H$ ,  $S_L$  such that the inductor current I12 oscillates between a first maximum level  $I12_{H1}$ and a first minimum level  $I12_{L1}$ , a second waveform 102 is obtained by selecting the upper and lower threshold  $S_H$ ,  $S_L$ such that the inductor current I12 oscillates between a second maximum level  $I12_{H2}$  and a second minimum  $I12_{L2}$ , and a third waveform 103 is obtained by selecting the upper and lower threshold  $S_H$ ,  $S_L$  such that the inductor current I12 oscillates between a third maximum level  $I12_{H3}$  and a third minimum level  $I12_{L3}$ . These maximum and minimum current level pairs are such that they result in different cycle periods. In general, a duration of the cycle period Ts decreases and, consequently, the switching frequency fs increases as a difference between the maximum level  $I12_H$ and the corresponding minimum level I12<sub>L</sub> decreases. This difference  $\Delta I12=I12_H-I12_L$  is referred to as current swing or peak-to-peak value in the following. From the three waveforms shown in FIG. 3, the first waveform 101 has the largest peak-to-peak value and, therefore, the longest cycle period  $T_{S1}$ , the third waveform 103 has the smallest peakto-peak value and, therefore, the shortest cycle period  $T_{S3}$ . A peak-to-peak value of the second waveform 102 is between the peak-to-peak values of the first waveform 101 and the third waveform 103, so that a second cycle period  $T_{s2}$  is between the first cycle period  $T_{S1}$  and the third cycle period

During operation of the power converter circuit, power losses occur. These power losses include, for example, conduction losses, switching losses or losses in the inductor such as hysteresis and eddy current core losses. Conduction losses are losses due to ohmic resistances in conductors (such as PCB traces, inductor winding, or the like) and the electronic switch 11, for example. Switching losses are losses associated with the switched mode operation of the at least one electronic switch 11. For instance, switching losses are associated with charging and discharging parasitic capacitances of the electronic switch 11. One such parasitic capacitance of the electronic switch 11 is illustrated in dashed lines in FIG. 1. This capacitance is charged when the electronic switch 11 switches off and a voltage across the electronic switch 11 increases, and is discharged when the electronic switch 11 switches on and the voltage across the electronic switch 11 essentially decreases to zero. Hysteresis and eddy current core losses are losses associated with magnetizing and demagnetizing the inductor 12 when the inductor current I12 increases or decreases. The conduction losses, for example, are proportional to the square of the

inductor current I12. From this perspective it may be desirable to avoid high maximum currents levels when adjusting a certain current level of the average inductor current I12 $_{AVG}$ . Avoiding high maximum currents is equivalent to selecting a small peak-to-peak value. Selecting a small 5 peak-to-peak value, however, results in a high switching frequency. Switching losses, however, increase as the switching frequency increases. These switching losses also include power consumed by the control circuit for driving the electronic switch 11. On the other hand, the losses in the 10 inductor 12 decrease as the switching frequency decreases.

In general, it is desirable to minimize power losses that occur during operation of the power converter circuit. However, due to different types of power losses that occur and due to the complex nature of these power losses, it is difficult 15 to find an analytical approach which, for each average current level that may occur during operation of the power converter circuit, finds a peak-to-peak value and a switching frequency, respectively, that minimizes the power losses occurring at the respective average current level. According 20 to one example, a mapping of an operating point of the power converter circuit to the first and second threshold signal  $S_H$ ,  $S_L$  performed by the operating point controller 4 is therefore based on experimental results and/or simulations. "Mapping the operating point to the first and second  $_{25}$  threshold signals  $S_H$ ,  $S_L$ ", according to one example, includes detecting the operating point of the converter stage based at least on the first operating point signal OP<sub>1</sub> and outputting the first and second threshold signals S<sub>H</sub>, S<sub>L</sub> associated with the detected operating point by the operating 30 point controller 4. This is illustrated in FIG. 4.

FIG. 4 shows a flowchart of the operation of the operating point controller 4. Referring to FIG. 4, the operation point controller 4 detects the operating point based on at least one operating point signal, such as the first operating point signal 35  $\mathrm{OP}_1$  explained above (see 101 in FIG. 4). Further, based on the detected operating point, the operating point controller 4 maps the detected operating point to first and second threshold signals  $\mathrm{S}_H$ ,  $\mathrm{S}_L$  associated with the detected operating point (see 102 in FIG. 4), and outputs the first and second 40 threshold signal  $\mathrm{S}_H$ ,  $\mathrm{S}_L$  to the hysteresis controller (see 103 in FIG. 4).

According to one example, the operating point controller 4 includes a look-up table (LUT) 4a that holds the individual first and second threshold values associated with the indi- 45 vidual operating points. Theoretically, the power converter circuit can be operated in an infinite number of different operating points as there is an infinite number of different average inductor current levels. An operating point of the power converter circuit may therefore be defined by inter- 50 vals of the first operating point signal  $OP_1$ . For example, the power converter circuit is in a first operating point when a signal value of the first operating point signal OP<sub>1</sub> is between a first value and a second value, the power converter circuit is in a second operating point when a signal value of the first 55 operating point signal OP<sub>1</sub> is between the second value and a third value, and so on. According to one example, the operating point is not only dependent on the first operating point signal OP<sub>1</sub> which, for example, represents the average inductor current, but is further dependent on at least one 60 further operating point signal. In this case, the operating point controller 4 detects the operating point based on at least two operating parameter signals and maps the detected operating point to the first and second threshold signals associated with the detected operating point.

One example of how the first and second thresholds  $\mathbf{S}_H$ ,  $\mathbf{S}_L$  associated with the individual operating points may be

8

obtained is explained with reference to FIGS. 5 and 6 below. FIG. 5 schematically illustrates a test setup with a test circuit, and FIG. 6 shows a flowchart that illustrates how the test circuit may operate. Referring to FIG. 5, the test circuit  $\mathbf{10}$  is connected to the input  $\mathbf{1}_{IN1}, \mathbf{1}_{IN2}$  and the output  $\mathbf{1}_{OUT1},$  $\mathbf{1}_{OUT2}$  of the converter stage 1, receives the current measurement signal  $S_{I12}$  and generates the drive signal  $S_{DRV}$ received by the electronic switch (not shown in FIG. 5) included in the converter stage 1. The test circuit 10 is configured to operate the converter stage 1 in different operating points, vary the switching frequency of the electronic switch 11 in each of these operating points, detect an optimum switching frequency at which power losses occurring in the converter stage 1 reach a minimum, and detect the maximum inductor current and the minimum inductor current occurring at the optimum switching frequency. This optimum switching frequency is referred to as optimum frequency  $f_{S, opt}$  in the following.

The test circuit 10 shown in FIG. 5 provides the input voltage  $V_{I\!\!N}$  and the input current  $I_{I\!\!N}$ , which define the input power received by the converter stage 1. Further, the test circuit 10 acts as a load that draws the output current  $I_{OUT}$  from the converter stage 1, wherein the output voltage  $V_{OUT}$  and the output current  $I_{OUT}$  define the output power of the converter stage 1. The test circuit 10 further includes a power analyzer that measures the input power and the output power and, based on the measured input power and the measured output power, calculates the power losses. These power losses may be calculated by subtracting a value representing the output power from a value representing the input power and additionally adding a value representing power required in the test circuit 10 for generating the drive signal  $S_{DRV}$ . That is,

### $P_{LOSS} \!\!=\!\! P_{I\!N} \!\!+\!\! P_{DRV} \!\!-\!\! P_{OUT},$

where  $P_{LOSS}$  denotes the power losses.  $P_{IN}$  denotes the input power,  $P_{OUT}$  denotes the output power and  $P_{DRV}$  denotes the power required for driving the electronic switch 11 and any other active devices in the power converter circuit such as an active rectifier element. According to one example, operating the converter stage 1 in one operating point by the test circuit 10 includes generating a fixed input voltage  $V_{IN}$  by the test circuit and drawing a constant output current  $I_{OUT}$ from the converter stage 1 by the test circuit 10, and regulating the output voltage  $V_{\ensuremath{\textit{OUT}}}$  to be constant. Regulating the output voltage  $\mathbf{V}_{OUT}$  includes regulating a duty cycle of the drive signal  $S_{DRV}$  such that the output voltage  $V_{OUT}$ reaches a predefined set value. The "duty cycle" of the drive signal  $S_{DRV}$  is a ratio between a duration of the on-period  $(T_{ON} \text{ in FIG. 2})$  and the duration  $T_S$  of the drive cycle period. Referring to the above, in each operating point, the test circuit 10 generates the drive signal  $S_{DRV}$  with several different switching frequencies, wherein the reciprocal of each switching frequency is the respective cycle period. At each of these different switching frequencies the test circuit 10 operates the converter stage 1 until the output voltage  $V_{OUT}$  has been regulated to the desired set value, that is, until the converter stage 1 is in the steady state. In the steady state, which is when the duty cycle of the drive signal  $S_{DRV}$ has been adjusted such that the output voltage  $V_{OUT}$  is constant and has reached the desired set value, the maximum value and the minimum value of the inductor current I12 are measured. The maximum and minimum inductor current values that are measured at the optimum frequency  $f_{S,opt}$  are then associated with the operating point in which the converter stage 1 is operated.

The test circuit 10 operates the converter stage 1 in a plurality of different operating points, detects the optimum frequency  $\mathbf{f}_{S,opt}$  in each of these operating points and detects the maximum and minimum inductor current values occurring at the respective optimum frequency  $\mathbf{f}_{S,opv}$  so that a 5 plurality of operating points and associated maximum and minimum inductor current values are obtained. Based on these maximum and minimum inductor current values associated with the individual operating points the first and second threshold values  $\mathbf{S}_H$ ,  $\mathbf{S}_L$  implemented in the operating point controller 4 are obtained.

The test procedure performed by the test circuit 10 is schematically illustrated in a flow chart shown in FIG. 6. Referring to FIG. 6, testing the converter stage 1 includes operating the converter stage in a plurality of different 15 operating points (201), and, in each of the plurality of different operating points, operating the electronic switch 11 at a plurality of different switching frequencies (202). At each of these different frequencies, when the converter stage is in the steady state, the power losses and the maximum 20 current level and the minimum current level of the inductor current are determined (203). Further, in each operating point, the switching frequency is detected at which a minimum of the power losses occurs. This frequency is the optimum switching frequency  $f_{S, opt}$ . The maximum and 25 minimum current level detected at the optimum switching frequency  $f_{S, opt}$  are associated with the respective operating point and are used to generate the first threshold and the second threshold  $S_H$ ,  $S_L$  associated with the operating point. According to one example, the first threshold and the second 30 threshold  $S_H$ ,  $S_L$  are generated to be proportional to detected maximum and minimum current levels.

Finding the optimum switching frequency  $f_{S,\ opt}$  by the test circuit 10 is schematically illustrated in FIG. 7. FIG. 7 schematically illustrates the power losses  $P_{\nu}$  measured in 35 one operating point dependent on the switching frequency  $f_{S}$ . Referring to FIG. 7, the optimum switching frequency  $f_{S}$ , opt op is the switching frequency at which a minimum  $P_{\nu,min}$  of the power losses  $P_{\nu}$  occurs, wherein these losses increase when the switching frequency is lower than the optimum 40 switching frequency and increase when the switching frequency is higher than the optimum switching frequency.

As an example, FIG. 8 illustrates the first threshold  $S_H$  and the second threshold  $S_L$  that were obtained by testing an example power converter circuit in accordance with the 45 method explained with reference to FIGS. 5 to 7. FIG. 8 shows the first and second thresholds  $S_H$ ,  $S_L$  dependent on the average inductor current  $I12_{AVG}$ . These first and second threshold were obtained in a test scenario in which the test circuit 10 kept the input voltage  $V_{IN}$  and the output voltage  $V_{OUT}$  essentially constant and varied the average inductor current  $I_{AVG}$  by varying the output current  $I_{OUT}$ . At each output current level, the test circuit 10 varied the switching frequency in order to find the optimum switching frequency  $f_{S,opt}$ . The first and second threshold levels  $S_H$ ,  $S_L$  shown in 55 FIG. 8 represent the first and second threshold levels obtained at the respective optimum switching frequency  $f_{S,opt}$ .

$f_{S,opp}$ . Based on curves of the first and second threshold  $S_H$ ,  $S_L$ , such as curves of the type shown in FIG. 8, obtained under 60 test conditions or by simulations the operating point controller 4 can be programmed. To "program" may include programming a look-up table implemented in the operating point controller. According to another example, programming the operating point controller includes finding a first 65 function that approximates the curve of the first threshold  $S_H$  and a second function that approximates the curve of the

10

second threshold  $S_L$  and implementing these functions in the operating point controller 4 such that the operating point controller is configured to calculate the first and second threshold levels  $S_H$ ,  $S_L$  based on these functions dependent on the operating point as represented at least by the first operating point signal. According to another example, the operating point controller includes a look-up table and a calculation unit. If, for example, an operating point is between a first operating point and a second operating point for each of which the look-up table holds a respective pair of first and second threshold levels  $S_H$ ,  $S_L$ , the first and second threshold signals output by the operating point controller 4 may be calculated by the calculation unit based on the first and second operating points.

Curves of the first and second thresholds  $S_H$ ,  $S_L$  may be obtained by determining the first and second thresholds  $S_H$ ,  $S_L$  at the optimum switching frequency  $f_{S,opt}$  at several operating points and determining the first and second thresholds  $S_H$ ,  $S_L$  associated with other operating points by interpolation.

Just for the purpose of illustration, the example shown in FIG. 8 is based on the assumption that the operating point is only defined by an average inductor current  $I12_{AVG}$ . However, as explained herein further below, the operating point may be dependent on further operating parameters, such as the input voltage and the output voltage. In this case, the curves representing the first and the second threshold levels  $S_H$ ,  $S_L$  may be represented by functions with more than one variable

The converter stage 1 may be implemented in various ways. That is, there is a variety of different topologies that may be used to implement the converter stage 1. Some examples of these topologies are explained herein further below. Further, each topology may be implemented with different types of electronic components. That is, one and the same topology may be implemented with different types of electronic switches, different types of inductors, and so on. In the following, "one type of converter stage" is a converter stage with a certain topology and with a certain set of electronic components used to implement the topology. The test or simulation procedure explained with reference to FIG. 5 may be applied to one sample of a certain type of converter stage, wherein the first and second threshold values obtained by testing the sample example may then be applied to any other converter stage of the same type. A manufacturer may therefore obtain by test and/or simulation the plurality of first and second thresholds  $\mathbf{S}_{\!H}\!,\,\mathbf{S}_{\!L}$  for one type of power converter circuit only once and use these first and second thresholds  $S_H$ ,  $S_L$  to program the operating point controllers of a plurality of power converter circuits of this type.

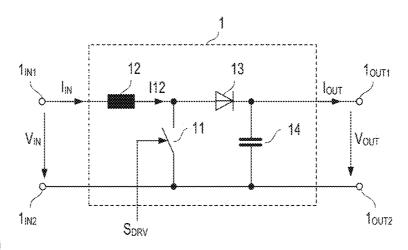

Referring to the above, the converter stage 1 may be implemented in different ways. Two examples of how the converter stage 1 may be implemented are shown in FIGS. 9 and 10. FIG. 9 shows the converter stage 1 implemented with a buck converter topology and FIG. 10 shows the converter stage 1 implemented with a boost converter topology. The converter stage 1, however, is not restricted to be implemented in accordance with one of these examples.

Referring to FIG. 9, in the converter stage 1 with the buck converter topology (buck topology), a series circuit with the electronic switch 11, the inductor 12 and a capacitor 14 is connected between the first input node  $1_{IN1}$  and the second input node  $1_{IN2}$  of the converter stage 1. The output voltage  $V_{OUT}$  is available across the capacitor 14, which is connected between the first output node  $1_{OUT}$  and the second

output node  $\mathbf{1}_{OUT2}$ , wherein the second input node  $\mathbf{1}_{IN2}$  and the second output node  $\mathbf{1}_{OUT2}$  of the converter stage  $\mathbf{1}$  are formed by the same circuit node. Further, a rectifier element 13 is connected in parallel with a series circuit including the inductor 12 and the capacitor 14. When the electronic switch 11 is driven by a drive signal  $S_{DRV}$  as shown in FIG. 2 that includes a plurality of successive drive cycles each including an on-period  $T_{ON}$  and an off-period  $T_{OFF}$  the inductor current I12 increases during the on-period  $T_{ON}$ , that is, when the electronic switch 11 is switched on, and decreases during the off-period. The slope  $m_{ON}$  of the inductor current I12 during the on-period  $T_{ON}$  is substantially given by a voltage across the inductor 12 divided by an inductance L of the inductor 12. During the on-time, the voltage across the  $_{15}$ inductor 21 is given by the input voltage  $V_{IN}$  minus the output voltage V<sub>OUT</sub> (wherein a voltage level of the input voltage  $V_{IN}$  is higher than the voltage level of the output voltage  $V_{OUT}$ ), so that the slope during the on-time is given

$$m_{ON} = \frac{V_{IN} - V_{OUT}}{L}. \tag{2a}$$

During the off-period, the voltage across the inductor 12 substantially equals the negative output voltage  $-V_{OUT}$ , so that the absolute value of the slope  $m_{OFF}$  is given by

$$m_{OFF} = -\frac{V_{OUT}}{L}. \tag{2b}$$

Referring to equations (2a) and (2b), the input voltage  $V_{IN}$  35 and the output voltage  $\mathbf{V}_{OUT}$  define the slopes of the inductor current. These slopes, affect the switching frequency. That is, at one first threshold  $S_H$  and a corresponding second threshold  $S_L$  the switching frequency is dependent on the current slopes, wherein the frequency increases as the slopes 40 are getting steeper. Thus, in a converter stage with a buck topology the operating point, besides the average inductor current  $I12_{AVG}$ , is defined by the input voltage  $V_{IN}$  and the output voltage  $V_{OUT}$ . The operating point controller 4 in this case receives a second operating point signal representing the output voltage  $V_{\scriptsize OUT}$  and a third operating point signal representing the input voltage  $V_{I\!N}$  additionally to the first operating point signal OP<sub>1</sub> representing the average inductor current, wherein the three operating point signals represent the operating point.

Referring to FIG. 10, in the converter stage 1 with boost topology, a series circuit with the inductor 12 and the electronic switch 11 is connected between the first input node  $\mathbf{1}_{IN1}$  and the second input node  $\mathbf{1}_{IN2}$  of the converter 55 stage 1. A series circuit with the rectifier element 13 and the capacitor 14 is connected in parallel with the electronic switch 11. The output voltage  $V_{OUT}$ , like in the buck topology shown in FIG. 9, is available across the capacitor 14. Like in the buck topology, the second input node  $1_{IN2}$ and the second output node  $\mathbf{1}_{OUT2}$  are formed by the same circuit node in the boost topology. During the on-period  $T_{ON}$ , that is, when the electronic switch 11 is switched on, a voltage across the inductor 12 substantially equals the input voltage  $V_{IN}$ , so that the slope of the inductor current I12 during the on-period is given by the input voltage  $V_{IN}$ divided by the inductance L, that is,

12

$$m_{ON} = \frac{V_{IN}}{L}.$$

(3a)

During the off-period  $T_{OFF}$ , that is, after the electronic switch 11 has been switched off, the voltage across the inductor 12 equals the input voltage  $V_{IN}$  minus the output voltage  $V_{OUT}$ . The slope of the inductor current I12 during the off-time is therefore given by

$$m_{OFF} = \frac{V_{IN} - V_{OUT}}{L}. ag{3b}$$

The output voltage  $V_{OUT}$  has a higher voltage level than the input voltage  $V_{IN}$  in the power converter circuit with the boost topology. Referring to equations (3a) and (3b), the input voltage  $V_{IN}$  and the output voltage  $V_{OUT}$  define the slopes of the inductor current, so that the operating point, besides the average inductor current  $I12_{AVG}$ , is defined by the input voltage  $V_{IN}$  and the output voltage  $V_{OUT}$ .

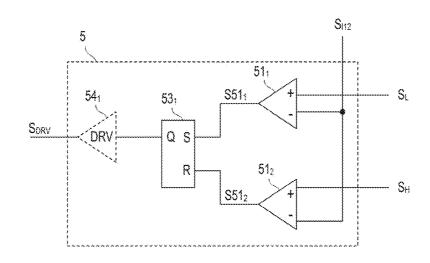

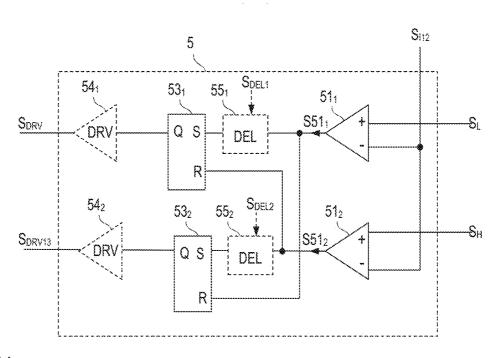

FIG. 11 illustrates one example of the hysteresis controller 5 configured to generate the drive signal  $S_{DRV}$  based on 25 the first and second thresholds  $\mathbf{S}_{H}$ ,  $\mathbf{S}_{L}$  received from the operating point controller 4 and the current measurement signal  $S_{I12}$ . In this example, the hysteresis controller 5 includes a first comparator 51, that receives the second threshold signal  $S_L$  and the current measurement signal  $S_{I12}$ , and a second comparator  $51_2$  that receives the current measurement signal  $S_{I12}$  and the first threshold signal  $S_H$ . A flip-flop 53, receives an output signal S51, of the first comparator 51, at a first input S and an output signal S51, of the second comparator  $51_2$  at a second input R. In this example, the first input S of the flip-flop 53<sub>1</sub> is a set input and the second input R is a reset input. The drive signal  $S_{DRV}$  is available at an output Q of the flip-flop 53<sub>1</sub>. Just for the purpose of illustration, the output Q of the flip-flop 53<sub>1</sub> is a non-inverting output in this example. Optionally, a driver  $54_1$  receives the output signal of the flip-flop  $53_1$  and generates the drive signal  $S_{DRV}$  based on this output signal. The driver  $54_1$  is configured to generate from the logic signal provided by the flip-flop  $53_1$  a drive signal  $S_{DRV}$  suitable to switch on and off the electronic switch 11. In the example shown in FIG. 11, the flip-flop 53<sub>1</sub> is set by the output signal  $S51_1$  of the first comparator  $S1_1$ , in order to switch on the electronic switch 11, each time the current measurement signal  $S_{I12}$  falls below the second threshold  $S_L$ . The flip-flop 53<sub>1</sub> is reset in order to switch off the electronic switch 11 when the current measurement signal  $S_{I12}$  reaches the first threshold  $S_H$ .

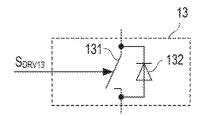

In the examples of the converter stage 1 shown in FIGS. 9 and 10 the rectifier element 13 is drawn as a passive rectifier element, in particular a bipolar diode. This, however, is only an example. According to another example, the rectifier element 13 is an active rectifier element. One example of an active rectifier element 13 is schematically illustrated in FIG. 12. This rectifier element 13 includes an electronic switch 131 that is controlled by a further drive signal  $S_{DRV13}$  and a passive rectifier element 132 such as a bipolar diode or a Schottky-diode connected in parallel with the electronic switch 131. Such active rectifier element 13 with an electronic switch 131 and a passive rectifier element 132 connected in parallel with the electronic switch 131 may also be referred to as synchronous rectifier (SR).

An active rectifier element 13 as shown in FIG. 12 may be implemented in various ways. Some examples are illus-

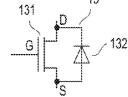

trated in FIGS. 13A to 13C. Referring to FIG. 13A, the active rectifier element 13 can be implemented as a MOS-FET (Metal Oxide Semiconductor Field-Effect Transistor). In this case, the rectifier element 132 can be formed by an integrated diode, which is often referred to as body diode, or by an additional rectifier element connected in parallel with a drain-source path D-S of the MOSFET. Just for the purpose of illustration, the MOSFET is drawn as an n-type MOSFET in the example shown in FIG. 13A. However, a p-type MOSFET may be used as well. According to another 10 example shown in FIG. 13B, the active rectifier element 13 may be implemented using an IGBT and a rectifier element connected in parallel with a collector-emitter path C-E of the IGBT. According to yet another example shown in FIG. 13C, the active rectifier element 13 may be implemented 15 using a HEMT (High Electron-Mobility Transistor) such as a gallium nitride-(GaN)-HEMT. The passive rectifier element 132 may be an inherent rectifier element, similar to the body diode in a MOSFET, and/or an additional passive rectifier element.

FIG. 14 shows one example of a hysteresis controller 5 configured to drive the electronic switch 11 by the drive signal  $S_{DRV}$  and the active rectifier element 13 by the further drive signal  $S_{DRV13}$ . The hysteresis controller 5 shown in FIG. 14 is based on the hysteresis controller shown in FIG. 25 11 and additionally includes a further flip-flop 53, that generates the further drive signal  $S_{DRV13}$ . Optionally, a drive circuit 542 generates the further drive signal  $S_{DRV13}$  from an output signal of the further flip-flop 532. The further flip-flop 53<sub>2</sub> receives the output signal S51<sub>2</sub> of the second comparator 30  $51_2$  at a first input and the output signals  $51_1$  of the first comparator  $51_1$  at a second input. The first input S is a set input and the second input R is a reset input in this example. The hysteresis controller 5 shown in FIG. 14 is configured to drive the electronic switch 11, which is also referred to as 35 first electronic switch in the following, and the electronic switch 131, which is also referred to as second electronic switch in the following, of the active rectifier element 13 such that only one of the first electronic switch 11 and the second electronic switch in the active rectifier element 13 is 40 switched on at the same time. In the example shown in FIG. 14 this is achieved in that the first comparator signal 51, resets the further flip-flop 53<sub>2</sub> in order to switch off the active rectifier element 13 and sets the first flip-flop 53, in order to switch on the electronic switch 11 it. Equivalently, when the 45 second comparator signal S51<sub>2</sub> sets the second flip-flop 53<sub>2</sub> in order to switch on the active rectifier element 13 it resets the first flip-flop 53, in order to switch off the electronic switch 11. Optionally, a first delay element 55<sub>1</sub> is connected between the first comparator 51, and the first input S of the 50 first flip-flop 531, and a second delay element 552 is connected between the second comparator 51<sub>2</sub> and the first input of the second flip-flop  $53_2$ . The first delay element  $55_1$ causes a delay time between a time instance when the first comparator signal S51<sub>1</sub> resets the second flip-flop 53<sub>2</sub> in 55 order to switch off the active rectifier element 13, that is, to switch off the second electronic switch, and a time instance when the first flip-flop 53<sub>1</sub> is set in order to switch on the electronic switch. Equivalently, the second delay element 55<sub>2</sub> causes a delay time between a time instance when the 60 first flip-flop 53, is reset in order to switch off the first electronic switch 11 and a time instance when the second flip-flop 53<sub>2</sub> is set in order to switch on the second electronic switch in the active rectifier element 13. These delay elements 55<sub>1</sub>, 55<sub>2</sub> therefore cause a delay time between time instances when one of the first electronic switch 11 and the rectifier element 13 with the second electronic switch

14

switches off and the other one of the first electronic switch 11 and the active rectifier element 13 with the second electronic switch switches on in order to prevent that the first electronic switch 11 and the active rectifier element 13 are switched on at the same time. After the first electronic switch 11 has been switched off and before the second electronic switch 131 switches on, for example, a current may flow through the passive rectifier element 132 of the active rectifier element 13.

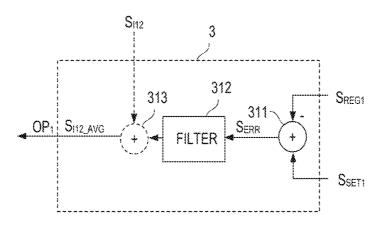

One example of the operating parameter controller 3 is shown in FIG. 15. In this example, the operating parameter controller 3 receives one operating parameter signal  $S_{REG1}$ and a corresponding setpoint signal  $S_{SET1}$ . The operating parameter signal  $S_{REG1}$  represents the operating parameter that is to be regulated. The operating parameter signal represents, for example, the output voltage  $\mathbf{V}_{OUT}$  or the input voltage  $V_{IN}$  of the converter stage 1 and can be obtained by measuring the respective operating parameter using a suitable measurement circuit such as a voltage measurement 20 circuit. Referring to FIG. 15, the operating parameter controller 3 includes a calculation unit 311 that generates an error signal  $S_{ERR}$  by calculating a difference between an instantaneous signal level of the operating parameter signal  $S_{REG1}$  and the signal level of the setpoint signal  $S_{SET1}$ . A filter 312 receives the error signal  $S_{ERR}$  and outputs the first operating point signal OP<sub>1</sub>. Referring to the above, this first operating point signal OP<sub>1</sub>, which is also referred to as  $S_{I12\ AVG}$  in the example shown in FIG. 15, represents the desired average current level  $I12_{AVG}$  of the inductor current I12. An operating parameter controller 3 of the type shown in FIG. 15 may be used in a DC/DC power converter circuit in which the converter stage 1 receives a direct input voltage  $V_{IN}$  and generates a direct output voltage  $V_{OUT}$  based on the direct input voltage.

Optionally, the operating parameter controller 3 includes a feed-forward loop with an adder 313 that adds a current measurement signal  $S_{1OUT}$  representing the output current  $I_{OUT}$  of the converter stage to the output signal of the filter 312. In this example, not the output signal of the filter 312 but an output signal of the adder 313 represents the desired level of the average inductor current  $I12_{AVG}$ , that is, is the first operating point signal  $OP_1$ . According to one example, the current measurement signal  $S_{IOUT}$  is proportional to the inductor current I12. This current measurement signal  $S_{IOUT}$  may be obtained by using any type of current measurement circuit.

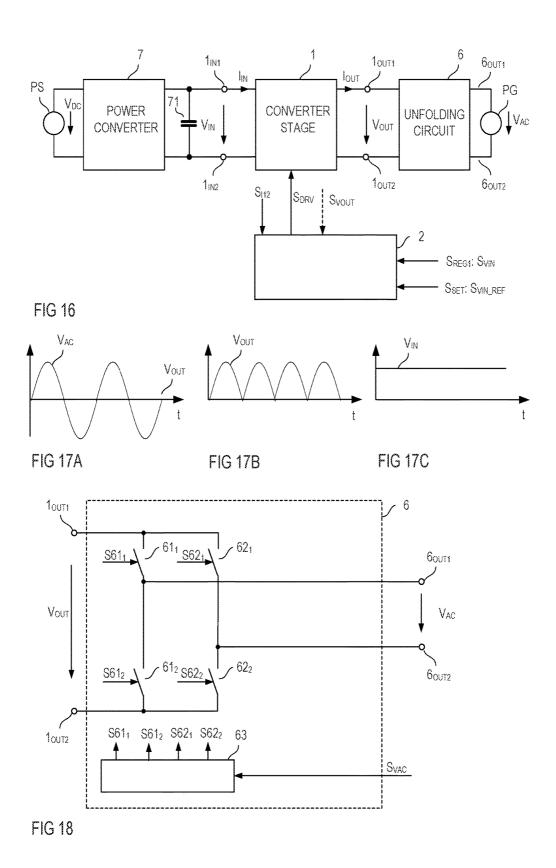

FIG. 16 shows one example of a power converter circuit in which the first power converter with the converter stage 1 and the control circuit 2 is part of a DC/AC converter. This DC/AC converter, besides the converter stage 1 and the control circuit 2, includes an unfolding circuit 6 connected between the output  $\mathbf{1}_{OUT1}$ ,  $\mathbf{1}_{OUT2}$  of the converter stage  $\mathbf{1}$ and a power grid PG. In this power converter circuit, the converter stage 1 drives the output current  $I_{OUT}$  via the unfolding circuit 6 into the power grid PG, wherein the output voltage  $V_{OUT}$  of the converter stage 1 is defined by an alternating voltage  $\mathbf{V}_{AC}$  provided by the power grid PG. Example waveforms of the alternating voltage  $V_{AC}$  provided by the power grid, the output voltage  $V_{OUT}$  of the converter stage 1, and the input voltage  $V_{I\!N}$  of the converter stage 1 are shown in FIGS. 17A, 17B and 17C, respectively. The output voltage V<sub>OUT</sub> of the converter stage 1 is a rectified sinusoidal voltage in this example, wherein this rectified sinusoidal output voltage  $V_{OUT}$  is provided by the unfolding circuit 6 based on the alternating voltage  $V_{AC}$  of the power grid PG. According to one example, the control circuit 2 is configured to regulate the input voltage  $V_{IN}$  and to generate the output

current  $I_{OUT}$  such that it is in phase with the output voltage  $V_{OUT}$  as defined by the grid voltage  $V_{AC}$ . According to one example, the converter stage 1 has a buck topology as shown in FIG. 9. The input power received by the converter stage 1, which is given by the input voltage  $V_{IN}$  multiplied with the input current  $I_{IN}$  is supplied by a further power converter 7 from a power source PS. According to one example, the power source PS is a DC power source, such as a photovoltaic (PV) panel. The further power converter 7 may be configured to regulate the voltage  $V_{DC}$  provided by the power source PS such that the power source PS operates in a maximum power point. Power converters configured to operate a DC load, such as a photovoltaic panel, in a maximum power point are commonly known, so that no further explanations are required in this regards.

One example of the unfolding circuit  $\bf 6$  is shown in FIG. 18. Referring to FIG. 18, the unfolding circuit includes a full bridge with two half bridges each including a high side switch  $\bf 61_1$ ,  $\bf 62_1$  and a low side switch  $\bf 61_2$ ,  $\bf 62_2$ . Each of these half bridges is connected between the first output node  $\bf 1_{OUT1}$  and the second output node  $\bf 1_{OUT2}$  of the converter stage 1. An output of each half bridge is formed by a circuit node common to the high side switch  $\bf 61_2$ ,  $\bf 62_2$ . The output of a first half bridge  $\bf 61_1$ ,  $\bf 61_2$  is connected to a first output node  $\bf 6_{OUT1}$  of the unfolding 25 circuit  $\bf 6$ , and the output of a second half bridge  $\bf 62_1$ ,  $\bf 62_2$  is coupled to a second output node  $\bf 6_{OUT2}$  of the unfolding circuit  $\bf 6$ . The unfolding circuit  $\bf 6$  is configured to be connected to the power grid via the first output node  $\bf 6_{OUT1}$  and the second output node  $\bf 6_{OUT2}$ .

A control circuit 63 drives the switches  $61_1$ ,  $61_2$ ,  $62_1$ ,  $62_2$ of the two half bridges based on a grid voltage signal  $S_{VAC}$ . This grid voltage signal  $S_{V\!AC}$  indicates if the grid voltage V<sub>A</sub>C is positive or negative, that is, the grid voltage signal  $S_{V\!AC}$  indicates the positive halfwave and the negative halfwave of the grid voltage  $V_{AC}$ . When the grid voltage signal  $S_{V\!AC}$  indicates the positive halfwave of the grid voltage  $V_{AC}$ it switches on the high side switch 61, of the first half bridge and the low side switch 62, of the second half bridge and switches off the high side switch  $62_1$  of the second half 40 bridge and the low side switch  $61_2$  of the first half bridge. During the negative halfwave of the grid voltage  $V_{AC}$ , the control circuit 63 switches on the high side switch  $62_1$  of the second half bridge and the low side switch 61<sub>2</sub> of the first half bridge and switches off the high side switch  $\mathbf{61}_1$  of the 45 first half bridge and the low side switch  $61_2$  of the second half bridge. The control circuit 63 drives the individual high side and low side switches by generating drive signals  $S61_1$ ,  $S61_2$ ,  $S62_1$ ,  $S62_2$  received by these switches.

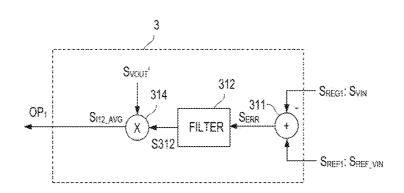

Referring to the above, in the power converter circuit 50 shown in FIG. 16, the converter stage 1 may be implemented with a buck topology as shown in FIG. 9. In the buck converter topology shown in FIG. 9, the output current  $I_{OUT}$ equals the average inductor current  $I12_{AVG}$ . In the power converter circuit shown in FIG. 16, it is desired that the 55 signal waveform of the output current  $I_{OUT}$  follows the waveform of the output voltage  $V_{\it OUT}$ . That is, it is desired to generate the output current  $I_{OUT}$  and, therefore, the average inductor current  $I12_{AVG}$  with a rectified sinusoidal waveform. One example of an operating parameter controller that may be implemented in the control circuit 2 shown in FIG. 16 is illustrated in FIG. 19. This operating parameter controller 3 is configured to generate the first operating point signal OP<sub>1</sub> that represents the average inductor current such that the input voltage  $V_{I\!N}$  is regulated and the average inductor I12<sub>AVG</sub> current has the waveform of a rectified sinusoidal signal. The first parameter signal  $S_{REG1}$  is a signal

16

$S_{V\!I\!N}$  that represents the input voltage  $V_{I\!N}$ . The setpoint signal  $S_{SET1}$  is a signal  $S_{SET\ VIN}$  that represents a desired voltage level of the input voltage  $V_{I\!N}$ . The operating parameter controller 3 shown in FIG. 19 is based on the operating parameter controller shown in FIG. 15 and includes the calculator 311 that calculates the difference between the setpoint signal  $S_{SET1}$  and the operating parameter signal  $S_{REG1}$  in order to generate the error signal  $S_{ERR}$ . A filter 312 filters the error signal  $S_{ERR}$ . Like in the example shown in FIG. 15, the filter 312 may have one of a proportional (P) characteristic, a proportional-integrative (PI) characteristic, a proportional-integrative, derivative (PID) characteristic, or the like. A multiplier 314 multiplies a filter output signal S312 with a signal  $S_{VOUT}$  that represents a signal waveform of the output voltage  $V_{\ensuremath{\textit{OUT}}}$  in order to generate the first operating point signal OP<sub>1</sub>, which represents the desired average current level of the inductor current I12. This operating point signal  $OP_1$  varies as the output voltage  $V_{OUT}$ (which is defined by the grid voltage  $V_{AC}$ ) varies. That is, in this example, the operating point signal OP<sub>1</sub> has the waveform of a rectified sinusoidal signal, wherein an amplitude is defined by the filter output signal S312 in order to regulate the input voltage  $V_{IN}$ . According to one example, the signal  $S_{\emph{VOUT}}$  is proportional to the output voltage  $V_{\emph{OUT}}$ . According to another example, the signal  $S_{VOUT}$  is a normalized signal that represents the waveform of the output voltage V<sub>OUT</sub>, but has a predefined amplitude. According to one example, the signal S<sub>VOUT</sub> is obtained by measuring the output voltage VOUT and by dividing the obtained signal by the voltage level of the input voltage  $V_{IN}$ .

Referring to the explanation of FIG. 9, in a buck converter, which may be used in the converter stage shown in FIG. 16, the operating point is defined by the average inductor current I12<sub>AVG</sub>, the input voltage  $V_{IN}$ , and the output voltage  $V_{OUT}$ . Thus, in the power converter circuit shown in FIG. 16, the control circuit, additionally to the current measurement circuit  $S_{I12}$  and the input voltage signals  $S_{VIN}$ , may receive an output voltage signal  $S_{VOUT}$  representing the output voltage  $V_{OUT}$  in order to detect the operating point.

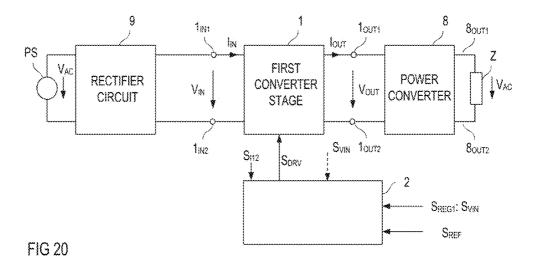

FIG. 20 shows a power converter circuit with a converter stage 1 and a control circuit 2 controlling operation of the converter stage 1 according to another example. In this example, the power converter circuit further includes a rectifier circuit 9 connected between a power source and the input  $1_{IN1}$ ,  $1_{IN2}$  of the converter stage 1 and the further power converter 8 connected between the output  $1_{OUT1}$ ,  $\mathbf{1}_{OUT2}$  of the converter stage 1 and a load Z. According to one example, the power source PS provides an alternating voltage  $V_{AC}$  with a sinusoidal waveform. The rectifier circuit 9 is configured to rectify the received alternating voltage  $V_{AC}$  such that the input voltage  $V_{IN}$  received by the converter stage 1 has the waveform of a rectified sinusoidal signal. Further, the control circuit 2 is configured to control operation of the converter stage 1 such that the output voltage V<sub>OUT</sub> is a regulated DC voltage. Examples of signal waveforms of the alternating voltage  $V_{AC}$  received by the rectifier circuit 9, the input voltage  $V_{I\!N}$  received by the converter stage 1 and the output voltage  $V_{OUT}$  provided by the converter stage 1 are shown in FIGS. 21A, 21B and 21C, respectively. According to one example, the converter stage 1 has a boost converter topology as shown in FIG. 10 and the control circuit 2 is configured to control operation of the converter stage 1 such that a signal waveform of the input current  $I_{IN}$  of the converter stage 1 is in phase with the input voltage  $V_{IN}$ . This is equivalent to controlling operation of

the converter stage 1 such that the average inductor current  $I12_{AVG}$  is in phase with the input voltage  $V_{IN}$ .

An operating parameter controller that is configured to suitably generate the first operating point signal  $OP_1$  such that the average inductor current  $I12_{AVG}$  is in phase with the input voltage  $V_{IN}$  as shown in FIG. 22. This operating parameter controller 3 is based on the operating parameter controller shown in FIG. 19 and is different from this operating parameter controller in that the regulated operating parameter is the output voltage  $V_{OUT}$  so that the operating parameter signal  $S_{REG1}$  is a signal  $S_{VOUT}$  that represents the output voltage  $V_{OUT}$ . Consequently, the setpoint signal  $S_{SET_1}$  is a signal  $S_{SET_2VOUT}$  that represents the desired voltage level of the output voltage  $V_{OUT}$ . Further, the multiplier 314 receives a signal  $S_{VIN}$  representing the input voltage  $V_{IN}$  besides the filter output signal S312 in order to generate the first operating point signal  $OP_1$ .

Referring to the explanation provided in connection with FIG. 10, in a boost converter, which may be used in the  $_{20}$  converter stage shown in FIG. 20, the operating point is defined by the average inductor current  $\rm I12_{\it AVG}$ , the input voltage  $\rm V_{\it IN}$ , and the output voltage  $\rm V_{\it OUT}$ . Thus, in the power converter circuit shown in FIG. 20, the control circuit, additionally to the current measurement circuit  $\rm S_{\it II.2}$  and the 25 output voltage signals  $\rm S_{\it VOUT}$ , may receive an input voltage signal  $\rm S_{\it VDV}$  representing the input voltage  $\rm V_{\it IN}$  in order to detect the operating point.

In the power converter circuit shown in FIG. 16 the output voltage  $V_{OUT}$  has the waveform of a rectified sinusoidal 30 signal, and in the power converter circuit shown in FIG. 20 the input voltage  $V_{IN}$  has the waveform of a rectified sinusoidal signal. In both power converter circuits, the average inductor current I12 $_{AVG}$  is regulated such that it has the waveform of a rectified sinusoidal signal that is essentially in phase with the input voltage  $V_{IN}$  or the output voltage  $V_{OUT}$ . In these power converter circuits, the operating point periodically varies due to the varying input voltage  $V_{IN}$  or output voltage  $V_{OUT}$ . The instantaneous input power and output power varies in accordance with a sine 40 square signal in these power converter circuits.

FIG. 23A illustrates the optimum switching frequency  $f_{S,opt}$  obtained by testing a power converter circuit of the type shown in FIG. 16 over one period of the rectified sinusoidal output voltage  $V_{OUT}$ . FIG. 23A shows the opti- 45 mum switching frequencies  $f_{S,opt}$  that were obtained by testing the power converter circuit at three different average output powers P1, P2, and P3. The "average output power" is the output power averaged over one period of the output voltage  $V_{OUT}$ . In the examples shown in FIG. 23A, a first 50 output power P1 is greater than a second output power P2, and the second output power P2 is greater than a third output power P3, that is, P1>P2>P3. In FIG. 23A, a curve labeled with OFM@P1 denotes the optimum switching frequency at the first output power P1, the curve labeled with OFM@P2 55 shows the optimum switching frequency at the second output power P2, and the curve labeled with OFM@P3 denotes the optimum switching frequency at the third output power P3. As can be seen from FIG. 23A, in each case, the switching frequency varies over one period of the output voltage, wherein a maximum switching frequency increases as the output power decreases. That is, the maximum switching frequency at the third output power P3 is higher than a maximum switching frequency at the second output power P2, and the maximum switching frequency at the second output power P2 is greater than the maximum switching frequency at the first output power P1.

18

Referring to the above, each optimum switching frequency obtained at one operating point is associated with a first threshold  $S_H$  and a second threshold  $S_L$ . The first and second thresholds associated with the curves of the optimum switching frequencies shown in FIG. 23A are illustrated in FIGS. 23B, 23C and 23D. FIG. 23B shows the first threshold and the second threshold obtained by testing the power converter circuit at the first output power P1, FIG. 23C shows the first threshold and the second threshold obtained by testing the power converter circuit at the second power P2, and FIG. 23D shows the first threshold and the second threshold obtained by testing the power converter circuit at the third power P3. In each of FIGS. 23B, 23C and 23D, the curve labeled with  $\mathbf{S}_{H}$ , OFM illustrates the first threshold over one period of the output voltage, and the curve labeled with  $S_L$ , OFM illustrates the second threshold over one period of the output voltage. Referring to FIGS. 23B, 23C and 23D, dependent on the instantaneous output power of the power converter circuit, the second threshold  $S_L$  can be negative. A negative second threshold  $S_L$  and an associated positive first threshold  $S_H$  is equivalent to that the inductor current I12 reverses its direction during one switching period. This may be associated with a zero voltage switching (ZVS). That is, towards the end of the switching period, the inductor current may discharge the parasitic capacitance (see FIG. 1) of the electronic switch 11 so that a voltage across the electronic switch 11 is essentially zero when the electronic switch 11 switches on at the beginning of the next switching period (drive period).

For comparison reasons, the power converter circuit underlying the curves shown in FIGS. 23A to 23D was also operated at a fixed switching frequency, so that only the duty cycle was varied. The curve that illustrates the switching frequency used in this scenario is labeled with PWM in FIG. 23A. When operating the power converter circuit at the fixed switching frequency the maximum inductor current and the minimum inductor current in each drive circle was detected. These maximum and minimum current correspond to the first and second threshold in a power converter circuit operated at the optimum switching frequency. These maximum and minimum inductor currents at the different operating points of the power converter circuit are also illustrated in FIGS. 23B, 23C and 23D. In each of these Figures, curves labeled with S<sub>H</sub>, PWM illustrate the maximum inductor currents, and curves labeled with  $S_L$ , PWM illustrate the minimum inductor currents. As can be seen from FIGS. 23B, 23C and 23D, this maximum and minimum inductor currents observed at the fixed switching frequency deviate from the maximum and minimum inductor currents (which are given by the first and second thresholds  $S_H$ ,  $S_L$ ) in a power converter circuit operated at the optimum switching frequency.

It can be shown that operating the power converter circuit at the optimum switching frequency results in lower power losses. This is illustrated in FIG. 23E. FIG. 23E illustrates the power losses that were measured over one period of the output voltage at the three different output powers P1, P2, and P3. In FIG. 23E, a curve labeled with OFM@P1 illustrates the power losses measured when operating the power converter circuit at the first output power P1 and when operating the power converter circuit at the optimum switching frequency. A curve labeled with PWMR@P1 illustrates the power losses that were measured when operating the power converter circuit at the fixed switching frequency. As can be seen from FIG. 23E, operating the power converter circuit at the optimum switching frequency results in lower power losses. The same applies when

operating the power converter circuit at the second output power P2 and the third output power P3.

FIG. 23F illustrates different types of losses that may occur in operation of the power converter circuit. These losses include conductional losses, switching losses, losses in a core of the inductor, DC current losses in the inductor and high frequency (HF) current losses in the inductor, and other types of losses that are summarized by auxiliary losses in FIG. 23F. FIG. 23F compares the losses occurring in a power converter circuit operated at a fixed switching frequency (the diagram labeled with PWM in FIG. 23F) and losses occurring in the power converter circuit when operated at the optimum switching frequency (the diagram labeled with OFM in FIG. 23F). The diagrams shown in FIG. 23F show the power losses that were observed in the 15 two different operation scenarios (fixed frequency and optimum frequency) at the same output power. As can be seen from FIG. 23F particularly the switching losses decrease when operating the power converter circuit at the optimum switching frequency instead of the fixed switching fre- 20

FIG. 24 shows one example of a first power converter that includes two converter stages  $\mathbf{1}_1$ ,  $\mathbf{1}_2$  each having a buck topology. These two converter stages  $1_1$ ,  $1_2$  may be used in a power converter circuit of the type shown in FIG. 16 25 instead of one converter stage 1 and the unfolding circuit 6. Each of these converter stages  $1_1$ ,  $1_2$  includes an electronic switch  $11_1$ ,  $11_2$ , an active rectifier element  $13_1$ ,  $13_2$  and an inductor  $12_1$ ,  $12_2$ . Inputs  $1_{IN1\_1}$ ,  $1_{IN2\_1}$ ,  $1_{IN1\_2}$ ,  $1_{IN1\_2}$  of these converter stages are connected in parallel so that each 30 converter stage receives the input voltage  $V_{DV}$ . Further, second output nodes  $1_{OUT2\_1}$ ,  $1_{OUT2\_2}$  of the two converter stages  $\mathbf{1}_1$ ,  $\mathbf{1}_2$  are connected with each other and connected to the second input nodes  $\mathbf{1}_{IN2_{-1}}$ ,  $\mathbf{1}_{IN2_{-2}}$ . An output of the arrangement with the two converter stages  $\mathbf{1}_1$ ,  $\mathbf{1}_2$  is formed 35 by the first output node  $1_{OUT1\_1}$  of the first converter stage  $\mathbf{1}_1$  and the first output node  $\mathbf{1}_{OUT1\_2}$  of the second converter stage 12, wherein the power grid PG may be connected to this output.

Each of the two converter stages  $\mathbf{1}_1$ ,  $\mathbf{1}_2$  is controlled by a 40 respective control circuit  $\mathbf{2}_1$ ,  $\mathbf{2}_2$ . The power converter further includes an activation/deactivation circuit  $\mathbf{2}_0$  configured to activate and deactivate the control circuits  $2_1$ ,  $2_2$  dependent on an output voltage signal  $S_{VOUT}$  that indicates if the output voltage  $V_{OUT}$ , which essentially equals the grid voltage  $V_{AC}$ , 45 has a positive halfwave or a negative halfwave. During the positive halfwave, the activation/deactivation circuit  $\mathbf{2}_0$  activates the control circuit  $\mathbf{2}_1$  of the first converter stage  $\mathbf{1}_1$  and deactivates the control circuit  $2_2$  of the second converter stage  $\mathbf{1}_2$ . During the negative halfwave, the activation/ 50 deactivation circuit  $\mathbf{2}_0$  activates the control circuit  $\mathbf{2}_2$  of the second converter stage 1<sub>2</sub> and deactivates the control circuit  $2_1$  of the first converter stage  $1_1$ . The control circuit that is activated operates the corresponding converter stage as explained before. The control circuit that is deactivated 55 permanently switches on the rectifier element 13<sub>1</sub>, 13<sub>2</sub> of the corresponding converter stage.