#### US010177681B2

# (12) United States Patent

Neumayr et al.

# (54) POWER CONVERTER INCLUDING AN AUTOTRANSFORMER AND POWER CONVERSION METHOD

(71) Applicant: Infineon Technologies Austria AG,

Villach (AT)

(72) Inventors: Dominik Neumayr, Zurich (CH);

Dominik Bortis, Zurich (CH); Mattia Guacci, Zurich (CH); Johann Kolar, Zurich (CH); Michael Leibl, Zurich (CH); Gerald Deboy, Klagenfurt (AT)

(73) Assignee: Infineon Technologies Austria AG,

Villach (AT)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/192,449

(22) Filed: Jun. 24, 2016

(65) Prior Publication Data

US 2017/0373608 A1 Dec. 28, 2017

(51) Int. Cl.

H02M 7/48

(2007.01)

H02M 1/00

(2006.01)

H02M 3/335

(2006.01)

(52) U.S. Cl.

CPC ...... *H02M* 7/4826 (2013.01); *H02M* 3/33569 (2013.01); *H02M* 2001/0058 (2013.01); *H02M* 2007/4818 (2013.01); *Y02B* 70/1425 (2013.01); *Y02B* 70/1441 (2013.01)

(58) Field of Classification Search

CPC ........ H02M 2001/0058; H02M 3/158; H02M 3/33569; H02M 7/04; H02M 7/4826; H02M 2007/4818; Y02B 70/1425; Y02B 70/1433; Y02B 70/1491; Y02B 70/1441

See application file for complete search history.

# (10) Patent No.: US 10,177,681 B2

(45) **Date of Patent: Jan. 8, 2019**

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

(Continued)

#### OTHER PUBLICATIONS

Grant, Duncan Andrew et al., "Synthesis of Tapped-Inductor Switched-Mode Converters", IEEE Transactions on Power Electronics, vol. 22, No. 5, Sep. 2007, pp. 1964-1969.

(Continued)

Primary Examiner — Fred E Finch, III

Assistant Examiner — Demetries A Gibson

(74) Attorney, Agent, or Firm — Murphy, Bilak & Homiller, PLLC

## (57) ABSTRACT

A power converter circuit includes a chopper circuit configured to receive an input voltage and generate a chopper voltage with an alternating voltage level based on the input voltage, an autotransformer including at least one tap, the autotransformer being coupled to the chopper circuit and configured to generate a tap voltage at the at least one tap, and a selector circuit configured to receive a plurality of voltage levels. At least one of these the voltage levels is based on the at least one tap voltage. The selector circuit is further configured to generate a selector output voltage based on the plurality of voltage levels such that the selector circuit selects two of the plurality of voltage levels and switches at a switching frequency between the two voltage levels.

# 23 Claims, 14 Drawing Sheets

# (56) References Cited

## U.S. PATENT DOCUMENTS

| 6,153,863 A    | 4 *  | 11/2000 | Snowball H05B 6/062  |

|----------------|------|---------|----------------------|

|                |      |         | 219/626              |

| 8,723,365 E    | 32*  | 5/2014  | Bordry H02J 7/345    |

| -,,            | _    |         | 307/77               |

| 8,730,700 E    | 22 * | 5/2014  | Yuzurihara H02M 7/48 |

| 6,730,700 E    | 32   | 3/2014  |                      |

|                |      |         | 363/132              |

| 8,836,228 E    | 32   | 9/2014  | Xu et al.            |

| 9,343,994 E    | 32 * | 5/2016  | Hosokawa H01F 30/04  |

| 2010/0220501 A | 41*  | 9/2010  | Krause H02M 3/33584  |

|                |      |         | 363/17               |

| 2012/0287678 A | 41*  | 11/2012 | Xu H02M 3/158        |

|                |      |         | 363/17               |

|                |      |         | 303/1/               |

# OTHER PUBLICATIONS

Gu, Yilei et al., "Voltage Doubler Application in Isolated Resonant Converters", 31st Annual Conference of IEEE Industrial Electronics Society, Nov. 2005, IECON 2005, pp. 1184-1188.

Hesterman, Bryce, "Analysis and Modeling of Magnetic Coupling", Denver Chapter, IEEE Power Electronics Society, University of Colorado, Boulder, Colorado, Apr. 10, 2007, pp. 1-93. Jung, Jee-Hoon et al., "High Efficiency Bidirectional LLC Resonant

Jung, Jee-Hoon et al., "High Efficiency Bidirectional LLC Resonant Converter for 380V DC Power Distribution System Using Digital Control Scherne", 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, Feb. 2012, pp. 532-538.

<sup>\*</sup> cited by examiner

FIG 4

FIG 7

FIG 8

FIG 9

FIG 11

FIG 12

FIG 13

FIG 14A FIG 14B

FIG 19

FIG 20

FIG 22

# POWER CONVERTER INCLUDING AN AUTOTRANSFORMER AND POWER CONVERSION METHOD

## TECHNICAL FIELD

This disclosure in general relates to a power converter and a power conversion method.

## BACKGROUND

Power conversion is an important issue in today's power supply systems. DC/AC power conversion is one type of power conversion which involves converting DC power into AC power. The DC power is provided by a DC power source 15 such as, for example, photovoltaic (PV) panels, batteries or the like. The AC power may be fed into a power grid or used to drive a motor, to name only two examples.

An important aspect in every type of power conversion is to efficiently convert the power, that is, to keep losses that 20 may occur in connection with the power conversion as low as possible.

#### **SUMMARY**

One example relates to a power converter circuit. The power converter circuit includes a chopper circuit configured to receive an input voltage and generate a chopper voltage with an alternating voltage level based on the input voltage, an autotransformer with at least one tap, wherein 30 the autotransformer is coupled to the chopper circuit and configured to generate a tap voltage at the at least one tap, and a selector circuit configured to receive a plurality of voltage levels. At least one of the voltage levels is based on the at least one tap voltage, and the selector circuit is 35 configured to generate a selector output voltage based on the plurality of voltage levels such that the selector circuit selects two of the plurality of voltage levels and switches at a switching frequency between the two voltage levels.

One example relates to a method. The method includes 40 receiving an input voltage and generating a chopper voltage with an alternating voltage level based on the input voltage by a chopper circuit, generating a tap voltage at the at least one tap by an autotransformer coupled to the chopper circuit, receiving a plurality of voltage levels by a selector circuit, 45 the con wherein at least one of the voltage levels is based on the at least one tap voltage, and generating a selector output voltage based on the plurality of voltage levels by the selector circuit such that a voltage level of the selector output voltage alternates at a switching frequency between 50 FIG. 8; two selected ones of the plurality of voltage levels.

Another example relates to a power converter circuit. The power converter circuit includes a chopper circuit configured to receive an input voltage and generate a chopper voltage with an alternating voltage level based on the input 55 voltage and with a chopper frequency, an autotransformer comprising at least one tap, wherein the autotransformer is coupled to the chopper circuit and configured to generate a tap voltage at the at least one tap, and a selector circuit configured to receive a plurality of voltage levels, wherein 60 at least one of the voltage levels is based on the at least one tap voltage. The selector circuit is configured to generate a selector output voltage based on the plurality of voltage levels. The power converter circuit includes at least one series resonant circuit excited by the chopper voltage, 65 wherein parameters of the at least one series resonant circuit are adapted to the chopper frequency such that the chopper

2

frequency substantially equals a resonant frequency of the at least one series resonant circuit.

Yet another example relates to a method. The method includes receiving an input voltage and generating a chopper voltage with an alternating voltage level based on the input voltage and with a chopper frequency by a chopper circuit, receiving the chopper voltage and generating at least one tap voltage based on the chopper voltage by an autotransformer, and receiving a plurality of voltage levels by a selector circuit, wherein at least one of the voltage levels is based on the at least one tap voltage, and generating a selector output voltage based on the plurality of voltage levels by the selector circuit. The chopper frequency substantially equals a resonant frequency of at least one series resonant circuit that includes a parasitic inductance of the autotransformer.

Those skilled in the art will recognize additional features and advantages upon reading the following detailed description, and upon viewing the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Examples are explained below with reference to the drawings. The drawings serve to illustrate certain principles, so that only aspects necessary for understanding these principles are illustrated. The drawings are not to scale. In the drawings the same reference characters denote like features.

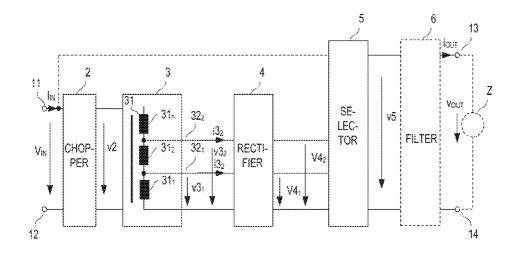

FIG. 1 shows one example of a power converter circuit that includes a chopper circuit, an autotransformer circuit, a rectifier circuit, and a selector circuit;

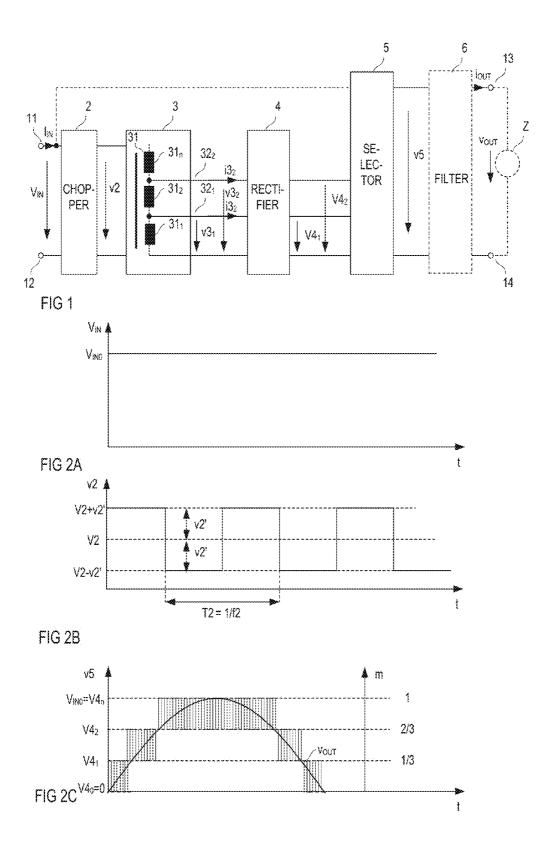

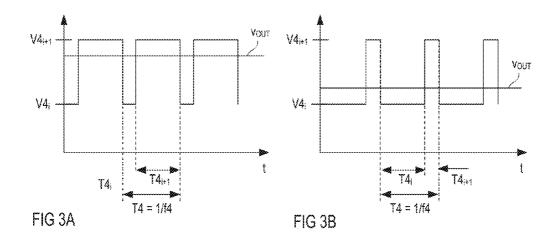

FIGS. 2A-2C show examples of timing diagrams of an input voltage, a chopper output voltage and a selector output voltage in the power converter circuit shown in FIG. 1;

FIGS. 3A and 3B show examples of timing diagrams of an output voltage of the rectifier circuit in the power converter circuit shown in FIG. 1;

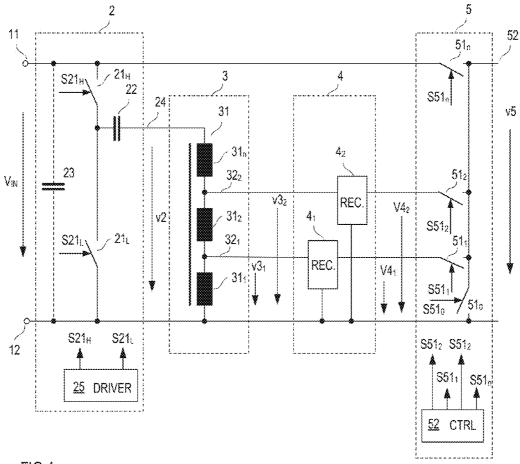

FIG. 4 shows examples of the chopper circuit, the autotransformer circuit, the rectifier circuit, and the selector circuit in greater detail;

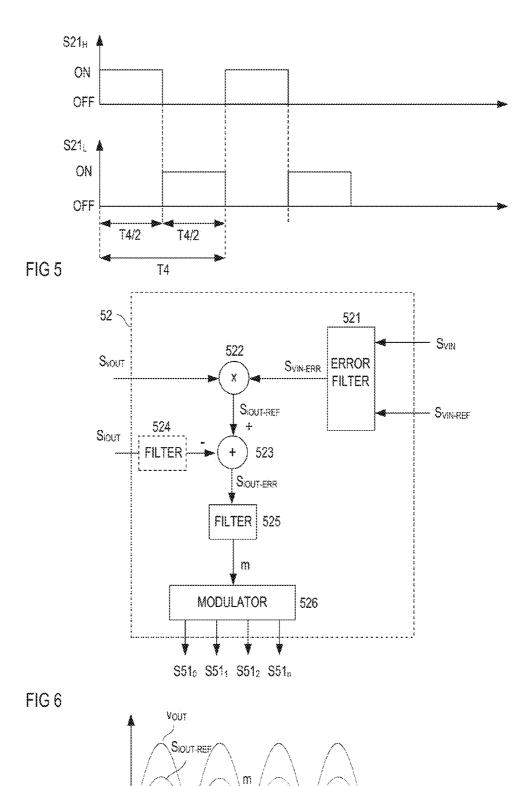

FIG. 5 shows timing diagrams of the drive signals of a half-bridge included in the chopper circuit shown in FIG. 4;

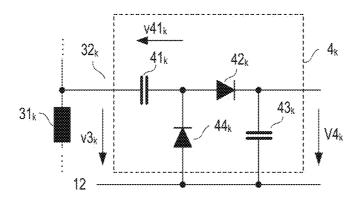

FIG. 6 shows one example of a controller in the selector circuit shown in FIG. 5;

FIG. 7 shows examples of timing diagrams of signals in the controller circuit shown in FIG. 6;

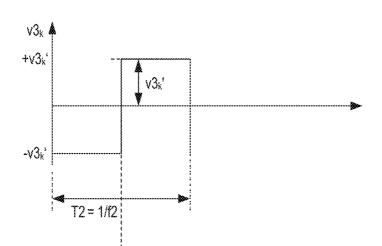

FIG. 8 shows one example of a rectifier stage in the rectifier circuit shown in FIG. 5;

FIG. 9 illustrates one example of a timing diagram of a tap voltage received at an input of the rectifier stage shown in FIG. 8:

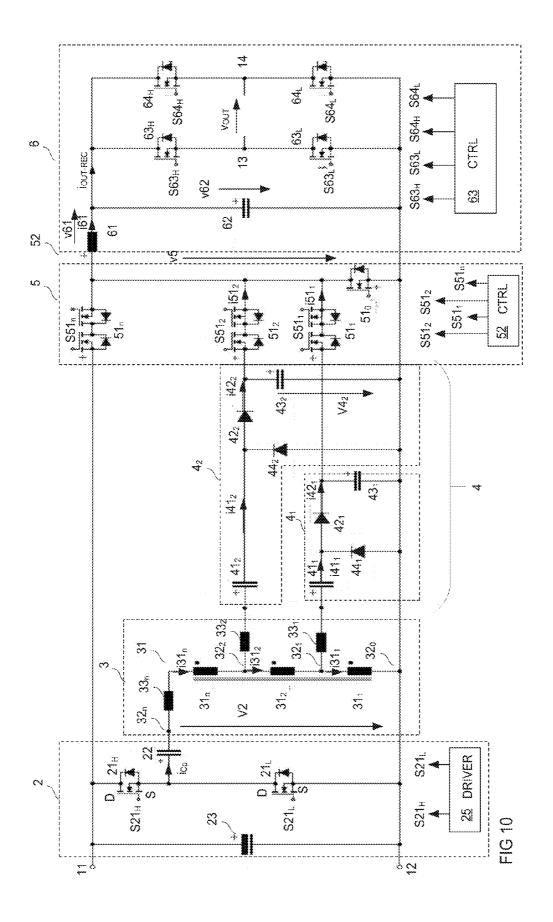

FIG. 10 shows one example of a power converter circuit that is based on the power converter circuit shown in FIG. 5 and includes an optional filter circuit, which is illustrated in greater detail;

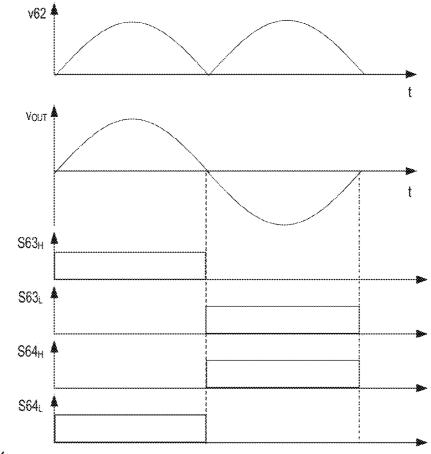

FIG. 11 shows timing diagrams that illustrate one way of operation of an unfolding circuit in the filter circuit shown in FIG. 10;

FIGS. 12-14B show timing diagrams of signals occurring in the power converter circuit shown in FIG. 10;

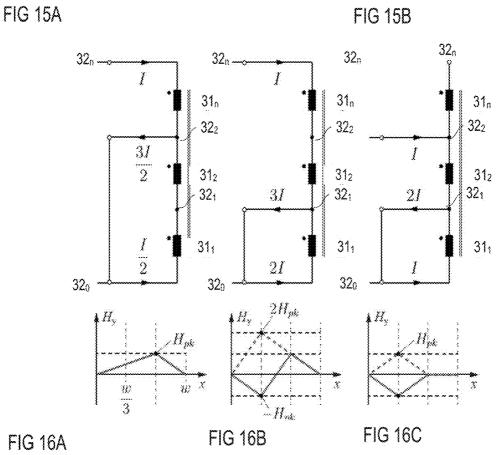

FIGS. 15A and 15B illustrate one method for determining parasitic inductances of an autotransformer;

FIGS. 16A-16C illustrate how the method shown in FIG. 15 may be applied to the autotransformer shown in FIG. 10;

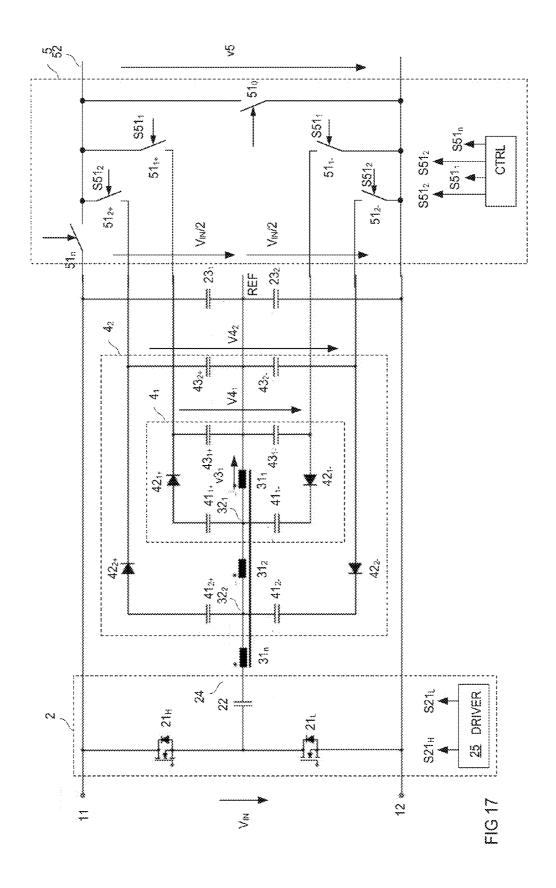

FIG. 17 show a rectifier circuit and a selector circuit according to another example;

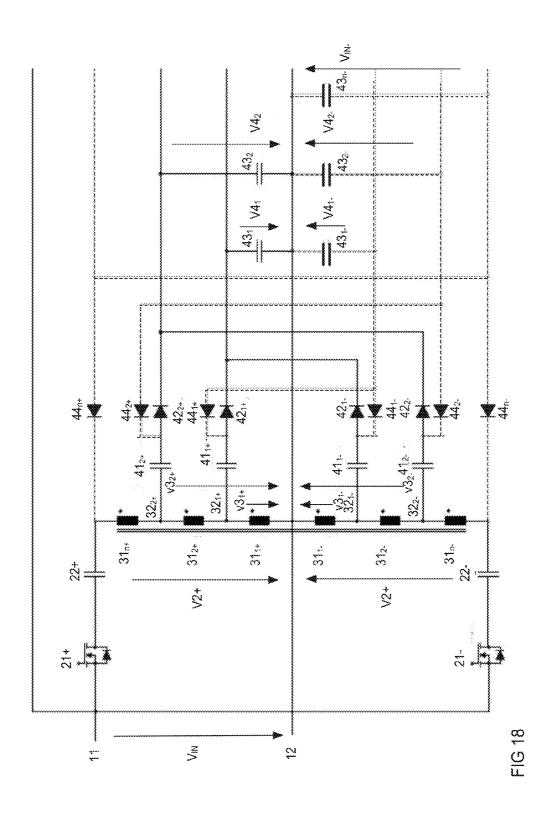

FIG. 18 show a chopper circuit, an autotransformer circuit and a rectifier circuit according to another example;

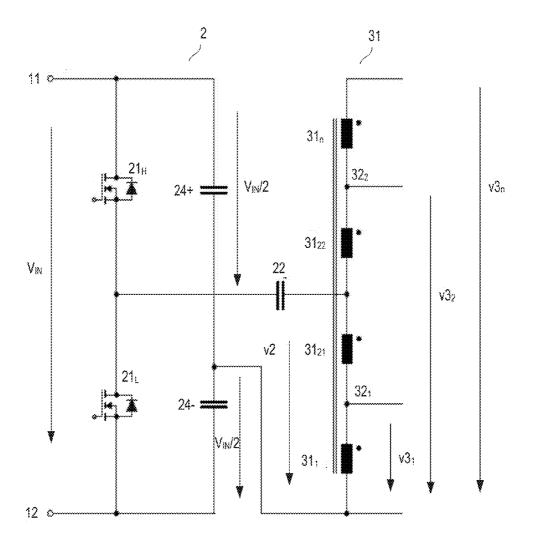

FIG. 19 show a chopper circuit and an autotransformer circuit according to another example;

FIG. 20 show a chopper circuit and an autotransformer circuit according to yet another example;

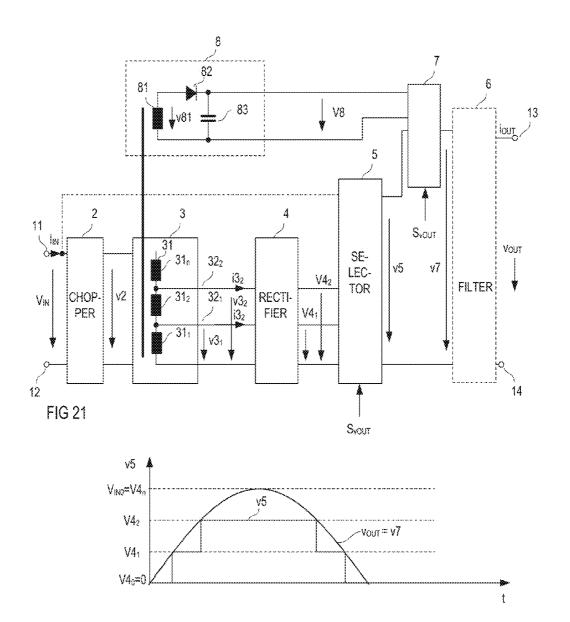

FIG. 21 shows a power converter circuit according to 5 another example; and

FIG. 22 shows timing diagrams of a selector output voltage and a power converter output voltage of the power converter circuit shown in FIG. 21.

#### DETAILED DESCRIPTION

In the following detailed description, reference is made to the accompanying drawings. The drawings form a part of the description and by way of illustration show specific embodiments in which the invention may be practiced. It is to be understood that the features of the various embodiments described herein may be combined with each other, unless specifically noted otherwise.

FIG. 1 shows one example of a power converter circuit 20 configured to convert an input power  $P_{IN}$  received at an input 11, 12 into an output power pour provided at an output 13, 14. The input power  $P_{IN}$  is defined as the product of an input current  $I_{IN}$  received at the input 11, 12 and an input voltage  $V_{IN}$  between a first input node 11 and a second input node 25 12 of the input, so that  $P_{IN} = V_{IN} \cdot I_{IN}$ . The output power pour is defined as the product of an output current  $i_{OUT}$  provided at the output 13, 14 and an output voltage  $v_{OUT}$  between a first output node 13 and a second output node 14 of the output, so that  $p_{OUT} = v_{OUT} \cdot i_{OUT}$ . A load Z (illustrated in 30 dashed lines in FIG. 1) may receive the output power pour supplied by the power converter circuit.

According to one example, the input power  $P_{IN}$  is a DC (Direct Current) power, that is, the input voltage  $V_{I\!N}$  is a direct voltage and the input current  $I_{IN}$  is a direct current. 35 According to one example, the power converter circuit is configured to convert the DC power received at the input 11, 12 into an AC (Alternating Current) power at the output 13, 14, so that the output current  $i_{\it OUT}$  is an alternating current and the output voltage  $v_{OUT}$  is an alternating voltage. 40 According to one example, the load Z is a power grid. In this example, the waveform of the output voltage  $v_{OUT}$  is defined by the load Z and the power converter circuit may generate the output current  $i_{OUT}$  to be in phase with or to have a predefined phase difference relative to the output voltage 45  $v_{OUT}$ . According to another example, the load Z is a motor that is driven by the output power pour. In this case, the power converter circuit defines the waveform of the output voltage  $v_{OUT}$ . The DC power received at the input 11, 12 may be provided by a conventional DC power source (not 50 shown in the drawings) such as a photovoltaic (PV) panel, a battery arrangement, a fuel cell arrangement, or the like.

In the following, capital letters such as V and I are used to denote direct currents, direct voltages and average levels (mean levels) of alternating currents and voltages, respectively. Lowercase letters such as v and i are used to denote alternating voltages and alternating currents.

Referring to FIG. 1, the power converter circuit includes a chopper circuit 2. The chopper circuit is configured to receive the input voltage  $V_{IN}$  and generate based on the input ovltage  $V_{IN}$  a chopper voltage v2 with an alternating varying signal level. An autotransformer circuit 3 that includes an autotransformer 31 receives the chopper voltage v2 and is configured to generate at least one tap voltage v3<sub>1</sub>, v3<sub>2</sub> based on the chopper voltage v2. Examples of how the autotransformer circuit 3 may generate the at least one tap voltage v3<sub>1</sub>, v3<sub>2</sub> from the chopper voltage v2 are explained in greater

4

detail herein below. A rectifier circuit 4 receives the at least one tap voltage  $v3_1$ ,  $v3_2$  from the autotransformer circuit 3 and is configured to generate at least one intermediate voltage  $V4_1$ ,  $V4_2$  from the at least one tap voltage  $v3_1$ ,  $v3_2$ . The at least one intermediate voltage  $V4_1$ ,  $V4_2$  is also referred to as DC link voltage in the following.

According to one example, as shown in FIG. 1, the autotransformer circuit 31 provides a plurality of tap voltages v3<sub>1</sub>, v3<sub>2</sub>. Just for the purpose of illustration, the 10 plurality of tap voltages v3<sub>1</sub>, v3<sub>2</sub> includes two voltages v3<sub>1</sub>, v3<sub>2</sub> in the example shown in FIG. 1, wherein each of these tap voltages  $v3_1$ ,  $v3_2$  is available at one tap  $32_1$ ,  $32_2$  of the autotransformer 32. This, however, is only an example, autotransformer circuit 3 can be implemented with an arbitrary number of taps, so that an arbitrary number of tap voltages a can be generated. Each tap  $32_1$ ,  $32_2$  of the autotransformer circuit 3 is a circuit node between two respective windings  $31_1$ ,  $31_2$ ,  $31_n$  of the autotransformer 31. These windings  $31_1$ ,  $31_2$ ,  $31_n$  are connected in series and inductively coupled. According to one example, each DC link voltage V4<sub>1</sub>, V4<sub>2</sub> is generated from one tap voltage v3<sub>1</sub>,  $v3_2$  so that the number of tap voltages equals the number of DC link voltages V4<sub>1</sub>, V4<sub>2</sub>.

Referring to FIG. 1, a selector circuit 5 receives the at least one DC link voltage V4<sub>1</sub>, V4<sub>2</sub> and generates a selector output voltage v5 based on the at least one DC link voltage V4<sub>1</sub>, V4<sub>2</sub>. Optionally, the selector circuit 5 further receives the input voltage  $V_{IN}$  in order to generate the selector output voltage v5 based on the at least one DC link voltage V4<sub>1</sub>, V4<sub>2</sub> and the input voltage V<sub>IN</sub>. According to one example, the selector output voltage v5 is the output voltage v<sub>OUT</sub> of the power converter circuit. According to another example, the output voltage v<sub>OUT</sub> is generated from the selector output voltage v5 by a filter circuit 6 connected between the selector circuit 5 and the output 13, 14. According to yet another example, a series voltage regulator generates the output voltage v<sub>OUT</sub> based on the selector output voltage v5.

FIGS. 2A-2C show examples of timing diagrams of some of the signals that occur in a power converter circuit of the type shown in FIG. 1 during its operation. FIG. 2A shows a timing diagram of the input voltage V<sub>IN</sub>, FIG. 2B shows a timing diagram of the chopper voltage v2, and FIG. 2C shows timing diagrams of the selector output voltage v5 and the output voltage  $v_{OUT}$ . In the example shown in FIG. 2A, the input voltage  $V_{IN}$  is a direct voltage with a voltage level  $V_{INO}$ . Referring to FIG. 2B, the chopper circuit 2 may generate the chopper voltage v2 to be a square-wave voltage based on the input voltage V<sub>IN</sub>. According to one example, the chopper voltage v2 is a periodic voltage that periodically changes its signal level between V2+v2' and V2-v2', where V2 denotes a mean of the chopper voltage v2 and v2' denotes the amplitude. In FIG. 2B, T2 denotes one period of the chopper voltage v2 and f2=1/T2 denotes the frequency of the chopper voltage v2. In every period of the chopper voltage v2, there is a time period, when the chopper voltage v2 has the lower level V2-v2' and a time period, when the chopper voltage v2 has the higher level V2+v2'. According to one example, these time durations are equal, that is, the chopper voltage v2 has the low level V2-v2' 50% of the period T2, and the high level V2+v2' 50% of the time period

The selector circuit 5 may generate the output voltage  $v_{OUT}$ . Alternatively, the selector circuit 5 generates a voltage based on which the optional filter 6 generates the output voltage your. FIG. 2C illustrates an example of how the selector circuit 5 may generate the selector output voltage based on two DC link voltages V4<sub>1</sub>, V4<sub>2</sub> and the input

voltage  $V_{I\!N}$ . FIG. 2C furthermore shows the waveform of an output voltage obtained by low-pass filtering the selector output voltage v5. In the example shown in FIG. 2C, the selector output voltage can have four different voltage levels which are selected from 0 (zero), the two tap voltages  $V4_1$ ,  $V4_2$ , and the input voltage level  $V_{INO}$ . Just for the purpose of explanation, the individual voltage levels are drawn such that  $V4_1 = \frac{1}{3} \cdot V_{IN0}$  and  $V4_2 = \frac{2}{3} \cdot V_{IN0}$ . In this case, voltage differences between neighboring voltage levels are equal, namely  $\frac{1}{3} \cdot V_{I\!N0}$ . This, however, is only an example. The voltage levels of the DC link voltages V41, V42 could also be generated such that voltage differences between neighboring voltage levels are not equal.

The selector circuit 5 generates the selector output voltage v5 such that at each time a voltage level of the selector output voltage v5 equals one of the different voltage levels 0, V4<sub>1</sub>, V4<sub>2</sub>, VIN<sub>0</sub> the selector circuit 5 receives. Referring to the above, the output voltage  $v_{OUT}$  may be generated from the selector output voltage v5 by low-pass filtering. If, for example, a desired (instantaneous) voltage level of the 20 output voltage  $v_{OUT}$  equals one of the voltage levels received by the selector circuit 5, the selector circuit 5 may simply pass through the respective voltage level to its output. If, however, a desired (instantaneous) voltage level of the Output voltage  $v_{OUT}$  is between two neighboring (consecutive) voltage levels received by the selector circuit 5, the selector circuit may approximate the output voltage v<sub>OUT</sub> by switching between two neighboring DC voltage levels in accordance with a switching frequency. The output voltage  $v_{OUT}$  is then the result of low-pass filtering the 30 selector output voltage v5, wherein the low-pass filter may be implemented such that its cutoff frequency is below the switching frequency of the selector circuit 5, but higher than a maximum frequency of the output voltage  $v_{\it OUT}$ . In the example shown in FIG. 1, the output voltage is a sinusoidal 35 voltage (or a rectified sinusoidal voltage), respectively, wherein only one half-period (or one period) is shown. The frequency of such sinusoidal voltage is much lower such as less than 1/1000, less than 1/1000, or even less than 1/10000 of the switching frequency of the selector circuit 5. In the example 40 shown in FIG. 2C, the selector circuit 5 only switches between consecutive voltage levels. This, however, is only an example. The selector circuit 5 may also switch between voltage levels that are not consecutive. That is, for example, the selector circuit 5 may switch between 0 and voltage level 45 between  $T4_{i+1}$  and T4 can be expressed as V4<sub>2</sub> wherein 0 and V4<sub>2</sub> are not consecutive voltage levels as there is another voltage level,  $V4_1$ , between 0 and  $V4_2$ .

According to one example, the selector circuit 5 operates in accordance with a modulation index m. The modulation index m is defined by a ratio between an instantaneous 50 voltage level of the output voltage  $\mathbf{v}_{OUT}$  and the maximum DC link voltage, wherein the input voltage  $V_{IN}$  is also regarded as one of the DC link voltages in this example. In the example shown in FIG. 2C, the maximum DC link voltage is the input voltage  $V_{INO}$ . In the example shown in 55 FIG. 2C, the modulation index m=1 if the instantaneous voltage level of the output voltage  $v_{OUT}$  equals the input voltage  $V_{INO}$ , m=0, if the output voltage  $v_{OUT}$  is zero and  $m=\frac{1}{3}$  if  $v_{OUT}=V4_1$ , for example.

Referring to FIG. 2C, the DC link voltages V41, V42 and 60 the input voltage  $V_{IN}$  define a plurality of consecutive voltage levels, with each pair of consecutive voltage levels defining a voltage interval. In the example shown in FIG. 2C, these voltage intervals are between 0 and  $V4_1$ , between V4, and  $V4_2$  and between  $V4_2$  and  $V_{IN}$ . The selector output voltage v5 is generated such that the selector circuit 5 at a switching frequency f4 (which is explained below) switches

6

between two of the voltage levels. According to one example, the selector circuit 5 is configured such that it only switches between voltage levels of one interval, wherein the choice of the interval is dependent on the desired voltage level of the output voltage. In the latter case, the maximum voltage swing at one time is given by the voltage defining one interval (only when the selector circuit 5 switches from a first interval to a second interval the swing may be higher, namely the sum of the voltages that define the first interval and the second interval. The "voltage defining an interval" is the voltage between the two voltage levels that define (border) the interval.

FIGS. 3A and 3B show two different examples of how the selector circuit 5 may approximate a certain instantaneous level of the output voltage  $v_{\it OUT}$  based on two neighboring DC link voltages. These DC link voltages are denoted as V4<sub>1</sub> and  $V4_{i+1}$  in FIGS. 3A and 3B. These DC link voltages  $V4_{i}$ ,  $V4_{i+1}$  may represent any two neighboring DC link voltages shown in FIG. 2C, wherein  $V_{INO}$  is also referred to as  $V4_n$ and zero (0) is also referred to as V4<sub>0</sub> in FIG. 2C. Referring to FIGS. 3A and 3B, the selector circuit 5 operates at a switching frequency f4, so that there is a plurality of successive operation cycles each having a duration T4=1/f4. The switching frequency f4 of the selector circuit 5 can be higher than, lower than or equal the frequency of the chopper voltage f2. According to one example, each of these frequencies f2 and f4 is selected from between several kilohertz (kHz) and several megahertz (MHz), in particular between 10 kHz and 1 MHz.

If the desired instantaneous voltage level of the output voltage v<sub>OUT</sub> is between the neighboring DC link voltages  $V4_i$ ,  $V4_{i+1}$  in each of the plurality of successive operation cycles there is a time period  $T\mathbf{4}_i$  when the lower one  $V\mathbf{4}_i$  of the two neighboring DC link voltages  $V4_i$ ,  $V_{i+1}$  is output by the selector circuit 5, and a time period  $T4_{i+1}$  when the higher one  $V4_{i+1}$  of the two neighboring DC link voltages  $V4_i$ ,  $V4_{i+1}$  is output by the selector circuit 5. A ratio between  $T\mathbf{4}_{i+1}$  and  $T\mathbf{4}_{i}$  is dependent on the relationship between the instantaneous level of the input voltage  $v_{OUT}$  and the two DC link voltages  $V4_i$ ,  $V4_{i+1}$ . FIG. 3A shows an example in which the output voltage  $\mathbf{v}_{OUT}$  is closer to the higher DC link voltage  $V4_{i+1}$  so that  $T4_{i+1}$  is longer than  $T4_i$ . FIG. 3B shows an example in which the output voltage  $v_{OUT}$  is closer to  $V4_i$ so that  $T\mathbf{4}_i$  is longer than  $T\mathbf{4}_{i+1}$ . In general, a relationship

$$\frac{T4_{i+1}}{T4}=a, \tag{1a}$$

if  $v_{OUT}=V4_i+(V4_{i+1}-V4_i)\cdot a,$

and T4, is given by

$$T4_i = T4 - T4_{i+}$$

(1b).

In general, if  $v_{OUT} = m \cdot V_{INO}$ , whereas m is the modulation index, and if  $V4_i \le v_{OUT} \le V4_{i+1}$  "a" can also be expressed as

$$a = \frac{m - m_i}{m_{i+1} - m_i},\tag{2}$$

wherein  $m_i = V\mathbf{4}_i/V_{DV0}$  and  $m_{i+1} = V\mathbf{4}_{i+1}/V_{DV0}$ .

FIG. 4 shows one example of a power converter circuit of the type shown in FIG. 1 in greater detail. In this example, the chopper circuit 2 includes a half-bridge with a high-side switch  $21_H$  and a low-side switch  $21_L$ . The high-side switch

$21_H$  and the low-side switch  $21_L$  are connected in series between the first input node 11 and the second input node 12. A capacitor 22, which is referred to as chopper capacitor 22 in the following, is connected between a tap of the halfbridge and an output 24 of the chopper circuit 2. The "tap" of the half-bridge is a circuit node common to the high-side switch  $21_H$  and the low-side switch  $21_L$ . The chopper voltage v2 is available between the output 24 of the chopper circuit 2 and a reference node, which is the second input node 12 in this example. Optionally, an input capacitor 23 is connected between the first input node 11 and the second input node 12, respectively. The high-side switch  $21_H$  and the low-side switch  $21_L$  switch on and off in accordance with a respective drive signal  $S21_H$ ,  $S21_L$  generated by a drive circuit 25. The drive circuit 25 switches on and off the 15 high-side switch  $21_H$  and the low-side switch  $21_L$  alternately so that only one of the high-side switch  $21_H$  and the low-side switch  $21_L$  is switched on at the same time. The drive circuit 25 operates the high-side switch  $21_H$  and the low-side switch 21, in accordance with the desired frequency f2 of the 20 chopper voltage v2, explained with reference to FIG. 2B. According to one example, the drive circuit 25 operates the high-side switch  $21_H$  and the low-side switch  $21_L$  at 50% duty-cycle. That is, each of the high-side switch  $21_H$  and the low-side switch  $21_L$  is switched on 50% of one period T2. 25 This is explained with reference to FIG. 5 below

FIG. 5 shows examples of timing diagrams of the drive signals  $S21_H$ ,  $S21_L$  of the high-side switch  $21_H$  and the low-side switch 21<sub>L</sub>. Referring to FIG. 5, each of these drive signals  $S21_H$ ,  $S21_L$  can have an on-level that switches on the 30 respective switch and an off-level that switches off the respective switch. Just for the purpose of explanation, the on-level is a high signal level and the off-level is a low signal level in the example shown in FIG. 5. In the following, an on-period of the respective drive signal  $S21_H$ ,  $S21_L$  is a time 35 period in which the respective drive signal  $S21_H$ ,  $S21_L$  has an on-level, and an off-period is a time period in which the respective drive signal  $S21_H$ ,  $S21_L$  has an off-level. Referring to FIG. 5, on-periods of the two drive signals S21<sub>H</sub>,  $S21_L$  do not overlap, so that only one of the high-side switch 40  $21_H$  and the low-side switch  $21_L$  is switched on at the same time. According to one example (not shown in FIG. 5), there is a dead time between the time when one of the high-side switch  $21_H$  and the low-side switch  $21_L$  switches off and the time when the other one of the high-side switch  $21_H$  and the 45 low-side switch  $21_L$  switches on. This may serve to safely prevent a cross current in the half-bridge. Referring to FIG. 5, a duration of the on-periods of each of the drive signals  $S21_H$  and  $21_L$  drive signal  $S21_L$  is T4/2. That is, each of the high-side switch  $21_H$  and the low-side switch  $S1_L$  is operated 50 at a duty-cycle of 50% (the duty-cycle is the ratio between the on-period and the overall period T4 of one drive cycle).

A chopper circuit **2** as explained with reference to FIGS. **4** and **5**, generates a chopper voltage v**2** that has a timing diagram as shown in FIG. **2B** in which the average value 55 (mean value) is zero, that is, V**2**=0 and in which the amplitude v**2**' is half the voltage level of the input voltage  $V_{IN}$ , that is, v**2**!= $V_{INO}/2$ . Thus, in the chopper circuit **2** shown in FIG. **4**, the chopper voltage v**2** alternates between + $V_{INO}/2$  and - $V_{INO}/2$  at a frequency of f**2**, wherein in each period of 60 the chopper voltage, the lower voltage level - $V_{INO}$  prevails half of the time period T**4**, and the upper level + $V_{INO}$  prevails half of the time period T**4**.

In the power converter circuit shown in FIG. 4, the autotransformer 31 receives the chopper voltage v2. That is, the autotransformer 31 is coupled to the output 24 of the chopper circuit 2 such that the chopper voltage v2 is applied

8

to the autotransformer 31, which includes a series circuit with a plurality of windings  $31_1$ ,  $31_2$ ,  $31_n$  that are inductively couples. Just for the purpose of illustration, the autotransformer 31 shown in FIG. 4 includes n=3 windings and n-1=2 taps  $32_1$ ,  $32_2$ . At each of the taps  $32_1$ ,  $32_2$  one tap voltage  $v3_1$ ,  $v3_2$  is available. Each tap voltage  $v3_1$ ,  $v3_2$  is substantially proportional to the chopper voltage v2 received by the autotransformer 31, wherein a proportionality factor between one tap voltage and the chopper voltage v2 is dependent on the number of turns of the individual windings  $s31_1$ ,  $s31_2$ ,  $s31_n$ . A first tap voltage  $s31_1$ , for example, is the voltage across a first winding  $s31_1$ . This first tap voltage  $s31_1$  is given by

$$v3_1 = \frac{N_1}{N_{cot}} \cdot v2,\tag{3}$$

where  $N_1$  is the number of turns of the first winding  $31_1$  and  $N_{tot}$  is the overall number of windings of the autotransformer 31. In the example shown in FIG. 4, wherein the autotransformer 31 includes the three windings  $31_1$ ,  $31_2$ ,  $31_n$ ,

$$N_{tot} = N_1 + N_2 + N_n$$

(4),

where  $N_2$  is the number of turns of a second winding  $31_2$  and  $N_n$  is the number of turns of an n-th (the third in this example) winding  $31_n$ . In the example shown in FIG. 4, a second tap voltage  $v3_2$ , which is the voltage between the second tap  $32_2$  and the reference node (the second input node in this example) is the voltage across the first winding  $31_1$  and the second winding  $31_2$ , so that the second tap voltage  $v3_2$  is given by

$$v3_2 = \frac{N_2 + N_1}{N_{TOT}} \cdot v2. (5)$$

According to one example, the individual windings  $31_1$ ,  $31_2$ ,  $31_n$  have the same number of turns, that is,  $N_1=N_2=N_n$ . In this case,  $v3_1=\frac{1}{2}v2$  and  $v3_2=\frac{2}{3}v2$ . In general, if the autotransformer 31 includes an arbitrary number of n windings that each have the same number of turns, n-1 different tap voltages  $v3_k$  can be obtained, wherein each of these tap voltages is given by

$$v3_k = \frac{k}{n} \cdot v2,\tag{6}$$

wherein k is selected from between 0 and n-1.

In the example shown in FIG. 4, the rectifier circuit 4 includes several rectifier stages in this example)  $\mathbf{4}_1$ ,  $\mathbf{4}_2$ , with each of these rectifier stages  $\mathbf{4}_1$ ,  $\mathbf{4}_2$  receiving one of the tap voltages  $v\mathbf{3}_1$ ,  $v\mathbf{3}_2$  and being configured to generate one of the DC link voltages  $V\mathbf{4}_1$ ,  $V\mathbf{4}_2$  based on the respective tap voltage  $v\mathbf{3}_1$ ,  $v\mathbf{3}_2$ .

Referring to FIG. 4, the selector circuit 5, besides the DC link voltages  $V_{4_1}$ ,  $V_{4_2}$  receives the input voltage  $V_{IN}$  and includes a plurality of switches  $51_0$ - $51_n$ , wherein each of these switches is configured to connect one of the plurality of voltages received by the selector circuit 5 to an output 52 of the selector circuit 5. The voltages (voltage levels) received by the selector circuit 5 shown in FIG. 4 are the DC link voltages  $V_{4_1}$ ,  $V_{4_2}$  output by the rectifier stages  $V_{4_1}$ ,  $V_{4_2}$  and the input voltage  $V_{4_1}$ . In this example, each of switches  $V_{4_1}$ ,  $V_{4_2}$  shown in FIG. 4 serves to connect one of the DC

C

link voltages  $V\mathbf{4}_1$ ,  $V\mathbf{4}_2$  to the output **52**, and a switch **51**, serves to connect the input voltage  $V_{IN}$  to the output **52**. Additionally, the selector circuit **5** includes a switch  $\mathbf{51}_0$  coupled between the output **52** and the second input node **12**, which serves as the reference node in the power converter circuit shown in FIG. **4**, whereas the output voltage v**5** is zero if tis switch  $\mathbf{51}_0$  is switched on. The individual switches  $\mathbf{51}_0$ - $\mathbf{51}_n$  are driven by drive signals  $\mathbf{S51}_0$ - $\mathbf{S51}_n$  generated by a control circuit **52**. According to one example, the control circuit **52** is configured to generate the drive signals  $\mathbf{S51}_0$ - $\mathbf{S51}_n$  such that only one of the switches  $\mathbf{51}_0$ - $\mathbf{51}_n$  is switched on at the same time.

One example of the control circuit 52 is explained with reference to FIG. 6. FIG. 6 shows a block diagram of one example of the control circuit 52 that controls operation of the selector circuit 5 and, therefore, controls the selector output voltage v5. The control circuit 52 shown in FIG. 6 generates the selector output voltage v5 such that the input voltage  $V_{IN}$  is regulated and the output current  $v_{OUT}$  (see FIG. 1) has a predefined signal waveform. This control 20 circuit 52 receives an input voltage signal S<sub>VIV</sub> that represents the input voltage  $V_{IN}$ . This input voltage signal  $S_{VIN}$ can be obtained by any kind of voltage measurement circuit, which is not shown in the drawings. An error filter 521 receives the input voltage signal S<sub>VIN</sub> and compares the input 25 voltage signal S<sub>VIN</sub> with an input voltage reference signal  $S_{VIN-REF}$ . This input voltage reference signal  $S_{VIN-REF}$  represents a desired voltage level of the input voltage  $V_{IN}$ . The error filter 521 calculates a difference between the input voltage signal  $S_{VIN}$  and the input voltage reference signal 30  $S_{\emph{VIN-REF}}$  and generates an input voltage error signal  $S_{VIN-ERR}$  based on this difference. According to one example, the input voltage error signal  $S_{VIN-ERR}$  is obtained by filtering this difference using one of an integral (I) filter, a proportional-integral (PI) filter, a proportional-integral- 35 derivative (PID) filter, or the like. A multiplier 522 receives the input voltage reference signal  $S_{VIN-ERR}$  and a signal representing a desired waveform of the output current  $I_{OUT}$ .

According to one example, the power converter circuit supplies the output current  $i_{OUT}$  to a power grid, so that the 40 output voltage  $v_{OUT}$  is defined by the power grid, and it is desired to generate the output current  $i_{OUT}$  to be in phase with the output voltage  $v_{OUT}$  or have a predefined phase difference relative to the output voltage  $v_{OUT}$ . In each case, the desired waveform of the output current  $i_{OUT}$  is given by the output voltage your. The signal defining the desired waveform of the output current  $i_{OUT}$  is an output voltage signal  $S_{vOUT}$  in this example. The output voltage signal  $S_{vOUT}$  can be obtained by measuring the output voltage  $V_{\it OUT}$  using any kind of current measurement circuit (not 50 shown in the figures). By multiplying the output voltage signal  $S_{vOUT}$  and the input voltage error signal  $S_{VIN-ERR}$ , the multiplier 522 generates an output current reference signal  $S_{iOUT\text{-}REF}$  which defines the desired output current  $i_{OUT}$ Based on this output current reference signal  $S_{iOUT-REF}$ , the 55 controller 52 generates an output current error signal  $S_{iOUT-ERR}$  by subtracting an output current signal  $S_{iOUT}$ , or a filtered version of this output current signal  $S_{iOUT}$ , from the output current reference signal  $S_{iOUT-REF}$ . An optional filter 524 that filters the output current signal  $S_{iOUT}$  in order 60 to obtain a filtered version of the output current signal  $S_{iOUT}$ is a low-pass filter, for example. The output current signal  $S_{iOUT}$  may be obtained by measuring the output current  $i_{OUT}$ using any kind of current measurement circuit (not shown in the figures).

Referring to FIG. 6, the output current error signal  $S_{iOUT-ERR}$  is received by another filter 525 that generates the

10

modulation index m from the output current error signal  $S_{iOUT\text{-}ERR}$ . According to one example, the filter 525 has one of an integrating (I) characteristic, a proportional-integral (PI) characteristic, or a proportional-integral-derivative (PID) characteristic. A modulator 526 receives the modulation index in and generates the drive signals  $S51_0$ - $S51_n$  based on the modulation index m, in the way basically explained with reference to FIG. 2C herein before.

It can be shown that, in case the output voltage  $v_{OUT}$  is a periodic voltage, the modulation index m is also a periodic signal, substantially with the same frequency as the output voltage  $v_{OUT}$ . For the purpose of explanation, it is assumed that the output voltage  $v_{OUT}$  is a rectified sine voltage with a frequency of 100 Hz or 120 Hz respectively. Based on such rectified sine voltage, a sine voltage with a frequency of 50 Hz or 60 Hz, respectively, can easily be generated by using an unfolding circuit explained herein further below.

FIG. 7 schematically illustrates the relationship between the output voltage  $\mathbf{v}_{OUT}$  and the modulation index m. As, referring to FIG. 6, the output current reference signal  $S_{iOUT\text{-}REF}$  is obtained by multiplying the output voltage signal  $S_{vOUT}$  with the input voltage error signal  $S_{VIN-ERR}$ , the output current reference signal  $S_{iOUT\text{-}REF}$  is proportional to the output voltage  $v_{OUT}$  (when assuming that the voltage level of the input voltage  $V_{I\!N}$  does not change during the time period illustrated in FIG. 7). Referring to FIG. 7, there may be a phase-shift  $\Phi$  between the output current reference signal  $\mathbf{S}_{iOUT\text{-}REF}$  and the modulation index m. This phase difference  $\Phi$  which is at most several degrees, may vary based on the difference between the output current reference signal  $S_{iOUT\text{-}REF}$  and the filtered output current signal  $S_{iOUT\text{-}}$ Further, it can be shown that an amplitude of the varying modulation index m is dependent on the amplitude of the input voltage  $V_{I\!N}$ , so that the input voltage  $V_{I\!N}$  can be regulated by suitably varying the modulation index m in the way explained with reference to FIG. 6. According to one example, the filter 525 is configured to generate the modulation index m as a normalized signal with values of between 0 and 1, wherein the modulation index m is one in those cases in which the input voltage  $V_{IN}$  is to be output as the selector voltage v5.

The control circuit **52** shown in FIG. **6** is only one example. This type of control may be used in a power converter that receives the input voltage  $V_{IN}$  from a power source with a varying output power such as, for example, a PV panel. In this case, controlling the input voltage  $V_{IN}$  to be constant is equivalent to adapting the input power  $P_{IN}$  of the power converter circuit to the power supplied by the power source.

According to another example, the input voltage  $V_{IN}$  is not regulated by the power converter circuit (because, for example, a regulator outside the power converter circuit regulates the input voltage  $V_{IN}$ ). In this case, the error filter 521 and the multiplier 522 can be omitted. The subtractor 523 receives the signal defining the waveform of the output current instead of the output current reference signal  $S_{iOUT\text{-}REF}$ , in this case. The signal defining the desired waveform of the output current  $i_{OUT}$  is the output voltage signal  $S_{vOUT}$  in the example shown in FIG. 6.

According to another example, the waveform of the output voltage  $\mathbf{v}_{OUT}$  is not defined by an external source such as a voltage grid, but by the power converter circuit. One type of application where the power converter circuit generates the waveform of the output voltage  $\mathbf{v}_{OUT}$  is a motor drive application, where the load Z is a motor driven by the power converter circuit. In this case, a controller (not shown) generates a sequence of modulation indices (with

each modulation index defining one instantaneous voltage level of the output voltage  $v_{OUT}$  or the selector output voltage v5, respectively) such that the output voltage  $v_{OUT}$  has a desired waveform and a desired frequency.

FIG. 8 shows one example of how the rectifier stages  $\mathbf{4}_1$ , 4<sub>2</sub> in the power converter circuit shown in FIG. 4 may be implemented. In FIG. 8,  $31_k$  denotes any of the windings 31<sub>1</sub>, 31<sub>2</sub> shown in FIG. 4, 32k denotes the respective tap connected to the winding  $31_k$ ,  $4_k$  denotes the respective rectifier stage, and  $V4_k$  denotes the DC link voltage generated by the respective rectifier stage  $\mathbf{4}_k$ . Referring to FIG. 8, the rectifier stage  $\mathbf{4}_k$  includes an output capacitor  $\mathbf{43}_k$  across which the DC link voltage  $V4_k$  is available. Another capacitor  $41_k$ , which is referred to as tap capacitor in the following, is connected to the tap  $32_k$ . A first rectifier element  $42_k$ , such as a diode, is connected between the tap capacitor  $41_k$  and the output capacitor  $43_k$ , and another rectifier element  $44_k$ , such as a diode is connected between a circuit node common to the tap capacitor  $41_k$  and the first rectifier element  $42_k$  and the reference node (which is the second input node 12 in this 20

One way of operation of the rectifier stage  $\mathbf{4}_k$  shown in FIG. 8 is explained with reference to FIG. 9 that illustrates a timing diagram of the tap voltage  $v3_k$  (which is the voltage between the tap  $32_k$  and the reference node 12) during one 25 period T2 of the chopper circuit 2. Referring to the above, the tap voltage  $v3_k$  is proportional to the chopper voltage v2. As, referring to the above, the chopper voltage v2 generated by the chopper circuit 2 shown in FIG. 4 is a zero-mean square voltage that varies between a negative signal level and a positive signal level the tap voltage  $v3_k$  is also a zero-mean square voltage that varies between a negative signal level and a positive signal level. The negative signal level of the tap voltage  $v3_k$  is referred to as  $-v3_k$ ' and the positive level is referred to as  $+v3_k$ ' in FIG. 9. When the tap voltage  $v3_k$  has the negative level, a voltage  $v41_k$  across the tap capacitor  $41_k$  substantially equals  $-v3_k$  (if conduction losses in the rectifier element  $44_k$ ) are neglected, so that a magnitude of the voltage v41 equals the amplitude  $v3_k$  of the tap voltage  $v3_k$ . When the tap voltage  $v3_k$  becomes 40 positive, the electrical potential at the tap  $32_k$  rises to  $v3_k$ , so that the output capacitor  $43_k$  is charged via the first rectifier element  $42_k$  by the charge stored in the tap capacitor  $41_k$ . In this rectifier stage  $\mathbf{4}_k$ , the output capacitor  $V\mathbf{4}_k$  is charged to  $2 \cdot v3_k$ , which is twice the amplitude of the tap voltage  $v3_k$ . 45 Consequently, in the power converter circuit shown in FIG. 4, the DC link voltages V4<sub>1</sub>, V4<sub>2</sub> are given by

$$V4_1 = \frac{N_1 \cdot V_{IN0}}{N_{tot}},\tag{7a}$$

$$V4_2 = \frac{(N_1 + N_2) \cdot V_{IN0}}{N_{tot}}. (7b)$$

FIG. 10 shows a power converter circuit with a chopper circuit 2, an autotransformer circuit 3, a rectifier circuit 4 and a selector circuit 5 of the type shown in FIG. 4. In the power converter circuit shown in FIG. 10, the rectifier stages  $\mathbf{4}_1$ ,  $\mathbf{4}_2$  of the rectifier circuit 4 are implemented as explained with reference to FIG. 8 and drawn in detail in FIG. 10. In the chopper circuit 2, the high-side switch  $\mathbf{21}_H$  and the low-side switch  $\mathbf{21}_L$  are each implemented as a MOSFET, in particular as an n-type MOSFET. This however, is only an example, other types of electronic switches such as IGBTs (Insulated 65 Gate Bipolar Transistors), IFETs (Junction Field Effect Transistors), Brfs (Bipolar Junction Transistors) or HEMTs

12

(High Electron-Mobility Transistors) may be used as well. In FIG. 10, a diode that is drawn to be connected between a drain node D and a source node S of the respective MOSFET  $21_H$ ,  $21_L$  represents an internal body diode of the respective MOSFET  $21_H$ ,  $21_L$  and/or an external diode connected in parallel with the drain-source path of the MOSFET

In the example shown in FIG. 10, the switch  $51_0$  that is connected between the output 52 of the selector circuit 5 and the reference node 12 is also implemented as a MOSFET, in particular an n-type MOSFET. This however, is only an example. Another type of electronic switch such as an IGBT (Insulated Gate Bipolar Transistor), a JFET (Junction Field Effect Transistors), a BJT (Bipolar Junction Transistor) or a HEMT (High Electron-Mobility Transistors) may be used as well. The other switches  $51_1$ ,  $51_2$ ,  $51_n$  of the selector circuit may each include two MOSFETs that are connected in series such that internal body diodes (which are also illustrated in FIG. 10) of these MOSFETs are connected back to back. In the example shown in FIG. 10, the MOSFETs that are connected in series have the same type, which is an n-type in this example. The two MOSFETs forming one switch may receive the same drive signal. That is, for example, the MOSFETs forming switch 51<sub>1</sub> each receive the drive signal S51, generated by the control circuit 52. According to another example, the two MOSFETs of one switch are driven based on the same drive signal, but in accordance with a modulation scheme such as, for example, a modulation scheme known as current dependent matrix converter commutation strategy. Such modulation scheme, for example, may switches off only one of the MOSFETs but leave the other MOSFET in an on state so as to allow a current flow in one direction (via the MOSFET that is in the on-state and the body diode of the other MOSFET). This may be used to allow inductances in the circuit to commu-

Using MOSFETs to implement the switches  $51_1$ ,  $51_2$ ,  $51_n$  is only an example. Other types of electronic switches such as IGBTs (Insulated Gate Bipolar Transistors), JFETs (Junction Field Effect Transistors), BJTs (Bipolar Junction Transistors) or HEMTs (High Electron-Mobility Transistors) may be used as well.

In the power converter circuit shown in FIG. 10, the output filter 6 includes an LC filter 61, 62 that receives the selector output voltage v5 and generates an LC filter output voltage v62. The LC filter output voltage v62 is a smoothed (filtered) version of the selector output voltage v5. If, for example, the selector output voltage v5 has a waveform as shown in FIG. 2C, the smoothed version of the selector output voltage v5 output voltage v5 generated by the LC filter has a waveform as denoted by your shown in FIG. 2C, The LC filter includes a series circuit with an inductor 61 and a capacitor 62. This series circuit is connected between the output 52 and the reference node 12 in the example shown in FIG. 10, whereas the LC filter output voltage v62 is available across the capacitor 62.

Referring to FIG. 10, the output filter 6 furthermore includes an unfolding bridge. The unfolding bridge includes two half-bridges each connected in parallel with the capacitor 62 of the LC filter. A first one of these two half-bridges includes a first high-side switch  $63_H$  and a first low-side switch  $63_L$ , and a second one of these two half-bridges includes a second high-side switch  $64_H$  and a second low-side switch  $64_L$ . A tap of the first half-bridge forms the first output node 13 and a tap of the second half-bridge forms the second output node 14. The unfolding bridge is configured to generate an alternating output voltage  $v_{OUT}$  based on the

LC filter output voltage v62. According to one example, the power converter circuit generates the filter output voltage v62 such that it has a rectified sine waveform and the unfolding bridge generates the output voltage  $v_{OUT}$  to have a sine waveform based on the filter output voltage v62. This is explained with reference to FIG. 11 in which example timing diagrams of the filter output voltage v62, the corresponding output voltage  $v_{OUT}$  of the power converter circuit and of drive signals  $S63_H$ ,  $S63_L$ ,  $S64_H$ ,  $S64_L$  of the individual switches of the half-bridges of the unfolding bridge are shown. Just for the purpose of illustration it is assumed that a high-level of a drive signal  $S63_H$ - $S64_L$  switches on the respective switch  $63_H$ - $64_L$  and that a low-level switches off the respective switch  $63_H$ - $64_L$ . Referring to FIG. 11, the unfolding bridge changes its switching state only once in each period of the filter output voltage V62, namely at the beginning of each period. One period of the output voltage  $v_{OUT}$  (wherein one such period is shown in FIG. 11) includes two periods of the filter output voltage v62. That is, each period of the filter output voltage v62 forms one half-period 20 of the final output voltage  $v_{OUT}$ . In one of these two half-periods, the filter output voltage v62 forms the output voltage your, and in the other half-period, the filter output voltage v62 is inverted by the unfolding bridge. In the example shown in FIG. 11, in a first half-period of these two 25 half-periods, the first high-side switch  $63_H$  and the second low-side switch  $64_L$  are on in order to apply the filter output voltage v62 to the output nodes 13, 14. In the second half-period, the first low-side switch 63, and the first highside switch  $64_H$  are on in order to apply the inverted filter 30 output voltage V62 the output nodes 13, 14.

In case the power converter circuit includes an unfolding bridge, the selector circuit **5** generates an output voltage with only one polarity. In this case, the control circuit **52** shown in FIG. **6** can be modified such that the output voltage signal  $_{VOUT}$  represents a rectified output voltage  $v_{OUT}$  instead of the output voltage  $v_{OUT}$ , and the output current signal  $S_{iOUT}$  represents the current  $i_{OUT-REC}$  flowing from the LC filter into the unfolding bridge.

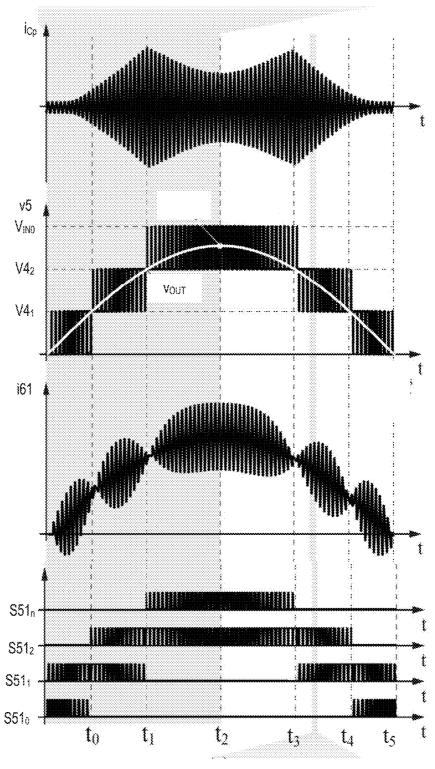

FIG. 12 shows timing diagrams of several signals occurring in the power converter circuit shown in FIG. 10 during operation. These timing diagrams serve to illustrate one way of operation of this power converter circuit. In particular, FIG. 12 shows timing diagrams of a current  $i_{C_p}$  through the chopper capacitor 22, the selector output voltage v5, a 45 current i61 through the inductor 61 of the LC filter 61, 62 and of the drive signals  $S51_0$ - $S51_n$  of the switches in the selector circuit 5. In FIG. 10, the timing diagrams are shown during one half-period of a sinusoidal output voltage  $v_{OUT}$  or one period of a rectified sinusoidal output voltage, respectively. A rectified sinusoidal output voltage can be generated by the power converter circuit shown in FIG. 10 by omitting the unfolding bridge.

Referring to FIG. 12, operation of the power converter circuit during one half-period (one period) of the output 55 voltage  $v_{OUT}$  can be subdivided into six sub-periods, namely a first sub-period, which is between a beginning of the half-period (period) and  $t_0$ , a second sub-period, which is between  $t_0$  and  $t_1$ , a third sub-period, which is between  $t_1$  and  $t_2$ , a fourth sub-period, which is between  $t_2$  and  $t_3$ , a fifth 60 sub-period, which is between  $t_4$  and  $t_5$ . Referring to FIG. 12,  $t_0$  and  $t_5$  are the times when the voltage level of the output voltage  $v_{OUT}$  crosses the voltage level of the first DC link voltage  $v_{OUT}$  crosses the voltage level of the second DC link voltage  $v_{OUT}$  crosses the voltage level of the second DC link voltage  $v_{OUT}$  crosses the times when the

14

output voltage  $v_{OUT}$  reaches its maximum. Operation in the first sub-period equals operation in the sixth sub-period, operation in the second sub-period equals operation in the fifth sub-period, and operation in the third sub-period equals operation in the fourth sub-period, so that only operation in the first, second and the third sub-period is explained in the following. These first, second and third sub-periods are sub-periods that cover a time period between a rime, when the output voltage  $v_{OUT}$  is zero and a rime, when the output  $v_{OUT}$  reaches its maximum. Thus, these three sub-periods cover one quarter (one half) of a period of a sinusoidal (a rectified sinusoidal) output voltage  $v_{OUT}$ .

Referring to FIG. 12, in the first sub-period, the selector circuit 5 switches between the first DC link voltage V4<sub>1</sub> and zero. Consequently, switches  $51_n$  and  $51_1$  of the selector 5are switched on and off in an alternating fashion during this first sub-period. In the second sub-period, the selector 5 switches between the first DC link voltage  $V4_1$  and the second DC link voltage V4<sub>2</sub>, so that switches 51<sub>1</sub> and 51<sub>2</sub> are switched on and off in an alternating fashion. In the third sub-period, the selector 5 switches between the second DC link voltage  $V_{INO}$ , so that switches  $51_2$  and  $51_n$  of the selector are switched on and off in an alternating fashion. During the first and second sub-period, the current  $i_{C_n}$  through the chopper capacitor 22 increases as the voltage level of the output voltage  $v_{OUT}$  increases. Referring to FIG. 12, the current  $i_{C_p}$  does not decrease to zero even if the output voltage  $V_{OUT}$  is zero. This is due to a magnetizing current of the autotransformer 31 During the third sub-period the capacitor current i<sub>C</sub> decreases as during this sub-period switch  $51_n$  that is directly connected to the first input node 11 conducts (with the duty-cycle increases as the voltage level of the output voltage  $v_{OUT}$  increases), whereas the current through switch  $51_n$  (other than the currents through the switches  $51_1$  and  $51_2$ ) does not flow through the chopper capacitor 22.

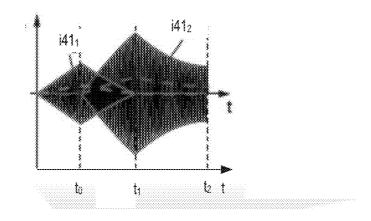

FIG. 13 illustrates the currents  $i41_1$ ,  $i41_2$  through the tap capacitances  $41_1$ ,  $41_2$  during the first three sub-periods.

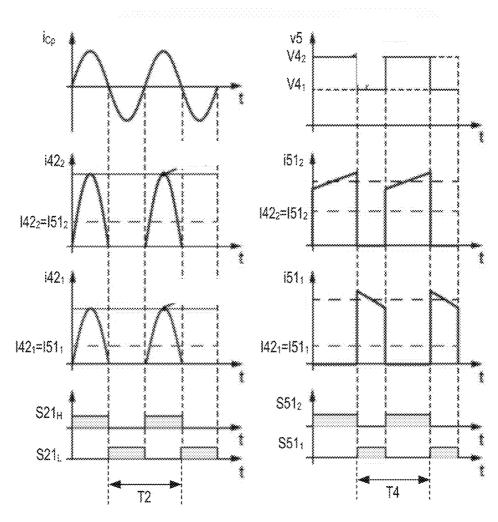

FIG. 14A shows timing diagrams of the current i<sub>C</sub> through the chopper capacitance 22, the currents I42<sub>2</sub>, I42<sub>1</sub> through the second diodes  $42_2$ ,  $42_1$  in the rectifier stages  $4_2$ ,  $\mathbf{4}_{1}$  and drive signals  $S21_{H}$  of the high-side switch  $21_{H}$  and  $S21_L$  of the low-side switch  $21_L$  of the chopper circuit 2 during two periods of the chopper circuit 2. FIG. 14B illustrates timing diagrams of the selector output voltage v5 currents  $\mathbf{i51}_2$ ,  $\mathbf{i51}_1$  through the switches  $\mathbf{51}_2$ ,  $\mathbf{51}_1$  of the selector circuit 5, and drive signals S51<sub>1</sub>, S52<sub>2</sub> of these switches  $51_1$ ,  $51_2$  during two periods of the selector circuit 5. FIGS. 14A and 14B show the timing diagrams in the second sub-period (which is between t<sub>0</sub> and t<sub>1</sub>) that is, when the selector circuit 5 switches between the second DC link voltage V4<sub>2</sub> and the first DC link voltage V4<sub>1</sub>. In the example shown in FIG. 14, the switching frequency f2 of the chopper circuit 2 is adapted to the inductances and capacitances in the power converter circuit such that the current i<sub>C</sub>. through the chopper capacitance 22 is a periodic current with a sinusoidal waveform. By this, the high-side switch  $21_H$  and the low-side switch  $21_L$  of the chopper circuit 2 can be operated in a zero current switching (ZCS) mode. That is, these switches  $21_H$ ,  $21_L$  switch on and off when the current through the respective switch is substantially zero. By this, switching losses in the chopper circuit 2 can be reduced.

Referring to FIG. 14A, each of the DC link capacitors  $43_1$ ,  $43_2$  is charged by the respective current  $i42_1$ ,  $i42_2$  each time, the high-side switch  $21_H$  is switched on. As the current  $i_{C_p}$  through the chopper capacitance 22 is a sinusoidal current, the charging currents of the DC link capacitors  $43_1$ ,  $43_2$  have

the form of one half-period of a sinusoidal signal each time, the high-side switch  $\mathbf{21}_H$  is switched on. When the low-side switch  $\mathbf{21}$  is switched off the tap capacitances  $\mathbf{41}_1$ ,  $\mathbf{41}_2$  are charged, as explained above, so that during these time periods, the charging currents  $\mathbf{i42}_1$ ,  $\mathbf{i42}_2$  of the DC link capacitors  $\mathbf{43}_1$ ,  $\mathbf{43}_2$  are zero.

Referring to FIG. 14B, the current i512 through the switch 51<sub>2</sub> increases, when the switch 51<sub>2</sub> is switched on and is zero, when the switch  $\mathbf{51}_2$  is switched off. When switch  $\mathbf{51}_2$ is switched on, a voltage v61 across the inductor 61 of the LC filter is given by V4<sub>2</sub>-v<sub>OUT</sub>, that is, the second DC link voltage V4, minus the output voltage your. As during the second sub-period the voltage level of the output voltage you is between the voltage level of the first DC link voltage 15  $V4_1$  and the voltage level of the second DC link voltage  $V4_2$ , the voltage v61 across the inductor is higher than zero, which results in the increase of the current. Equivalently, when switch  $51_1$  of the selector circuit 5 is switched on, the voltage v61 across the inductor 61 is given by V4<sub>1</sub>-v<sub>OUT</sub>, 20 that is, the first DC link voltage V4, minus the output voltage  $v_{OUT}$ . This voltage is negative, so that the current i51<sub>1</sub> through this switch  $51_1$  decreases when the switch  $51_1$  is switched on and this current i51, is zero, when the switch 51, is switched off. The current i61 through the inductor 61 25 of the LC filter is given by the current i51, plus the current i51<sub>2</sub> so that the current i61 has a triangular waveform during the second sub-period.

Referring to FIG. 10, the power converter circuit includes several series resonant circuits that can be excited by the 30 chopper circuit 2. In order to obtain ZCS the parameters of these series resonant circuits and the switching frequency f2 of the chopper circuit 2 are suitably adapted to one another. This is explained in further detail herein below. Referring to FIG. 10, a first series resonant circuit includes the tap capacitance  $41_1$  of the rectifier stage  $4_1$  coupled to the first tap 321, a first parasitic inductance 331 of the autotransformer 31 between the first tap  $32_1$  and the tap capacitor  $41_1$ , another parasitic capacitance  $33_n$  of the autotransformer 31in series with the n-th winding  $31_n$  and the chopper capacitor 40 22. Another series resonant circuit includes the tap capacitor  $41_2$  of the rectifier stage  $4_2$  coupled to the second tap  $32_2$ , a second parasitic inductance 33<sub>2</sub>, the parasitic inductance and the chopper capacitor 22. The parasitic inductances  $33_1$ ,  $33_2$ ,  $33_n$  of the autotransformer 31 result from leakage induc- 45 tances of the autotransformer 31. In general, a power converter circuit with an autotransformer with n windings and n-1 taps includes n-1 series resonant circuits. Each of these resonant circuits is associated with one tap 32, and includes the tap capacitor  $41_i$  connected to the respective tap  $32_i$ , a 50 leakage inductance  $33_i$  at the respective tap  $32_i$ , the chopper capacitance 22, and the leakage inductance  $33_n$  in series with the chopper capacitor 22.

These parasitic inductances  $33_1$ ,  $33_2$ ,  $33_n$  can be obtained by measuring and/or simulating the specific autotransformer 51 employed in the power converter circuit. Based on these parasitic inductances  $33_1$ ,  $33_2$ ,  $33_n$  and based on the desired switching frequency  $41_1$ ,  $41_2$ , and the chopper capacitor  $41_1$

The power converter circuit operates in the resonant mode if, in each of the sub-periods explained before, each of the current  $i_{C_p}$  through the chopper capacitor 22, the currents  $i31_1$ ,  $i31_2$ ,  $i31_n$  through the windings  $31_1$ ,  $31_2$ ,  $31_n$ , and the currents  $i41_1$ ,  $i41_2$  through the tap capacitors  $41_1$ ,  $41_2$ , have a sinusoidal waveform with a frequency equal the switching frequency f2 of the chopper circuit 2. That is, the power converter circuit operates in the resonant mode if each of the currents mentioned above can be expressed as

$$i_x(t) = b \cdot e_x(t) \cdot \sin(2\pi f 2 \cdot t) \tag{8},$$

where  $i_x(t)$  denotes any of the currents explained above,  $e_x$  is a timely varying envelope of the respective current  $i_x(t)$ ,  $f\mathbf{2}$  is the switching frequency of the chopper circuit, and b is a (constant) proportionality factor. In the power converter circuit shown in FIG.  $\mathbf{10}$ , for example, the envelopes  $e_x(t)$  of the individual currents in the individual sub-periods are given as shown in Table 1 below. Table 1 shows the envelopes  $e_x(t)$  of the currents given in the left column in the three sub-periods  $0 < t < t_0$ ,  $t_0 < t < t_1$ , and  $t_1 < t < t_2$ .

TABLE 1

|  | e <sub>x</sub> (t)                   | $0 < t < t_0$     | $t_0 \le t \le t_1$ | t <sub>1</sub> < t < t <sub>2</sub> |  |  |  |

|--|--------------------------------------|-------------------|---------------------|-------------------------------------|--|--|--|

|  | i41 <sub>1</sub><br>i41 <sub>2</sub> | d*<br>0           | 2 - d*<br>d* - 1    | 0<br>3 - d*                         |  |  |  |

|  | $i_{C_p} = i31_n$                    | $\frac{d^*}{3}$   | $\frac{d^*}{3}$     | $2 \cdot \frac{3 - d^*}{3}$         |  |  |  |

|  | i31 <sub>2</sub>                     | $\frac{d^*}{3}$   | $\frac{3-2d^*}{3}$  | $\frac{d^*-3}{3}$                   |  |  |  |

|  | i31 <sub>1</sub>                     | $\frac{-2d^*}{3}$ | $\frac{d^*-3}{3}$   | $\frac{d^*-3}{3}$                   |  |  |  |

In Table 1,  $i31_1$ ,  $i31_2$ ,  $i31_n$  denote the currents through the respective windings of the autotransformer 31, and  $d^*$  is given by

$$d^* = \frac{3v_{OUT}}{V_{INO}}.$$

(9)

As mentioned above, the leakage inductances  $33_1$ ,  $33_2$ ,  $33_n$  can be obtained by measuring and/or simulating certain parameters of the autotransformer 31 before assembling the power converter circuit. As will be explained below, the inductances  $33_1$ ,  $33_2$ ,  $33_n$  shown in FIG. 10 can be obtained from leakage inductances of the autotransformer 31 between taps of the autotransformer. These taps include taps  $32_1$  and  $32_2$  explained above. For the purpose of explanation, a first input node where the autotransformer 31 is connected to the output of the chopper circuit 2 is referred to as tap  $32_n$  and a second input node where the autotransformer 31 is connected to the reference node 12 is referred to as tap  $32_0$  in the following.

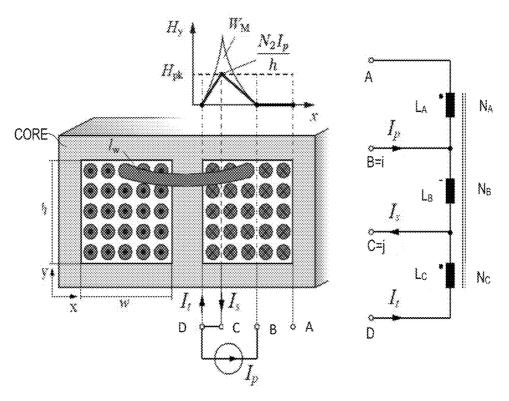

FIG. 15A schematically illustrates an autotransfonner with n=3 windings  $L_A$ ,  $L_B$ , and  $L_C$  wound around the same core and with four taps A, B, C, D, where A and D are the input nodes of the autotransformer and B and C are taps between  $L_A$  and  $L_B$  and between  $L_B$  and  $L_C$ , respectively. FIG. 15B shows an equivalent circuit diagram of the autotransformer shown in FIG. 15B. In this autotransformer shown in FIG. 15A, an average length of one turn of each winding is  $l_w$ , a width of a winding window of the core is w, and a height of the winding window is h. In the following,

based on FIGS. 15A and 15B, it is explained how the leakage inductance between two taps of the autotransformer may be calculated based on a model of the autotransformer. With reference to FIGS. 16A to 16C it is then explained how the leakage inductances of the autotransformer 31 shown in FIG. 10 can be calculated.

In the following  $L_{s(i,j)}$  denotes a leakage inductance between two taps i and j of an autotransformer. For the purpose of explanation, it is assumed that these taps are taps B and C of the autotransformer shown in FIGS. 15A and 15B. Referring to FIG. 15A, determining the leakage inductance  $L_{s(i,j)}$  includes calculating the leakage inductance  $L_{s(i,j)}$  based on the assumption that a current  $I_p$  is driven into tap i and winding  $L_C$  is short-circuited, that is, short tap C=j and tap D are short-circuited. A current  $I_p$  driven into tap B generates a magnetic field  $H_y$ . This magnetic field  $H_y$  and the magnetic energy  $W_M$  associated therewith is schematically illustrated in the graph drawn above the autotransformer shown in FIG. 15A. The magnetic energy stored in the autotransformer when operating the autotransformer in a configuration as shown in FIGS. 15A and 15B and when a current level of the current  $I_p$  is given by I can be calculated as:

$$\begin{split} W_{M(i,j)} &= \frac{1}{2} L_{s(i,j)} I^2 = \\ &\mu_0 \frac{l_w h}{2} \int_0^w H_y^2(x) \, dx = \mu_0 \frac{l_w h}{2} \left[ \int_0^{\frac{N_C}{N_{tot}} w} \left( \frac{1}{h} N_C \frac{N_B}{N_C} I \frac{x}{\frac{N_C}{N_{tot}} w} \right)^2 + \right. \\ &\left. \int_{\frac{N_C}{N_{tot}} w}^{\frac{N_B + N_C}{N_{tot}} w} \left( -\frac{1}{h} N_2 I \frac{x - \frac{N_B + N_C}{N_{tot}} w}{\frac{N_B}{N_{tot}} w} \right)^2 \right] = \frac{1}{2} \frac{\mu_0 l_w w}{h} \\ &\left. \left( \frac{N_{tot}}{3} \right)^2 I^2 \frac{3(N_B + N_C) N_B^2}{N_{tot}^3} \right. \\ &\left. \left( \frac{N_{tot}}{3} \right)^2 I^2 \frac{3(N_B + N_C) N_B^2}{N_{tot}^3} \right. \\ \end{split}$$

where

$$L_0 \approx \frac{\mu_0 l_w w}{h} \left(\frac{N_{tot}}{3}\right)^2, \tag{11}$$

and wherein  $N_B$  denotes the number of turns of winding  $L_B$ ,  $N_C$  denotes the number of turns of winding  $L_C$ ,  $N_D$  denotes the number of turns of winding  $L_D$ , and  $N_{tot}$  denotes the overall number of turns, which is  $N_{tot} = N_A + N_B + N_C$ . Based on equations (9) and (10), the leakage inductance  $L_{s(2,1)}$  can be expressed as

$$L_{s(i,j)} = L_{s(B,C)} = L_0 \frac{3(N_B + N_C)N_B^2}{N_{tot}^3}$$

(12)

Thus, the leakage inductance  $L_{s(B,C)}$  between two taps B,C of an autotransformer can be calculated based on the geometry of the transformer, which is included in  $L_0$ , based on the 60 number of turns  $N_B$  that are located between the taps B and C, the number of turns  $N_C$  that are short-circuited, and the overall number of turns  $N_{tot}$ .

In the following,  $L_s$  denotes the plurality of leakage inductances of the autotransformer 31 shown in FIG. 10. In this transformer 31, taps  $32_m$ ,  $32_2$ ,  $32_1$ ,  $32_0$  may briefly be referred to as taps n, 2, 1, and 0, respectively. Thus, for

18

example,  $L_{s(2,1)}$  denotes the leakage inductance between taps  $\bf 32_2$  and  $\bf 32_1$  of the autotransformer shown in FIG.  $\bf 10$ . The plurality of leakage inductances includes a leakage inductance  $L_{s(n,2)}$  between taps n and 2, a leakage inductance  $L_{s(n,1)}$  between taps n and 1, and a leakage inductance  $L_{s(2,1)}$  between taps 2 and 1.  $L_s$  is therefore given as:

$$L_{s} = [L_{s(n,2)}L_{s(n,1)}L_{(2,1)}]^{T} \approx \Lambda^{T}L_{0}$$

(13)

FIGS. 16A, 16B and 16C illustrate the set-up for calculating the leakage inductances  $L_{s(n,2)}$ ,  $L_{s(n,1)}$ , and  $L_{s(2,1)}$ , respectively, in the autotransformer 31 shown in FIG. 10. Calculating the leakage inductance  $L_{s(n,2)}$ , for example, includes referring to FIG. 16A driving a current I into tap n and short circuiting windings 31<sub>2</sub> and 31<sub>1</sub>. Comparing FIGS. 15B and 16A it can be seen that the number  $N_B$  of turns between the taps where the leakage inductance is to be determined equals  $N_n$  in FIG. 16A, and the number of turns  $N_C$  that are short-circuited equals  $N_2+N_1$  in FIG. 16A. Inserting  $N_B=N_n$  and  $N_C=N_1+N_2$  in equation (11) and assuming that the individual windings 31<sub>1</sub>, 31<sub>2</sub>, 31<sub>n</sub> have the same number of turns, so that  $N_1=N_2=N_n=1/3N_{tot}$ , it can be shown that

$$L_{s(n,2)} = \frac{1}{3} \cdot L_0$$

(14),

where  $L_0$  includes parameters of the transformer geometry and the overall number of turns, as explained with equation (10). Based on equation (12) and on what is shown in FIGS. **16**B and **16**C it can be shown that A is given as follows, if the individual windings  $\mathbf{31}_1$ ,  $\mathbf{31}_2$ ,  $\mathbf{31}_n$  have the same number of turns, so that  $N_1 = N_2 = N_n = 1/5 N_{tot}$ .

$$\Lambda = \left[\frac{1}{3} \frac{4}{3} \frac{2}{9}\right] \tag{15a}$$

Equation (10) and, therefore equation (12) from which equation (15a) had been derived, is based on the assumption that the windings of the autotransformer are connected in the same order as shown in FIGS. 10 and 16A to 16C, so that there is no interleaving in the winding arrangement. The curves drawn in dashed lines in the graphs shown in FIGS. 16A to 16C illustrate the magnetic field in the transformer in this case.

If the winding arrangement is modified, for example by interleaving the three windings 31<sub>n</sub>, 31<sub>2</sub>, 31<sub>1</sub>, which may reduce the magnetic energy and, therefore, result in a more efficient magnetic design, equation (10) is not valid anymore. For example, swapping the windings associated to 31<sub>2</sub> and 31<sub>1</sub> and repeating the procedure explained with reference to FIGS. 15 and 16A to 16C results in a magnetic field that is represented by the solid lines in the graphs shown in FIGS. 16A to 16C. As can be seen from FIG. 16B, for example, the magnetic field is reduced to 50%. In this case,

$$\Lambda = \left[ \frac{1}{3} \frac{1}{3} \frac{2}{9} \right]. \tag{15b}$$

The inductances gathered in Ls do not have a direct correspondence in the autotransformer equivalent circuit shown in FIGS. **10** and **15**. That is, inductances  $L_{s(n,2)}$ ,  $L_{s(n,1)}$ ,  $L_{s(2,1)}$  are not the inductances  $33_n$ ,  $33_2$ ,  $33_1$  shown in FIG. **10**. These inductances  $33_n$ ,  $33_2$ ,  $33_1$  are also referred to as  $L_{\infty n}$ ,  $L_{\infty 2}$ ,  $L_{\infty 1}$  in the following. One way of how  $L_{\infty n}$ ,  $L_{\infty 2}$ ,

$L_{\sigma 1}$  may be calculated based on Ls is explained below. For the purpose of explaining this calculation a compact notation is introduced as follows:

$$W_{M} = [W_{M(n,2)}W_{M(n,1)}W_{M(2,1)}]^{T}$$

(16) 5

$$W_E = [W_{E(n,2)}W_{E(n,1)}W_{E(2,1)}]^T (17)$$

$$L_{\sigma} = [L_{\sigma n} L_{\sigma 2} L_{\sigma 1}]^T \tag{18}$$

$$C_{\sigma}^{-1} = \left[ \frac{1}{C_p} \frac{1}{C_{top,2}} \frac{1}{C_{top,1}} \right]$$

(19)

where  $W_{E(i,j)}$  denotes the electrical energy and  $W_{M(i,j)}$  denotes the magnetic energy stored in the autotransformer when measuring  $L_{s(i,j)}$  as explained above. Furthermore,  $C_p$  is the capacitance of the chopper capacitor 22,  $C_{tap,2}$  is the capacitance of the second tap capacitor  $41_2$ , and  $C_{tap,1}$  is the capacitance of the first tap capacitor  $41_1$ .

Considering the current ratios shown in FIGS. 16A-C, the magnetic energy  $W_M$  stored in the autotransformer in each experiment is

$$W_M = \frac{1}{2} L_s I^2 = \frac{1}{2} M L_\sigma I^2 \tag{20}$$

so that

$$L_{\sigma} = M^{-1} \Lambda^T L_0 \tag{21}$$

where

$$M = \begin{bmatrix} 1 & \left(\frac{3}{2}\right)^2 & 0 \\ 1 & 0 & 3^2 \\ 0 & 1 & 2^2 \end{bmatrix}$$

(22)

Consequently, the capacitors  $C_{\sigma}^{-1}$  can be calculated as follows in order to tune the frequency of the currents in each sub-period to f2:

$$C_{\sigma}^{-1} = (2 \cdot \pi \cdot f^2)^2 M^{-1} \Lambda^T L_0 \tag{23}.$$

Thus, based on parameters of the autotransformer and in consideration of a desired switching frequency f2 of the chopper circuit 2 the capacitances of the chopper capacitor 22, and the tap capacitors 41, 41<sub>2</sub> can be suitably selected 50 in order to obtain sinusoidal current waveforms, that is, in order to operate the power converter circuit, in particular the chopper circuit 2 and the rectifier circuit 4 in a resonant fashion. The parameters of the transformer, such as the leakage inductances may be calculated as explained above, 55 measured and/or simulated before employing the autotransformer in the power converter circuit. Alternatively, these parameters may be obtained from a data sheet provided by the supplier of the autotransformer.

It should be noted that the topology shown in FIG. 10 is 60 only one of a plurality of suitable power converter topologies. Examples of some other topologies are explained with reference to FIGS. 17 to 20 herein below.

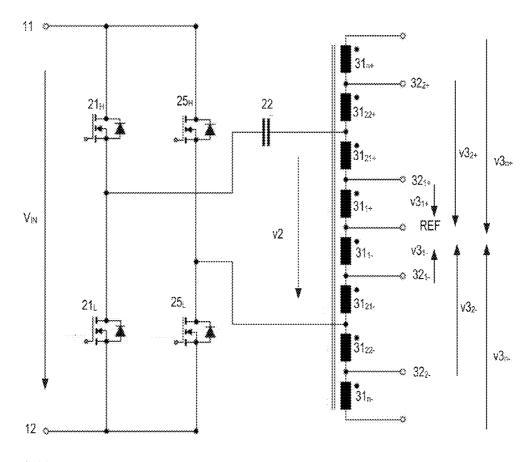

FIG. 17 shows a chopper circuit 2, a rectifier circuit 4 and a selector circuit 5 of a power converter circuit according to another example. In this example, the chopper circuit 2 has the same topology as explained with reference to FIGS. 4

20

and 10 herein before. The autotransformer 31 has the same topology as the autotransformer 31 explained before, but is connected between the output of the chopper circuit 2 and a reference node REF that is different from the second output node. This reference node REF is formed by a tap of a capacitive voltage divider with a first capacitor  $23_1$  and a second capacitor  $23_2$  wherein this capacitive voltage divider  $23_1$ ,  $23_2$  is connected between the first input node 11 and the second input node 12. According to example, voltage divider capacitors have the same capacitance so that the voltage at the reference node REF is  $V_{IV}/2$  as referenced to the second input node 12. The chopper voltage  $v^2$  is the voltage between the output 24 of the chopper circuit 2 and the reference node REF. This chopper voltage again is a zero-mean square wave voltage with a frequency of f2.

The rectifier stages  $\mathbf{4}_1$ ,  $\mathbf{4}_2$  are different from the rectifier stages  $\mathbf{4}_1$ ,  $\mathbf{4}_2$  shown in FIG. 10 in that each rectifier stage  $\mathbf{4}_1$ ,  $\mathbf{4}_2$  includes two output capacitors  $\mathbf{43}_{1+}$ ,  $\mathbf{43}_{1-}$ , and  $\mathbf{43}_{2+}$ ,  $\mathbf{43}_{2-}$ , respectively, wherein one circuit node of each of these capacitors is connected to the reference node REF. One way of operation of these rectifier circuits  $\mathbf{4}_1$ ,  $\mathbf{4}_2$  is explained with reference to the rectifier stage  $\mathbf{4}_1$  in the following. The rectifier stage  $\mathbf{4}_2$  operates equivalently.