#### US009762134B2

# (12) United States Patent Deboy et al.

(10) Patent No.: US 9,762,134 B2

(45) **Date of Patent:** Sep. 12, 2017

#### (54) MULTI-CELL POWER CONVERSION METHOD AND MULTI-CELL POWER CONVERTER

# (71) Applicant: Infineon Technologies Austria AG,

Villach (AT)

(72) Inventors: **Gerald Deboy**, Klagenfurt (AT);

Johann Kolar, Zurich (CH); Matthias

Kasper, Zurich (CH)

(73) Assignee: Infineon Technologies Austria AG,

Villach (AT)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 210 days.

(21) Appl. No.: 14/479,711

(22) Filed: Sep. 8, 2014

## (65) **Prior Publication Data**

US 2016/0072394 A1 Mar. 10, 2016

(51) Int. Cl.

H02M 3/335

(2006.01)

H02M 7/217

(2006.01)

H02M 1/00

(2006.01)

H02M 7/483

(2007.01)

(52) U.S. Cl.

CPC ...... **H02M 3/33592** (2013.01); **H02M 7/217** (2013.01); H02M 2001/0074 (2013.01); H02M 2001/0077 (2013.01); H02M 2007/4835 (2013.01)

## (58) Field of Classification Search

CPC ...... H02M 3/33592; H02M 7/217; H02M 2007/4835; H02M 2001/0077; H02M

2001/0074

See application file for complete search history.

## (56) References Cited

#### U.S. PATENT DOCUMENTS

| 7,046,534 B2    | 5/2006      | Schmidt et al.  |  |

|-----------------|-------------|-----------------|--|

| 7,212,419 B2    | 5/2007      | Vinciarelli     |  |

| 7,411,802 B2    | 8/2008      | Victor et al.   |  |

| 8,238,128 B2    | 8/2012      | Falk            |  |

| 9,397,580 B1    | 7/2016      | Alexander       |  |

| 2002/0024824 A1 | 2/2002      | Reinold et al.  |  |

| 2004/0218318 A1 | 11/2004     | Bijlenga et al. |  |

| 2005/0270812 A1 | 12/2005     | Vinciarelli     |  |

|                 | (Continued) |                 |  |

#### FOREIGN PATENT DOCUMENTS

| CN | 101473506 A | 7/2009 |

|----|-------------|--------|

| CN | 101635505 A | 1/2010 |

|    | (Cont       | inued) |

#### OTHER PUBLICATIONS

Everts, J. et al., "Comparative Evaluation of Soft-Switching, Bidirectional, Isolated AC/DC Converter Topologies", 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, Feb. 5-9, 2012, pp. 1067-1074. (Continued)

Primary Examiner — Jue Zhang (74) Attorney, Agent, or Firm — Murphy, Bilak & Homiller, PLLC

## (57) ABSTRACT

A method includes converting power by a power converter comprising a plurality of converter cells, and selectively operating at least one converter cell of the plurality of converter cells in one of an active and an inactive mode based on a level of a power reference signal.

## 35 Claims, 57 Drawing Sheets

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 2006/0226130 | A1* | 10/2006 | Kooken B23K 9/1056      |

|--------------|-----|---------|-------------------------|

|              |     |         | 219/130.1               |

| 2008/0123374 | A1  | 5/2008  | Vinciarelli             |

| 2010/0007221 | A1* | 1/2010  | Ye H02M 7/493           |

|              |     |         | 307/151                 |

| 2010/0066319 | A1* | 3/2010  | Qiu H02M 3/1584         |

|              |     |         | 323/272                 |

| 2010/0314937 | A1  | 12/2010 | Jacobson et al.         |

| 2011/0127976 | A1* | 6/2011  | Hiltbrunner H02M 3/1584 |

|              |     |         | 323/272                 |

| 2011/0140535 | A1  | 6/2011  | Choi et al.             |

| 2011/0267845 | A1* | 11/2011 | Ye H02M 3/33569         |

|              |     |         | 363/21.02               |

| 2012/0155125 | A1  | 6/2012  | Zhang et al.            |

| 2012/0267955 | A1  | 10/2012 | Zhan et al.             |

| 2013/0009700 | A1  | 1/2013  | Deboy et al.            |

| 2013/0320769 | A1* | 12/2013 | Sawyers G06F 1/263      |

|              |     |         | 307/80                  |

| 2013/0334212 | A1  | 12/2013 | Sawada et al.           |

| 2014/0063884 | A1  | 3/2014  | Itoh et al.             |

| 2014/0153294 | A1  | 6/2014  | Deboy et al.            |

| 2014/0266131 | A1  | 9/2014  | Deboy et al.            |

| 2015/0029761 | A1  | 1/2015  | Trinh et al.            |

| 2015/0222170 | A1  | 8/2015  | Berger et al.           |

| 2015/0357912 | A1  | 12/2015 | Perreault et al.        |

| 2015/0372614 | A1  | 12/2015 | Yamada                  |

| 2016/0065081 | A1  | 3/2016  | Raju et al.             |

#### FOREIGN PATENT DOCUMENTS

| CN | 102742134 A   | 10/2012 |

|----|---------------|---------|

| EP | 0557599 A1    | 12/1992 |

| JP | S48091548 A   | 11/1973 |

| JP | H4261360 A    | 9/1992  |

| JP | H7154967 A    | 6/1995  |

| JP | H865889 A     | 3/1996  |

| JP | H8126352 A    | 5/1996  |

| JP | H1189242 A    | 3/1999  |

| JP | 2004266884 A  | 9/2004  |

| JP | 2008005657 A  | 1/2008  |

| JP | 2008099464 A  | 4/2008  |

| JP | 2008228517 A  | 9/2008  |

| JP | 2008301640 A  | 12/2008 |

| JP | 2009513101 A  | 3/2009  |

| JP | 2009165222 A  | 7/2009  |

| JP | 2009201350 A  | 9/2009  |

| JP | 2009232587 A  | 10/2009 |

| JP | 2012010420 A  | 1/2012  |

| JP | 2012114971 A  | 6/2012  |

| JP | 2012147559 A  | 8/2012  |

| JP | 2012210013 A  | 10/2012 |

| JP | 2013059251 A  | 3/2013  |

| JP | 2013255308 A  | 12/2013 |

| JP | 2014054121 A  | 3/2014  |

| WO | 2011033698 A  | 3/2011  |

| WO | 2011033820 A1 | 3/2011  |

| WO | 2013017994 A1 | 2/2013  |

| WO | 2013093963 A1 | 6/2013  |

|    |               |         |

## OTHER PUBLICATIONS

Fiorentino, C. et al., "A Line Cycle Skipping Method to Improve the Light Load Efficiency and THD of PFC Converters", 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, Mar. 17-21, 2013, pp. 368-373.

Giri, R. et al., "Common-Duty-Ratio Control of Input-Series Connected Modular DC-DC Converters with Active Input Voltage and Load-Current Sharing", IEEE Transactions on Industry Applications, vol. 42, No. 4, Jul.-Aug. 2006, pp. 1101-1111.

Gong, G. et al., "A Comparative Study of Multicell Amplifiers for AC-Power-Source Applications", IEEE Transactions on Power Electronics, vol. 26, No. 11, Jan. 2011, pp. 149-164.

Huber, L. et al., "Comparison of Audible Noise Caused by Magnetic Components in Switch-Mode Power Supplies Operating in Burst Mode and Frequency-Foldback Mode", 2014 Twenty-Ninth Annual IEEE Applied Power Electronics Conference and Exposition, Fort Worth, TX, Mar. 16-20, 2014, pp. 2895-2901.

Worth, TX, Mar. 16-20, 2014, pp. 2895-2901. Iman-Eini, H. et al., "A Modular AC/DC Rectifier Based on Cascaded H-Bridge Rectifier", 13th Power Electronics and Motion Control Conference, 2008 (EPE-PEMC 2008), Ponzan, Sep. 1-3, 2008, pp. 173-180.

Iman-Eini, H. et al., "A Modular Strategy for Control and Voltage Balancing of Cascaded H-Bridge Rectifiers", IEEE Transactions on Power Electronics, vol. 23, No. 5, Sep. 2008, pp. 2428-2442.

Kang, D.-W. et al., "A Simple Method for Acquiring the Conducting Angle in a Multilevel Cascaded Inverter using Step Pulse Waves", IEE Proceedings Electric Power Applications, vol. 152, Issue 1, Jan. 7, 2005, pp. 103-111.

Krismer, F. et al., "Closed Form Solution for Minimum Conduction Loss Modulation of DAB Converters", IEEE Transactions on Power Electronics, vol. 27, No. 1, Jan. 2012, pp. 174-188.

Lai, J.-S. et al., "Multilevel Converters—A New Breed of Power Converters", IEEE Transactions on Industry Applications, vol. 32, Issue 3, May-Jun. 1996, pp. 509-517.

Malinowski, M. et al., "A Survey on Cascadd Multilevel Inverters", IEEE Transactions on Industrial Electronics, vol. 57, No. 7, Jul. 2010, pp. 2197-2206.

Rodriguez, J. et al., "Multilevel Inverters: A Survey of Topologies, Controls and Applications", IEEE Transactions on Industrial Electronics, vol. 49, No. 4, Aug. 2002, pp. 724-738.

Rufer, A.-C., "An Aid in the Teaching of Multilevel Inverters for High Power Applications", 26th Annual IEEE Power Electronics Specialists Conference, 1995 (PESC '95 Record), vol. 1, Atlanta, GA, Jun. 18-22, 1995, pp. 247-252.

Schminke, W., "Hochleistungsmodulator in PSM-Technik für 500-kW-Kurzwellen- und 600-kW-Mittelwellensender", Brown Boveri Review, vol. 72, No. 5, 1985, pp. 235-240.

Shi, J. et al., "Research on Voltage and Power Balance Control for Cascaded Modular Solid-State Transformer", IEEE Transactions on Power Electronics, vol. 26, No. 4, Apr. 2011, pp. 1154-1166.

Tolbert, L. M. et al., "Multilevel Converters for Large Electric Drives", IEEE Transactions on Industry Applications, vol. 35, No. 1, Jan.-Feb. 1999, pp. 36-44.

Van Der Merwe, W. et al., "Natural Balancing of the Two-Cell Back-to-Back Multilevel Converter with Specific Application to the Solid-State Transformer Concept", 4th IEEE Conference on Industrial Electronics and Applications, 2009 (ICIEA 2009), Xi'an, May 25-27, 2009, pp. 2955-2960.

Zhao, T. et al., "Voltage and Power Balance Control for a Cascaded H-Bridge Converter-Based Solid-State Transformer", IEEE Transactions on Power Electronics, vol. 28, No. 4, Apr. 2013, pp. 1523-1532.

Zhou, L. et al., "99% Efficiency True-Bridgeless Totem-Pole PFC Based on GaN HEMTs", Available online at: http://www.transphormusa.com/sites/default/files/transphorm/news/Totem-

pole&20paper\_0.pdf, publication date unknown, pp. 1-9.

Huber, J. et al., "Optimum Number of Cascaded Cells for High-Power Medium-Voltage Multilevel Converters", Proceedings of the IEEE Energy Conversion and Exposition (ECCE USA 2013), Denver, Colorado, USA, Sep. 15-19, 2013, pp. 359-366.

Rothmund, D. et al., "Sic-Based Unidirectional Solid-State Transformer Concepts for Directly Interfacing 400V DC to Medium-Voltage AC Distribution Systems", 2014 IEEE 36th International Telecommunications Energy Conference (INTELEC), Vancouver, British Columbia, Canada, Sep. 29-Oct. 2, 2014, pp. 1-9.

Dodge, Jonathan, "Power MOSFET Tutorial", Advanced Power Technology, Application Note, APT-0403 Rev B, Mar. 2, 2006, pp. 1-12.

<sup>\*</sup> cited by examiner

FIG 1

**IPOP**

FIG 7

Sep. 12, 2017

FIG 12

FIG 15

FIG 16

FIG 17

FIG 18

FIG 19A FIG 19B

FIG 20

FIG 21

FIG 22

FIG 23

FIG 25A

FIG 25B

FIG 26A

FIG 27

FIG 29

FIG 30

FIG 31

FIG 32Å

FIG 32B

FIG 33

FIG 34

FIG 35

$V_{\text{OUT\_M}}$

lout\_m

FIG 36

51

**FILTER**

522

FIG 37

FIG 39

FIG 41A

N3-1

2

POUT\_THS POUT\_THS POUT\_THS POUT\_THS POUT\_THS POUT\_REF POUT\_THS POU

PHASE SHEDDING IN A MULTI-CELL CONVERTER WITH OP TOPOLOGY

FIG 43

**FIG 44**

FIG 45A

FIG 45B

FIG 46

PHASE SHEDDING IN A MULTI-CELL CONVERTER WITH IP TOPOLOGY

FIG 48

FIG 49

FIG 50

FIG 51

FIG 52

FIG 54

FIG 55

INTERMITTENT OPERATION IN A MULTI-CELL CONVERTER WITH OP TOPOLOGY

INTERMITTENT OPERATION IN A MULTI-CELL CONVERTER WITH IP TOPOLOGY

FIG 58

FIG 59

FIG 60

FIG 65

FIG 66

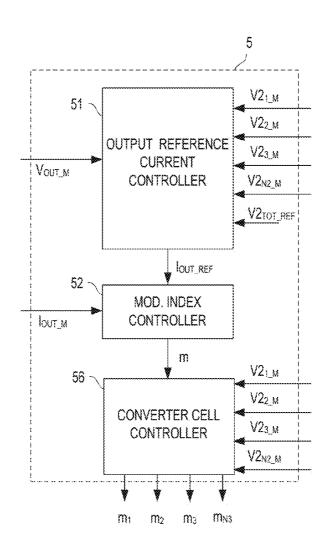

Vоит\_и CONTROLLER  $V2_{N2\_M}$ V2TOT\_REF OUT\_REP 52 MOD. INDEX CONTROLLER OUT\_M 54 CONVERTER AND FILTER CELL CONTROLLER  $m_1$  $m_2$  $m_3$ m<sub>N3</sub>  $m_0$

FIG 69

FIG 71

FIG 72

FIG 73

FIG 75

FIG 76B

FIG 77

FIG 78

FIG 79A

FIG 79B

FIG 80

Sep. 12, 2017

FIG 83

**FIG 84**

FIG 85

FIG 86

FIG 87

FIG 89

FIG 90

# MULTI-CELL POWER CONVERSION METHOD AND MULTI-CELL POWER **CONVERTER**

### TECHNICAL FIELD

This disclosure in general relates to power conversion methods, and to power converters.

### BACKGROUND

Power conversion is an important issue in many different electronic applications. An important aspect in almost every kind of power conversion is to efficiently convert the power, that is, to keep losses that may occur in connection with the power conversion as low as possible.

### **SUMMARY**

According to one embodiment, a method includes converting power by a power converter which includes a plurality of converter cells, and selectively operating at least one converter cell of the plurality of converter cells in one of an active and an inactive mode based on a level of a power 25 a multi-cell power converter shown in FIG. 12. reference signal.

According to one embodiment, a method includes receiving a periodic voltage by a power converter which includes a plurality of converter cells, and selectively operating at least one converter cell of the plurality of converter cells in 30 one of an active and an inactive mode based on a change of a voltage level of the periodic voltage such that within one period of the periodic voltage, the number of active converter cells changes as the voltage level of the periodic voltage changes.

According to one embodiment, a power converter circuit includes at least one power converter, wherein the power converter includes a plurality of converter cells, and a controller configured to operate at least one converter cell of the plurality of converter cells in one of an active and an inactive mode based on a level of a power reference signal.

According to one embodiment, a power converter circuit includes a power converter which includes a plurality of converter cells and is configured to receive a periodic 45 voltage, and a controller. The controller is configured to selectively operate at least one converter cell of the plurality of converter cells in one of an active and an inactive mode based on a change of the periodic voltage such that within one period of the periodic voltage, the number of active 50 converter cells changes as a voltage level of the periodic voltage changes.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Examples are explained below with reference to the drawings. The drawings serve to illustrate certain principles, so that only aspects necessary for understanding these principles are illustrated. The drawings are not to scale. In the drawings the same reference characters denote like 60 features.

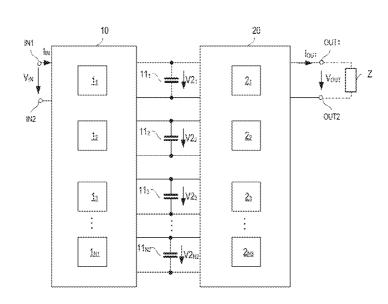

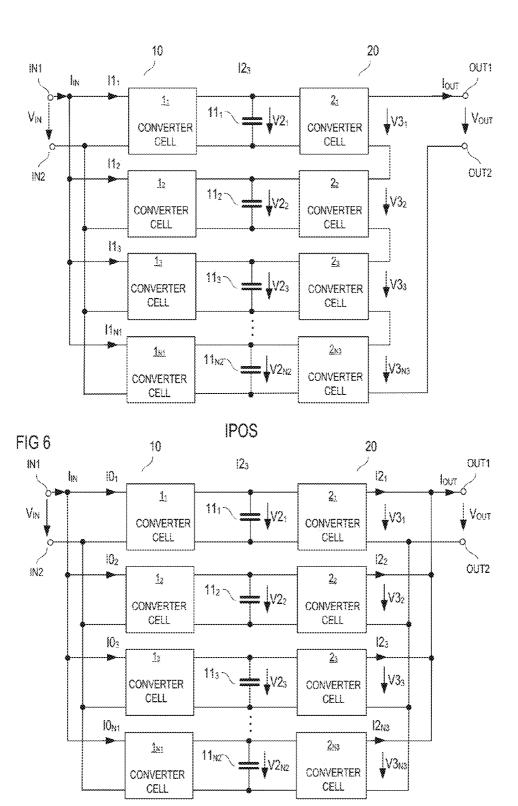

- FIG. 1 illustrates a power converter circuit with two power converters.

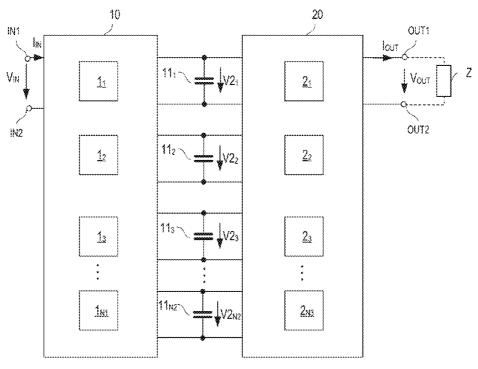

- FIGS. 2A-2C show timing diagrams which illustrate some different types of power conversion methods.

- FIGS. 3A-3C show timing diagrams which illustrate some different types of power conversion methods.

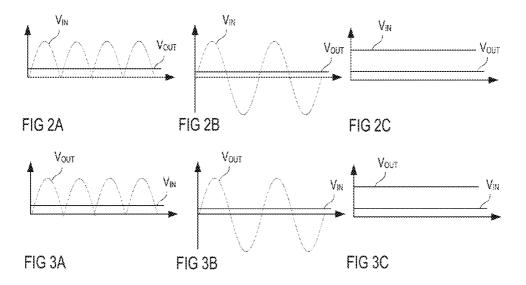

- FIG. 4 shows one embodiment of a power converter circuit having an ISOP (Input Serial, Output Parallel) topol-

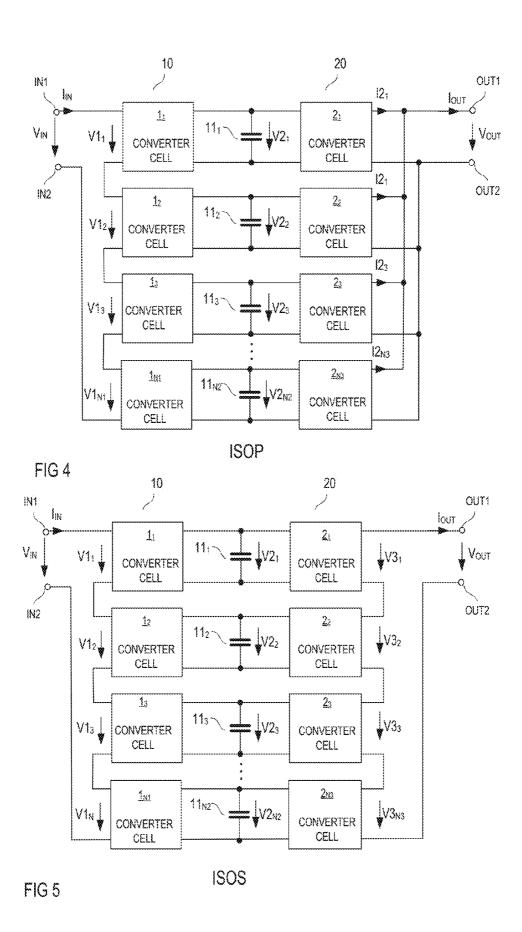

- FIG. 5 shows one embodiment of a power converter 5 circuit having an ISOS (Input Serial, Output Serial) topol-

- FIG. 6 shows one embodiment of a power converter circuit having an IPOS (Input Parallel, Output Serial) topol-

- FIG. 7 shows one embodiment of a power converter circuit having an IPOP (Input Parallel, Output Parallel)

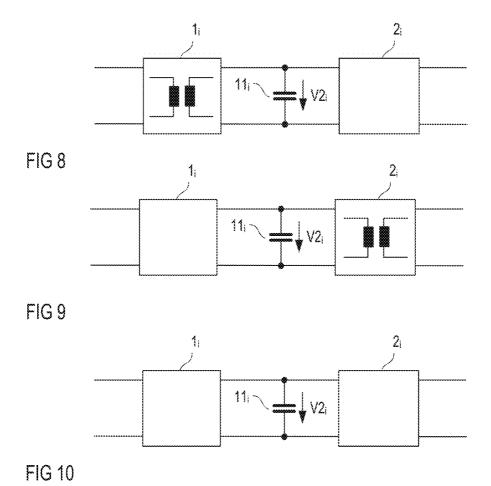

- FIG. 8 shows two converter cells of a power converter circuit from which one has an isolating topology and one has 15 a non-isolating topology.

- FIG. 9 shows two converter cells of a power converter circuit from which one has an isolating topology and one has a non-isolating topology.

- FIG. 10 shows two converter cells of a power converter circuit, both having a non-isolating topology.

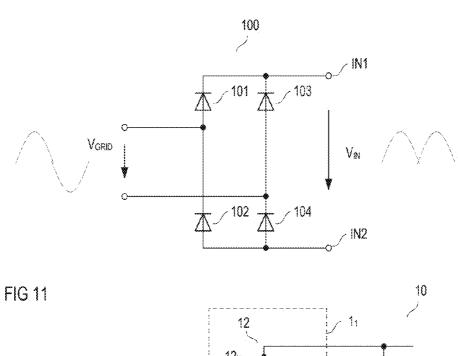

- FIG. 11 shows one embodiment of a rectifier circuit.

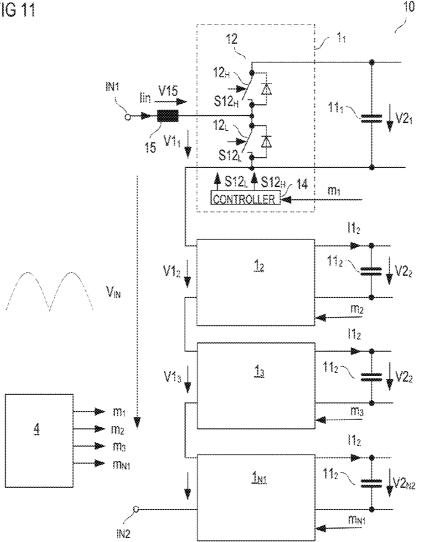

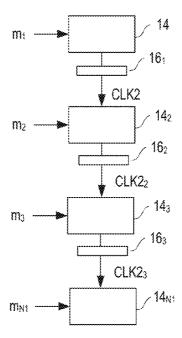

- FIG. 12 shows one embodiment of a multi-cell power converter with an IS (Input Serial) topology.

- FIG. 13 shows one embodiment of a main controller in the

- FIG. 14 shows one embodiment of the controller shown in FIG. 13 in greater detail.

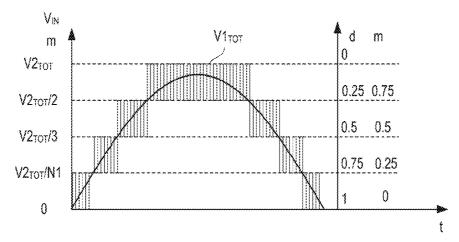

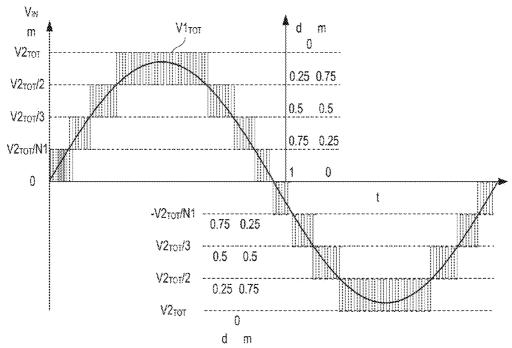

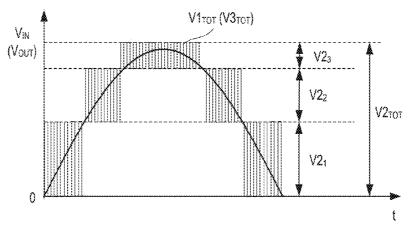

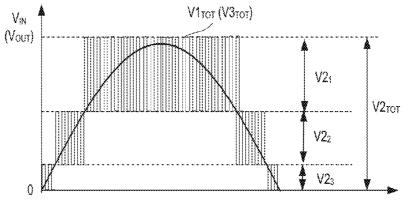

- FIG. 15 schematically illustrates one embodiment of an input voltage of the multi-cell power converter shown in FIG. 12, and of a corresponding modulation index.

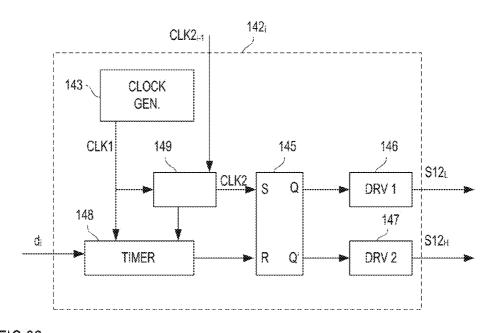

- FIG. 16 shows one embodiment of a cell controller of one converter cell in the multi-cell power converter shown in FIG. 12.

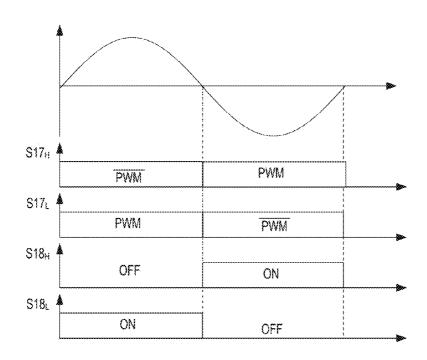

- FIG. 17 shows timing diagrams which illustrate one way 35 of operation of the controller shown in FIG. 16.

- FIG. 18 shows one embodiment of a PWM controller in the cell controller shown in FIG. 17.

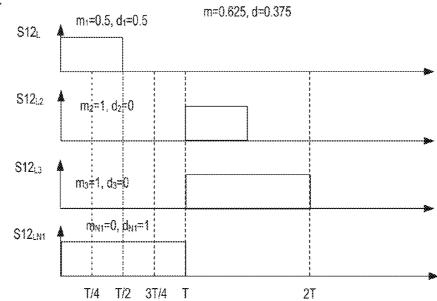

- FIGS. 19A-19B show timing diagrams which illustrates one way of operation of the multi-cell power converter shown in FIG. 12 at different modulation indices.

- FIG. 20 schematically illustrates one embodiment of an input voltage waveform of the multi-cell power converter shown in FIG. 12, and of a corresponding total cell input voltage.

- FIG. 21 illustrates how cell controllers in individual converter cells of the multi-cell power converter shown in FIG. 12 may be synchronized.

- FIG. 22 shows a modification of the PWM controller shown in FIG. 18.

- FIG. 23 shows timing diagrams which illustrate another way of operation of the multi-cell power converter shown in FIG. 12.

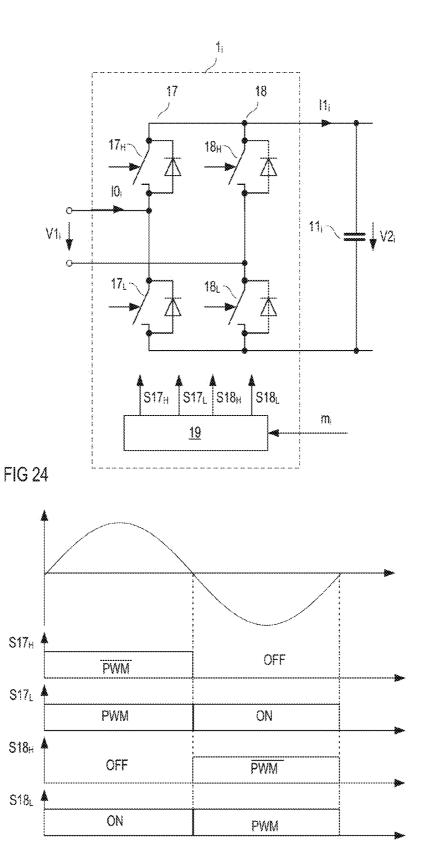

- FIG. 24 shows a converter cell of a multi-cell power converter according to one embodiment.

- FIGS. 25A-25B show timing diagrams which illustrate one way of operation of the converter cell shown in FIG. 24.

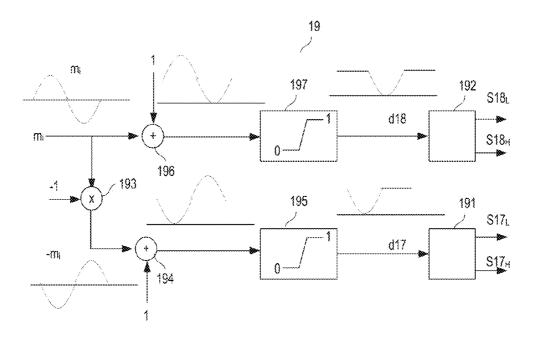

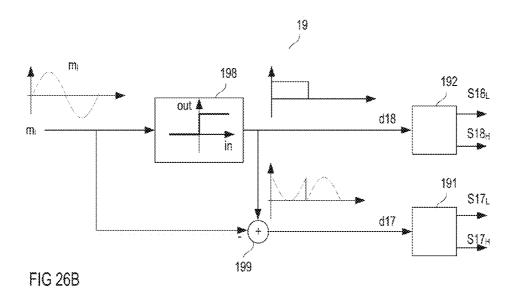

- FIGS. 26A-26B show two embodiments of a cell controller in the converter cell shown in FIGS. 25A-25B.

- FIG. 27 schematically illustrates one embodiment of an input voltage waveform of a multi-cell power converter shown in FIG. 12 when implemented with a converter cell shown in FIG. 24, and of a corresponding total cell input voltage.

- FIG. 28 shows a modification of the main controller 65 shown in FIG. 14.

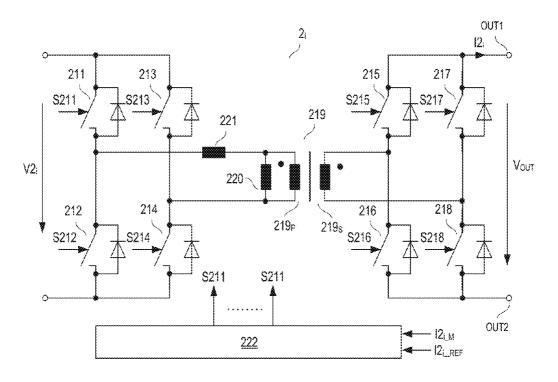

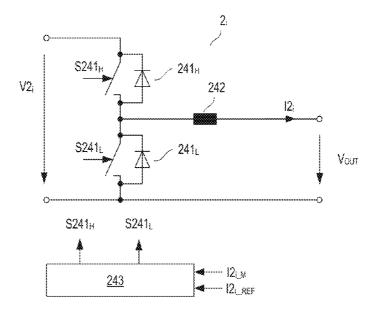

- FIG. 29 shows one embodiment of a multi-cell power converter with an IP (Input Parallel) topology.

FIG. 30 shows one embodiment of a controller in one of the converter cells shown in FIG. 29.

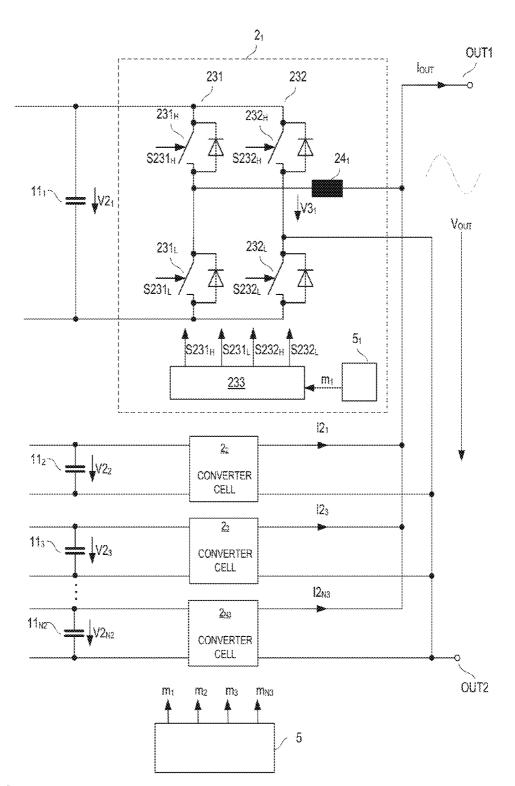

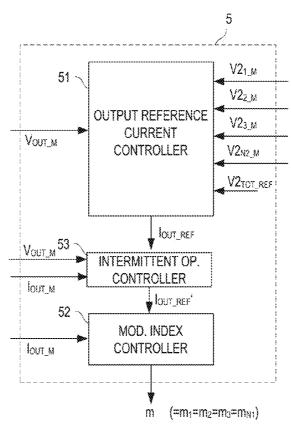

FIG. 31 shows one embodiment of a multi-cell power converter with an OP (Output Parallel) topology.

FIGS. 32A-32B shows two embodiments of a converter cell which may be used in the multi-cell power converter shown in FIG. 31.

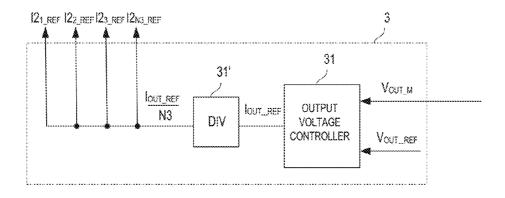

FIG. 33 shows one embodiment of a main controller in the multi-cell power converter shown in FIG. 31.

FIG. 34 shows one embodiment of a multi-cell power converter with an OS (Output Serial) topology.

FIG. 35 shows one embodiment of a main controller of the multi-cell power converter shown in FIG. 34.

FIG. 36 shows one embodiment of the main controller 15 shown in FIG. 35 in greater detail.

FIG. 37 shows one embodiment of a multi-cell power converter with an OP (Output Parallel) topology.

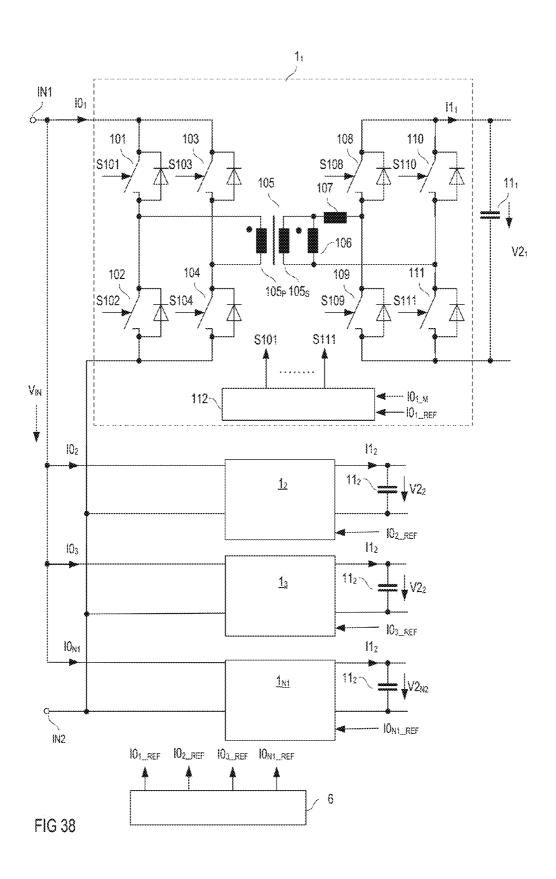

FIG. 38 shows one embodiment of a multi-cell power converter with an IP (Input Parallel) topology.

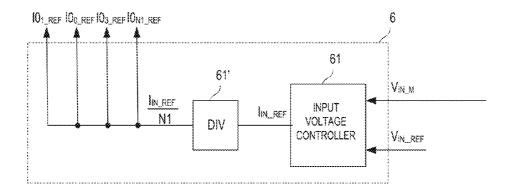

FIG. 39 shows one embodiment of a main controller in the multi-cell power converter shown in FIG. 38.

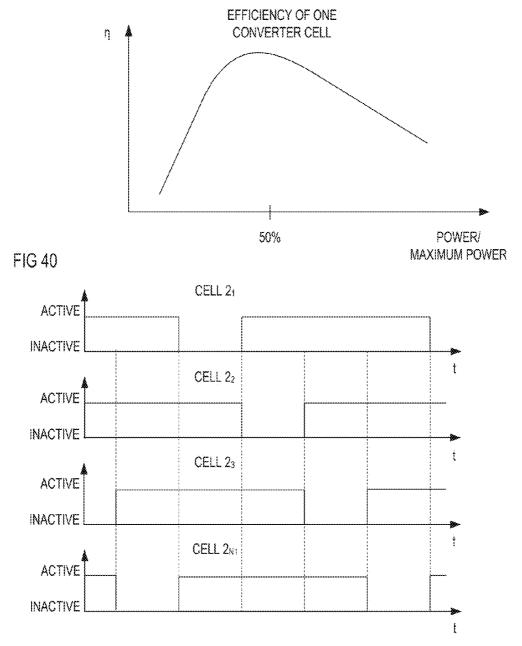

FIG. 40 schematically illustrates the efficiency of a converter cell based on the power level of the converted power.

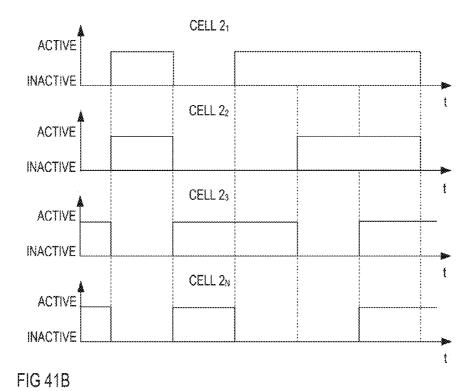

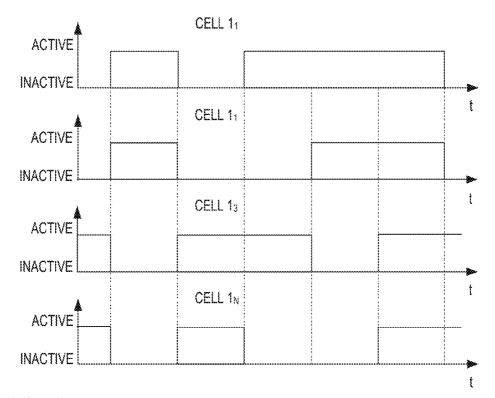

FIGS. 41A-41B show timing diagrams which illustrate 25 activating and deactivating converter cells (phase shedding) in a multi-cell power converter with OP topology.

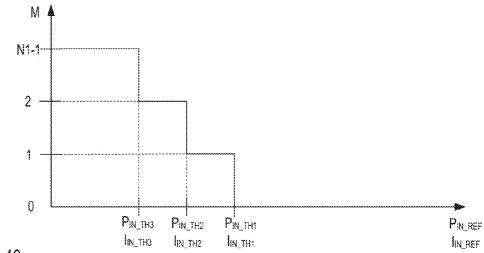

FIG. 42 schematically illustrates how a number of inactive converter cells may be set in a multi-cell power converter with OP topology dependent on an output power.

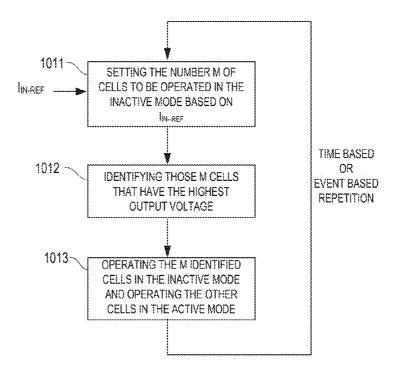

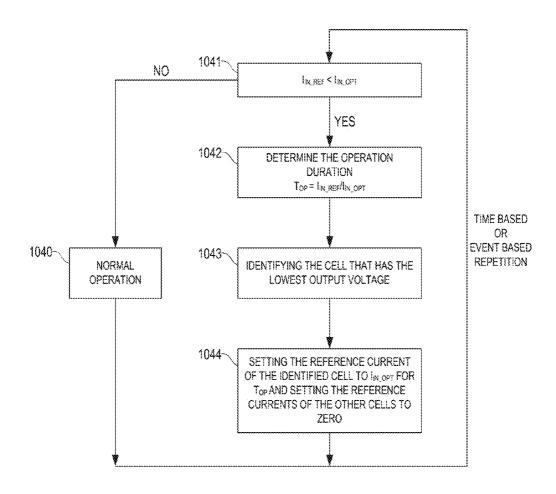

FIG. 43 illustrates one embodiment of operating a multicell converter with OP topology.

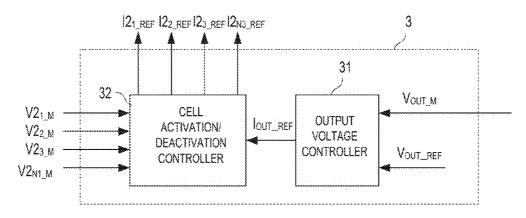

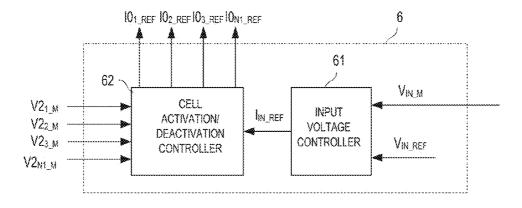

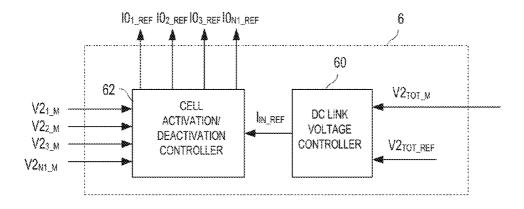

FIG. 44 shows one embodiment of a main controller in a multi-cell power converter having a phase shedding functionality.

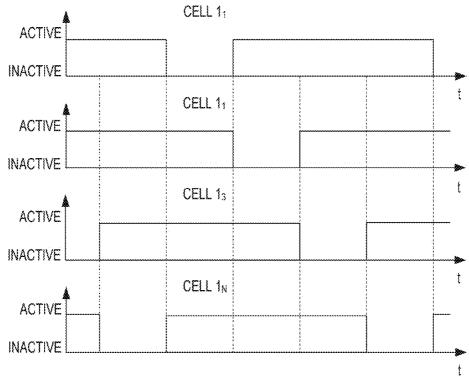

FIGS. 45A-45B show timing diagrams which illustrate activating and deactivating converter cells (phase shedding) in a multi-cell power converter with IP topology.

tive converter cells may be set in a multi-cell power converter with IP topology dependent on an output power.

FIG. 47 illustrates one embodiment of operating a multicell converter with OP topology.

FIG. 48 shows one embodiment of a main controller in a 45 multi-cell power converter having a phase shedding functionality.

FIG. 49 shows one embodiment of a main controller in a multi-cell power converter having a phase shedding functionality.

FIG. 50 shows timing diagrams which illustrate one way of operation of an IS or OS multi-cell converter in an intermittent operation mode.

FIG. 51 shows one embodiment of a main controller in an functionality.

FIG. 52 shows one embodiment of a main controller in an IS multi-cell converter having an intermittent operation

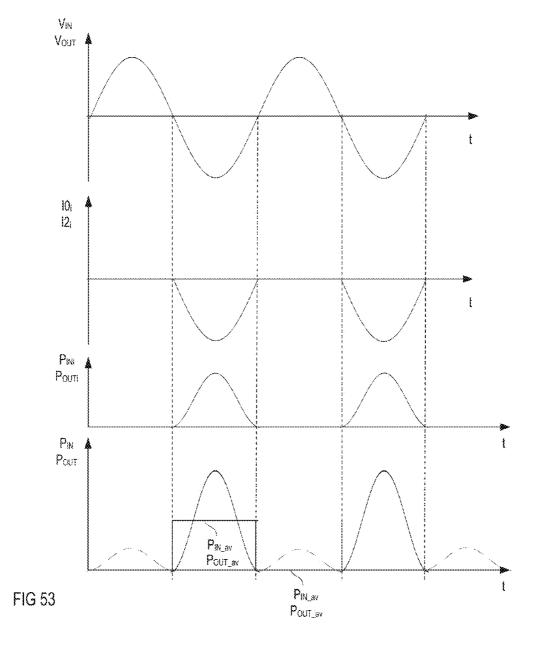

FIG. 53 shows timing diagrams which illustrate one way 60 of operation of an IP or OP multi-cell converter in an intermittent operation mode.

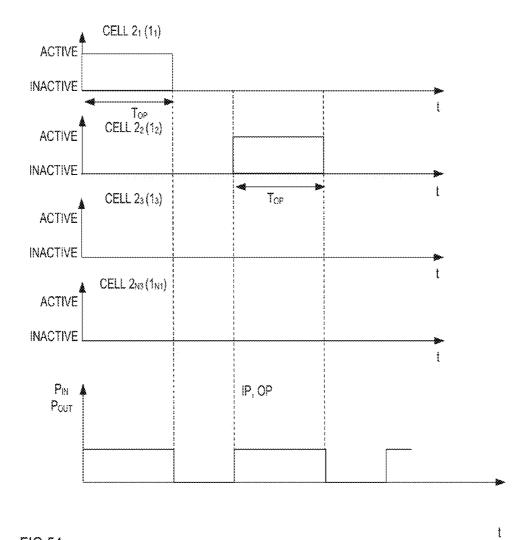

FIG. 54 shows timing diagrams which illustrate one way of operation of an IP or OP multi-cell converter in an intermittent operation mode.

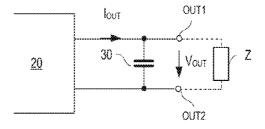

FIG. 55 shows one section of a power converter circuit which includes an output capacitor.

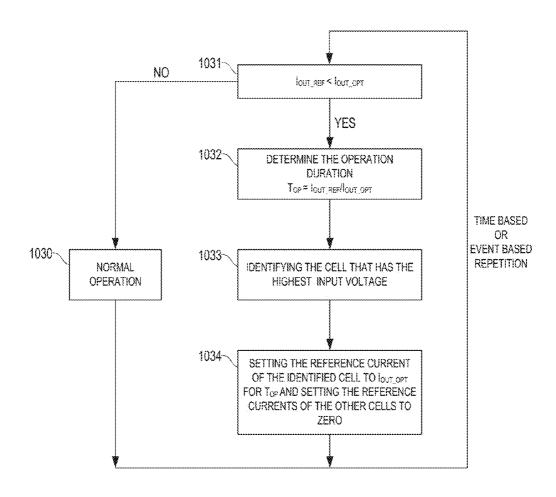

FIG. 56 illustrates one embodiment of operating a multicell converter with OP topology in an intermittent operation

FIG. 57 illustrates one embodiment of operating a multicell converter with IP topology in an intermittent operation

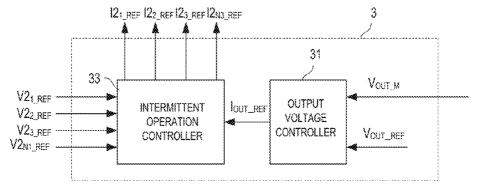

FIG. 58 shows one embodiment of a main controller in a multi-cell converter with OP topology.

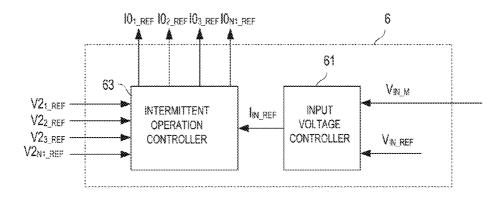

FIG. 59 shows one embodiment of a main controller in a multi-cell converter with IP topology.

FIG. 60 shows one embodiment of a multi-cell converter which includes a filter cell.

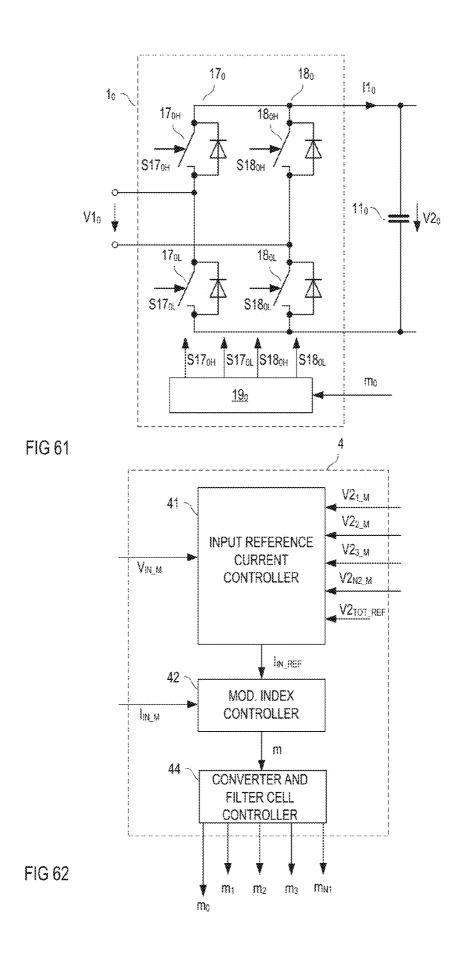

FIG. 61 shows one embodiment of the filter cell shown in FIG. 60.

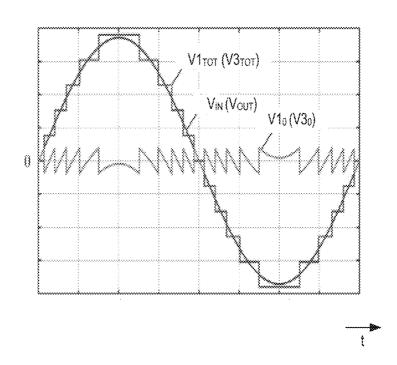

FIG. 62 shows one embodiment of a main controller in the multi-cell converter shown in FIG. 60.

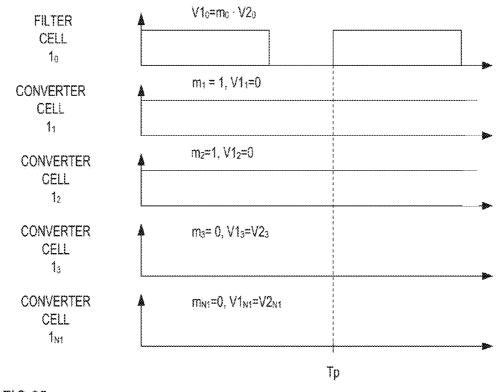

FIG. 63 shows timing diagrams which illustrate one way of operation of the multi-cell converter shown in FIG. 60.

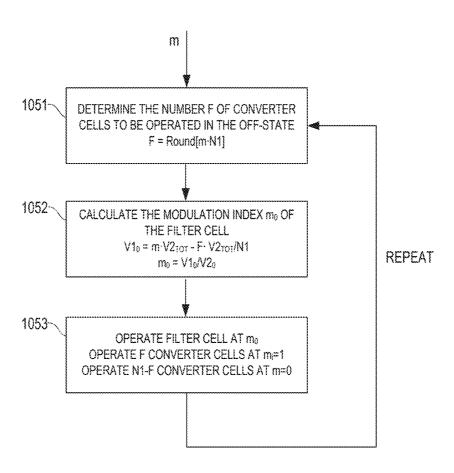

FIG. 64 shows one embodiment of operating the multi-20 cell converter shown in FIG. 60.

FIG. 65 shows timing diagrams which illustrate one way of operation of the multi-cell converter shown in FIG. 60.

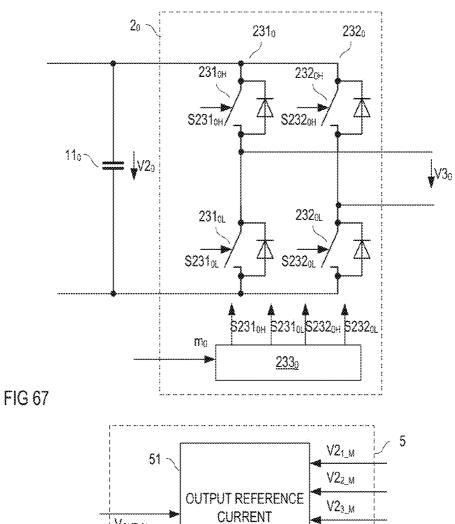

FIG. 66 shows one embodiment of a multi-cell converter which includes a filter cell.

FIG. 67 shows one embodiment of the filter cell shown in FIG. 66.

FIG. 68 shows one embodiment of a main controller in the multi-cell converter shown in FIG. 66.

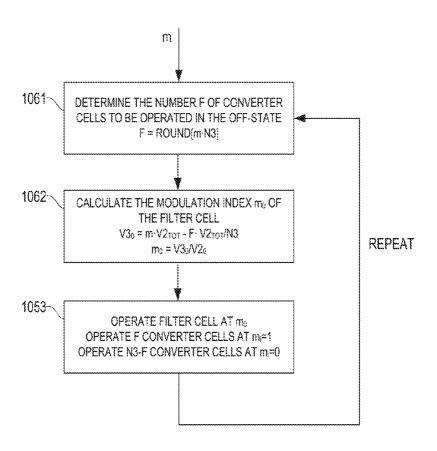

FIG. 69 shows one embodiment of operating the multi-30 cell converter shown in FIG. 66.

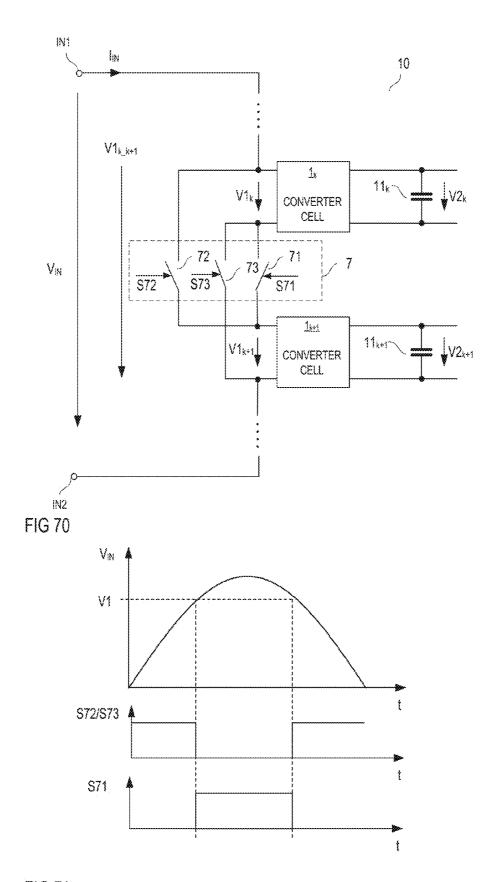

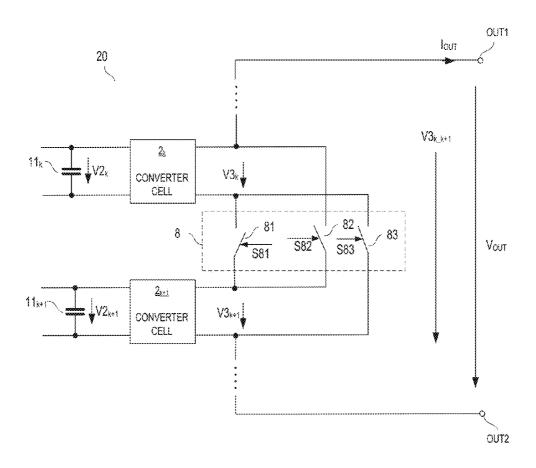

FIG. 70 shows two converter cells of a multi-cell converter and a switch circuit which connects the cell inputs either in series or in parallel.

FIG. 71 shows timing diagrams which illustrate one way 35 of operation of the converter cells shown in FIG. 70.

FIG. 72 shows one embodiment of a main controller in a multi-cell converter with two rearrangeable converter cells as shown in FIG. 70.

FIG. 73 shows two converter cells of a multi-cell con-FIG. 46 schematically illustrates how a number of inac- 40 verter and a switch circuit which connects the cell inputs either in series or in parallel.

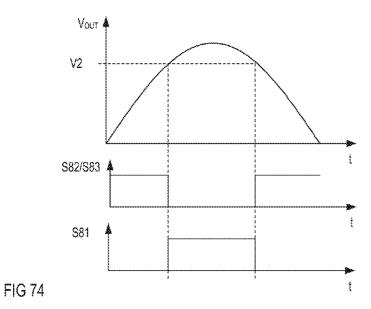

> FIG. 74 shows timing diagrams which illustrate one way of operation of the converter cells shown in FIG. 73.

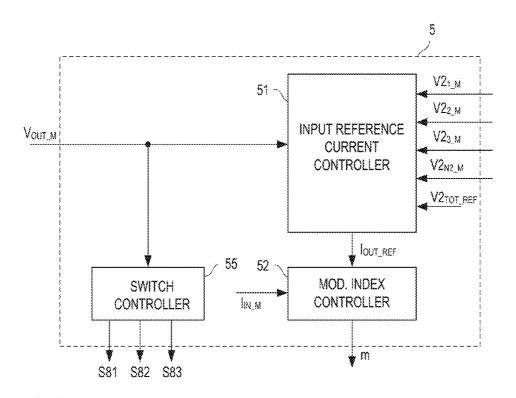

> FIG. 75 shows one embodiment of a main controller in a multi-cell converter with two rearrangeable converter cells as shown in FIG. 73.

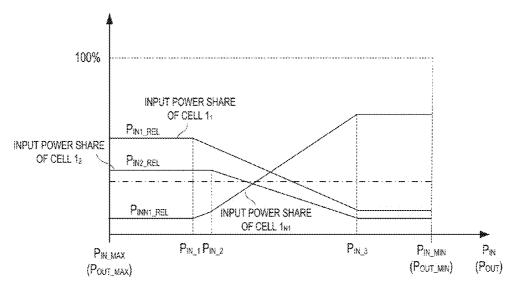

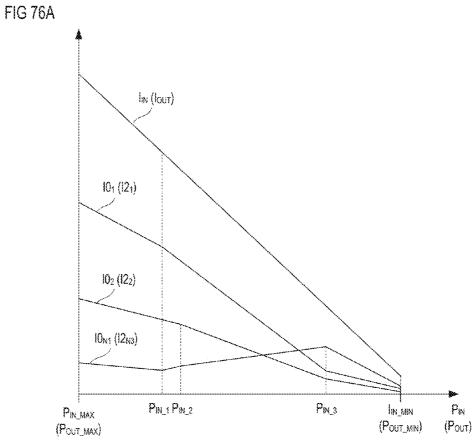

> FIGS. 76A-76B illustrate an unequal distribution of power shares and current shares, respectively, in a multi-cell converter.

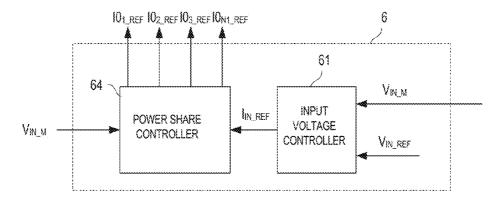

FIG. 77 shows one embodiment of a main controller configured to control a distribution of power and current shares, respectively, in a multi-cell converter with an IP

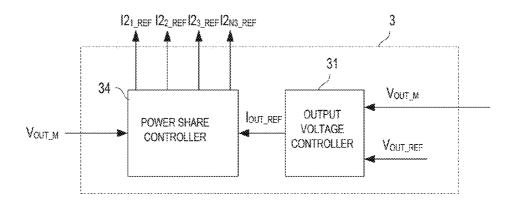

FIG. 78 shows one embodiment of a main controller IS multi-cell converter having an intermittent operation 55 configured to control a distribution of power and current shares, respectively, in a multi-cell converter with an OP

> FIGS. 79A-79B show timing diagrams which illustrate operation of a multi-cell converter with an IS or OS topology such that DC link voltages have different voltage levels.

FIG. 80 shows one embodiment of a main controller configured to operate a multi-cell converter as shown in FIGS. 79A-79B.

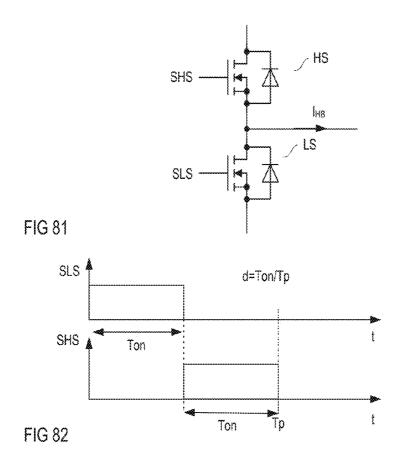

FIG. 81 shows one embodiment of a half-bridge in a 65 converter cell of multi-cell converter.

FIG. 82 shows timing diagrams which illustrate a PWM operation of the half-bridge shown in FIG. 81.

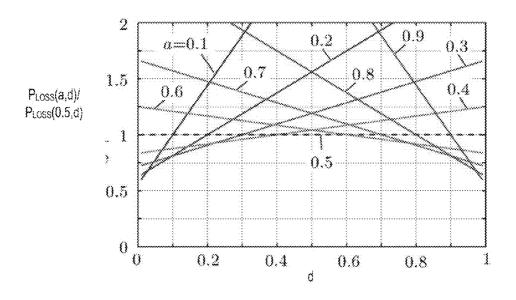

FIG. **83** illustrates losses that occur in the half-bridge shown in FIG. **81** at different duty cycles of a PWM operation for several different designs of the half-bridge.

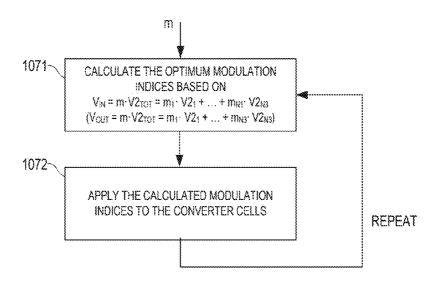

FIG. **84** shows one embodiment of a method for optimizing operation of a multi-cell power converter by differently operating the individual converter cells.

FIG. **85** shows one embodiment of a main controller in an IS multi-cell converter with an optimization functionality as illustrated in FIG. **84**.

FIG. **86** shows one embodiment of a main controller in an <sup>10</sup> OS multi-cell converter with an optimization functionality as illustrated in FIG. **84**.

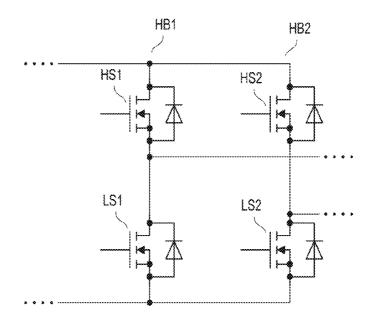

FIG. 87 shows one embodiment of a bridge circuit in a multi-cell converter.

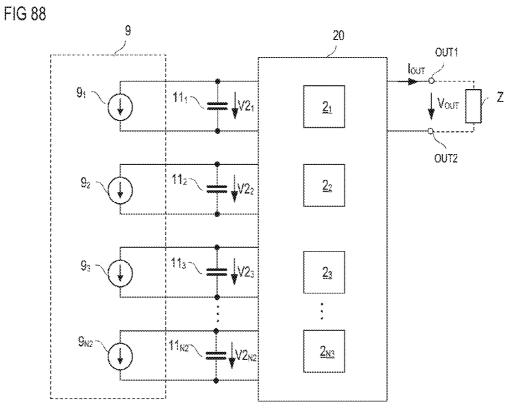

FIG. **88** shows one embodiment of a power converter 15 circuit which includes a multi-cell converter and a single cell converter

FIG. **89** shows one embodiment of a power converter circuit which includes a multi-cell converter which receives a plurality of DC voltages from different power sources.

FIG. 90 shows one embodiment of a power converter circuit which includes a multi-cell converter and a plurality of single cell converters coupled to the multi-cell converter.

## DETAILED DESCRIPTION

In the following detailed description, reference is made to the accompanying drawings. The drawings form a part of the description and by way of illustration show specific embodiments in which the invention may be practiced. It is to be 30 understood that the features of the various embodiments described herein may be combined with each other, unless specifically noted otherwise.

In the following, several embodiments of power conversion methods and power converter circuits are explained 35 with reference to drawings. These power converter circuits include at least one power converter with several power converter cells. A power converter including several power converter cells will be referred to as multi-cell power converter or multi cell converter in the following. A power 40 conversion method which uses at least one multi-cell converter will be referred to as multi-cell power conversion method.

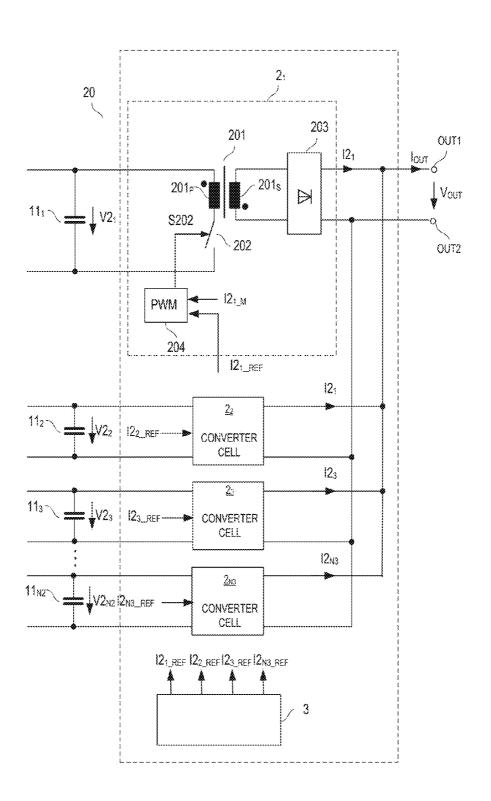

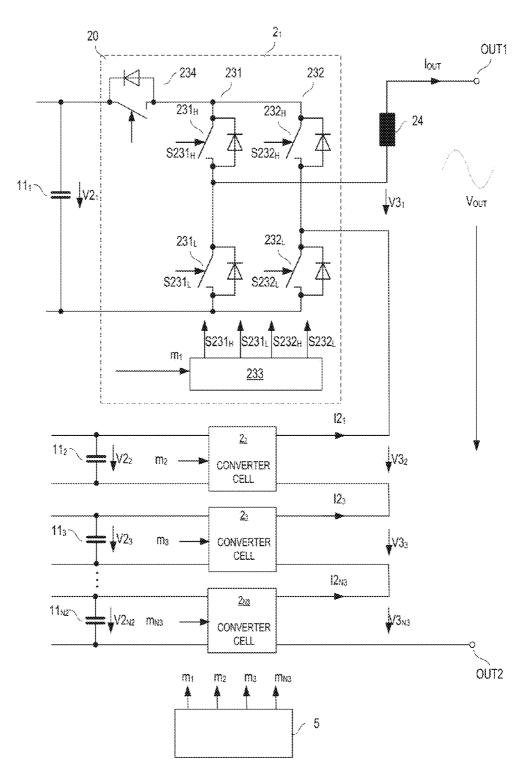

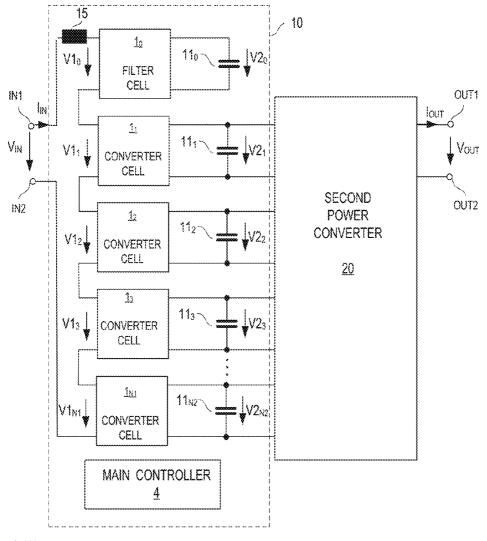

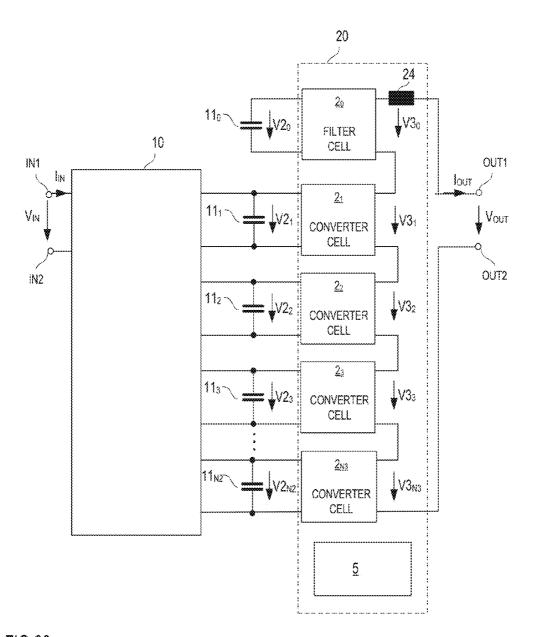

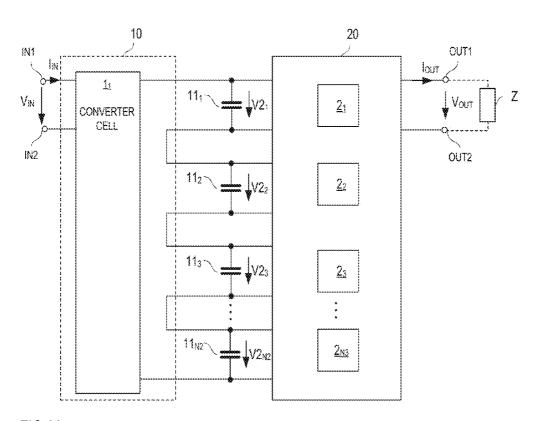

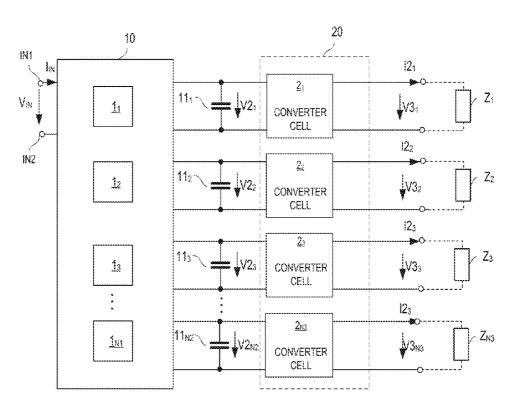

FIG. 1 shows one embodiment of a power converter circuit which is configured to convert an input power  $P_{IN}$  45 received at an input IN1, IN2 into an output power  $P_{OUT}$  provided at an output OUT1, OUT2. The input power  $P_{IN}$  is defined as the product of an input current  $I_{IN}$  received at the input IN1, IN2, and an input voltage  $V_{IN}$  between a first input node IN1 and a second input node IN2 of the input, so 50 that  $P_{IN} = V_{IN} I_{IN}$ . The output power  $P_{OUT}$  is defined as the product of an output current  $I_{OUT}$  provided at the output OUT1, OUT2, and an output voltage  $V_{OUT}$  between a first output node OUT1 and a second output node OUT2 of the output, so that  $P_{OUT} = V_{OUT} I_{OUT}$ . A load Z (illustrated in 55 dashed lines in FIG. 1) may receive the output power  $P_{OUT}$  provided by the second power converter 20.

The power converter circuit includes a first converter 10 configured to receive the input power at the input IN1, IN2, and a second power converter 20 configured to provide the 60 output power at the output OUT1, OUT2. At least one of the first power converter 10 and the second power converter includes a plurality of power converter cells, which will briefly be referred to as converter cells in the following. In the embodiment shown in FIG. 1, the first power converter 10 includes a plurality of converter cells  $1_1$ - $1_{N1}$ , and the second power converter 20 includes a plurality of converter

6

cells  $\mathbf{2}_1$ - $\mathbf{2}_{N3}$ . These converter cells are only schematically illustrated in FIG. 1. The first power converter  $\mathbf{10}$  and the second power converter  $\mathbf{20}$  are linked by a plurality of capacitors  $\mathbf{11}_1$ - $\mathbf{11}_{N2}$ . These capacitors  $\mathbf{11}_1$ - $\mathbf{11}_{N2}$  will also be referred to as DC link capacitors in the following. Capacitances of the individual DC link capacitors are dependent on several aspects, such as a waveform of the input voltage and/or the output voltage, or a power rating of the power converter circuit, to name only a few. According to one embodiment, the capacitances of the DC link capacitors are selected from a range of between several microfarads ( $\mu$ F), such as 2 uF, and several millifarads (mF), such as 9 mF.

Referring to FIG. 1, the first power converter 10 may include a first number N1 of converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$ , a second number N2 of capacitors  $\mathbf{11}_1$ - $\mathbf{11}_{N2}$  may link the first power converter 10 and the second power converter 20, and the second power converter 20 may include a third number N3 of converter cells  $\mathbf{2}_1$ - $\mathbf{2}_{N2}$ . According to one embodiment, the first number N1, the second number N2, and the third number N3 are equal, so that N1=N2=N3=N.

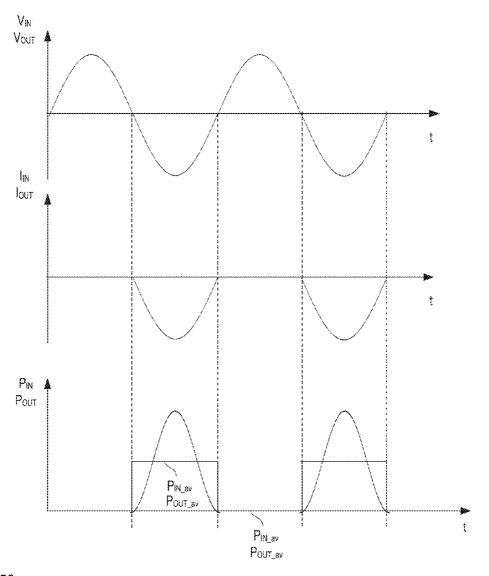

Dependent on how the first power converter 10 and the second power converter 20 are implemented, different types of power conversion methods may be performed by the power converter circuit. Some of those different types of power conversion methods are explained with reference to FIGS. 2A-3C below. Each of these FIGS. 2A-3C schematically illustrates timing diagrams of the input voltage  $V_{I\!N}$  and the output voltage  $V_{OUT}$ .

Referring to FIG. 2A, the input voltage  $V_{IN}$  may be a rectified sine voltage and the output voltage  $\mathbf{V}_{OUT}$  may be a direct voltage with a voltage level lower than a peak voltage of the input voltage  $V_{IN}$ . Referring to FIG. 2B, the input voltage  $V_{IN}$  may be a sine voltage and the output voltage  $V_{\it OUT}$  may be a direct voltage with a voltage level lower than the amplitude of the input voltage  $V_{IN}$ . A rectified sine voltage as shown in FIG. 2A may be obtained by rectifying a sine voltage as shown in FIG. 2B. According to one embodiment, the sine voltage is a grid voltage with  $110V_{RMS}$ or  $220V_{RMS}$  and a frequency of 50 Hz or 60 Hz. The type of power conversion shown in FIG. 2B may be used in a variety of different applications in which a load Z is to be supplied with DC power from a power grid. Examples of those applications include telecommunication switches, computers, or the like. Referring to FIG. 2C each of the input voltage  $V_{IV}$  and the output voltage  $V_{OUT}$  may be a direct voltage, wherein a voltage level of the input voltage is  $V_{IN}$ is higher than a voltage level of the output voltage  $V_{\it OUT}$

Referring to FIG. 3A, the output voltage  $V_{OUT}$  may be a rectified sine voltage and the input voltage  $V_{IN}$  may be a direct voltage with a voltage level lower than a peak voltage of the output voltage  $V_{\it OUT}$ . Referring to FIG. 3B, the output voltage  $V_{\ensuremath{\textit{OUT}}}$  may be a sine voltage and the input voltage  $V_{IN}$  may be a direct voltage with a voltage level lower than the amplitude of the output voltage V<sub>OUT</sub>. According to one embodiment, the sine voltage shown in FIG. 3B is a grid voltage with  $110V_{RMS}$  or  $220V_{RMS}$  and a frequency of 50 Hz or 60 Hz. The type of power conversion shown in FIG. 3B may be used in applications in which power is to be supplied to a power grid from a DC power source, such as, for example a photovoltaic panel, a battery, or the like. Referring to FIG. 3C each of the input voltage  $V_{I\!N}$  and the output voltage V<sub>OUT</sub> may be a direct voltage, wherein a voltage level of the input voltage  $V_{IN}$  is lower than a voltage level of the output voltage  $\mathbf{V}_{OUT}$

In the embodiments shown in FIGS. 2A-2C, the voltage level of the output voltage  $V_{OUT}$  is lower than the voltage level or the effective voltage level of the input voltage  $V_{IN}$ .

In the following, a power converter circuit configured to perform one of these types of power conversion will be referred to as a power converter circuit having a step-down characteristic. In the embodiments shown in FIGS. 3A-3C, the voltage level of the input voltage  $V_{IV}$  is lower than the 5 voltage level or the effective voltage level of the output voltage. In the following, a power converter circuit configured to perform one of these types of power conversion will be referred to as a power converter circuit having a step-up characteristic.

Four different power converter circuits of the type shown in FIG. 1 are explained with reference to FIGS. 4-7 below. In each of these embodiments, each of the first power converter 10 and the second 20 power converter 20 includes embodiments, N1=N2=N3=N so that each of the plurality of converter cells in the first power converter 10 is linked to one of the plurality of converter cells in the second power converter 20 by one DC link capacitor. However, this is only example. Other examples where only one of the first and 20 second power converters 10, 20 includes a plurality of converter cells, or where at least two of N1, N2, and N3 are different are explained further below. The power converter circuits shown in FIGS. 4-7 are different in how the converter cells of the first power converter 10 are connected to 25 the input IN1, IN2, and in how the converter cells of the second power converter 20 are connected to the output OUT1, OUT2,

FIG. 4 shows one embodiment of a power converter circuit with an ISOP (Input Serial, Output Parallel) topology. 30 In this power converter circuit the converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N_1}$  of the first power converter 10 are connected in series at the input IN1, IN2, and the converter cells  $2_1$ - $2_{N3}$  of the second power converter 20 are connected in parallel at the output OUT1, OUT2. This is explained below.

The converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  of the first power converter  $\mathbf{10}$ will also be referred to as first converter cells in the following. Each of these first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  includes a cell input and a cell output. The cell output of each converter cell  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  is connected to one of the plurality of 40 converter circuit. The other second converter cells (the DC link capacitors  $\mathbf{11}_1$ - $\mathbf{11}_{N1}$ , namely to the DC link capacitor associated with the respective first converter cell  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$ . The cell inputs of the first converter cells  $\mathbf{1}_1 \cdot \mathbf{1}_{N1}$  are connected in series at the input IN1, IN2 of the power converter circuit. That is, a first cell input node of one of the plurality 45 of first converter cells (the converter cell  $\mathbf{1}_1$  in the embodiment shown in FIG. 4) is connected to the first input node IN1. A second cell input node of another one of the plurality of first converter cells (the first converter cell  $\mathbf{1}_{N1}$  in the embodiment shown in FIG. 1) is connected to the second 50 input node IN2 of the power converter circuit. The other first converter cells (the converter cells  $1_2$ ,  $1_3$  shown in FIG. 1) each have the first cell input node connected to the second cell input node of another first converter cell, and have their of another first converter cell. In other words, the cell inputs of the individual first converter cells  $\mathbf{1}_1 - \mathbf{1}_{N_1}$  form a cascade between the input nodes IN1, IN2 of the power converter

The converter cells  $\mathbf{2}_{1}$ - $\mathbf{2}_{N3}$  of the second power converter 60 20 will also be referred to as second converter cells in the following. Each of these second converter cells  $2_1-2_{N3}$ includes a cell input and a cell output. The cell input of each converter cell  $2_1$ - $2_{N3}$  is connected to one of the plurality of DC link capacitors. The cell outputs of the second converter cells  $2_1$ - $2_{N3}$  are connected in parallel at the output OUT1, OUT2 of the power converter circuit. That is, each of the

8

second converter  $\mathbf{2}_{1}$ - $\mathbf{2}_{N3}$  cells has a first cell output node connected to a first output node OUT1 of the power converter circuit, and each of the second converter cells  $2_1-2_{N3}$ has a second cell output node connected to a second output node OUT2 of the power converter circuit.

In the power converter circuit with the ISOP topology shown in FIG. 4, each of the series connected first converter cells  $\mathbf{1}_1 \cdot \mathbf{1}_{N_1}$  receives a share or portion of the input voltage  $V_{IN}$  as a cell input voltage  $V\mathbf{1}_1$ - $V\mathbf{1}_{N1}$ . That is, a sum of the 10 cell input voltages  $V1_1$ - $V1_{N1}$  corresponds to the input voltage  $V_{IN}$ ,

$$V_{IN} = \sum_{i=1}^{N_I} V_{I_i} \tag{1}$$

A cell input current of each first converter cell  $\mathbf{1}_1$ - $\mathbf{1}_{N_1}$ a plurality of converter cells. Further, in each of these 15 equals the input current I<sub>IN</sub>. Further, each of the parallel connected second converter cells  $\mathbf{2}_{1}\text{-}\mathbf{2}_{N3}$  provides a cell output current I2<sub>1</sub>-I2<sub>N3</sub> which is a share or portion of the output current  $I_{OUT}$ . That is, a sum of the cell output currents  $I2_1-I2_{N3}$  corresponds to the output current  $I_{OUT}$ ,

$$I_{OUT} = \sum_{i=1}^{N3} I \sum_{i}$$

(2).

A cell output voltage of each of the second converter cells corresponds to the output voltage  $V_{OUT}$  of the power converter circuit.

FIG. 5 shows one embodiment of a power converter circuit with an ISOS (Input Serial, Output Serial) topology. Like in the power converter circuit shown in FIG. 4, the first converter cells  $\mathbf{1}_1 \cdot \mathbf{1}_{N_1}$  are connected in series at the input IN1, IN2. The power converter circuit shown in FIG. 5 is different from the power converter circuit shown in FIG. 4 in that the second converter cells  $2_1-2_{N3}$  are connected in series at the output OUT1, OUT2. This is explained below.

Referring to FIG. 5, a first cell output node of one of the plurality of second converter cells (the converter cell  $2_1$  in the embodiment shown in FIG. 5) is connected to the first output node OUT1. A second cell output node of another one of the plurality of second converter cells (the second converter cell  $2_{N3}$  in the embodiment shown in FIG. 5) is connected to the second output node OUT2 of the power converter cells 22, 23 shown in FIG. 5) each have the first cell output node connected to the second cell output node of another second converter cell, and have their second cell output node connected to the first cell output node of another second converter cell. In other words, the cell outputs of the individual second converter cells  $\mathbf{2}_{\scriptscriptstyle{1}}\text{-}\mathbf{2}_{\scriptscriptstyle{N3}}$  form a cascade between the output nodes OUT1, OUT2 of the power converter circuit. In this embodiment, a cell output voltage  $V3_1$ - $V3_{N3}$  of each of the plurality of second converter cells  $\mathbf{2}_{1}$ - $\mathbf{2}_{N3}$  is a share of the output voltage  $V_{OUT}$  of the power converter circuit. That is,

$$V_{OUT} = \sum_{i=1}^{N3} V_{3_i}$$

(3).

A cell output current of each of the plurality of second second cell input node connected to the first cell input node 55 converter cells  $2_1$ - $2_{N3}$  equals the output current of the power converter circuit.

> In the power converter circuit shown in FIG. 5, like in the power converter circuit shown in FIG. 4, the cell output of each of the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N_1}$  is connected to one of the plurality of DC link capacitors  $11_1-11_{N2}$ , and the cell input of each of the second converter cells 2<sub>1</sub>-2<sub>N3</sub> is connected to one of the DC link capacitors  $11_1-11_{N2}$ , wherein each of the DC link capacitors  $11_1-11_{N2}$  has only one first converter cell and only one second converter cell connected thereto.

FIG. 6 shows one embodiment of a power converter circuit with an IPOS (Input Parallel, Output Serial) topology.

Like in the power converter circuit shown in FIG. 5, the second converter cells  $\mathbf{2}_1$ - $\mathbf{2}_{N3}$  are connected in series at the output OUT1, OUT2. The power converter circuit shown in FIG. 6 is different from the power converter circuit shown in FIG. 5 in that the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  are connected in parallel at the input IN1, IN2. That is, each of the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N3}$  has its first cell input node connected to the first input node IN1 of the power converter circuit, and has its second cell input node connected to the second input node IN2 of the power converter circuit. Thus, each of the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N3}$  receives the input voltage  $V_{IN}$  as a cell input voltage, and a cell input current  $\mathbf{I0}_1$ - $\mathbf{I0}_{N1}$  of each of the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  is a share or portion of the input current  $I_{OUT}$ , so that

$$I_{IN} = \sum_{i=1}^{N} I_{i} I_{0} I_{i}$$

(4).

FIG. 7 shows one embodiment of a power converter circuit with an IPOP (Input Parallel, Output Parallel) topology. In this power converter circuit, the first converter cells  $\mathbf{1}_1 \cdot \mathbf{1}_{N1}$  are connected in parallel at the input IN1, IN2, and 20 the second converter cells  $\mathbf{2}_1 \cdot \mathbf{2}_{N3}$  are connected in parallel at the output. Concerning the parallel connection of the first converter cells  $\mathbf{1}_1 \cdot \mathbf{1}_{N1}$  reference is made to FIG. 6 and the corresponding description, and concerning the parallel connection of the second converter cells  $\mathbf{2}_1 \cdot \mathbf{2}_{N3}$  reference is 25 made to FIG. 4 and the corresponding description.

Each of the first converter cells  $\mathbf{1}_1 - \mathbf{1}_{N1}$  and the second converter cells  $2_1$ - $2_{N3}$  is implemented with a power converter topology and is configured to receive a cell input power at the cell input and provide a cell output power at the 30 cell output. Each of the first converter cells  $\mathbf{1}_1 \cdot \mathbf{1}_{N_1}$  receives its cell input power from the input IN1, IN2. The cell output power of each of the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N_1}$  is the power the respective first converter cells provides to the DC link capacitor connected to the cell output and to the second 35 converter cell connected to the cell output, respectively. The cell input power of each of the plurality of second converter cells  $2_1$ - $2_{N3}$  is the power, the respective second converter cell receives from the DC link capacitor it is connected thereto, and from the first converter it is connected thereto, 40 respectively. Each of the second converter cells provides its cell output power to the output OUT1, OUT1. The DC link capacitors  $11_1$ - $11_{N2}$  are capable of storing energy so that the power level of the cell output power of one of the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  and the power level of the cell input 45 power of the associated second converter cell can be different. In the following, the word "associated" is used to describe the relationship between one first converter cells, the DC link capacitor connected to this first converter cell, and the second converter cells connected to this first con- 50 verter cell and this DC link capacitor.

The type of converter topology implemented in the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  and the second converter cells  $\mathbf{2}_1$ - $\mathbf{2}_{N3}$ is, for example, dependent on the type of power conversion the power converter circuit performs. In general, the con- 55 verter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$ ,  $\mathbf{2}_1$ - $\mathbf{2}_{N3}$  can be implemented with an isolating power converter topology, or with a non-isolating power converter topology. In the first case, the respective converter cell includes a transformer which galvanically isolates the cell input and the cell output. In the second case, the cell input and the cell output of the converter cell are not galvanically isolated. This is explained with reference to FIGS. 8-10 below. Each of these Figures shows a first converter cell 1, the DC link capacitor 11, of the first converter cell 11, and a second converter cell 2, connected to the first converter cell  $\mathbf{1}_i$ . The first converter cell  $\mathbf{1}_i$  and the second converter cell 2, represent any pair of a first converter

10

cell  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  and a second converter cell  $\mathbf{2}_1$ - $\mathbf{2}_{N3}$  connected to the first converter cell  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  in any of the power converter circuits explained herein before.

In the embodiment shown in FIG. **8**, the first converter cell **1**<sub>i</sub> is implemented with an isolating converter topology. This is schematically illustrated by the transformer symbol in the circuit block representing the first converter cell **1**<sub>i</sub>. The second converter cell **2**<sub>i</sub> is implemented with a non-isolating converter topology. In a power converter circuit in which the first converter cells **1**<sub>1</sub>-**1**<sub>N1</sub> are implemented with an isolating converter topology, and the second converter cells **2**<sub>1</sub>-**2**<sub>N3</sub> are implemented with a non-isolating converter topology, as shown in FIG. **8**, the first converter cells **1**<sub>1</sub>-**1**<sub>N1</sub> provide for a galvanic isolation between the input IN**1**, IN**2** and the output OUT**1**, OUT**2** of the power converter circuit.

In the embodiment shown in FIG. 9, the first converter cell  $\mathbf{1}_i$  is implemented with a non-isolating converter topology. This is schematically illustrated by the transformer symbol in the circuit block representing the second converter cell  $\mathbf{2}_i$ . The first converter cell  $\mathbf{1}_i$  is implemented with a non-isolating converter topology. In a power converter circuit in which the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N_1}$  are implemented with a non-isolating converter topology, and the second converter cells  $\mathbf{2}_1$ - $\mathbf{2}_{N_3}$  are implemented with an isolating converter topology, as shown in FIG. 9, the second converter cells  $\mathbf{2}_1$ - $\mathbf{2}_{N_3}$  provide for a galvanic isolation between the input IN1, IN2 and the output OUT1, OUT2.

In the embodiment shown in FIG. 10, none of the first power converter circuit  $\mathbf{1}_i$  and the second power converter circuit  $\mathbf{2}_i$  is implemented with an isolating converter topology. According to another embodiment (not shown), both of the first power converter circuit  $\mathbf{1}_i$  and the second power converter circuit  $\mathbf{2}_i$  is implemented with an isolating converter topology.

In the following, different embodiments of the first power converter 10 and ways of operation of these embodiments are explained. In the following, a first multi-cell power converter 10 with series connected converter cells  $1_1$ - $1_{N1}$ will be referred to as IS (Input Serial) converter, or power converter with an IS topology. Equivalently, a first multi-cell power converter 10 with parallel connected converter cells  $\mathbf{1}_{1}$ - $\mathbf{1}_{N1}$  will be referred to as IP (Input Parallel) converter, or power converter with an IP topology. A second multi-cell power converter with series connected converter cells  $2_1$ - $2_{N3}$  will be referred to as OS (Output Serial) converter, or power converter with an OS topology. Equivalently, a second multi-cell power converter 20 with parallel connected converter cells  $\mathbf{1}_{1}\text{-}\mathbf{1}_{N1}$  will be referred to as OP (Output Parallel) converter, or power converter with an OP topology. In context with one of the first and second power converters 10, 20, "series connected converter cells" are converter cells which either have their cell inputs connected in series (in the first converter 10), or have their cell outputs connected in series (in the second converter 20), and "parallel connected converter cells" are converter cells which either have their cell inputs connected in parallel (in the first converter 10), or have their cell outputs connected in parallel (in the second converter 20).

At first, an embodiment of a first power converter 10 with an IS topology is explained which is configured to receive as an input voltage V<sub>IN</sub> a rectified sine voltage, as shown in FIG. 2A, and to provide a plurality of DC link voltages V2<sub>1</sub>-V2<sub>N2</sub> at the individual DC link capacitors 11<sub>1</sub>-11<sub>N2</sub> (wherein N1=N2, in this embodiment). Referring to FIG. 11, such input voltage V<sub>IN</sub> with a rectified sinusoidal waveform may be obtained from a sinusoidal grid voltage V<sub>GRID</sub> by a bridge rectifier 100 with four rectifier elements 101-104.

These rectifier elements may be diodes, as shown in FIG. 11. However other rectifier elements such as switches operated as synchronous rectifier elements may be used as well. These rectifier elements 101-104 are connected in a bridge-configuration and receive the grid voltage  $V_{GRID}$  as an input 5 voltage and provide the rectified sine voltage as an output voltage. This output voltage of the rectifier circuit 100 is the input voltage  $V_{IN}$  of the power converter circuit, from which only the input IN1, IN2 is shown in FIG. 11.

The grid voltage  $V_{\textit{GRID}}$  may be a  $110\,V_{\textit{RMS}}$  or a  $230\,V_{\textit{RMS}}$  sine voltage. In the first case, a peak voltage of the rectified input voltage  $V_{\textit{IN}}$  is about 160V and in the second case, the peak voltage is about 320V. According to another embodiment, the grid voltage is a medium voltage with a peak voltage of up to several kilovolts (kV).

According to one embodiment, The first power converter 10 with the plurality of first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  is configured to generate the DC link voltages  $\mathbf{V2}_1$ - $\mathbf{V2}_{N2}$  from the input voltage  $\mathbf{V}_{IN}$  such that a voltage level of an overall DC link voltage (total DC link voltage)  $\mathbf{V2}_{TOT}$  is higher than the 20 voltage level of the peak voltage of the input voltage  $\mathbf{V}_{IN}$ . The total DC link voltage  $\mathbf{V2}_{TOT}$  equals the sum of the individual DC link voltages  $\mathbf{V2}_{1}$ - $\mathbf{V2}_{N}$ , that is,

$$V2_{TOT} = \sum_{i=1}^{N2} V2_i \tag{5}$$

According to one embodiment, the total DC link voltage  $V2_{TOT}$  is between 1.1 times and 1.3 times the peak voltage. For example, in case of an input voltage  $V_{IN}$  obtained from a  $220V_{RMS}$  sine voltage, the total DC link voltage  $V2_{TOT}$  is about 400V.

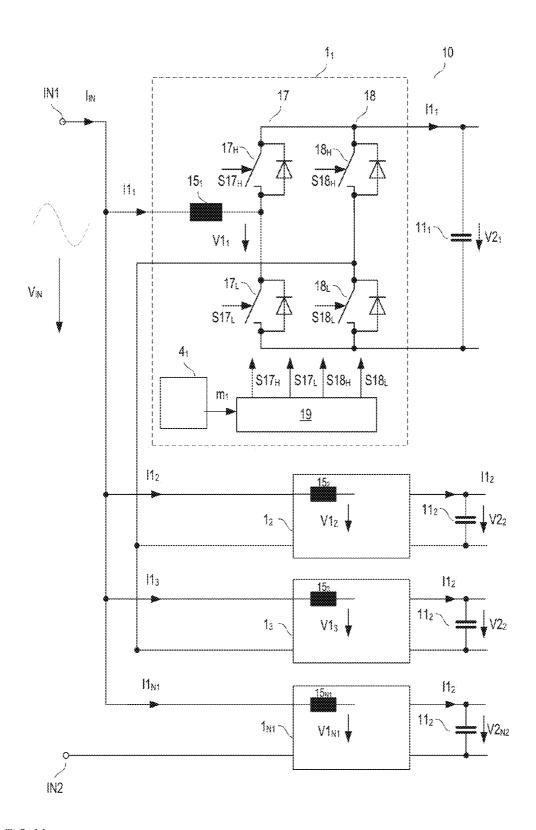

FIG. 12 shows one embodiment of a first power converter 10 having an IS topology and configured to generate the total DC link voltage  $V2_{TOT}$  with a higher voltage level than the peak voltage level of the input voltage  $V_{IN}$ . In this embodiment, the individual first converter stages  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  are each 35 implemented with a boost converter topology, which is one type of a non-isolating converter topology. In FIG. 12, only one of the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  namely the first converter cells  $\mathbf{1}_2$ - $\mathbf{1}_{N1}$  are implemented with the same topology. Thus, 40 the explanation provided in context with the first converter cells  $\mathbf{1}_2$ - $\mathbf{1}_{N1}$  are involved in context with the first converter cells  $\mathbf{1}_2$ - $\mathbf{1}_{N1}$ .

Referring to FIG. 12, the first converter cells 1 includes a half-bridge 12 with a low-side switch  $12_L$  and a high-side switch  $12_H$ . The high-side switch  $12_H$  is optional and may be replaced with a rectifier element such as, for example, a diode. Referring to FIG. 12, the high-side switch may be implemented with an electronic switch and a parallel rectifier element. The electronic switch is operated as a synchronous rectifier which switches on each time the parallel rectifier element is conducting. Thus, the high-side switch  $12_H$  operates like an active rectifier element. However, losses occurring in the high-side switch  $12_H$  when the switch is on are lower than losses that occur in a comparable 55 passive rectifier element, such as a diode. The low side switch 12, may also be implemented with an electronic switch and a parallel rectifier element. However, the rectifier element is optional in this embodiment. The high-side switch  $12_H$  and the low-side switch  $12_L$  can be implemented 60 as electronic switches. Examples of those switches include, but are not restricted to, MOSFETs (Metal Oxide Semiconductor Field-Effect Transistors), IGBTs (Insulated Gate Bipolar Transistors), JFETs (Junction Field-Effect Transistors), BJTs (Bipolar Junction Transistor), HEMTs (High Electron Mobility Transistor), GaN-HEMTs, or the like. Some types of these electronic switches, such as MOSFETs,

12

include an integrated diode (body diode) which may be used as the rectifier element shown in FIG. 12.

Referring to FIG. 12, the low-side switch  $12_L$  is connected between cell input nodes of the first converter cell  $1_1$ . Thus the low-side switch  $12_L$  of the first converter cell  $1_1$  and corresponding low-side switches (not shown) in the other first converter cells  $1_2$ - $1_{N1}$  form a series circuit which is connected between the input nodes of the input IN1, IN2. The high-side switch  $12_H$  and the DC link capacitor  $11_1$  of the first converter cell  $1_1$  form a series circuit, wherein this series circuit is connected in parallel with the low-side switch  $12_L$ .

The first power converter circuit 10 further includes at least one inductor 15 such as a choke. In the embodiment shown in FIG. 12, the individual first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  share the inductor 15. That is, there is one inductor which is connected in series with low-side switch  $\mathbf{12}_L$  in the first converter cell  $\mathbf{1}_1$  and the correspondent low-side switches in the other converter cells  $\mathbf{1}_2$ - $\mathbf{1}_{N1}$ . According to another embodiment (not shown) each converter cell  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  includes one inductor connected between one cell input node and the circuit node common to the high-side switch and the low-side switch in the respective converter cell.

Referring to FIG. 12, the first converter cell  $\mathbf{1}_1$  further includes a controller  $\mathbf{14}_1$  which is configured to control operation of the low-side switch  $\mathbf{12}_L$  and the high-side switch. In case the high-side switch  $\mathbf{12}_H$  is replaced with a passive rectifier element, the controller  $\mathbf{14}$  only controls operation of the low-side switch  $\mathbf{12}_L$ .

The low-side switch  $12_L$  receives a drive signal  $S12_L$  from the controller 14, wherein the drive signal  $S12_L$  switches the low-side switch  $12_L$  either on or off. Equivalently, the high-side switch  $12_H$  receives a drive signal  $S12_H$  from the controller 14, wherein the drive signal  $S12_H$  switches the high-side switch  $12_H$  either on or off. According to one embodiment, the controller 14 drives the low-side switch  $12_L$  and the high-side switch  $12_H$  such that they are not switched on at the same time, so as to prevent the DC link capacitor  $11_1$  from being discharged via these switches  $12_L$ ,  $12_H$ .

According to one embodiment, the controller 14 in the first converter cell  $\mathbf{1}_1$  and corresponding controllers in the other converter cells  $\mathbf{1}_2$ - $\mathbf{1}_{N1}$  are controlled by a controller 4 of the first power converter 10. This controller 4 will also be referred to as main controller of the first power converter 10 in the following. Ways of operation of this main controller 4 and possible implementations are explained below.

According to one embodiment, the main controller 4, via the controller 14 in the first converter cell  $\mathbf{1}_1$  and corresponding controllers in the other converter cells  $\mathbf{1}_2$ - $\mathbf{1}_{N_1}$  is configured to control (regulate) the total DC link voltage  $V2_{TOT}$ . According to one embodiment, the main controller 4 is further configured to control a current waveform of the input current I<sub>IV</sub> such that the waveform of the input current  $I_{IN}$  substantially corresponds to the waveform of the input voltage V<sub>IN</sub>. A phase difference between the waveform of the input voltage  $V_{IN}$  and the resulting waveform of the input current  $I_{DV}$  may be zero or may be different from zero. Controlling the input current  $I_{IN}$  to have substantially the same waveform as the input voltage  $V_{\mathit{IN}}$  may help to control the power factor of the input power  $P_{IN}$  received at the input IN1, IN2. A first power converter 10 configured to control the waveform of the input current  $I_{IN}$  to substantially be equal to the waveform of the input voltage  $V_{IN}$  will be referred to as a first power converter 10 with a PFC (Power Factor Correction) capability or, briefly, as a first PFC power converter 10.

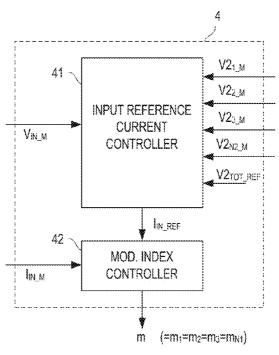

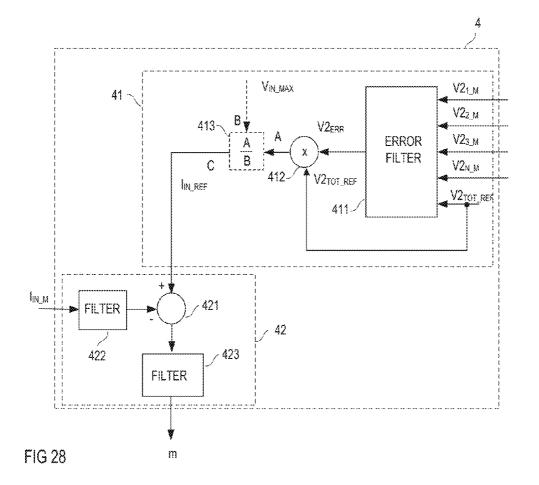

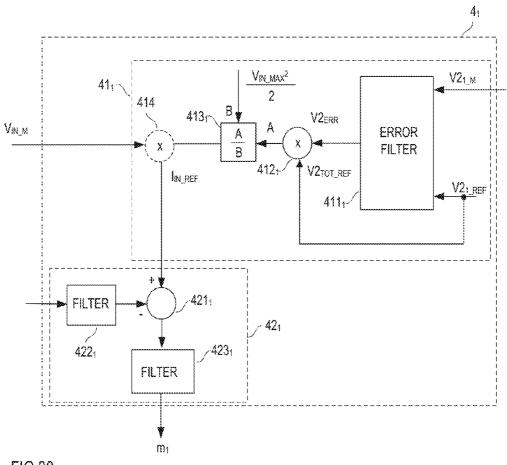

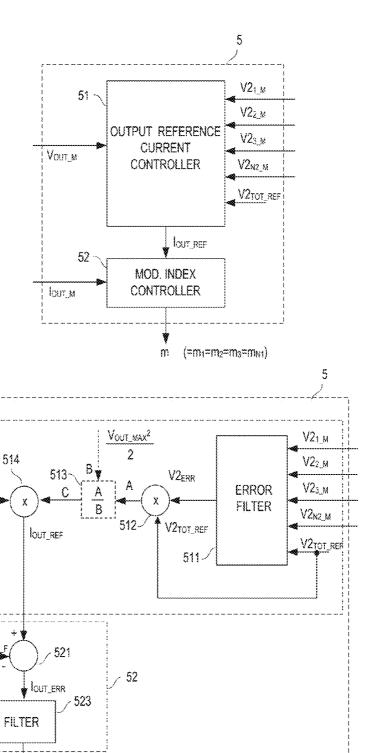

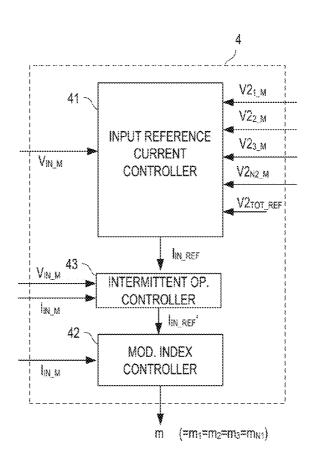

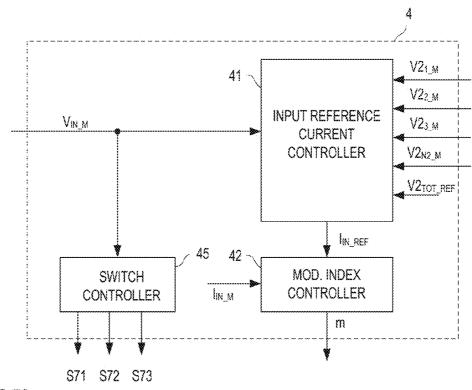

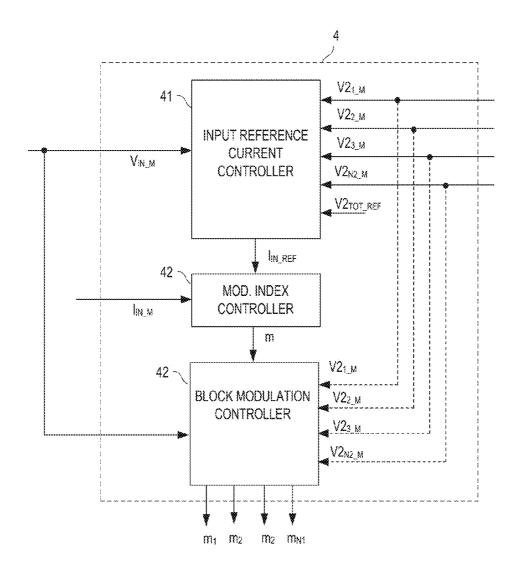

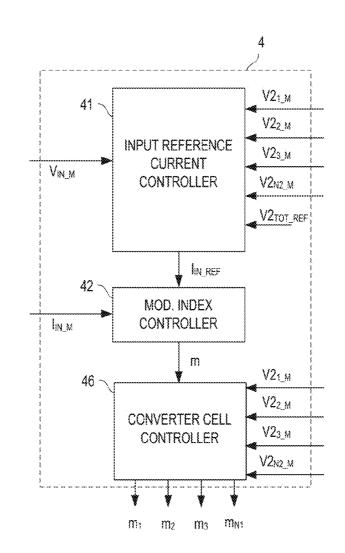

One embodiment of a main controller 4 which is configured to control the total DC link voltage  $\mathbf{V2}_{TOT},$  and the current waveform of the input current  $I_{I\!N}$  is shown in FIG. 13. Referring to FIG. 13, the main controller 4 includes an input reference current controller 41 and a converter cell controller 42, which will also be referred to as modulation index controller. The input reference current controller 41 is configured to generate an input current reference signal  $I_{IN\ REF}$ . The input current reference signal  $I_{IN\ REF}$  represents the desired current level (set point) of the input current 10  $I_{IN}$ , which is required in order to control the total DC link voltage  $V2_{TOT}$  such that a voltage level of the total DC link voltage  $V2_{TOT}$  equals a predefined voltage level. A level of this input current reference signal  $I_{IN\_REF}$  may vary over time as the input voltage  $V_{I\!N}$  varies. The input reference 15 current controller 41 receives an input voltage signal  $V_{IN\_M}$ which represents the instantaneous voltage level of the input voltage  $V_{IN}$ . This input voltage signal  $V_{IN\_M}$  may be obtained by measuring the input voltage  $V_{IN}$ , or by other means. The input reference current controller 41 further 20 receives DC link voltage signals  $V2_{1\_M}$ - $V2_{N2\_M}$ . Each of these DC link voltage signals  $V2_{1\_M}V2_{N2\_M}$  represents one of the DC link voltages  $V2_1-V2_{N2}$ . These DC link voltage signals  $V2_{1\_M}$ - $V2_{N2\_M}$  may be obtained by measuring the individual  $\bar{DC}$  link voltages  $V2_1$ - $V2_{N2}$ . The input reference current controller 41 further receives a total DC link voltage reference signal  $V2_{TOT\_REF}$ . This reference signal  $V2_{TOT\text{-}REF}$  represents the desired (predefined) voltage level of the total DC link voltage  $V2_{TOT}$ . The input reference current controller 41 calculates the input current reference signal  $I_{IN\ REF}$  based on these input signals. As the input reference current controller 41 generates the current level of the input current reference signal  $I_{IN\ REF}$  such that the total DC link voltage assumes the desired level defined by the DC link voltage reference signal  $V2_{TOT}$  REF, the input reference 35 current controller 41, in the present embodiment as well as in other embodiments explained below, may also be referred to as DC link voltage controller.

The modulation index controller 42 receives the input current reference signal  $I_{IN\_REF}$  and an input current signal 40  $I_{IN\ M}$ . The input current signal  $I_{IN\ M}$  represents the instantaneous current level of the input current I<sub>IN</sub>. This input current signal  $I_{IN\_M}$  may be obtained by measuring the input current I<sub>IN</sub>, or by other means. The modulation index controller 42 outputs a control signal m which is received by the 45 controllers  $14_1$ - $14_N$  in the individual first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_N$ . Referring to FIG. 12, each of the controllers (more precisely, the controller in each of the converter cells) receives a control signal  $m_1$ - $m_{N1}$  from the main controller 4. According to one embodiment, the individual first converter 50 cells  $\mathbf{1}_1$ - $\mathbf{1}_{N_1}$  receive the same control signal m, so that  $m=m_1=m_2=m_3=m_{N_1}$ . Details on this control signal m, which will also be referred to as modulation index m in the following, are explained below. Before going into further detail on the modulation index m, embodiments of the input 55 reference current controller 41 and the converter cell controller 42 are explained with reference to FIG. 14. The modulation index controller 42 serves to control the input current  $I_{IN}$ . Thus, the modulation index controller 42 may also be referred to as (input) current controller.

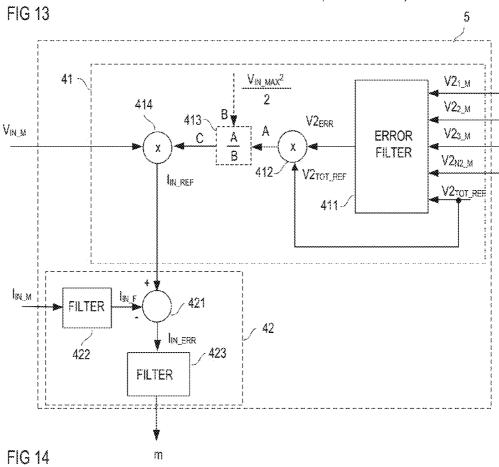

In context with FIG. 14, the input reference current controller 41 will briefly be referred to as current controller. Referring to FIG. 14, the current controller 41 may include an error filter 411 which receives the DC link voltage signals  $V2_{1\_M}V2_{N2\_M}$  and the total DC link voltage reference signal  $V2_{TOT\_REF}$ . The error filter 411 generates an error signal  $V2_{FRR}$  which is dependent on a difference between the

14

total DC link voltage reference signal  $V2_{TOT\_REF}$  and the sum of the individual DC link voltage signals  $V2_{1\_M^-}$   $V2_{N\_M}$ . The sum of these DC link voltage signals  $V2_{1\_M^-}$   $V2_{N\_M}$  represents the total DC link voltage  $V2_{TOT}$ . The error filter may calculate the difference

$$V_{2\_TOI} - \sum_{i=1}^{N_1} V_{2_{i\_M}}$$

(6)

and filter this difference in order to generate the error signal V2 $_{ERR}$ . The filter may have one of an proportional (P) characteristic, a proportional-integral (PI) characteristic, and a proportional-integral-derivative (PID) characteristic. A multiplier 412 receives the error signal V2 $_{ERR}$  and the total DC link voltage signal V2 $_{TOT\_REF}$  and provides the product of these signals V2 $_{ERR}$ , V2 $_{TOT\_REF}$  as an output signal A. An optional divider 413 receives the multiplier output signal A and a signal B, wherein the signal B is dependent on the square of the peak voltage level V $_{IN\_MAX}$  of the input voltage V $_{IN}$ . In the embodiment shown in FIG. 14,

$$B = \frac{V_{IN\_MAX^2}}{2}. (7)$$

An output signal C of the divider 413 equals the quotient A/B of the divider input signals A, B. A further multiplier 414 receives the divider output signal C and the input voltage signal  $V_{IN\_M}$  and is configured to multiply the instantaneous levels of these signals C and  $V_{IN\_M}$ . The further multiplier 414 provides the input current reference signal  $I_{IN\_REF}$  as an output signal.

As explained with reference to FIG. 13, the input current reference signal  $I_{IN\_REF}$  defines the desired current level of the input current  $I_{IN}$ . In case the input voltage  $V_{IN}$  is timely varying the input current reference signal  $I_{IN\_REF}$  is also timely varying. This is a result of generating the input current reference signal  $I_{IN\ REF}$  by multiplying the input voltage signal  $V_{I\!N\_M}$  with the output signal C of the divider **413**. The divider  $4\overline{1}3$  may be omitted. In this case, the further multiplier 414 receives the output signal A from the multiplier 412 as an input signal. Assuming that the input current reference signal  $I_{IN\_REF}$  is a periodic signal with a frequency defined by the input voltage signal  $V_{\emph{IN\_M}}$ , then an amplitude of the input current reference signal  $I_{IN\_REF}$  is defined by an amplitude of the input voltage signal  $V_{IN\_M}$ , and by one of the divider output signal C and the multiplier output signal A. These signals C and A are dependent on the total DC link voltage  $V2_{TOT}$ . The error filter 411 is configured to generate the error signal  $V2_{ERR}$  such that a signal level of the error signal  $V2_{ERR}$  increases when the total DC link voltage  $V2_{TOT}$  falls below the level defined by the total DC link voltage reference signal  $V2_{TOT\_REF}$ , so as to increase the level of the multiplier output signal A and the amplitude of the input current reference signal  $I_{IN\_REF}$ , and so as to regulate the total DC link voltage  $V\mathbf{2}_{TOT}$  such that a voltage level of the total DC link voltage  $V_{\it TOT}$  substantially corresponds to the voltage level as defined by the total DC link voltage reference signal  $V2_{TOT\_REF}$ . Equivalently, the error filter 411 decreases a level of the error signal  $V2_{ERR}$  when 60 the voltage level of the total DC link voltage  $V_{TOT}$  increases to above the voltage level defined by the total DC link voltage reference signal  $V2_{TOT\_REF}$ , so as to reduce the amplitude of the input voltage reference signal  $I_{IN\ REF}$  and to counteract a further increase of the total DC link voltage

The optional divider 413 may be used in those applications, in which the amplitude of the input voltage  $V_{IN}$  may

vary. The divider 413 acts in accordance with the feed-forward principle and helps to reduce the amplitude of the input current  $\mathbf{I}_{I\!N}$ , by reducing the amplitude of the input current reference signal  $\mathbf{I}_{I\!N\_REF}$ , when the amplitude of the input voltage  $\mathbf{V}_{I\!N}$  increases. In this case, the average input power, which is the input power averaged over one period of the input voltage  $\mathbf{V}_{I\!N}$  is substantially independent of the amplitude of the input voltage  $\mathbf{V}_{I\!N}$  and is substantially defined by the error signal  $\mathbf{V2}_{ERR}$  and the total DC link voltage reference signal  $\mathbf{V2}_{TOT\_REF}$ .

Referring to FIG. 14, the modulation index controller 42 includes a first filter 422 which receives the input current signal  $I_{IN\_M}$ . A subtractor 421 receives the input current reference signal  $I_{IN\_REF}$  and the filter output signal 422. This subtractor 421 subtracts the instantaneous signal level of the filter output signal  $I_{IN\_F}$  from the instantaneous level of the input current reference signal  $I_{IN\_REF}$ . An output signal  $I_{IN\_ERR}$  of the subtractor 421 represents a current error. That is, the subtractor output a signal  $I_{IN\_ERR}$  which represents an instantaneous difference between the desired input current 20 level and the actual input current level. A second filter 423 receives this current error signal  $I_{IN\_ERR}$  and provides the modulation index m. According to one embodiment, the first filter 422 has a low-pass characteristic. The second filter 423 may have one of a P, PI, and a PID characteristic.

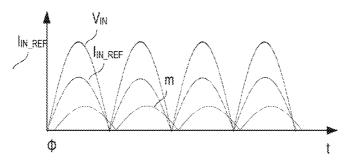

It can be shown that, in case the input voltage  $V_{IN}$  is a periodic voltage such as, for example, a rectified sine voltage with a frequency of 100 Hz or 120 Hz, the modulation index m is also a periodic signal, substantially with the same frequency as the input voltage  $V_{I\!N}$  FIG. 15 schematically illustrates the relationship between the input voltage  $V_{IN}$  and the modulation index m. As, referring to FIG. 14, the input current reference signal  $I_{IN\_REF}$  is obtained by multiplying the input voltage signal  $V_{IN\_M}$  with one of signals C and A which are dependent on the total DC link voltage, the waveform shown in FIG. 15 which represents the input voltage  $V_{I\!N}$  also represents the input current reference signal  $I_{IN\_REF}$  (when assuming that the voltage level of the total DC link voltage  $V_{TOT}$  does not change during the time period illustrated in FIG. 15). Referring to FIG. 15, there may be a phase-shift  $\phi$  between the input 40 voltage  $V_{IN}$  and the input current reference signal  $I_{IN\_REF}$ , respectively, on the one hand, and the modulation index m on the other hand. This phase difference  $\phi$  which is at most several degrees, may vary based on the difference between the input voltage reference signal  $\mathbf{I}_{I\!N\_REF}$  and the filtered input current signal  $I_{IN\_F}$ , and on the voltage V15 across the inductor 15 (see, FIG.  $\overline{11}$ ). Further, it can be shown that an amplitude of the varying modulation index m is dependent on the amplitude of the input voltage  $V_{IN}$ , whereas the amplitude of the modulation index m increases as the amplitude of the input voltage  $V_{I\!N}$  increases. According to one embodiment the main controller 4 is configured to generate the modulation index m as a normalized signal with values of between 0 and 1, wherein the modulation index m has an amplitude of 1 only in those cases in which an amplitude of the input voltage  $V_{IN}$  corresponds to the total 55 DC link voltage  $V_{TOT}$ .

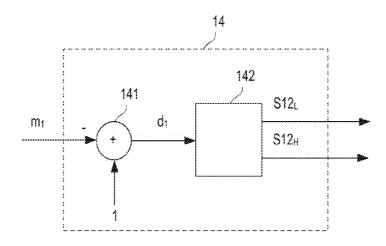

FIG. 16 shows one embodiment of the controller 14 in the first converter cell  $\mathbf{1}_1$  shown in FIG. 12. Each of the controllers (not shown in FIG. 12) in the other converter cells  $\mathbf{1}_2$ - $\mathbf{1}_{N1}$  may be implemented in accordance with the 60 controller 14 shown in FIG. 16. Referring to FIG. 16, the controller  $\mathbf{14}_1$  is configured to calculate a duty cycle  $\mathbf{d}_1$  based on the modulation index  $\mathbf{m}_1$  received from the cell controller 42. In the embodiment shown in FIG. 16, calculating the duty cycle d includes calculating the duty cycle d as follows: 65

16

For the purpose of explanation it is assumed that each of the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  receives the same modulation index m from the main controller, so that in the controller of each of the first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  the same duty cycle d=1-m is calculated.

Like the modulation index  $m_1$ , the duty cycle  $d_1$  may vary between 0 and 1. Like the modulation index  $m_1$ , the duty cycle  $d_1$  may timely vary and may vary between 0 and 1. A PWM controller 142 receives the duty cycle or, more precisely, a signal representing the duty cycle  $d_1$ , and generates the drive signal S12<sub>L</sub> for the low-side switch 12<sub>L</sub> and, optionally, the drive signal S12<sub>H</sub> for the high-side switch 12<sub>H</sub> based on the duty cycle  $d_1$ .

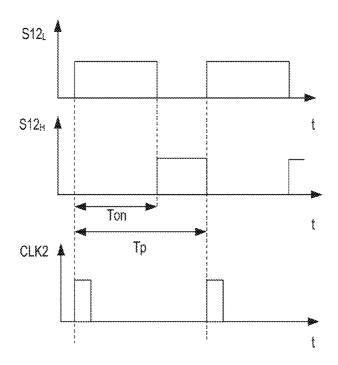

One way of operation of the PWM controller 142 shown in FIG. 16 is explained with reference to FIG. 17 in which timing diagrams of the drive signal  $S12_L$  received by the low-side switch  $12_L$  and the drive signal  $S12_H$  received by the high-side switch  $12_H$  are shown. Each of these drive signal  $S12_L$ ,  $S12_H$  can assume an on-level which switches on the respective switch, and an off-level which switches off the respective switch. Just for the purpose of explanation, in FIG. 17, an on-level is drawn as a high signal level, and an off-level is drawn as a low signal level.

Referring to FIG. 17, the PWM controller 142 is configured to cyclically switch on the low-side switch  $12_L$ . In particular, the PWM controller 142 may be configured to periodically switch on the low-side switch  $12_L$ . In FIG. 17, Tp denotes the duration of one drive cycle of the low-side switch  $12_L$ . The time period Tp is defined by a switching frequency fp, with Tp=1/fp. The switching frequency range of between 18 kHz and several 100 kHz. In FIG. 17 Ton denotes an on-time of the low-side switch  $12_L$ , which is a time period within one drive cycle in which the low-side switch  $12_L$  is switched on. The duty cycle  $d_1$  defines the duration of this on-time relative to the duration Tp of one drive cycle, wherein

$$d_1 = Ton/Tp \tag{9}.$$

Thus, the on-time increases relative to the time period Tp of one drive cycle as the duty cycle  $d_1$  increases, and vice versa.

Referring to FIG. 17, the PWM controller 142 may switch on and off the high-side switch  $12_H$  complementary to switching on and off the low side switch  $12_L$ . That is, the PWM controller 142 may be configured to switch on the high-side switch  $12_H$  when the low-side switch  $12_L$  is switched off, and vice versa. There may be a delay time between switching off the low-side switch  $12_L$  and switching on the high-side switch  $12_H$ , and between switching off the high-side switch  $12_H$  and again switching on the low-side switch. However, such delay times are not shown in FIG. 17. During such delay times, the rectifier element of the high-side switch  $12_H$  conducts. In case the high-side switch  $12_H$  is replaced by a rectifier element, the rectifier element "automatically" conducts when the low-side switch  $12_L$  is in the off state.

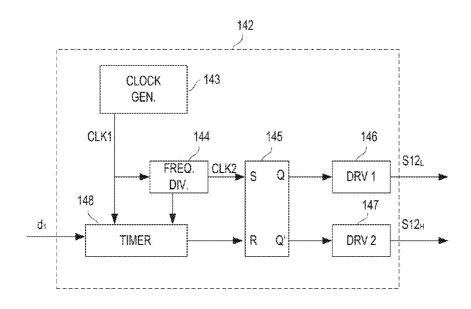

FIG. 18 shows one embodiment of the PWM controller 142 in the controller 14 shown in FIG. 16. Referring to FIG. 18, the PWM controller 142 may include a clock generator 143 which generates a first clock signal CLK1. A frequency of this first clock signal CLK1 may be higher than the switching frequency fp. According to one embodiment, the frequency of the first clock signal CLK1 is at least several MHz. A frequency divider 144, which may be implemented with a counter or the like, receives the first clock signal CLK1 and generates a second clock signal CLK2. The

second clock signal CLK2 defines the switching frequency fp. This second clock signal CLK2 is also illustrated in FIG. 17. Referring to FIG. 17, the drive signal  $S12_L$  of the low-side switch  $12_L$  may assume an on-level each time a signal pulse of the second clock signal CLK2 occurs. A latch, such as an SR flip flop 145 may receive the second clock signal CLK2 at a set input S. A first driver 146 has an input coupled to a non-inverting first output Q of the flip flop 145 and generates the drive signal  $S12_L$  of the low-side switch  $12_L$  based on the output signal at the first input Q of the flip flop 145. An optional second driver 147 generates the drive signal  $S12_H$  of the high-side switch  $12_H$  based on an output signal at a second inverting output Q' of the flip flop **145**. In order to adjust the on-time Ton of the low-side switch  $12_L$ , a timer 148 receives the second clock signal CLK2, the duty cycle signal d and the first clock signal CLK1. The timer 145 is configured to reset the flip flop 145, in order to cause the drive signal  $S12_L$  to assume the off-level at a predefined time period after a signal pulse of the second clock signal CLK2, wherein this time period is 20 defined by the duty cycle d.

It should be noted that FIG. 18 shows only one of a variety of possible implementations of the PWM controller 142. Of course, the implementation of the PWM controller 142 is not restricted to the specific embodiment shown in FIG. 18.

It can be shown that the modulation index generated as explained above approximately corresponds to

$$m = V_{IN}/V2_{TOT} \tag{10}$$

wherein  $V_{IN}$  denotes the instantaneous voltage level of the 30 input voltage  $V_{IN}$ , and  $V\mathbf{2}_{TOT}$  represents the (desired) total DC link voltage. However, this is only an approximation. Referring to what is stated in context with FIGS. 13 and 14 above, the modulation index m is not only dependent on the input voltage  $V_{IN}$ , but may further vary based on the 35 difference between current level of the input current  $I_{IN}$  and the reference input current  $I_{IN}$  REF.

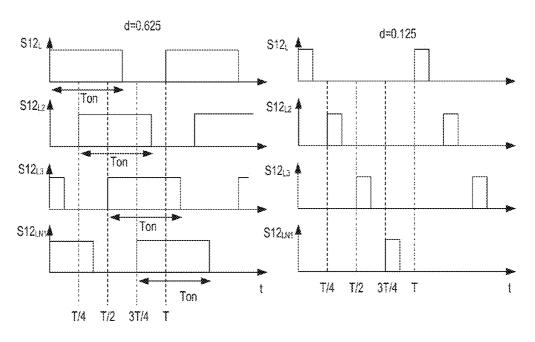

According to one embodiment, the controller 14 in the first converter cell 1, and corresponding controllers in the other converter cells  $1_2$ - $1_{N1}$  receive the same modulation 40 index m from the main controller 4, and the individual converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  are operated in an interleaved fashion. This is explained with reference to FIGS. 19A and 19B. FIGS. 19A and 19B show timing diagrams of the drive signal  $S12_L$  of the low-side switch  $12_L$  in the first converter 45 cell  $\mathbf{1}_1$  and timing diagrams of drive signals  $S12_{L2}$ - $S12_{LN1}$  of corresponding low-side switches in the other converter cells  $1_2$ - $1_{N1}$ . In FIGS. 19A and 19B, these drive signals S12<sub>L</sub>- $S12_{LN1}$  are shown at two different duty cycles d, namely d=0.625 in FIG. 19A and d=0.125 in FIG. 19B. Operating 50 the individual converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  in an interleaved fashion means that the drive cycles of the individual converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  begin with a time offset of Tp/N1. Here, like in the embodiments explained before, N1 denotes the number of first converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$ . If, for example, N1=4, the 55 time offset is Tp/4, as shown in FIGS. 19A and 19B. For example, there is a delay time of Tp/4 between the begin of the on-time of the drive signal  $S12_L$  in converter cell  $1_L$  and the begin of the on time of the drive signal  $S12_{L2}$  in the converter cell 1<sub>2</sub>, there is a delay time Tp/4 between the begin of the-on time of the drive signal  $S12_{L2}$  in the converter cell  $\mathbf{1}_2$  and the begin of the on time of the drive signal  $S12_{L3}$  in the converter cell  $1_3$ , and there is a delay time Tp/4 between the begin of the on time of the drive signal  $S12_{L3}$  in the converter cell  $1_3$  and the begin of the on time of the drive signal  $S12_{LN1}$  in the converter cell  $1_{N1}$ . Operating the individual converter cells  $\mathbf{1}_1$ - $\mathbf{1}_{N1}$  in an interleaved

18

fashion results in an overall switching frequency of N1·fp. This higher overall switching frequency may help to reduce ripples in the input current  $I_{I\!N}$  that may result from the switched-mode operation of the first power converter 10 or, more precisely, from a switched mode operation of the individual first converter cells  $1_1$ - $1_{N1}$ .