© 2019 IEEE

IEEE Transactions on Industrial Electronics, Vol. 34, No. 7, pp. 6036-6047, July 2019

# P3DCT - Partial-Power Pre-Regulated DC Transformer

D. Neumayr, M. Vöhringer, N. Chrysogelos, G. Deboy, J. W. Kolar

Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# P<sup>3</sup>DCT - Partial-Power Pre-Regulated DC Transformer

Dominik Neumayr<sup>\*</sup>, *Student Member, IEEE*, Matthias Vöhringer<sup>\*</sup>, Nikolaos Chrysogelos<sup>\*</sup>, Gerald Deboy<sup>†</sup>, *Senior Member, IEEE* and Johann W. Kolar<sup>\*</sup>, *Fellow, IEEE* \*Power Electronic Systems Laboratory, ETH Zurich, Switzerland <sup>†</sup>Infineon Technologies Austria AG, Villach, Austria

Corresponding Author: Dominik Neumayr, ETL I12, Physikstrasse 3, 8092 Zurich, Switzerland E-Mail: neumayr@lem.ee.ethz.ch, Tel.: +41 44 633 83 58

Abstract—In this paper a new approach to regulate the output voltage of a resonant, constant voltage transfer ratio 380 V/48 V isolated DC/DC converter is presented. Rather than applying variable frequency control to the resonant converter which would result in reactive power processing and a more complicated EMC filter design, the converter remains in its optimal operating point all time and an additional partial-power (PP) processing auxiliary converter is used to tightly regulate the output voltage. The PP converter, supplied through a tertiary winding of the resonant converter's transformer, regulates the output by adding or subtracting voltage from the DC input and has only a marginal impact on the overall efficiency of the DC/DC converter. The principal of operation is explained in detail including Sankey diagrams to illustrate the power processing of the converter and a feedback control system is proposed to tightly regulate the 48 V output voltage. A hardware demonstrator rated at 1.5 kWis implemented to cope with input voltage variations between  $340\,\mathrm{V}$  -  $420\,\mathrm{V}$  and experimental results are provided showing that the the output voltage can be kept within  $\pm 1\,\%$  of the nominal  $48\,\mathrm{V}$  even under harsh input voltage and load transients. The realized DC/DC converter with PP pre-regulation features an overall efficiency of 97.7 % at rated power and a power density of  $8.6 \,\mathrm{kW/dm^3}$  (141 W/in<sup>3</sup>).

This paper is accompanied with supplementary video material demonstrating the principle of operation of the implemented converter prototype.

Index Terms—Pre-Regulation, Auxiliary Converter, Partial-Power Converter, Series-Resonant LLC Converter, DC Transformer

# I. INTRODUCTION

The series-resonant LLC DC/DC converter is widely accepted in the IT and telecom industry due to several desired features such as high efficiency, low EMI and high power density. The converter is typically employed to step down from 380 V and to supply a 48 V power distribution bus. When operated exactly at the resonance frequency of the LLC tank, the voltage transfer ratio becomes ideally independent of the actual load [1]. At this point, the LLC converter is self-regulated and adjusts its current automatically according to the load condition, essentially behaving like a DC transformer (DCT). If regulation of the output voltage is required, fixed duty-cycle and variable frequency control could be applied which shifts the LLC tank operating point out of resonance

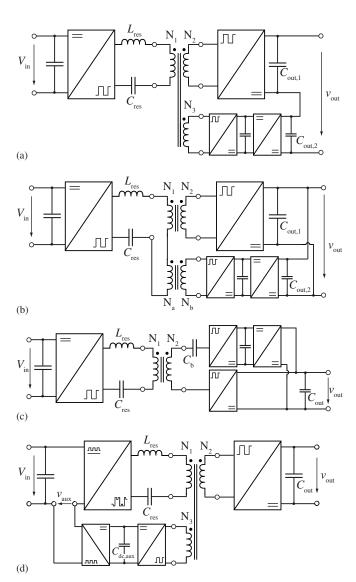

into inductive operation in case a lower voltage transfer ratio is needed [17]-[20]. However, besides the reduced efficiency due to the additionally processed reactive power, the arising load dependency and the potential loss of Zero Voltage Switching (ZVS), variable frequency control is often depreciated as it complicates the EMC filter design. An alternative method which keeps the resonant converter in its optimal operating point is to employ an additional partial-power (PP) auxiliary converter to regulate the output voltage [5]-[12]. This auxiliary converter is dimensioned for just a small fraction of the rated power of the resonant converter and therefore has only marginal impact on the overall efficiency of the converter system. The PP regulation approach has also been thoroughly analyzed in PV applications for high efficiency maximum power point tracking (MPPT) and/or PV string balancing [13]-[16]. In [7], [8] a PP post regulator as shown in Fig. 1 (a) is proposed, where the output of a PP DC/DC converter is connected in series with the output of the main converter and the load. The input of the PP DC/DC regulator is connected to an intermediate DC-link supplied by means of a tertiary transformer winding and subsequent rectifier. Unidirectional buck, boost and buck-boost DC/DC converters are suggested to implement the post-regulator. In [11], [12] the topology shown in Fig. 1 (b) is described. In this configuration, the primary winding of a separate auxiliary transformer (two separate cores) is connected in series with the primary winding of the main transformer and the output of the PP DC/DC converter is connected in parallel to the output of the main converter. In order to regulate the output voltage, the partialpower converter (PPC) is used to adjust the voltage across the primary side of the main converter. A similar approach is presented in [5], however there the DC-side of the PPC is connected in parallel to the DC input  $(V_{in})$  by means of a boost converter. In the topology suggested in [10], an auxiliary DC/DC converter is inserted between the rectifier bridge-legs of the main converter as illustrated in Fig. 1 (c). The auxiliary converter alters the power flow across the preceding rectifier bridge-leg by means of adjusting the rectifier voltage (voltage across the capacitor between the rectifier and the auxiliary DC/DC converter) in order to regulate  $V_{out}$ . However, since the auxiliary DC/DC converter processes around half the

Fig. 1. (a)-(c) Several approaches to provide a regulated output voltage by means of an additional partial-power (PP) converter and (d) the filter-less, PP, pre-regulation approach proposed in this paper.

rated power of the main converter, the proposed topology constitutes a 11/2 stage converter rather then an unregulated main converter with PP regulation.

The filter-less, pre-regulation approach proposed in this paper is depicted in Fig. 1 (d). Here, the output voltage  $V_{out}$  is regulated by adjusting the average voltage applied to the input of the main converter. Omitting additional filter components at the output of the PPC, a pulse width modulated voltage is impressed between the negative terminal of the DC input  $(V_{in})$  and the main converter. It follows that the square wave voltage applied to the resonant tank of the DCT exhibits a high frequency superimposed PWM pattern which allows to adjust the average amplitude of the fundamental square wave voltage applied to the LLC tank by adopting the modulation index.

In the following the proposed converter topology is presented in detail and the basic theory of operation is discussed (Section II). Subsequently, in Section III a control system for the proposed converter is designed. In order to demonstrate the basic concept and verify the claimed performance of the proposed PP pre-control, a hardware demonstrator is implemented as described in detail in Section IV. The implemented 380 V/48 V DC/DC converter is rated at 1.5 kW and has been designed to cope with input voltage variations in the range of 340 V - 420 V. The design specifications are summarized in Tab. I. Subsequently, in Section V experimental results are

TABLE I DESIGN SPECIFICATION OF THE CONVERTER

| Parameter                 | Value                                                                      | Description                                                                 |  |  |

|---------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| $V_{\rm in,nom}$          | $380\mathrm{V}$                                                            | Nominal DC input voltage                                                    |  |  |

| $V_{\mathrm{in},\Delta}$  | $340 \mathrm{V} - 420 \mathrm{V}$<br>( $\approx \pm 10.0 \%$ )             | Input voltage range                                                         |  |  |

| $V_{\rm out,nom}$         | $48\mathrm{V}$                                                             | Nominal DC output voltage                                                   |  |  |

| $V_{\mathrm{out},\Delta}$ | $\begin{array}{l} \pm 500 \mathrm{mV} \\ (\approx \pm 1.0 \%) \end{array}$ | Max. output voltage deviation<br>in steady-state and during tran-<br>sients |  |  |

| $P_{\rm r}$               | $1.5\mathrm{kW}$                                                           | Rated power                                                                 |  |  |

| $\eta^*$                  | 98%                                                                        | Target efficiency $98\%$ and max. power density                             |  |  |

presented showing the performance of the implemented prototype in steady-state and during transients. Finally, Section VI concludes this paper.

# II. PARTIAL-POWER PRE-REGULATED (P<sup>3</sup>) DC TRANSFORMER

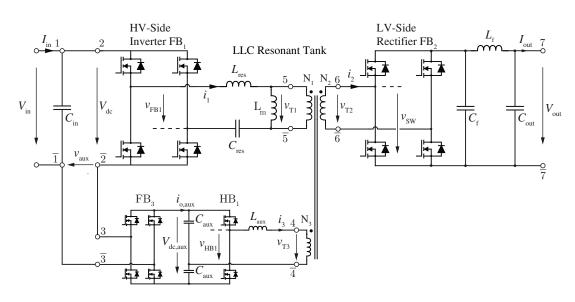

The proposed topology shown in Fig. 2 consist of an unregulated resonant LLC converter and an additional PPC employed to tightly control output voltage  $V_{out}$  by pre-regulating the voltage applied to the input of the LLC converter. The fullbridge input stage,  $FB_1$ , of the LLC converter processes the main share of the output power and the resonant tank is dimensioned to feature a resonance frequency typ. in the range of 70 kHz - 250 kHz in order to achieve a high power density. Since the resonant converter is always operated exactly at the resonance frequency regardless of input voltage and load conditions, a very efficient transfer of real power to the 48 V output is possible because only the reactive power to enable ZVS of full-bridge  $FB_1$  must be processed. The stepped-down rectangular AC voltage appearing at the secondary side of the transformer,  $v_{T2}$ , is then rectified by means of a diode rectifier or a low-voltage MOSFET full-bridge (shown in Fig. 2) for increased conversion efficiency (sync. rectification) and/or bidirectional power flow support. When operated at resonance, the LLC converter is capable of autonomously adapting the current in case of a load step in order to keep the output voltage at its nominal value according to the voltage transfer ratio defined by the transformer turns ratio. Thus, the control system of the pre-regulation converter just has to ensure a proper input voltage level of  $FB_1$  to compensate for ohmic voltage drops and other non-idealities in the main converter in order to keep  $V_{\rm out}$  tightly regulated to the desired  $48\,{

m V}$ reference value.

Partial-Power Pre-Regulation (P3) Converter

Fig. 2. Schematic of the proposed 380 V/48 V DC/DC converter comprised of a unregulated, resonant LLC converter operating as DC Transformer (DCT) and an additional Partial-Power (PP) Pre-Regulation (P<sup>3</sup>) auxiliary converter dedicated to tightly control output voltage  $V_{o}$ .

#### A. Partial-Power Pre-Regulation Auxiliary Converter

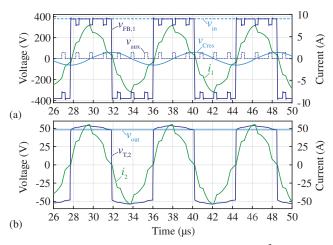

As shown in Fig. 2 a PPC with bidirectional power flow and bipolar voltage generation capabilities is proposed. The rectifier-side terminals of the PPC (cf.  $4 - \overline{4}$ ) are connected to a tertiary winding of the isolation transformer  $(N_3)$  and the output terminals of the inverter (cf.  $3-\overline{3}$ ) are connected between the negative terminal of the input capacitor,  $C_{in}$ , and the negative rail of the full-bridge  $FB_1$  of the main converter. The PP DC-link,  $V_{DC,aux}$ , formed by two stacked capacitors  $C_{\rm aux}$  is supplied from the LLC converter transformer through the low-voltage rectifier half-bridge HB<sub>1</sub> operated with the switching frequency of the main converter. For the given input voltage range (cf. Tab. I), the level of  $V_{\rm DC,aux}$  is regulated typ. to 50 V - 60 V by adjusting the phase-shift between HB<sub>1</sub> and the leading-leg of full-bridge  $FB_1$  of the main converter. One of the novelties of this approach is that the switched voltage  $v_{\rm aux}$ , generated from pulse-width modulation of  $V_{\rm DC,aux}$ , is directly impressed between the terminals  $\overline{1} - \overline{2}$  (cf. Fig. 2), taking advantage of the transfer characteristic of the LLC resonant tank and omitting additional filter elements. The waveforms of a circuit simulation with preliminary system parameters according to Tab. II are provided in Fig. 3 (a) and (b) in order to illustrate the basic operation of the proposed converter system. Given that the switching frequency of  $FB_3$ is a multiple of the resonance frequency (typ. factor 4-10) of the main converter, a rectangular waveform with modulated amplitude due to the superimposed pulse pattern is applied to the LLC tank of the main converter. It follows that the average amplitude of the square wave voltage applied to the resonant tank can be adjusted by means of the modulation index of  $\mathrm{FB}_3$ , although the switched voltage  $v_{\mathrm{aux}}$  causes the resonant current  $i_1$  to slightly deviate from it's ideal sinusoidal shape.

Choosing a switching frequency multiple of 6 or higher, the Total Harmonic Distortion (THD) of  $i_1$  can be kept below  $\approx 12\%$  according to circuit simulation.

TABLE II

PARAMETERS OF THE P<sup>3</sup>DCT CIRCUIT SIMULATION (FIG. 3)

| System                                                           |                                         | P <sup>3</sup> DCT                                                     |                                               |                                                                                                                |                                                   |

|------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| $V_{ m in} \ V_{ m out} \ V_{ m dc,aux} \ P_{ m r} \ P_{ m aux}$ | 380 V<br>48 V<br>50 V<br>1.5 kW<br>60 W | $C_{\rm res} \\ C_{\rm in} \\ C_{\rm out} \\ L_{\rm res} \\ L_{\rm m}$ | 150 nF<br>400 μF<br>5.4 mF<br>10 μH<br>400 μH | $C_{\mathrm{aux}}$<br>$f_{\mathrm{s,FB,1}}$<br>$f_{\mathrm{s,HB,1}}$<br>$f_{\mathrm{s,FB,3}}$<br>$N_1:N_2:N_3$ | 125 μF<br>120 kHz<br>120 kHz<br>720 kHz<br>14:2:1 |

Fig. 3. Switching frequency waveforms of the simulated  $P^3DCT$  converter operating at rated power (1.5 kW). Primary side related voltage and current waveforms are shown in (a), secondary side related waveforms in (b).

Given a converter input current  $I_{in} \ge 0$  for unidirectional operation of the main converter, the polarity of the average pre-

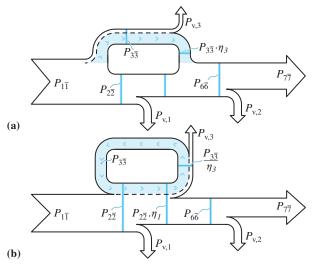

regulation voltage,  $\overline{v}_{aux}$ , defines the direction of power flow in the PPC as illustrated by the Sankey diagrams in Fig. 4. In case of  $\overline{v}_{aux} > 0$ , a fraction of the output power  $P_{77}$  (index  $7\overline{7}$ denotes the respective power flow interface according to the terminal labels in Fig. 2) is actually provided by the PPC as depicted in Fig. 4 (a). On the contrary, for  $\overline{v}_{aux} < 0$ , power  $P_{3\overline{3}}$

Fig. 4. Sankey diagram of the power flow inside the P<sup>3</sup>DCT for pre-regulation voltage (a)  $\overline{v}_{aux} > 0$  and (b)  $\overline{v}_{aux} < 0$ . The indices denote the power flow through the respective interfaces labeled in Fig. 2. Power loss  $P_{v,1}$  and  $P_{v,2}$  is caused by the inverter and rectifier stage of the main converter, respectively.  $P_{v,3}$  are the losses associated with the processing of the pre-regulation power flow.

circulates within the PPC and the inverter stage of the DCT and does not contribute to the output power  $P_{77}$ . Consequently, an operation of the P<sup>3</sup>DCT with  $\overline{v}_{aux} > 0$  is advantageous in terms of efficiency.

#### B. Power Rating and Efficiency Impairment

The power requirement of the PPC is given by

$$P_{\text{aux}} = \frac{\overline{v}_{\text{aux}}}{V_{\text{in}}} P_{\text{out}} = \frac{V_{\text{in}} - nV_{\text{out}} - \Delta v(i_1)}{V_{\text{in}}} P_{\text{out}}$$

$$= \left(1 - n\frac{V_{\text{out}}}{V_{\text{in}}} - \frac{\Delta v(i_1)}{V_{\text{in}}}\right) P_{\text{out}},$$

(1)

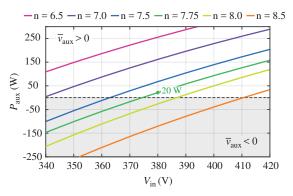

where,  $n = \frac{N_1}{N_2}$ , is the primary-to-secondary winding turnsratio of the isolation transformer and  $\Delta v$ , a function of the resonant current  $i_1$ , takes the voltage drop across circuit nonidealities such as e.g. transistor on-state or winding resistances into account. Expression (1) is plotted in Fig. 5 with respect to the input voltage,  $V_{\rm in}$ , and different transformer turns-ratios. It can be seen that depending on n, unipolar operation is feasible, e.g.  $\overline{v}_{aux} \leq 0$  for n > 8.75 considering the given input voltage range, which would allow to further simplify the topology of the PPC (half-bridge instead of  $FB_3$  and diode rectifier instead of HB<sub>1</sub>). However, as a consequence of unipolar operation, the total power to be processed by the PPC increases substantially due to the additional bias in  $\overline{v}_{aux}$  at nominal input voltage which reduces the overall conversion efficiency of the P<sup>3</sup>DCT although operation with circulating power (cf. Fig. 4 (b)) could be completely omitted

Fig. 5. Power requirement of the PPC as a function of the input voltage  $V_{\rm in}$  and the transformer turns ratio,  $n = N_1 : N_2$ , at 1.5 kW output power.

if  $\overline{v}_{aux}$  remains positive for n < 7.0. For the implemented hardware demonstrator described in detail in Section IV of this paper, a turns-ratio of n = 7.75 was chosen (cf. green line in Fig. 5) which results in a maximum power requirement of approximately 150 W. At rated output power and nominal input voltage,  $V_{in} = 380$  V, the PPC processes only around 20 W. Thus, the PPC must only be dimensioned for a fraction of the nominal output power processed by the main converter.

A numerical example based on efficiency measurements of the hardware demonstrator presented later in Section V should illustrate the marginal impairment of the overall conversion efficiency due to the PPC. The total conversion efficiency of the  $P^3DCT$  can be derived from the Sankey diagrams (cf. Fig. 4) and is given by

$$\eta = \begin{cases} \eta_1 \eta_2 \cdot (1+k) - \frac{\eta_2}{\eta_{\text{aux}}} \cdot k, & \overline{v}_{\text{aux}} < 0\\ \eta_1 \eta_2 \cdot (1-k) + \eta_2 \eta_{\text{aux}} \cdot k, & \overline{v}_{\text{aux}} > 0 \end{cases}$$

(2)

wherein  $\eta_1$  and  $\eta_2$  denotes the efficiency of the inverter and the rectifier stage, respectively. Accordingly, the efficiency of the main converter is given by  $\eta_m = \eta_1 \eta_2$ . The efficiency of the PP pre-regulator is denoted with  $\eta_3$  and factor  $k = P_{aux}/P_1$ is the ratio between the power processed by the pre-regulator and the DCT. Given the efficiency of the main converter,  $\eta_m =$  $99.25\% \cdot 98.75\% = 98.0\%$ , a power ratio  $k = {}^{20}W/{}_{1.5\,kW} =$ 0.013 and an efficiency  $\eta_{aux} = 82\%$  at 20 W of the PPC, then according to (2),  $\eta = 97.7\%$  results if  $\overline{v}_{aux} < 0$  and  $\eta = 97.8\%$  if  $\overline{v}_{aux} > 0$ . Hence, the (very) low efficiency (82\%) of the PPC reduces the overall conversion efficiency of the converter at rated power only by 0.2% - 0.3% at rated power and nominal input voltage.

# **III. CONTROL SYSTEM DESIGN**

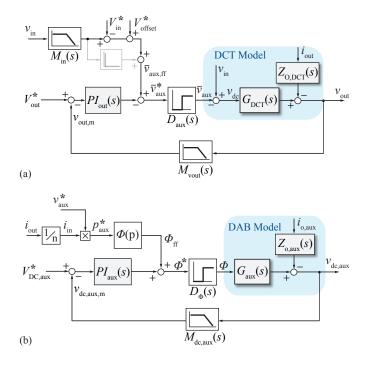

In order to tightly regulate the output voltage to 48 V and reject load and input voltage disturbances, the control system depicted in Fig. 6 is proposed. Two feedback control loops are employed to regulate  $v_{out}$  and the partial-power DClink voltage  $v_{DC,aux}$ . As it will become evident from the experimental results presented in Section V, the DC-link of the PPC is sized large enough and/or the bandwidth of the  $v_{DC,aux}$  control loop suffices such that coupling between the control loops can be neglected and, for the sake of simplicity, two individual SISO designs are considered in the following. The proposed small-signal feedback loop of the output voltage

Fig. 6. Schematic of the control system to regulate (a) the output voltage,  $v_{\rm out}$ , of the main converter and (b) the DC-link voltage of the auxiliary converter,  $v_{\rm DC,aux}$ .

is shown in Fig. 6 (a). A first-order low-pass filter with  $1 \,\mathrm{kHz}$  corner frequency,  $M_{\mathrm{vout}}$ , is employed to take both analog and digital implemented low-pass filters of the output voltage measurement into consideration. The control error, the difference between reference  $V_{\mathrm{out}}^*$  and  $v_{\mathrm{out,m}}$ , is passed on to the PI controller,

$$\operatorname{PI}_{\operatorname{out}}(s) = K_{\operatorname{p,out}} \frac{(sT_{\operatorname{i,out}} + 1)}{s}.$$

(3)

Deviations of the input voltage from the nominal  $V_{\rm in}^* = 380 \,{\rm V}$ are directly compensated by means of the feed-forward term,  $\overline{v}_{\rm aux,ff}$ . The transfer function  $M_{\rm in}$  represents a first-order lowpass with 10 kHz corner frequency and captures the phasedelay introduced by the measurement and conditioning of  $v_{in}$ . A derivative term can be included to better cope with abrupt input voltage changes but was finally not implemented on the Digital Signal Controller (DSC) of the hardware demonstrator. The parameter  $V^{\ast}_{\rm offset},$  added to the measured input voltage, is used to adjust  $\overline{v}^*_{aux}$ , such that the nominal input voltage results in the desired 48 V output voltage for a specific transformer turns-ratio. According to the polarity of the auxiliary voltage  $\overline{v}_{aux}$  in Fig. 2,  $\overline{v}_{aux}$  must be decreased in order to increase the output voltage, which explains why the output of  $\mathrm{PI}_{\mathrm{out}}$  is subtracted from the feed-forward term,  $\overline{v}_{aux,ff}$ . The dead-time introduced by the pulse width modulator (PWM) of  $FB_3$  is considered by means of a second-order Padé approximation of the delay  $D_{\text{aux}}(s) = e^{-s \frac{T_{\text{s,aux}}}{2}}$ , where  $T_{\text{s,aux}}$  is the switching period of FB3. In order to determine suitable coefficients for the PI controller, a small-signal model of the DCT including the CLC filter (cf. Fig. 2) was derived based on the analysis

presented in [1]. The PI controller parameter (3) for a conservative design with 400 Hz bandwidth and  $60^{\circ}$  phase-margin are listed in Tab. III.

| TABLE III<br>Controller Parameters |                 |                                        |  |  |  |

|------------------------------------|-----------------|----------------------------------------|--|--|--|

| Controller                         | Parameter       | Value                                  |  |  |  |

| Plout                              | $K_{\rm p,out}$ | $17.0 \times 10^3$                     |  |  |  |

| r lout                             | $T_{\rm i,out}$ | $2.94\times10^{-6}$                    |  |  |  |

| Plaux                              | $K_{\rm p,aux}$ | 1.5                                    |  |  |  |

| r I <sub>aux</sub>                 | $T_{i,aux}$     | 0.02                                   |  |  |  |

| $\Phi(p)$                          | m               | $3.641\times 10^{-3}~(\mathrm{rad/W})$ |  |  |  |

| $\Psi(p)$                          | q               | $6.9\times 10^{-2}~({\rm rad})$        |  |  |  |

The proposed feedback loop to control the PPC DC-link voltage,  $v_{\rm DC,aux}$ , is depicted in Fig. 6 (b). By means of another PI controller,

$$\mathrm{PI}_{\mathrm{aux}}(s) = K_{\mathrm{p,aux}} \frac{(sT_{\mathrm{i,aux}} + 1)}{s}, \tag{4}$$

the phase-shift  $\Phi$  between the leading-leg of FB<sub>1</sub> and HB<sub>3</sub> is regulated in order to control the correct power flow at the terminals of the transformer tertiary winding (cf.  $4 - \overline{4}$  in Fig. 2) such that  $v_{\text{DC,aux}}$  meets the reference value  $V_{\text{dc,aux}}^*$ . A first-order low-pass filter with 1 kHz corner frequency,  $M_{\text{DC,aux}}$ , is employed to model the measurement and conditioning of the DC-link voltage. The dead-time introduced by the PWM of HB<sub>1</sub> is considered by means of a secondorder Padé approximation of the delay  $D_{\phi}(s) = e^{-s\frac{T_s}{2}}$ , where  $T_s$  is the switching period of FB<sub>1</sub>. In order to determine proper parameters for PI<sub>out</sub>(s), a small-signal model of the PPC rectifier,  $G_{\text{aux}}(s) = \frac{v_{\text{DC,aux}}(s)}{\Phi(s)}$ , was derived according to the work in [2], [3]. The PI controller parameter (4) for a conservative design with 100 Hz bandwidth and 135° phasemargin are listed in Tab. III. By estimating the power processed by the PPC,

$$p_{\rm aux}^* = \overline{v}_{\rm aux} I_{\rm in} \approx \overline{v}_{\rm aux}^* I_{\rm in} = \overline{v}_{\rm aux}^* \frac{I_{\rm out}}{n},\tag{5}$$

a feed-forward phase-shift term,  $\Phi_{\rm ff}^*$ , is added to the output of controller PI<sub>aux</sub>. The phase-shift in the range  $[-\pi/2, \pi/2]$  as a function of power is given by [3],

$$\Phi(p_{\rm aux}^*) = \frac{\pi}{2} \left( 1 - \sqrt{1 - \frac{8f_{\rm s,FB1}L_{\rm aux}|p_{\rm aux}^*|}{(1/2v_{\rm DC,aux})(N_3/N_2v_{\rm out})}} \right) \quad (6)$$

$$\cdot \operatorname{sign}(p_{\rm aux}^*),$$

and is linearized around the nominal operating point ( $P_{\rm out} = 1.5 \,\mathrm{kW}$ ,  $P_{\rm aux} = 20 \,\mathrm{W}$ ) in order to facilitate implementation on the DSC of the hardware prototype,

$$\Phi(p_{\rm aux}^*) \approx m \cdot p_{\rm aux}^* + q, \tag{7}$$

with parameters m and q listed in Tab. III.

In order to implement the designed controllers on the DSC of the hardware prototype (cf. Section IV),  $PI_{out}(s)$  and  $PI_{aux}(s)$  were discretized using the Tustin z-transformation with a sample frequency of  $F_{ctrl} = 25 \text{ kHz}$ . In addition, the designed PI controllers were augmented with output limitation and anti-windup capability.

#### IV. HARDWARE PROTOTYPE

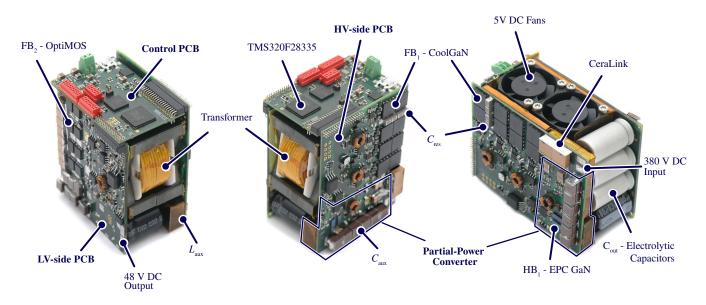

In order to verify the proposed converter topology shown in Fig. 2 and assess the performance of the suggested control system, a hardware prototype was realized as will be described in this section. The implemented  $380 \text{ V}/48 \text{ V} \text{ P}^3\text{DCT}$  is depicted in Fig. 7. The system is rated for 1.5 kW and exhibits a total volume of  $175 \text{ cm}^3$  which corresponds to a power density of  $8.6 \text{ kW/dm}^3$  ( $141 \text{ W/in}^3$ ). Only 10% - 15% of the total converter volume is occupied by components related to the PPC. The component parameter values of the realized hardware are listed in Tab. IV and have been obtained from a comprehensive Pareto design optimization, seeking maximum power density at a minimum target efficiency of around 98%.

As it can be seen from the picture, the converter system is realized by means of two individual power PCBs, the first PCB is equipped with power electronic components of the HVside (380 V) and the PPC and the second PCB with the power electronics of the LV-side (48 V). In addition, a third dedicated digital control and auxiliary supply board is connected to both power PCBs. In order to extract the losses from the power electronics, both power PCBs are attached to the baseplates of a double-sided forced-air cooled heatsink. The implemented cooling system with  $25 \times 25 \,\mathrm{mm}$ , 5 V DC fans achieves a  $R_{\rm th}$  of around 0.49 K/W at a volume of roughly  $33\,{\rm cm}^3$ which corresponds to a Cooling System Performance Index (CSPI, [4]) of roughly  $62 \,\mathrm{W/(K \, dm^3)}$ . The primary-side fullbridge (cf. FB<sub>1</sub>) is realized with 600 V,  $55 \text{ m}\Omega$  E-mode GaN from Infineon, whereby two physical transistors are connected in parallel per switch. The employed gate drive employs the LM5114 IC and the MAX13256 full-bridge transformer driver IC for galvanic isolation of the high-side supply voltage and is described in detail in [21].

The secondary-side full-bridge (cf. FB<sub>2</sub>) is realized with 60 V,  $2.5 \text{ m}\Omega$  OptiMOS from Infineon, also with two physical transistors per switch, and employs the UCC27211A gate drive

IC with bootstrapping supply of the high-side gate voltage. The switching frequency of  $FB_1$  and  $FB_3$  is 100 kHz which corresponds to the natural frequency of the series resonant tank comprised of  $L_{\sigma}$ , the stray inductance of the transformer, and  $C_{\rm res}$ . The employed three-winding transformer, encompassed by the PCBs and cooled by the air-flow exiting the heatsink, is implemented by means of a PQ 40/40, N97 MnZn ferrite core with custom-machined total height of 30 mm. In order to adjust the magnetizing current to achieve Zero Voltage Switching (ZVS) of  $FB_1$ , a total air gap of 200 µm is introduced resulting in a magnetizing inductance of 950 µH. HFlitz wire according to the specifications in Tab. IV is used to implement the three windings of the transformer, whereby  $N_1 = 31$  and  $N_2 = 4$  results in a turns ratio of n = 7.75and  $N_3 = 2$  results in a turns ratio of  $n_{\rm aux} = 15.5$ . The stacked DC-link capacitors of the PPC, Caux, are assembled from  $5 \times 22 \,\mu\text{F}$ ,  $100 \,\text{V}$  MLCCs, and  $V_{\text{DC,aux}}$  is regulated to 50 V by means of adjusting the phase-shift between FB<sub>1/2</sub> and HB<sub>3</sub>. An additional discrete inductor,  $L_3 = 3.0 \,\mu\text{H}$ , is added which results in a linearized power-transfer to phaseshift ratio of  $\frac{P_{\rm aux}}{\Phi} \approx 4.795\,{\rm W}/^\circ$  (cf. (7) and Tab. III). The PPC is designed to process peak powers up to 150 W in order to cope with the specified input voltage range (340 V - 420 V)up to the rated power of the converter. At nominal DC input voltage,  $V_{\rm in} = 380 \,\mathrm{V}$ , and  $1.5 \,\mathrm{kW}$  output power, the PPC processes just 20W which corresponds to a phase-shift of roughly 4.2°. The rectifier half-bridge, HB<sub>3</sub>, and the inverter full-bridge,  $FB_3$ , of the PPC, are implemented using 100 VE-mode GaN HEMT from EPC in combination with Si8274 gate drive IC from Silicon Labs. The switching frequency of the inverter is set to  $f_{s,aux} = 600 \, \text{kHz}$ , a reasonable tradeoff between the distortion of the LLC converter's sinusoidal current and the occurring switching loss in FB3. The output filter at the 48 V side of the converter was designed to meet the 100 mV steady-state ripple requirement and confine output voltage deviation during load and input voltage transients to

Fig. 7. Pictures of the implemented P<sup>3</sup>DCT hardware prototype taken from different perspectives.

|                                    | Т                  | ECHNICAL DETAILS OF                                     | THE IMPLEMENTED P <sup>3</sup> DCT HARDWARE P                  | ROTOTYPE             |

|------------------------------------|--------------------|---------------------------------------------------------|----------------------------------------------------------------|----------------------|

|                                    | Component          | Parameter                                               | Description                                                    | Part Number          |

| Power Semiconductors               | $FB_1$             | $600 \text{ V}, 55 \text{ m}\Omega$<br>Infineon CoolGaN | HV-side full-bridge,<br>2 transistors in parallel              |                      |

|                                    | $\mathrm{FB}_2$    | $60 \text{ V}, 2.5 \text{ m}\Omega$<br>Infineon OptiMOS | LV-side full-bridge,<br>2 transistors in parallel              | BSC028N06NS          |

|                                    | $\mathrm{HB}_1$    | 100 V, 3.0 mΩ<br>EPC GaN                                | Transformer-side half-bridge                                   | EPC2022              |

|                                    | $FB_3$             | $100 \text{ V}, 5.6 \text{ m}\Omega$<br>EPC GaN         | HV-side full-bridge                                            | EPC2001C             |

|                                    | $F_{s}$            | $100\mathrm{kHz}$                                       | Switching frequency of $FB_1$ , $FB_2$ , $HB_1$                |                      |

|                                    | $F_{\rm s,aux}$    | $600\mathrm{kHz}$                                       | Switching frequency of $FB_3$                                  |                      |

| Transformer &<br>Resonant Tank     | Core               | PQ 40/40,<br>MnZn Ferrite N97                           | Customized $30 \mathrm{mm}$ height and $100 \mu\mathrm{m}$ gap | B65883A0000R097      |

|                                    | $N_1$              | 31 turns                                                | $120 \times 71  \mu m$ HF-litz wire                            |                      |

|                                    | $N_2$              | 4 turns                                                 | $630 \times 71  \mu m$ HF-litz wire                            |                      |

| sfor                               | $N_3$              | 2 turns                                                 | $120 \times 71 \mu\mathrm{m}$ HF-litz wire                     |                      |

| rans<br>eso                        | $L_{\sigma}$       | 18 µH                                                   | Stray inductance of transformer                                |                      |

| ΗN                                 | $L_{\rm m}$        | $950\mu\mathrm{H}$                                      | Magnetizing inductance of transformer                          |                      |

|                                    | $C_{\rm res}$      | $4\times 33\mathrm{nF}$                                 | 630 V COG MLCC                                                 | C3225C0G2J333J250AA  |

|                                    | $C_{\mathrm{in}}$  | $5 	imes 2\mu F$                                        | 500 V CeraLink                                                 |                      |

| æ                                  | $C_{\mathrm{aux}}$ | $5 \times 22  \mu F$                                    | 100 V X7S MLCC                                                 | CKG57NX7S2A226M500JJ |

| DC Capacitors &<br>Filter Passives | $L_{\mathrm{aux}}$ | 3.0 µH                                                  | Coilcraft Power Inductor $43 \text{ A} I_{\text{sat}}$         | XAL1580-302          |

| Cap:<br>Pa                         | $C_{\mathrm{f}}$   | $14 	imes 22  \mu F$                                    | 100 V X7S MLCC                                                 | CKG57NX7S2A226M500JJ |

| C C<br>lter                        | $L_{\rm f}$        | $150\mathrm{nH}$                                        | Inductor 50 A $I_{\rm sat}$                                    | FP0906R1-R15-R       |

| Ц                                  | a                  | $3 \times 560  \mu F$                                   | 63 V Electrolytic Capacitor                                    | EGPD630ELL561MK25H   |

|                                    | $C_{\mathrm{out}}$ | $1\times 680\mu\mathrm{F}$                              | 63 V Electrolytic Capacitor                                    | UHW1J681MHD6TN       |

| Cooling System                     | $l_{\rm hs}$       | 11 mm                                                   | Length of the heatsink                                         |                      |

|                                    | $w_{ m hs}$        | $50\mathrm{mm}$                                         | Width of the heatsink                                          |                      |

|                                    | $h_{ m hs}$        | $25\mathrm{mm}$                                         | Height of the fins                                             |                      |

|                                    | $w_{\rm c,hs}$     | $0.7\mathrm{mm}$                                        | Space between individual fins                                  |                      |

|                                    | $b_{\rm hs}$       | $4\mathrm{mm}$                                          | Thickness of the baseplate                                     |                      |

|                                    | Fans               | 5 V DC                                                  | Dimension: 25 mm x 25 mm                                       | MC25060V2-000U-A99   |

TABLE IV Fechnical Details of the Implemented P<sup>3</sup>DCT Hardware Prototyp

$\pm 500 \,\mathrm{mV} \ (\approx \pm 1\% \text{ of } 48 \,\mathrm{V})$ . The implemented CLC filter structure (cf. Fig. 2) is comprised of  $100 \,\mathrm{V}$  MLCCs at the output of FB<sub>3</sub>,  $C_{\rm f} = 308 \,\mu\text{F}$ , a subsequent  $150 \,\mathrm{nH}$  inductor and an  $2.4 \,\mathrm{mF}$  output capacitance assembled from individual  $560 \,\mu\text{F}$ ,  $63 \,\mathrm{V}$  aluminum electrolytic capacitors.

The developed control system presented in Section III was implemented on a TMS320F28335 Digital Signal Controller (DSC) from Texas Instruments Delfino series, located on the designated control PCB. The DSC generates the constant 50 % duty-cycle gate signals for full-bridge FB<sub>1</sub>, FB<sub>2</sub> and the phase-shift adjusted half-bridge HB<sub>3</sub> and the varying duty-cycle gate signals for the inverter full-bridge, FB<sub>3</sub>. The control board is supplied by means of a 12 V laboratory voltage source and is equipped with 12 V/5 V DC/DC converters (LMZ21701) to provide auxiliary power to the HV and LV power boards. The ground potential of the control board is connected to the DC- rail of the HV full-bridge FB<sub>1</sub> (cf. terminal  $\overline{2}$  in Fig. 2).

The DC input voltage,  $V_{in}$ , is measured by means of a

differential amplifier with a corner frequency set to 12 kHz employing the AD8615 operational amplifier from Analog Devices. The 48 V output voltage,  $V_{out}$ , is measured by means of a differential amplifier with a corner frequency set to 48 kHz employing the AD8615 operational amplifier. Subsequently, the precision isolation amplifier ACPL-C79B from Broadcom is employed to provide galvanic isolation between control board and LV-side. The output current,  $I_{out}$ , is measured with the current sensor ACS722 from Allegro featuring a 80 kHz bandwidth. The DC-link voltage of the PPC,  $V_{dc,aux}$ , is sensed by means of a differential amplifier with a corner frequency of 30 kHz employing the AD8615 operational amplifier and subsequently the ACPL-C87BT isolation amplifier from Broadcom to provide galvanic isolation between PPC and control board.

## V. EXPERIMENTAL RESULTS

In this section the experimental measurement results of the implemented P<sup>3</sup>DCT prototype are presented. First, the performance of the converter system under steady-state conditions is

presented and subsequently the effectiveness of the proposed topology and control system is confirmed by step response waveforms. The output voltage is tightly regulated to 48 V and the DC-link of the PPC is regulated to 50 V.

# A. Steady-State Measurements

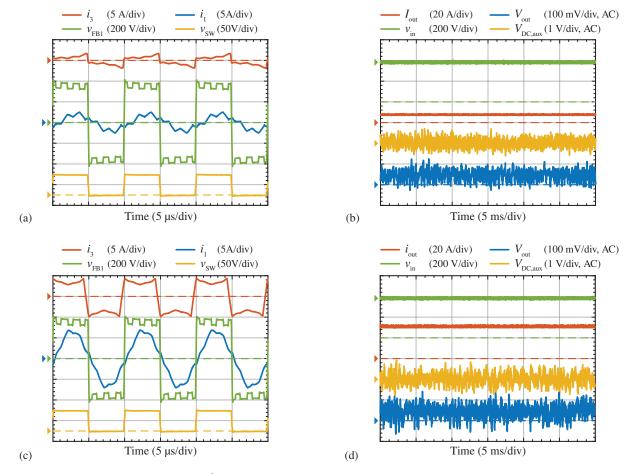

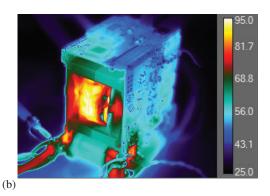

The waveforms of the P<sup>3</sup>DCT operating in steady-state at 350 W output power ( $P_r/4$ ) and 380 V nominal input voltage are shown in Fig. 8 (a) and (b) and at 1.5 kW output power in Fig. 8 (c) and (d). The high frequency ac waveforms of the converter are shown in Fig. 8 (a) and (b) with a time resolution of 5 µs/division and the DC waveforms are depicted in Fig. 8 (c) and (d) with a time resolution of 5 ms/division. The waveforms are labeled according to the circuit schematic shown in Fig. 2. Clearly visible is the superimposed pulse pattern in  $v_{\rm FB1}$  and the deviation of current  $i_1$  from its ideal sinusoidal shape which is more pronounced under light load condition. The power processed by the PPC increases from 9W at 350W output power to around 20W at rated output power also indicated by the increased amplitude of  $i_3$ . Moreover, the  $V_{\rm out}$  voltage ripple requirement of  $\pm 100 \,\mathrm{mV}$  is met as can be inferred from Fig. 8 (b) and (d). The conversion efficiency of the P<sup>3</sup>DCT was determined with the Yokogawa

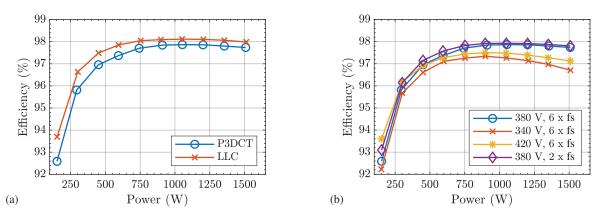

WT3000 power analyzer and includes the 12 V auxiliary power supply for digital control and gate drive circuitry as well as the 5V power supply for the employed DC fans. Fig. 12 (a) depicts the measured conversion efficiency with respect to output power of the P<sup>3</sup>DCT (blue line) and the DCT without regulation (red line). The realized P<sup>3</sup>DCT exhibits an efficiency of 97.7 % at 1.5 kW and shows a peak efficiency of 97.9% around 1.0 kW. In comparison, the DCT transformer without regulation (PPC disabled and/or bypassed) reaches 98.0% efficiency at  $1.5\,\mathrm{kW}$  and a peak efficiency of 98.1%around 1.0 kW. It must be mentioned, that in case of the unregulated DCT, the input voltage  $V_{in}$  was slightly adjusted (3% max. deviation from nominal input voltage) to ensure 48 V at the output. It can be concluded that the additional PPC leads to a reduction of efficiency by approximately  $0.25\,\%$  for an output power above  $1\,\mathrm{kW}$  and to a reduction of  $0.3\,\%$  -1% in the low output power range. At rated output power, the reduction of 0.25% in efficiency corresponds to an additional power loss of roughly 3.75 W caused by the PPC assuming that the loss of the DCT is unchanged. The PPC processes around 20 W at the input terminal (cf.  $3 - \overline{3}$  in Fig. 2) in this operating point which results in an estimated efficiency of approximately 82%. The efficiency with respect to output

Fig. 8. Measured steady-state waveforms of the  $P^3DCT$  hardware demonstrator operating at a quarter of the output power,  $P_r/4 = 350$  W, shown in (a) and (b) and at rated output power,  $P_r = 1.5$  kW, shown in (c) and (d). The waveforms of the HF link are depicted in (a) and (c) and the DC waveforms are shown in (b) and (d). The waveforms are labeled according to the circuit schematic shown in Fig. 2.

Fig. 9. Efficiency of the  $P^3DCT$  with respect to output power determined with Yokogawa WT3000 power analyzer. (a) shows the efficiency of the  $P^3DCT$  for nominal input voltage,  $V_{in} = 380$  V, opposed to the efficiency of the unregulated DCT (main converter) without PPC. (b) shows the efficiency of the  $P^3DCT$  with respect to output power for different input voltages and switching frequencies of FB<sub>3</sub> (cf. Fig. 2)

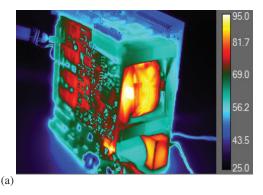

Fig. 10. Steady state infrared image of the  $P^3DCT$  operating at  $1.5 \, kW$  output power. The PPC processes  $100 \, W$  in the selected operating point. The low-voltage side of the converter facing the IR camera is shown in (a) and the high-voltage side in (b).

power for the minimal and maximal specified input voltage,  $V_{\rm in} = 340 \, {

m V}$  and  $V_{\rm in} = 420 \, {

m V}$  is depicted in red (cross marker) and in yellow (star marker), respectively. Since the PPC processes a larger share of the output power if the input voltage deviates from the nominal 380 V, the overall converter efficiency deteriorates as the PPC exhibits a lower efficiency. At 340 V and 420 V, the overall efficiency at the rated power drops to 96.7% and 97.13%, respectively. As discussed in Section II-A, for lower than nominal input voltage the power processed by the PPC only circulates within the system and is not provided to the output which explains why the overall efficiency at  $V_{\rm in} = 340 \, {\rm V}$  is lower compared to  $V_{\rm in} = 420 \, \text{V}$ . Moreover, the efficiency of the P<sup>3</sup>DCT with inverter full-bridge FB3 operating at only 200 kHz (only twice the DCT switching frequency,  $F_s$ ) is depicted in purple (diamond marker). It can be seen that the overall efficiency marginally improves, most notably at light load conditions. The infrared (IR) images in Fig. 10 show the steady-state temperature distribution of the  $P^3DCT$  operating at  $1.5 \,\mathrm{kW}$ output power with 100 W being processed by the PPC. The captured temperature distribution of the converter with the LV-side and HV-side facing the IR camera is depicted in Fig. 10 (a) and (b), respectively, and reveals that permanent operation at rated power can be sustained by the realized hardware. It can be seen that the max. measured surface temperature of 95 °C is attained by the transformer winding.

The LV-side power transistors (OptiMOS) and the rectifier of the PPC attain a steady-state temperature of around 80 °C. The HV-side power transistors (CoolGaN) and the inverter of the PPC exhibit a surface temperature in the 60 °C range.

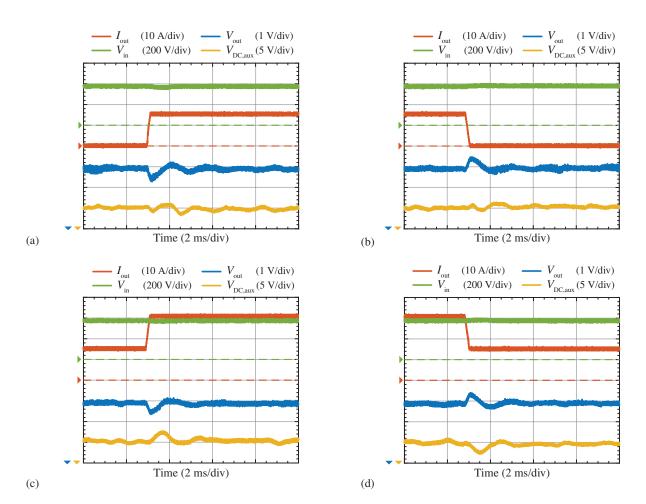

#### B. Step Response Measurements

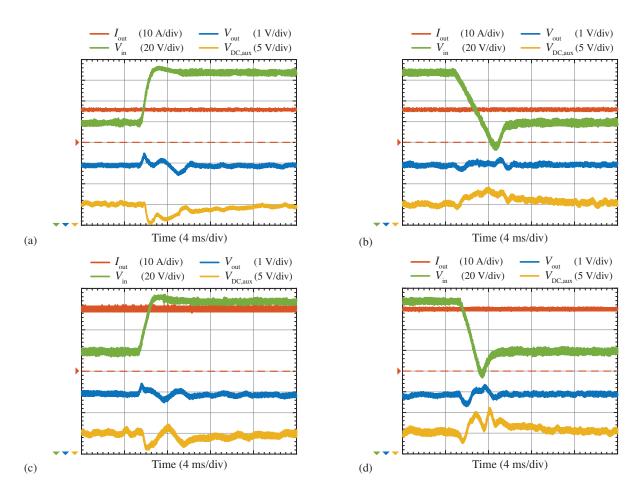

In order to assess the performance of the converter with proposed control system, stepwise input voltage and output load variations were applied. The output load was adjusted with a Chroma 63202 electric load and the input voltage steps were applied using a Xantrex XDC 600-10 DC supply. The current and voltage slew-rates of the supplies were set to their maximum supported values for the conducted step response experiments. Figs. 11 (a) and (b) depict the output voltage and PPC DC-link voltage of the P<sup>3</sup>DCT subject to a stepwise change of output load between 0W and 750W. Likewise, the response to a stepwise change of output load between 750 W and 1.5 kW is shown in Fig. 11 (c) and (d). It can be seen from the measurements, that stepwise load changes up to half the rated power are causing a Vout deviation of less than  $\pm 500 \,\mathrm{mV}$  ( $\approx \pm 1 \,\%$  of  $48 \,\mathrm{V}$ ) which is eliminated by the control in less than approximately 5 ms. The deviation in DClink voltage,  $V_{\rm DC,aux}$ , remains within  $\pm 3 \,\rm V$  and settles within  $3 \,\mathrm{ms}$ . The responses of the P<sup>3</sup>DCT subject to a 50 V stepwise change in input voltage amplitude between 350 V and 400 V are shown in Fig. 12, whereby in Fig. 12 (a) and (b) the input

Fig. 11. Measured output voltage  $V_{\text{out}}$  and PPC DC-link time behavior of the  $P^3$ DCT hardware demonstrator subject to a stepwise output load change between 0 W and 750 W shown in (a) and (b) and between 750 W and 1.5 kW shown in (c) and (d). The waveforms are labeled according to the circuit schematic shown in Fig. 2.

voltage steps are performed at 750 W output power and in Fig. 12 (c) and (d) at 1.5 kW output power. It can be seen from the experimental waveforms, that the maximum  $V_{\text{out}}$  deviation resulting from input voltage steps with 50 V magnitude is also around  $\pm 500 \text{ mVand}$  settles in less than approximately 8 ms. The deviation in DC-link voltage,  $V_{\text{DC,aux}}$ , remains within  $\pm 7 \text{ V}$  and settles within 8 ms. Note that because of the limited current sink capability of the employed DC supply, the input voltage slope is mainly governed by the actual load of the converter which explains the different slew rates in Fig. 12 (c) and (d), and consequently there is an undershoot of roughly 20 V present in  $V_{\text{in}}$ .

**Remark:** In order to visualize the basic operation of the P<sup>3</sup>DCT, this paper is accompanied with additional video content showing the oscilloscope screen with several captured waveforms: Channel C1 (yellow) shows the PPC DC-link voltage  $V_{DC,aux}$ ; Channel C2 (red) shows the PPC rectifier current  $i_3$ ; Channel C3 shows output voltage  $V_{out}$  (blue); Channel C4 (green) shows the primary full-bridge voltage,  $v_{FB1}$ . In **Video A**, the output voltage reference is slowly varied between 43 V and 52 V in order to visualize how controller PI<sub>out</sub> adjusts  $\overline{v}_{aux}$ ; the superimposed pulse-pattern in  $v_{FB1}$  changes accordingly. The DC-link voltage controller, PI<sub>aux</sub>

adjusts the phase-shift according to the resulting processed power (depends on level of  $\overline{v}_{aux}$ ) which alters the amplitude of current  $i_3$  to keep  $V_{DC,aux}$  at its reference value. In a similar fashion, **Video B** shows the waveforms of the the P<sup>3</sup>DCT subject to a slow variation of the DC-link reference value between 40 V and 60 V, illustrating how the DC-link voltage can be changed while keeping  $V_{out}$  tightly regulated to the desired 48 V. In **Video C**, the DC input voltage of the P<sup>3</sup>DCT,  $V_{in}$ , is slowly varied between 340 V and 420 V. It can be seen how  $\overline{v}_{aux}$  and thus the superimposed pulse-pattern is adopted by controller PI<sub>out</sub> in order to keep  $V_{out}$  at 48 V despite the changing input voltage.

#### VI. CONCLUSION

In this paper a novel approach to realize a high efficiency 380 V to 48 V DC/DC converter with output voltage regulation was presented. A main DC/DC converter, implemented by means of an unregulated resonant LLC converter operating as DC transformer (DCT), is accompanied by a partial-power auxiliary converter (PPC) dedicated to tightly regulate the output voltage by means of adjusting the average input voltage of the main converter. Taking advantage of the transfer characteristic of the DCT, a filter-less implementation of the

Fig. 12. Measured output voltage  $V_{out}$  and PPC DC-link time behavior of the P<sup>3</sup>DCT hardware demonstrator subject to a stepwise change of the input voltage change  $V_{in}$  between 350 V and 400 V shown in (a) and (b) for 750 W output power and in (c) and (d) for 1.5 kW output power. The waveforms are labeled according to circuit schematic in Fig. 2.

PPC was proposed where the pulse-width modulated auxiliary DC-link voltage is superimposed to the DC input voltage of the main converter. Since the PPC processes only a fraction of the rated power, the overall efficiency is only marginally affected. A prototype of the proposed converter rated at 1.5 kW was implemented and specified to cope with input voltage variations between 340 V - 420 V. The hardware demonstrator features an overall conversion efficiency of 97.7 % at rated power and a power density of  $8.6 \text{ kW/dm}^3$ . The performance of the partial-power regulator with proposed control system was assessed by means of input voltage and load step responses. A stepwise change of half the rated output power (750 W) and a 50 V stepwise variation of the input voltage are causing an output voltage deviation of less than  $\pm 500 \text{ mV}$  which is settled within 8 ms.

Adding output voltage control to an unregulated, seriesresonant LLC DC/DC converter by means of a PPC adds roughly 10% of volume to the converter while reducing the overall efficiency by 0.3%. The proposed PPC can also be used to mitigate or completely eliminate the double-line frequency DC voltage ripple in single-phase DC/AC converter systems with very tight voltage ripple requirements and/or demanding power density requirements.

#### REFERENCES

- J. Huber and J. W. Kolar, "Analysis and Design of Fixed Voltage Transfer Ratio DC/DC Converter Cells for Phase-Modular Solid-State Transformers," in *Proc. of the IEEE Energy Convers. Congr. and Expo.* (ECCE USA), Montreal, Canada, 2015.

- [2] K. Zhang, "Large- and Small-Signal Average Modeling of Dual Active Bridge DC-DC Converter Considering Power Losses," M.Sc. Thesis, College of Electrical and Computer Eng., Univ. of British Columbia, Vancouver, Aug. 2015. [Online]. Available: https://open.library.ubc.ca/ cIRcle/collections/ubctheses/24/items/1.0166507

- [3] F. Krismer, "Modeling and Optimization of Bidirectional Dual Active Bridge DC/DC Converter Topologies," Doctoral Thesis, Department of Information Technology and Electrical Eng., ETH Zurich, Switzerland, 2010. [Online]. Available: https://doi.org/10.3929/ethz-a-006395373

- [4] U. Drofenik, A. Stupar, J. W. Kolar, "Analysis of Theoretical Limits of Forced-Air Cooling Using Advanced Composite Materials With High Thermal Conductivities," *IEEE Transactions on Components, Packaging,* and Manufacturing Technology, Vol. 1, No. 4, pp. 528-535, April 2011.

- [5] J. A. Carrasco, A. H. Weinberg, E. Maset and E. J. Dede, "A High-Efficiency Regulation Technique for a Zero-Voltage Zero-Current Power Switching Converter,"*IEEE Transactions on Power Electronics*, Vol. 13, No. 4, pp. 739-747, 1998.

- [6] J. Zhao, K. Yeates and Y. Han, "Analysis of High Efficiency DC/DC Converter Processing Partial Input/Output Power," in *Proc. of 14th IEEE* Workshop on Control and Modeling for Power Electronics (COMPEL), Salt Lake City, Utah, USA, 2013.

- [7] H. Chiu, Y. Lo, P. Tseng and Y. Liu, "High-Efficiency Battery Charger with Cascode Output Design,"*IET Power Electronics*, Vol. 7, No. 7, pp. 1725-1735, 2014.

- [8] H. Dai, L. Ye, D. Fu and D. Chen, "Parallel Hybrid Converter Apparatus and Method," Patent Application US2017/0207707 A1, July 20, 2017.

- [9] M. Salato, "Ein neuartiger Ansatz f

ür industrielle Gleichrichtersysteme: Kompakte, effiziente und modulare Architektur durch Wandler mit festem Übersetzungsverh

ältnis (in German)," Vicor U.K. Ltd, White Paper, 2014.

- [10] H. Dai, D. Fu, L. Ye and D. Chen, "Serial Hybrid Converter Apparatus and Method," Patent Application US2016/094135 A1, March 31, 2016.

- [11] L. Zhang, X. Wu and H. Chen, "1MHz LLC Resonant DC/DC Converter with PWM Output Regulation Capability," in *Proc. of the 8th IEEE Intern. Power Electronics and Motion Control Conf.*, (IPEMC-ECCE Asia), Hefei, China, 2016.

- [12] X. Wu, H. Chen and Z. Qian, "1-MHz LLC Resonant DC Transformer (DCX) with Regulating Capability," in *IEEE Transactions on Industrial Electronics*, Vol. 63, No. 5, pp. 2904-2912, 2016.

[13] R. Button, "An Advanced Photovoltaic Array Regulator Module," in

- [13] R. Button, "An Advanced Photovoltaic Array Regulator Module," in Proc. of the 31st Intersociety Energy Conversion Eng. Conf. (IECEC), Washington DC, 1996.

- [14] J. Enslin and D. Snyman, "Combined Low-Cost, High-Efficient Inverter, Peak Power Tracker and Regulator for PV Applications," *IEEE Transactions on Power Electronics*, Vol. 6, No. 1, pp. 73-82, 1991.

- [15] M. S. Agamy, M. Harfman-Todorovic, A. Elasser, S. Chi, R. L. Steigerwald, J. A. Sabate, A. J. McCann, L. Zhang and F. J. Mueller, "An Efficient Partial Power Processing DC/DC Converter for Distributed PV Architectures," *IEEE Transactions on Power Electronics*, Vol. 29, No. 2, pp. 674-686, 2014.

- [16] M. Kasper, D. Bortis and J. W. Kolar, "Classification and Comparative Evaluation of PV Panel-Integrated DC-DC Converter Concepts," *IEEE Transactions on Power Electronics*, Vol. 29, No. 5, pp. 2511-2526,2014.

- [17] R. Liu and C. Q. Lee, "The LLC-type Series Resonant Converter-Variable Switching Frequency Control," in *Proc. of the 32nd Midwest Symposium on Circuits and Systems*, Champaign, Illinois, USA, 1989.

- [18] I. O. Lee and G. W. Moon, "Analysis and Design of a Three-Level LLC Series Resonant Converter for High- and Wide-Input-Voltage Applications," *IEEE Transactions on Power Electronics*, Vol. 27, No. 6, pp. 2966-2979, June 2012.

- [19] F. Musavi, M. Craciun, M. Edington, W. Eberle and W. G. Dunford, "Practical Design Considerations for a LLC Multi-Resonant DC-DC Converter in Battery Charging Applications," in *Proc. of the IEEE Applied Power Electronics Conf. (APEC)*, Orlando, Florida, USA, 2012.

- [20] M. Jovanovic and B. T. Irving, "Efficiency Optimization of LLC Resonant Converters Operating in Wide Input- and/or Output-Voltage Range by On-the-Fly Topology-Morphing," in *Proc. of the IEEE Applied Power Electronics Conf. (APEC)*, Charlotte, North Carolina, USA, 2015.

- [21] D. Bortis, O. Knecht, D. Neumayr and J. W. Kolar, "Comprehensive Evaluation of GaN GIT in Low- and High-Frequency Bridge Leg Applications," in *Proc. of the 8th IEEE Intern. Power Electron. and Motion Control Conf. (ECCE Asia)*, Hefei, China, 2016.

**Dominik Neumayr** (SM'15) started his academic education at the University of Applied Sciences (FH) for Automation Engineering in Wels, Austria and received the Dipl.-Ing. (FH) degree in 2008. He was with the Center for Advanced Power Systems (CAPS) in Tallahassee, FL, USA, working on Power/Controller Hardware-in-the-Loop simulations and control systems design for AC/DC/AC PEBB based converter systems from ABB. He continued his academic education at the Swiss Federal Institute of Technology in Zurich (ETH Zurich) with a focus

on power electronics and control engineering and received the M.Sc. degree in electrical engineering and information technology in 2015. Since spring 2015 he is a PhD student at the Power Electronic Systems (PES) Laboratory, ETH Zurich. His current research focuses on the design and control of high power density converter systems.

Matthias Vöhringer received his Bachelor degree in Renewable Energy Engineering at University of Stuttgart in 2014. After an internship in power electronics at the competence center for power electronics at Maschinenfabrik Reinhausen GmbH he continued his academic education at ETH Zurich, focusing on power electronics and power systems. After working on the integration of power modules during an internship at the ABB corporate research center, he completed his final thesis at ETH's Power Electronic Systems Laboratory (PES) and subse-

quently received his Master degree in Energy Science and Technology in 2017. Since 2018, Matthias is working as a system engineer for power electronic converters at ABB Switzerland Ltd..

Nikolaos Chrysogelos received the B.Sc. degree in electrical engineering from the National Technical University of Athens (NTUA) in 2014 and the M.Sc. degree with a focus on electric power systems and power electronics from the Swiss Federal Institute of Technology (ETH) in 2017. He was involved in projects regarding optimization of power converters at the Research Center of ABB in Baden and sensor networks at Cern in Geneva while now he is working as a power electronics engineer in drone industry.

Gerald Deboy received the M.S. and Ph.D. degree in physics from the Technical University Munich in 1991 and 1996 respectively. He joined Siemens Corporate Research and Development in 1992 and the Semiconductor Division of Siemens in 1995, which became Infineon Technologies later on. His research interests were focused on the development of new device concepts for power electronics, especially the revolutionary COOLMOS(TM) technology. From 2004 onward he was heading the Technical marketing department for power semiconductors

and ICs within the Infineon Technologies Austria AG. Since 2009 he is leading a business development group specializing on new fields for power electronics. He is a Sr. member of IEEE and has served as a member of the Technical Committee for Power Devices and Integrated Circuits within the Electron Device Society. He has authored and coauthored more than 70 papers in national and international journals including contributions to three student text books. He holds more than 60 granted international patents and has more applications pending.

Johann W. Kolar is a Fellow of the IEEE and received his Ph.D. degree (summa cum laude) from the Vienna University of Technology, Austria. He is currently a Full Professor and the Head of the Power Electronic Systems Laboratory at the Swiss Federal Institute of Technology (ETH) Zurich. He has proposed numerous novel PWM converter topologies, and modulation and control concepts and has supervised over 70 Ph.D. students. He has published over 750 scientific papers in international journals and conference proceedings, 4 book chapters, and has

filed more than 160 patents. He has presented over 20 educational seminars at leading international conferences, has served as IEEE PELS Distinguished Lecturer from 2012 through 2016, and has received 26 IEEE Transactions and Conference Prize Paper Awards, the 2014 IEEE Power Electronics Society R. David Middlebrook Achievement Award, the 2016 IEEE William E. Newell Power Electronics Award, the 2016 IEEE PEMC Council Award, and two ETH Zurich Golden Owl Awards for excellence in teaching.